Technical documentation

ZHCSI22F - OCTOBER 2017 - REVISED DECEMBER 2021

**TPS2662**

# TPS2662x 具有集成输入和输出反极性保护功能的 60V 800mA 工业电子保险丝

# 1 特性

**TEXAS**

INSTRUMENTS

- 工作电压为 4.5V 至 60V, 绝对最大值为 62V

- 集成反向输入极性保护,低至 - 60V

- 集成反向输出极性保护,低至 - (60 - V<sub>IN</sub>) ( 仅限 TPS26624 和 TPS26625 )

- 总 RON 为 478m Ω 的集成背对背 MOSFET

- 25mA 至 880mA 可调节电流限制 (880mA 时精度为 ±5%)

- 使用最少的外部组件在浪涌期间提供负载保护 (IEC 61000-4-5)

- 符合 IEC 61000-4-4 标准的电气快速瞬变抗扰度

- 快速反向电流阻断响应 (0.3µs)

- 可调节 UVLO、OVP 切断、 输出压摆率控制,用于浪涌电流限制

- **38V** 固定过压钳位 (仅限 TPS26622 和 TPS26623)

- 低静态电流(工作时为 340µA, 关断时为 12µA)

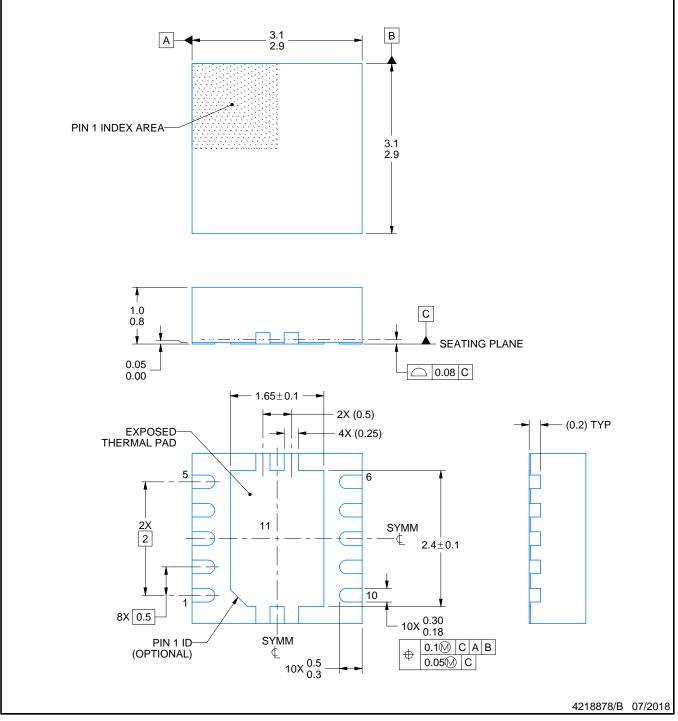

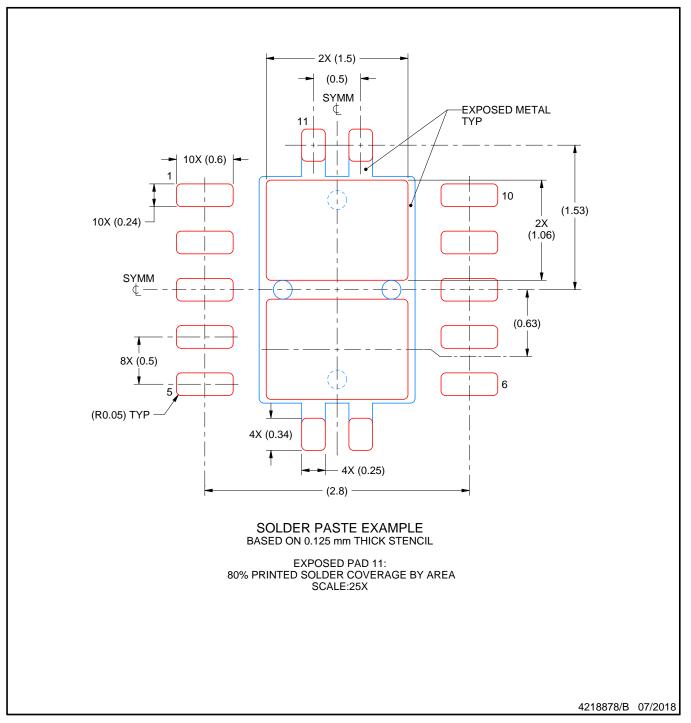

- 小尺寸 10L (3mm × 3mm) VSON

- 通过 UL 2367 认证

- 文件编号 169910

- R<sub>ILIM</sub> ≥ 7.5kΩ(最大电流为 0.91A)

- 通过 IEC 62368-1 认证

# 2 应用

- PLC I/O 模块

- 交流和伺服驱动器

- 传感器和控制

- 恒温器

- PoE 高侧保护

# 3 说明

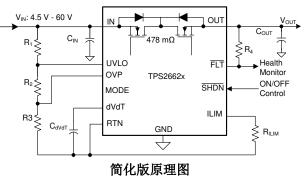

TPS2662x 系列高电压电子保险丝设计紧凑,功能丰 富,且具有一整套保护功能。4.5V 至 60V 的宽电源输 入范围可实现对众多常用直流总线电压的控制。该器件 可以承受并保护由高达 ±60V 的正负电源供电的负载。 TPS26624 和 TPS26625 器件支持输入和输出反极性 保护功能。集成的背对背 FET 可提供反向电流阻断功 能,因此该器件适用于在电源故障和欠压条件下要求保 持输出电压的系统。负载、电源和器件保护具有许多可 调特性,包括过流、输出压摆率和过压、欠压阈值。 TPS2662x 系列内部可靠的保护控制模块以及高额定电 压有助于简化针对浪涌保护的系统设计。

TPS26620、TPS26622 和 TPS26624 具有闭锁功能, TPS26621、TPS26623 和 TPS26625 具有自动重试功 能,用于应对过热和过流故障事件。

这些器件采用 3mm × 3mm 10 引脚 SON 封装,额定 工作温度范围为 - 40°C 至 +125°C。

| 器件型号                                                                 | 封装       | 封装尺寸(标称值)       |  |  |  |  |

|----------------------------------------------------------------------|----------|-----------------|--|--|--|--|

| TPS26620<br>TPS26621<br>TPS26622<br>TPS26623<br>TPS26624<br>TPS26625 | SON (10) | 3.00mm × 3.00mm |  |  |  |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 (1)录。

- 60V 电源时的反向输入极性保护

# **Table of Contents**

| 1 | 特性                                   | 1 |

|---|--------------------------------------|---|

|   | 应用                                   | 1 |

|   | ,<br>说明                              | 1 |

|   | Revision History                     | 2 |

|   | Device Comparison Table              | 4 |

|   | Pin Configuration and Functions      |   |

|   | Specifications                       |   |

|   | 7.1 Absolute Maximum Ratings         | 5 |

|   | 7.2 ESD Ratings                      |   |

|   | 7.3 Recommended Operating Conditions |   |

|   | 7.4 Thermal Information              | 6 |

|   | 7.5 Electrical Characteristics       | 6 |

|   | 7.6 Timing Requirements              | 8 |

|   | 7.7 Typical Characteristics          | 9 |

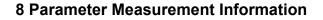

|   | Parameter Measurement Information14  |   |

| 9 | Detailed Description1                | 5 |

|   | 9.1 Overview                         | 5 |

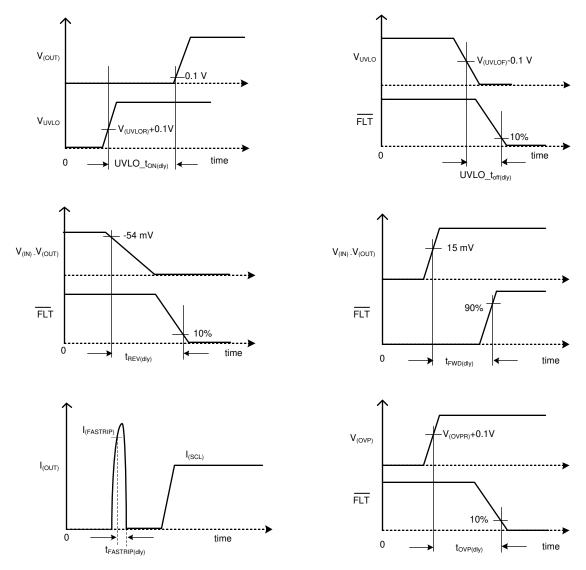

|   | 9.2 Functional Block Diagram16       | 6 |

|   | 9.3 Feature Description16            | 6 |

|   | 9.4 Device Functional Modes          | 4 |

| 10 Application and Implementation       | 25 |

|-----------------------------------------|----|

| 10.1 Application Information            |    |

| 10.2 Typical Application                |    |

| 10.3 System Examples                    |    |

| 10.4 Do's and Don'ts                    |    |

| 11 Power Supply Recommendations         |    |

| 11.1 Transient Protection               |    |

| 12 Layout                               |    |

| 12.1 Layout Guidelines                  |    |

| 12.2 Layout Example                     |    |

| 13 Device and Documentation Support     |    |

| 13.1 Documentation Support              |    |

| 13.2 接收文档更新通知                           |    |

| 13.3 支持资源                               |    |

| 13.4 Trademarks                         |    |

| 13.5 Electrostatic Discharge Caution    |    |

| 13.6 术语表                                |    |

| 14 Mechanical, Packaging, and Orderable |    |

| Information                             | 37 |

|                                         |    |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| C | hanges from Revision E (August 2019) to Revision F (December 2021)                                                              | Page            |

|---|---------------------------------------------------------------------------------------------------------------------------------|-----------------|

| • | 更新了整个文档中的表格、图和交叉参考的编号格式                                                                                                         | 1               |

| • | Moved I <sub>SHDN</sub> from Source Current to Sink Current row in the Absolute Maximum Ratings table                           | 5               |

| • | Changed External Capacitance min from 0.1 to 0.01 in Recommended Operating Conditions table                                     |                 |

| • | Deleted OVP <sub>MAX</sub> row in Electrical Characteristics table                                                              | 6               |

| • | Changed I(FLT) test condition in Electrical Characteristics table                                                               | 6               |

| • | Deleted UVLO_t <sub>REC</sub> row in Timing Requirements table                                                                  |                 |

| • | Updated the Parameter Measurement Information section                                                                           | 14              |

| • | Added t <sub>CL Dly</sub> description to Overvoltage Protection (OVP) section                                                   | 17              |

| • | Changed device mention to TPS2662x to include all variants in Input Side Reverse Polarity Protection                            | section         |

| • | Added UVLO back to the Overload Protection section                                                                              | 20              |

| • | Added more description and clarification for the t <sub>CL(dly)</sub> parameter in the Overload Protection section              | <mark>20</mark> |

| • | Added minimum voltage to FAULT Response section                                                                                 | 23              |

| С | hanges from Revision D (February 2019) to Revision E (August 2019)                                                              | Page            |

| • | 将特性部分中的"UL 2367 认证正在处理中"更改为"通过 UL 2367 认证"和"通过 IEC 62368-1 认证                                                                   | 1               |

| • | Replaced TPS26623 with TPS26624 for Pin No. 4 SHDN in the Pin Functions table                                                   |                 |

| • | Added UVLO Recovery Time in the Timing Requirements table in the Specifications section                                         |                 |

| • | Changed Input voltage range MAX from 60 V to 62 V in the Absolute Maximum Ratings table in the                                  |                 |

|   | Specifications section                                                                                                          | <mark>5</mark>  |

| • | Changed Input voltage MAX from 57 V to 60 V in the <i>Recommended Operating Conditions</i> table in the Specifications section. | 5               |

| • | Updated the Parameter Measurement Information graph to explain the UVLO_t <sub>REC</sub>                                        | 14              |

| • | Updated the Feature Description Undervoltage Lockout (UVLO) section to explain the UVLO_tREC time                               | r 16            |

|   |                                                                                                                                 |                 |

٠

| •<br> | Removed UVLO from the Overload Protection section<br>hanges from Revision C (July 2018) to Revision D (February 2019) | 20<br>Page       |

|-------|-----------------------------------------------------------------------------------------------------------------------|------------------|

| •     | Changed SHDN pin voltage MAX from 4 V to 6 V in the <i>Recommended Operating Conditi</i><br>Specifications section    | ons table in the |

| CI    | hanges from Revision B (April 2018) to Revision C (July 2018)                                                         | Page             |

| •     | 将状态从 "预告信息" 更改为 "量产数据"                                                                                                | 1                |

| CI    | hanges from Revision A (March 2018) to Revision B (April 2018)                                                        | Page             |

| •     | Changed Repinse to Response in the Device Comparison table header                                                     | 4                |

| CI    | hanges from Revision * (October 2017) to Revision A (March 2018)                                                      | Page             |

| •     | 将一页更改为整个数据表                                                                                                           | 1                |

# **5** Device Comparison Table

| PART NUMBER | OVERVOLTAGE PROTECTION          | OVERLOAD and THERMAL FAULT<br>RESPONSE | REVERSE POLARITY PROTECTION |

|-------------|---------------------------------|----------------------------------------|-----------------------------|

| TPS26620    | Overvoltage cut-off, adjustable | Latch Off                              | Input side                  |

| TPS26621    | Overvoltage cut-off, adjustable | Auto-Retry                             | Input side                  |

| TPS26622    | Overvoltage clamp, fixed (38 V) | Latch Off                              | Input side                  |

| TPS26623    | Overvoltage clamp, fixed (38 V) | Auto-Retry                             | Input side                  |

| TPS26624    | Overvoltage cut-off, adjustable | Latch Off                              | Input and Output side       |

| TPS26625    | Overvoltage cut-off, adjustable | Auto-Retry                             | Input and Output side       |

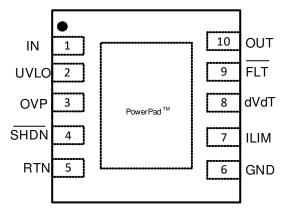

# **6** Pin Configuration and Functions

# 图 6-1. DRC Package 10-Pin VSON Top View

#### 表 6-1. Pin Functions

| PIN |           | ТҮРЕ  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                            |  |

|-----|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME      | ITFE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                            |  |

| 1   | IN        | Power | Input supply voltage                                                                                                                                                                                                                                                                                                                                   |  |

| 2   | UVLO      | I     | Resistor programmable undervoltage lockout threshold setting input. An undervoltage event pens the internal FET. If the Undervoltage Lock Out function is not needed, the UVLO terminal nust be connected to the IN terminal with at least a $1-M\Omega$ resistor. UVLO pin is 5-V rated and his resistor limits the UVLO pin current to < 60 $\mu$ A. |  |

| 3   | OVP       | I     | Resistor programmable overvoltage protection threshold. An overvoltage event opens internal FET. In TPS26620, TPS26621, TPS26624, TPS26625 devices, if overvoltage protection feature is not to be used then connect OVP terminal to RTN. For overvoltage clamp response (TPS26622 and TPS26623 only) connect OVP to RTN externally.                   |  |

| 4   | SHDN      | I     | Shutdown pin. Pulling the pin low makes the device to enter into low power shutdown mode.<br>Cycling SHDN low and then back high resets the device that has latched off (TPS26620,<br>IPS26622, TPS26624 only) due to a fault condition.                                                                                                               |  |

| 5   | RTN       | -     | Reference ground for all internal voltages                                                                                                                                                                                                                                                                                                             |  |

| 6   | GND       | -     | System ground                                                                                                                                                                                                                                                                                                                                          |  |

| 7   | ILIM      | I/O   | A resistor from this pin to RTN sets the overload and short-circuit current limit. See the Overload and Short Circuit Protection section.                                                                                                                                                                                                              |  |

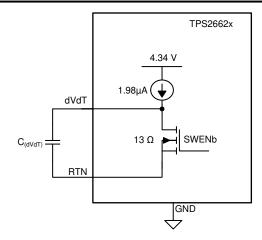

| 8   | dVdT      | I/O   | A capacitor from this pin to RTN sets output voltage slew rate. See the Hot Plug-In and In-Rush Current Control section.                                                                                                                                                                                                                               |  |

| 9   | FLT       | 0     | Fault event indicator. This pin is an open drain output. If unused, leave floating.                                                                                                                                                                                                                                                                    |  |

| 10  | OUT       | Power | Output voltage                                                                                                                                                                                                                                                                                                                                         |  |

| -   | PowerPAD™ | -     | Connect PowerPAD to RTN plane for heat sinking. Do not use PowerPAD as the only electrical connection to RTN.                                                                                                                                                                                                                                          |  |

# **7** Specifications

# 7.1 Absolute Maximum Ratings

|                                |                                                                                                                                     | MIN                       | MAX                | UNIT |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------|------|

|                                | IN, IN - OUT                                                                                                                        | - 60                      | 62                 |      |

|                                | OUT (TPS26624 and TPS26625 Only)                                                                                                    | – (60 – V <sub>IN</sub> ) | 62                 |      |

| Input voltage renge            | IN, IN - OUT (10 ms transient), T <sub>A</sub> = 25 $^\circ \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | - 70                      | 70                 | V    |

| Input voltage range            | [IN, OUT, FLT, SHDN] to RTN                                                                                                         | - 0.3                     | 62                 | v    |

|                                | [UVLO, OVP, dVdT, ILIM] to RTN                                                                                                      | - 0.3                     | 5                  |      |

|                                | RTN                                                                                                                                 | - 60                      | 0.3                |      |

| Sink current                   | I <sub>FLT</sub> , I <sub>dVdT</sub>                                                                                                |                           | 10                 | mA   |

| Source current                 | I <sub>dVdT</sub> , I <sub>ILIM</sub> , I <sub>SHDN</sub>                                                                           | Internally limite         | d                  |      |

| Operating junction temperature | т                                                                                                                                   | - 40                      | 150                | °C   |

| Transient junction temperature | - ' 」                                                                                                                               | - 65                      | T <sub>(TSD)</sub> | °C   |

| Storage temperature            | T <sub>stg</sub>                                                                                                                    | - 65                      | 150                | °C   |

over operating free-air temperature range, all voltages referred to GND (unless otherwise noted)<sup>(1)</sup>

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                                            |                                                                             |                                                                                          | VALUE | UNIT |

|--------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±1500                                                                                    | V     |      |

|                                            |                                                                             | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                          |                                | MIN  | NOM | MAX | UNIT |

|--------------------------|--------------------------------|------|-----|-----|------|

| IN                       | Input voltage                  | 4.5  |     | 60  | V    |

| out, FLT                 | Input voltage                  | 0    |     | 60  | V    |

| UVLO, OVP,<br>dVdT, ILIM | Input voltage                  | 0    |     | 4   | V    |

| SHDN                     | Input voltage                  | 0    |     | 6   | V    |

| ILIM                     | Resistance                     | 7.5  |     | 267 | kΩ   |

| IN, OUT                  |                                | 0.01 |     |     | μF   |

| dVdT                     | External capacitance           | 6.8  |     |     | nF   |

| Tj                       | Operating junction temperature | - 40 | 25  | 125 | °C   |

#### 7.4 Thermal Information

|                        |                                              | TPS2662    |      |  |

|------------------------|----------------------------------------------|------------|------|--|

|                        | THERMAL METRIC <sup>(1)</sup>                | DRC (VSON) | UNIT |  |

|                        |                                              | 10 PINS    |      |  |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 44.8       | °C/W |  |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 39.5       | °C/W |  |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 20.7       | °C/W |  |

| ΨJT                    | Junction-to-top characterization parameter   | 0.5        | °C/W |  |

| Ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 20.7       | °C/W |  |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.4        | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

$\label{eq:constraint} \begin{array}{c} -40^{\circ}C \leqslant T_{A} = T_{J} \leqslant +125^{\circ}C, \, V_{(IN)} = 24 \; \text{V}, \, V_{(\,\overline{\text{SHDN}})} = 2 \; \text{V}, \, \text{R}_{(ILIM)} = 267 \; \text{k} \; \Omega \, , \, \overline{\text{FLT}} = \text{OPEN}, \, C_{(OUT)} = 1 \; \mu\text{F}, \, C_{(dVdT)} = \text{OPEN}. \ \text{(All voltages referenced to GND, (unless otherwise noted))} \end{array}$

|                        | PARAMETER                                           | TEST CONDITIONS                                                          | MIN   | TYP   | MAX   | UNIT |

|------------------------|-----------------------------------------------------|--------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY VO              | LTAGE                                               | · · ·                                                                    |       |       | I     |      |

| V <sub>(IN)</sub>      | Operating input voltage                             |                                                                          | 4.5   |       | 60    | V    |

| V <sub>(PORR)</sub>    | Internal POR threshold, rising                      |                                                                          | 3.54  | 3.73  | 4.2   | V    |

| V <sub>(PORHys)</sub>  | Internal POR hysteresis                             |                                                                          |       | 110   |       | mV   |

| IQ <sub>(ON)</sub>     | Supply surrent                                      | Enabled: V <sub>(SHDN)</sub> = 2 V                                       |       | 343   | 482   | μA   |

| IQ <sub>(OFF)</sub>    | <ul> <li>Supply current</li> </ul>                  | V <sub>(SHDN)</sub> = 0 V                                                |       | 11.5  | 25    | μA   |

| I <sub>(VINR)</sub>    | Reverse Input supply current                        | V <sub>(IN)</sub> = - 24 V, V <sub>(OUT)</sub> = 0 V                     |       | 50    | 130   | μA   |

| V <sub>(OVC)</sub>     | Over voltage clamp                                  | V <sub>(IN)</sub> > 40 V, ILOAD = 10 mA,TPS26622,<br>TPS26623 Only       | 36    | 37.5  | 40    | V    |

| UNDERVOL               | AGE LOCKOUT (UVLO) INPUT                            |                                                                          |       |       |       |      |

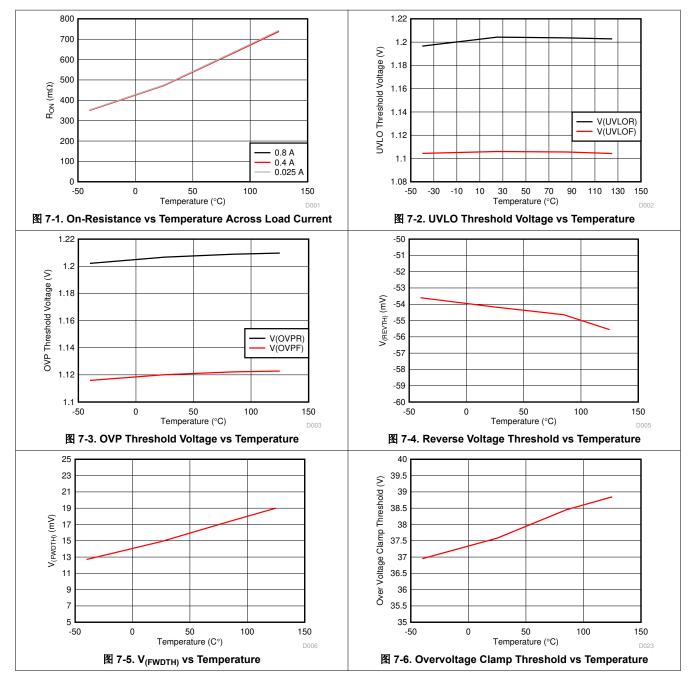

| V <sub>(UVLOR)</sub>   | UVLO threshold voltage, rising                      |                                                                          | 1.18  | 1.2   | 1.23  | V    |

| V <sub>(UVLOF)</sub>   | UVLO threshold, Falling                             |                                                                          | 1.09  | 1.1   | 1.135 | V    |

| I <sub>(UVLO)</sub>    | UVLO Input Leakage Current                          | $0 \text{ V} \leqslant \text{V}_{(\text{UVLO})} \leqslant 3.5 \text{ V}$ | - 100 | 0     | 100   | nA   |

| I <sub>(UVLO)</sub>    | UVLO Input Leakage Current                          | V <sub>(UVLO)</sub> = 5 V                                                |       | 18.8  | 38    | μA   |

| OVER VOLT              | AGE PROTECTION (OVP) INPUT                          |                                                                          |       |       | I     |      |

| V <sub>(OVPR)</sub>    | Overvoltage threshold voltage, rising               |                                                                          | 1.18  | 1.2   | 1.23  | V    |

| V <sub>(OVPF)</sub>    | Overvoltage threshold, falling                      |                                                                          | 1.09  | 1.12  | 1.135 | V    |

| I <sub>(OVP)</sub>     | OVP Input Leakage Current                           | $0 V \leq V_{(OVP)} \leq 5 V$                                            | - 100 | 0     | 100   | nA   |

| LOW IQ SHU             | JTDOWN ( SHDN) INPUT                                |                                                                          |       |       |       |      |

| V( SHDN)               | Output voltage                                      | I <sub>(SHDN)</sub> = 0.1 μA                                             | 2.39  | 2.781 | 3.1   | V    |

| V <sub>(SHUTF)</sub>   | SHDN Threshold Voltage for Low IQ Shutdown, Falling |                                                                          | 0.9   |       |       | V    |

| V <sub>(SHUTR)</sub>   | SHDN Threshold, rising                              |                                                                          |       |       | 1.8   | V    |

| I( SHDN)               | Input current                                       | V <sub>(SHDN)</sub> = 0.4 V                                              | - 10  | - 2.4 |       | μA   |

|                        | MP CONTROL (dVdT)                                   |                                                                          |       |       |       |      |

| I <sub>(dVdT)</sub>    | dVdT Charging Current                               | $V_{(dVdT)} = 0V$                                                        | 1.68  | 1.98  | 2.33  | μA   |

| R <sub>(dVdT)</sub>    | dVdT Discharging Resistance                         | $V_{(SHDN)} = 0 V$ , with $I_{(dVdT)} = 10mA$ sinking                    |       | 13.1  | 22    | Ω    |

| V <sub>(dVdTmax)</sub> | dVdT Max Capacitor Voltage                          |                                                                          | 4     | 4.34  | 4.75  | V    |

| GAIN <sub>(dVdT)</sub> | dVdT to OUT Gain                                    | V <sub>(OUT)</sub> /V <sub>(dVdT)</sub>                                  | 23.9  | 24.6  | 25.2  | V/V  |

# 7.5 Electrical Characteristics (continued)

$-40^{\circ}C \leq T_A = T_J \leq +125^{\circ}C$ ,  $V_{(IN)} = 24$  V,  $V_{(\overline{SHDN})} = 2$  V,  $R_{(ILIM)} = 267$  k  $\Omega$ ,  $\overline{FLT} = OPEN$ ,  $C_{(OUT)} = 1$   $\mu$ F,  $C_{(dVdT)} = OPEN$ . (All voltages referenced to GND, (unless otherwise noted))

|                           | PARAMETER                                                                   | TEST CONDITIONS                                                                                                                                                         | MIN   | TYP             | MAX          | UNIT    |  |  |  |  |  |

|---------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|--------------|---------|--|--|--|--|--|

| CURRENT LI                | MIT PROGRAMMING (ILIM)                                                      |                                                                                                                                                                         |       |                 |              |         |  |  |  |  |  |

| V <sub>(ILIM)</sub>       | ILIM bias voltage                                                           |                                                                                                                                                                         |       | 1               |              | V       |  |  |  |  |  |

|                           |                                                                             | $R_{(ILIM)}$ = 267 k $\Omega$ , $V_{(IN)} - V_{(OUT)}$ = 1 V                                                                                                            | 0.02  | 0.025           | 0.032        |         |  |  |  |  |  |

|                           |                                                                             | $R_{(ILIM)}$ = 44.2 k $\Omega$ , $V_{(IN)}$ – $V_{(OUT)}$ = 1 V                                                                                                         | 0.145 | 0.152           | 0.159        |         |  |  |  |  |  |

|                           |                                                                             | $R_{(ILIM)} = 26.7 \text{ k} \Omega$ , $V_{(IN)} - V_{(OUT)} = 1 \text{ V}$                                                                                             | 0.237 | 0.25            | 0.257        | ^       |  |  |  |  |  |

| I <sub>(OL)</sub>         |                                                                             | $R_{(ILIM)} = 13.3 \text{ k} \Omega$ , $V_{(IN)} - V_{(OUT)} = 1 \text{ V}$                                                                                             | 0.47  | 0.5             | 0.52         | A       |  |  |  |  |  |

|                           | Overload Current Limit                                                      | $R_{(ILIM)} = 8.25 \text{ k} \Omega$ , $V_{(IN)} - V_{(OUT)} = 1 \text{ V}$                                                                                             | 0.757 | 0.8             | 0.827        |         |  |  |  |  |  |

|                           |                                                                             | $R_{(ILIM)} = 7.5 \text{ k} \Omega, V_{(IN)} - V_{(OUT)} = 1 \text{ V}$                                                                                                 | 0.83  | 0.88            | 0.91         | )1      |  |  |  |  |  |

| I <sub>(OL_R-OPEN)</sub>  | _                                                                           | R <sub>(ILIM)</sub> = OPEN, Open Resistor Current<br>Limit (single point failure test: UL60950)                                                                         | 8     | 15.5            | 27           | mA      |  |  |  |  |  |

| I <sub>(OL_R-SHORT)</sub> |                                                                             | R <sub>(ILIM)</sub> = SHORT, Shorted Resistor<br>Current Limit (single point failure test:<br>UL60950)                                                                  | 31    | 39.3            | 51           | mA      |  |  |  |  |  |

| I <sub>(SCL)</sub>        | Short-Circuit Current Limit                                                 | $R_{(ILIM)} = 7.5 \text{ k} \Omega$ , $V_{(IN)} - V_{(OUT)} = 24 \text{ V}$                                                                                             |       | 0.885           |              | А       |  |  |  |  |  |

| I <sub>(FAST-TRIP)</sub>  | Fast-Trip Comparator Threshold                                              |                                                                                                                                                                         |       | 1.6             |              | А       |  |  |  |  |  |

| PASS FET OL               | JTPUT (OUT)                                                                 |                                                                                                                                                                         |       |                 | I            |         |  |  |  |  |  |

| R <sub>ON</sub>           |                                                                             | $\label{eq:2.1} \begin{array}{ c c c c } 0.025 \; A \leqslant I_{(OUT)} \leqslant 0.8 \; A_{,} \; T_{J} = 25^{\circ} C, \\ R_{(ILIM)} = 7.5 \; k \; \Omega \end{array}$ | 435   | 478             | 521          |         |  |  |  |  |  |

|                           |                                                                             | $\label{eq:loss_loss} \begin{array}{l} 0.025 \; A \leqslant I_{(OUT)} \leqslant 0.8 A_{,} \; T_{J} = 85^{\circ} C, \\ R_{(ILIM)} = 7.5 \; k \; \Omega \end{array}$      |       | 626             | 685          | mΩ      |  |  |  |  |  |

|                           |                                                                             |                                                                                                                                                                         | 250   | 478             | 800          |         |  |  |  |  |  |

| I <sub>lkg(OUT)</sub>     |                                                                             | $V_{(IN)} = 57 \text{ V}, V_{(\overline{SHDN})} = 0 \text{ V}, V_{(OUT)} = 0 \text{ V},$<br>Sourcing                                                                    |       | 4.38            | 12           |         |  |  |  |  |  |

|                           | OUT Leakage Current in Off State                                            | $V_{(IN)} = 0 \text{ V}, V_{(SHDN)} = 0 \text{ V}, V_{(OUT)} = 24 \text{ V},$<br>Sinking                                                                                |       | 7.27            | 102          | 2<br>µA |  |  |  |  |  |

|                           |                                                                             | $V_{(IN)}$ = - 57V, $V_{(SHDN)}$ = 0V, $V_{(OUT)}$ = 0V, Sinking                                                                                                        | 168   |                 |              | μΑ      |  |  |  |  |  |

|                           | OUT leakage current under output reverse polarity condition                 | $V_{(IN)}$ = 24 V, $V_{(OUT)}$ = $-$ 24 V, $V_{(\overline{SHDN})}$ = 2 V, TP26624, TPS26625 Only                                                                        |       | 450             |              |         |  |  |  |  |  |

| V <sub>(REVTH)</sub>      | $V_{(IN)} - V_{(OUT)}$ threshold for reverse protection comparator, falling |                                                                                                                                                                         | - 71  | - 54            | - 40         | mV      |  |  |  |  |  |

| V <sub>(FWDTH)</sub>      | $V_{(IN)} - V_{(OUT)}$ threshold for reverse protection comparator, rising  |                                                                                                                                                                         | 1.4   | 15              | 30           | mV      |  |  |  |  |  |

| FAULT FLAG                | (FLT): ACTIVE LOW                                                           |                                                                                                                                                                         |       |                 | <sup>_</sup> |         |  |  |  |  |  |

| R <sub>(FLT)</sub>        | FLT Pull-Down Resistance                                                    | $V_{(OVP)}$ = 2 V, I <sub>(FLT)</sub> = 5mA sinking                                                                                                                     | 45    | 82.3            | 145          | Ω       |  |  |  |  |  |

| I <sub>(FLT)</sub>        | FLT Input Leakage Current                                                   | $0~V \leqslant V_{(~FLT)} \leqslant 60~V$                                                                                                                               | - 100 | 0               | 100          | nA      |  |  |  |  |  |

| THERMAL SH                | IUT DOWN (TSD)                                                              |                                                                                                                                                                         |       |                 |              |         |  |  |  |  |  |

| T <sub>(TSD)</sub>        | TSD Threshold, rising                                                       |                                                                                                                                                                         |       | 155             |              | °C      |  |  |  |  |  |

| T <sub>(TSDhyst)</sub>    | TSD Hysteresis                                                              |                                                                                                                                                                         |       | 10              |              | °C      |  |  |  |  |  |

|                           |                                                                             | TPS26620, TPS26622, TPS26624                                                                                                                                            |       | Latch           |              |         |  |  |  |  |  |

|                           | Thermal Fault (Latch or Auto-Retry)                                         | TPS26621, TPS26623, TPS26625                                                                                                                                            |       | Auto -<br>retry |              |         |  |  |  |  |  |

# 7.6 Timing Requirements

$-40^{\circ}C \le T_A = T_J \le +125^{\circ}C$ ,  $V_{(IN)} = 24 V$ ,  $V_{(\overline{SHDN})} = 2 V$ ,  $R_{(ILIM)} = 267 k \Omega$ ,  $\overline{FLT} = OPEN$ ,  $C_{(OUT)} = 1 \mu F$ ,  $C_{(dVdT)} = OPEN$ . (All voltages referenced to GND, (unless otherwise noted))

|                             | PARAMETER                              | TEST CONDITIONS                                                                                                                                                                         | MIN NOM                                | MAX | UNIT |  |

|-----------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|------|--|

| IN and UVLO I               | NPUT                                   |                                                                                                                                                                                         |                                        |     |      |  |

|                             |                                        | UVLO $\uparrow$ (100 mV above V <sub>(UVLOR)</sub> ) to V <sub>(OUT)</sub> = 100 mV, C <sub>(dVdT)</sub> = Open                                                                         | 51                                     |     | μs   |  |

|                             | UVLO Turnon Delay                      | UVLO $\uparrow$ (100 mV above V <sub>(UVLOR)</sub> ) to V <sub>(OUT)</sub> = 100 mV, C <sub>(dVdT)</sub> > 4.7 nF, [C <sub>(dVdT)</sub> in nF]                                          | 51 +<br>27.4 x<br>C <sub>(dVdT)</sub>  |     | μs   |  |

| UVLO_t <sub>off(dly)</sub>  | UVLO Turnoff delay                     | UVLO↓ (100 mV below V <sub>(UVLOF)</sub> ) to FLT↓                                                                                                                                      | 6.14                                   |     | μs   |  |

| SHUTDOWN C                  | ONTROL INPUT ( SHDN)                   | 1                                                                                                                                                                                       |                                        | I   |      |  |

|                             |                                        | $\overline{\text{SHDN}}$ † to V <sub>(OUT)</sub> = 100 mV, C <sub>(dVdT)</sub> = Open                                                                                                   | 156                                    |     | μs   |  |

| t <sub>SD(dly)</sub>        | SHUTDOWN exit delay                    | $\overline{\text{SHDN}}$ † to V <sub>(OUT)</sub> = 100 mV, C <sub>(dVdT)</sub> > 4.7 nF, [C <sub>(dVdT)</sub> in nF]                                                                    | 156 +<br>27.4 x<br>C <sub>(dVdT)</sub> |     | μs   |  |

|                             | SHUTDOWN entry delay                   | SHDN ↓ (below SHUTF) to FLT ↓                                                                                                                                                           | 6.83                                   |     | μs   |  |

| OVER VOLTAG                 | SE PROTECTION INPUT (OVP)              | I                                                                                                                                                                                       |                                        | 1   |      |  |

|                             | OVP Exit delay                         | xit delay $\begin{array}{c} \text{OVP} \downarrow \ (20 \text{ mV below V}_{(\text{OVPF})}) \text{ to V}_{(\text{OUT})} = 100 \text{ mV}, \\ \text{TPS26620/21/24/25 Only} \end{array}$ |                                        |     |      |  |

| t <sub>OVP(dly)</sub>       | OVP Disable delay                      | OVP ↑ (20mV above V <sub>(OVPR)</sub> ) to FLT ↓ ,<br>TPS26620/21/24/25 Only                                                                                                            | 4.84                                   |     | μs   |  |

| CURRENT LIM                 | пт                                     | l l                                                                                                                                                                                     |                                        | I   |      |  |

| t <sub>CL(dly)</sub>        | Maximum duration in current limit      | $ I_{(ILIM)} < I_{(OUT)} < I_{(FAST-TRIP)}, V_{(IN)} - V_{(OUT)} < 2.6 V$                                                                                                               | 512                                    |     | ms   |  |

| t <sub>FAST-TRIP(dly)</sub> |                                        | $I_{(OUT)} > I_{(FAST-TRIP)}, V_{(IN)} - V_{(OUT)} = 2 V$                                                                                                                               | 1.5                                    |     | μs   |  |

|                             | Fast-Trip Comparator Delay             | $I_{(OUT)}$ > $I_{(FAST-TRIP)}, 4.5$ V < $V_{(IN)} \leqslant 6$ V, $V_{(IN)}$ – $V_{(OUT)} \geqslant 2.6$ V                                                                             | 1.4                                    |     | μs   |  |

|                             |                                        | $ _{(OUT)}$ > $ _{(FAST-TRIP)}$ , 6 V < $V_{(IN)}$ $\leqslant$ 57 V, $V_{(IN)}$ – $V_{(OUT)}$ $\geqslant$ 2.6 V                                                                         | 220                                    |     | ns   |  |

| REVERSE PRO                 | DTECTION COMPARATOR                    | · · · · · ·                                                                                                                                                                             |                                        |     |      |  |

|                             |                                        | $(V_{(IN)} - V_{(OUT)}) \downarrow (10 \text{ mV overdrive below} V_{(REVTH)})$ to internal FET turn OFF                                                                                | 15                                     |     |      |  |

|                             | Reverse Protection Comparator<br>Delay | (V <sub>(IN)</sub> <sup>-</sup> V <sub>(OUT)</sub> ) ↓ (1 V overdrive below V <sub>(REVTH)</sub> )<br>to internal FET turn OFF                                                          | 3.71                                   |     |      |  |

|                             |                                        | $(V_{(IN)}~^-~V_{(OUT)})\leqslant~^-$ 2.6 V to internal FET turn OFF                                                                                                                    | 0.31                                   |     | μs   |  |

|                             |                                        | $(V_{(IN)} - V_{(OUT)}) ↓$ (150 mV overdrive below $V_{(REVTH)}$ ) to FLT ↓                                                                                                             | 45                                     |     |      |  |

| t <sub>FWD(dly)</sub>       |                                        | $(V_{(IN)} - V_{(OUT)}) \uparrow (100 \text{ mV overdrive above} V_{(FWDTH)}) \text{ to } FLT \uparrow$                                                                                 | 63                                     |     |      |  |

| THERMAL SH                  | UTDOWN                                 | ·                                                                                                                                                                                       |                                        | I   |      |  |

| Retry Delay in<br>TSD       |                                        |                                                                                                                                                                                         | 512                                    |     | ms   |  |

| OUTPUT RAM                  | P CONTROL (dVdT)                       | ·                                                                                                                                                                                       |                                        | I   |      |  |

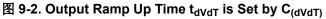

|                             | Quitaut Doma Time                      | $\overline{\text{SHDN}}$ $\uparrow$ to V <sub>(OUT)</sub> = 23.9 V, with C <sub>(dVdT)</sub> = 22 nF                                                                                    | 11                                     |     |      |  |

| t <sub>dVdT</sub>           | Output Ramp Time                       | $\overline{\text{SHDN}}$ $\uparrow$ to V <sub>(OUT)</sub> = 23.9 V, with C <sub>(dVdT)</sub> = open                                                                                     | 0.664                                  |     | ms   |  |

| FAULT FLAG (                | FLT)                                   | · ·                                                                                                                                                                                     |                                        |     |      |  |

# 7.6 Timing Requirements (continued)

$-40^{\circ}C \leq T_{A} = T_{J} \leq +125^{\circ}C$ ,  $V_{(IN)} = 24$  V,  $V_{(\overline{SHDN})} = 2$  V,  $R_{(ILIM)} = 267$  k  $\Omega$ ,  $\overline{FLT} = OPEN$ ,  $C_{(OUT)} = 1$   $\mu$ F,  $C_{(dVdT)} = OPEN$ . (All voltages referenced to GND, (unless otherwise noted))

|                     | PARAMETER         | TEST CONDITIONS                                                           | MIN | NOM                                   | MAX | UNIT |

|---------------------|-------------------|---------------------------------------------------------------------------|-----|---------------------------------------|-----|------|

| t <sub>PGOODF</sub> |                   | Falling edge                                                              |     | 875                                   |     | μs   |

|                     |                   | Rising edge, C <sub>(dVdT)</sub> = Open                                   |     |                                       |     | ms   |

| t <sub>PGOODR</sub> | GOODR PGOOD Delay | Rising edge, $C_{(dVdT)} > 4.7 \text{ nF}$ , $[C_{(dVdT)} \text{ in nF}]$ |     | 750 +<br>573 x<br>C <sub>(dVdT)</sub> |     | μs   |

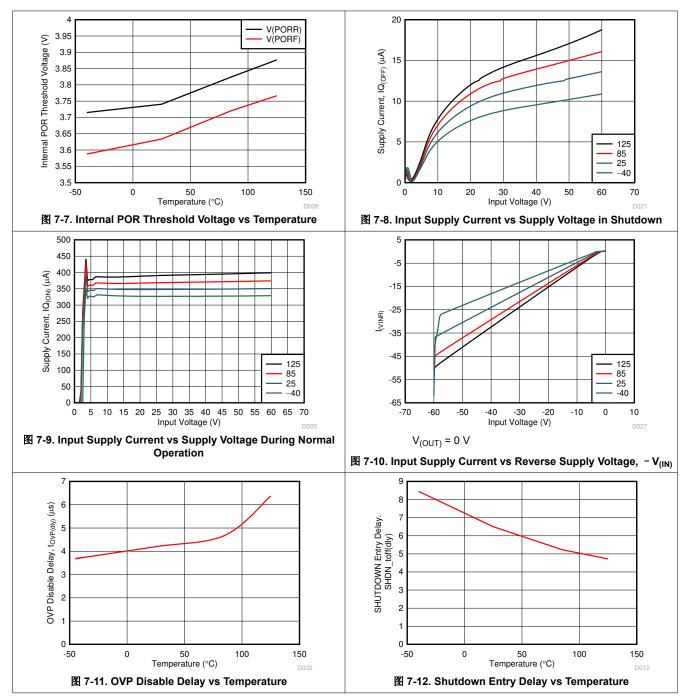

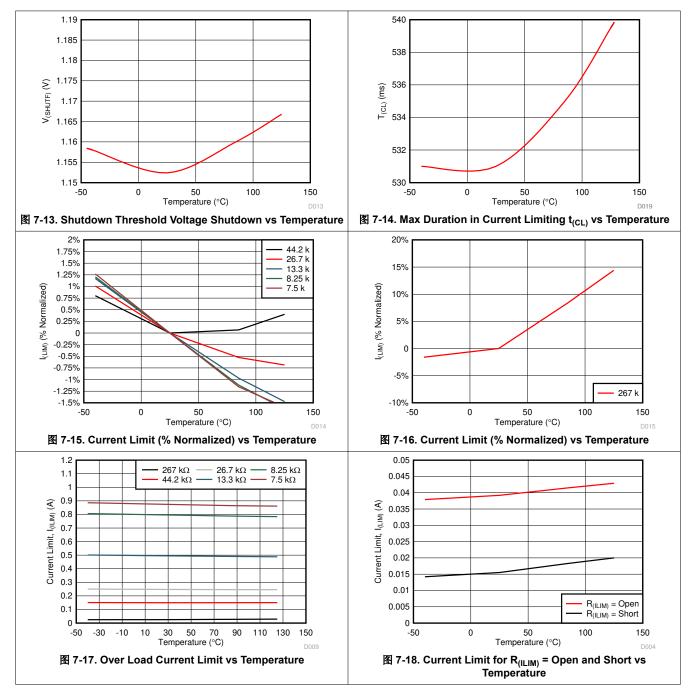

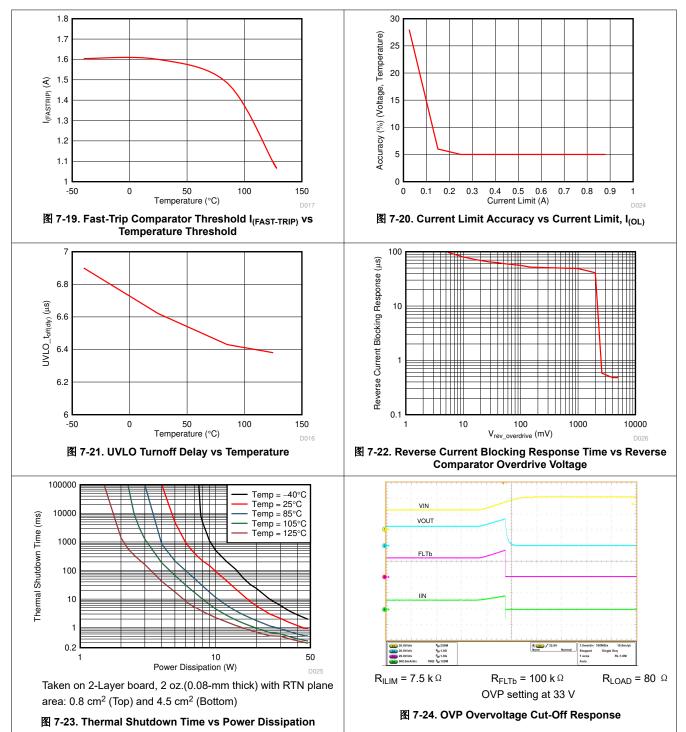

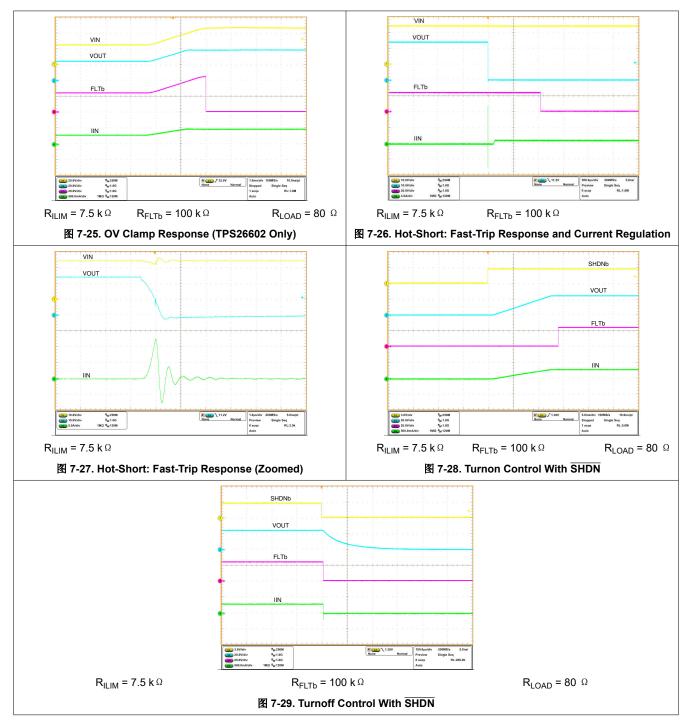

# 7.7 Typical Characteristics

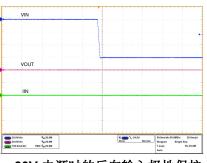

图 8-1. Timing Waveforms

# 9 Detailed Description

### 9.1 Overview

The TPS2662x is a family of high voltage industrial eFuses with integrated back-to-back MOSFETs and enhanced built-in protection circuitry. The device provides robust protection for all systems and applications powered from 4.5 V to 60 V. The device can withstand ±60-V positive and negative supply voltages without damage. The device features fully integrated reverse polarity protection and require zero additional power components. For hot-pluggable boards, the device provides hot-swap power management with in-rush current control. Load, source, and device protections are provided with many programmable features including overcurrent, overvoltage, undervoltage. The precision overcurrent limit (±5% at 880 mA) helps to minimize over design of the input power supply, while the fast response short-circuit protection 220 ns (typical) immediately isolates the faulty load from the input supply when a short circuit is detected.

The internal robust protection control blocks of the TPS2662x along with its  $\pm$ 60-V rating helps to simplify the system designs for the surge compliance ensuring complete protection of the load and the device. TPS2662x devices are immune to noise tests like Electrical Fast Transients that are common in industrial applications and simplifies the system design that require criterion-A performance during this test.

The device provides precise monitoring of voltage bus for brown-out and overvoltage conditions and asserts fault signal for the downstream system. The TPS2662x monitor functions threshold accuracy of  $\pm 3\%$  ensures tight supervision of the supply bus, eliminating the need for a separate supply voltage supervisor chip.

The device monitors  $V_{(IN)}$  and  $V_{(OUT)}$  to provide true reverse current blocking when a reverse condition or input power failure condition is detected.

# 9.2 Functional Block Diagram

# 9.3 Feature Description

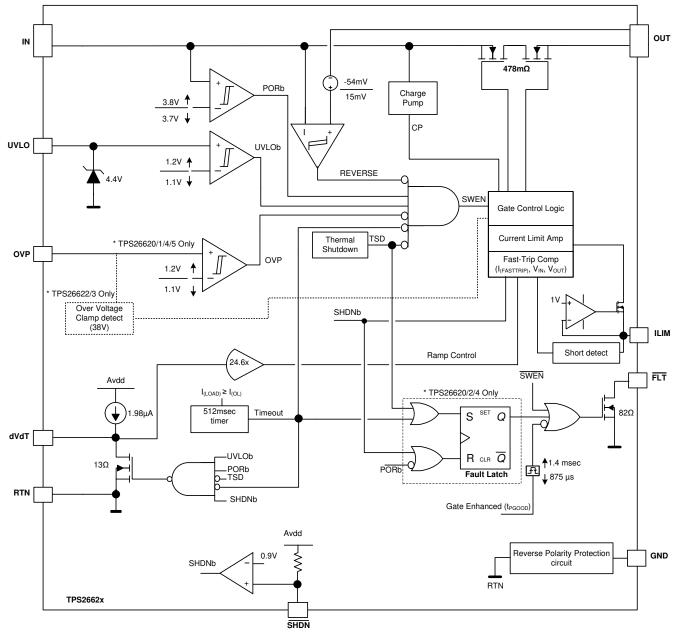

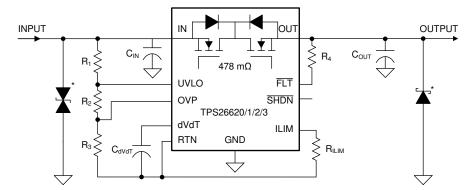

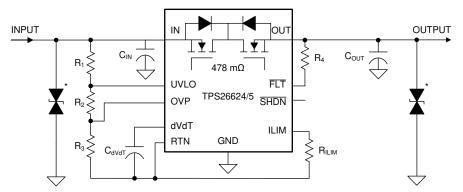

#### 9.3.1 Undervoltage Lockout (UVLO)

When the voltage at UVLO pin falls below  $V_{(UVLOF)}$  during input power fail or input undervoltage fault, the internal FET quickly turns off and FLT is asserted. The UVLO comparator has a hysteresis of 100 mV. To set the input UVLO threshold, connect a resistor divider network from IN supply to UVLO terminal to RTN as shown in  $\mathbb{R}$  9-1.

图 9-1. UVLO and OVP Thresholds Set by R<sub>1</sub>, R<sub>2</sub> and R<sub>3</sub>

If the Undervoltage Lockout function is not needed, the UVLO terminal must be connected to the IN terminal with a 1-M $\Omega$  resistor. UVLO pin is 5-V rated and this resistor limits the UVLO pin current to < 60  $\mu$ A. The UVLO terminal must not be left floating.

#### 9.3.2 Overvoltage Protection (OVP)

The TPS2662x family incorporate circuitry to protect the system during overvoltage conditions. The TPS26620, TPS26621, TPS26624 and TPS26625 feature overvoltage cut off functionality. A voltage more than  $V_{(OVPR)}$  on OVP pin turns off the internal FET and protects the downstream load. To program the OVP threshold externally, connect a resistor divider from IN supply to OVP terminal to RTN as shown in 🕅 9-1. If the overvoltage feature is not to be used then connect OVP terminal to RTN directly and ensure  $V_{IN}$  is not exceeded beyond OVP<sub>MAX</sub>.

The TPS26622 and TPS26623 feature an internally fixed 38-V overvoltage clamp (V<sub>OVC</sub>) functionality. The OVP terminal of these devices must be connected to the RTN terminal directly. These devices clamp the output voltage to V<sub>OVC</sub>, when the input voltage exceeds 38 V. During the output voltage clamp operation, the power dissipation in the internal MOSFET is  $P_D = (V_{IN} - V_{OVC}) \times I_{OUT}$ . Excess power dissipation for prolonged period can make the device to enter into thermal shutdown. If the device temperature does not reach T<sub>(TSD)</sub>, the device turns off the internal FETs after a delay of t<sub>CL\_Dly</sub>. After the internal FETs are turned off, TPS26622 latches-off and TPS26623 device auto-retries.  $\boxed{8}$  7-25 illustrates the overvoltage clamp functionality.

#### 9.3.3 Hot Plug-In and Inrush Current Control

The devices are designed to control the inrush current upon insertion of a card into a live backplane or other *hot*power source. This design limits the voltage sag on the backplane's supply voltage and prevents unintended resets of the system power. The controlled start-up also helps to eliminate conductive and radiative interferences. An external capacitor connected from the dVdT pin to RTN defines the slew rate of the output voltage at power-on as shown in <u>8</u> 9-2 and Figure 9-3.

(1)

方程式 1 governs slew rate at start-up.

$$I_{(dVdT)} = \left(\frac{C_{(dVdT)}}{Gain_{(dVdT)}}\right) \times \left(\frac{dV_{(OUT)}}{dt}\right)$$

where

- I<sub>(dVdT)</sub> = 1.98 μA (typical) dV (OUT)

- dt = Desired output slew rate

- Gain<sub>(dVdT)</sub> = dVdT to V<sub>OUT</sub> gain = 24.6

The total ramp time ( $t_{dVdT}$ ) of  $V_{(OUT)}$  for 0 to  $V_{(IN)}$  can be calculated using  $\overline{\beta}$ 程式 2.

$t_{dVdT} = 20.5 \times 10^3 \times V_{(IN)} \times C_{(dVdT)}$ <sup>(2)</sup>

图 9-3. Hot Plug-In and Inrush Current Control at 24-V Input

# 9.3.4 Reverse Polarity Protection

# 9.3.4.1 Input Side Reverse Polarity Protection

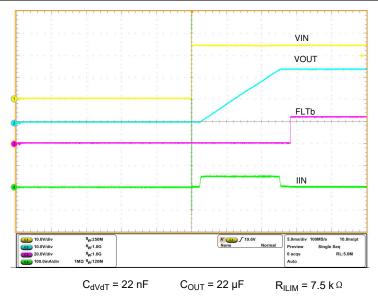

TPS2662x eFuses feature fully integrated input side reverse polarity protection. The internal FETs of the eFuse turn OFF during the input reverse polarity event and protect the downstream loads from negative supply voltages that can appear due to field mis-wiring on the input power terminals. Figure 9-4 illustrates the reverse input polarity protection functionality.

图 9-4. Reverse Input Supply Protection at - 60 V

# 9.3.4.2 Output Side Reverse Polarity Protection

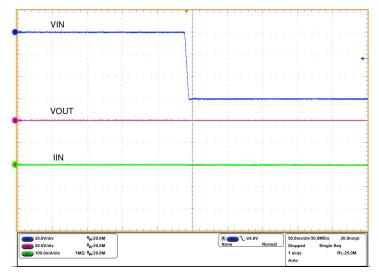

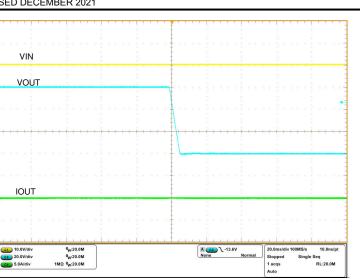

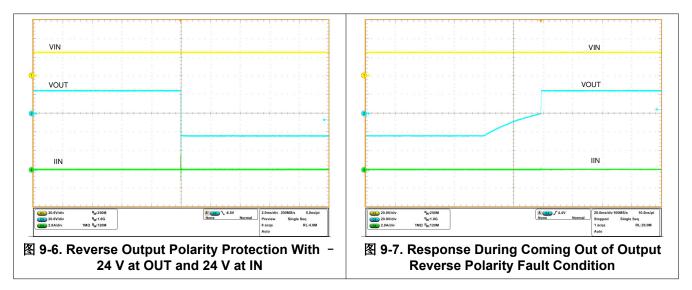

The TPS26624 and TPS26625 eFuses feature fully integrated input as well as output reverse polarity protection. The internal FETs of the eFuse turn OFF during the output reverse polarity event and protects the upstream circuits from negative voltage that can appear at the output of the eFuse due to field miswiring at the output side with an external isolated power supplies.  $\boxed{8}$  9-5 illustrates the performance during output side reverse polarity event with V<sub>(IN)</sub> un-powered and  $\boxed{8}$  9-6 illustrates the performance with V<sub>(IN)</sub> powered.  $\boxed{8}$  9-7 illustrates the output recovery performance after the reverse polarity is removed.

图 9-5. Reverse Output Polarity Protection With -60 V at OUT and VIN = 0 V

#### 9.3.5 Overload and Short-Circuit Protection

The device monitors the load current by sensing the voltage across the internal sense resistor. The FET current is monitored during start-up and normal operation.

#### 9.3.5.1 Overload Protection

Connect a resistor across ILIM to RTN to program the over load current limit  $I_{(OL)}$ . During overload conditions, the device regulates the current through it at  $I_{(OL)}$  programmed by the  $R_{(ILIM)}$  resistor as shown in 方程式 3 for a maximum duration of  $t_{CL(dly)}$ .

$$I_{OL} = \frac{6.636}{R_{ILIM}}$$

where

- I<sub>(OL)</sub> is the overload current limit in Ampere

- R<sub>(ILIM)</sub> is the current limit resistor in k Ω

During the current limit operation the output voltage droops and this can cause the device to hit the thermal shutdown threshold  $T_{(TSD)}$  before  $t_{CL(dly)}$  time. After the thermal shutdown threshold is hit or  $t_{CL(dly)}$  is elapsed,

(3)

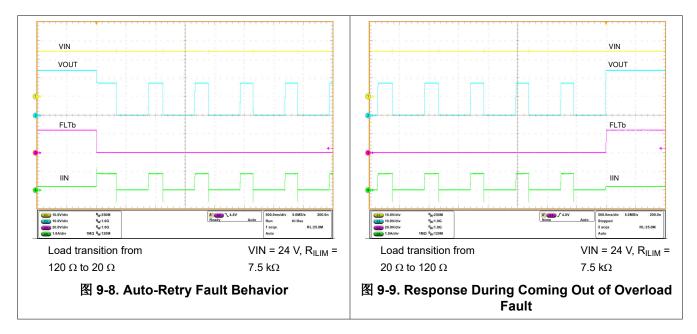

the internal FETs of TPS2662x turns OFF. FETs in TPS26620, TPS26622 and TPS26624 remain OFF and latched. To reset the latch, cycle the SHDN or UVLO, or recycle the V<sub>IN</sub>. TPS26621, TPS26623 and TPS26625 commence an auto-retry cycle after a retry time of 512 msec. The internal FETs turn back on in dVdT mode after this retry time. If the overload still exists, then the device regulates the current at programmed current limit, I<sub>(OL)</sub>.  $t_{CL(dly)}$  is the maximum duration for current limiting and estimated as  $t_{CL(dly)}$  = 512 ms + [3.3 × C<sub>dVdT</sub> / 2  $\mu$  A] (C<sub>dVdT</sub> in nF).

#### 9.3.5.2 Short-Circuit Protection

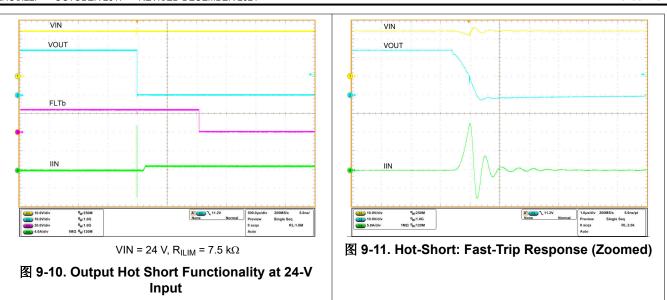

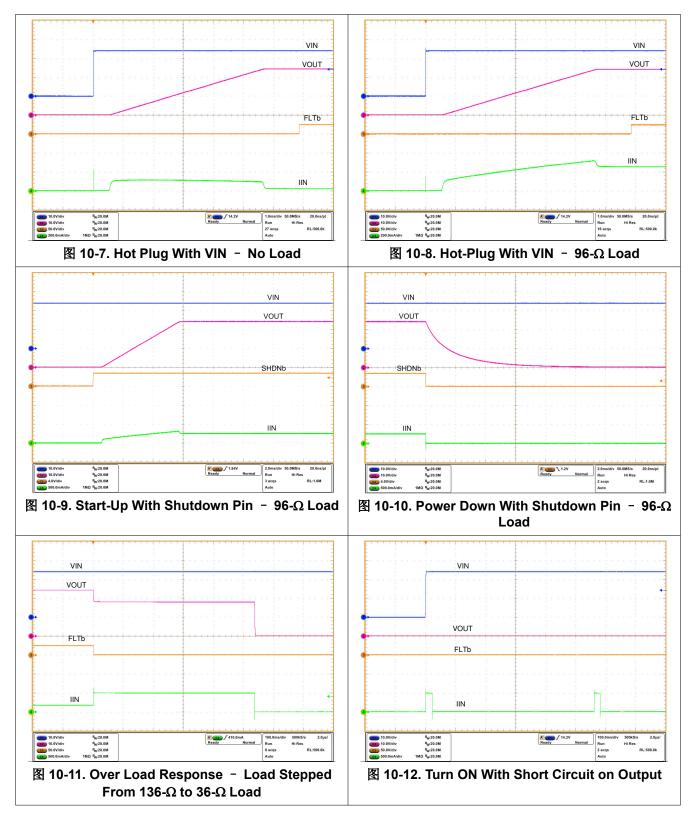

During a transient output short circuit event, the current through the device increases rapidly. As the current-limit amplifier cannot respond quickly to this event due to its limited bandwidth, the device incorporates a fast-trip comparator. The fast-trip comparator architecture is designed for fast turn OFF ( $t_{FAST-TRIP(dly)} = 220$  ns (typical)) of the internal FET during an output short circuit event. The fast-trip threshold is internally set to  $I_{(FAST-TRIP)}$ . The fast-trip circuit holds the internal FET off for only a few microseconds, after which the device functions similar to slowly, allowing the current-limit loop to regulate the output current to  $I_{(OL)}$ . Then the device functions similar to the overload condition. Figure 9-10 and Figure 9-11 illustrate the behavior of the system during output short-circuit condition.

TPS2662 ZHCSI22F - OCTOBER 2017 - REVISED DECEMBER 2021

The fast-trip comparator architecture has a supply line noise immunity resulting in a robust performance in noisy environments. This feature is achieved by controlling the turn OFF time of the internal FET based on the differential voltage across  $V_{(IN)}$  and  $V_{(OUT)}$  after the current through the device exceeds  $I_{(FAST-TRIP)}$ . Higher the voltage difference  $V_{(IN)} - V_{(OUT)}$ , faster the turn OFF time,  $t_{FAST-TRIP(dly)}$ .

#### 9.3.5.2.1 Start-Up With Short-Circuit On Output

When the device is started with short-circuit on the output, it limits the load current to the current limit,  $I_{(OL)}$ , and functions similar to the overload condition. Figure 9-12 illustrates the function of the device in this condition. This feature helps in quick isolation of the fault and ensures stability of the DC bus.

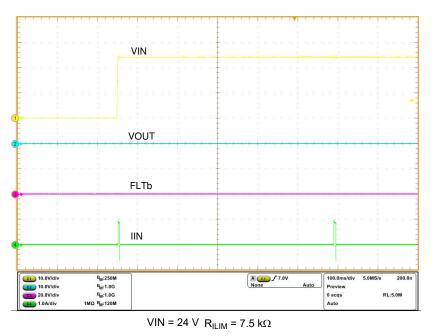

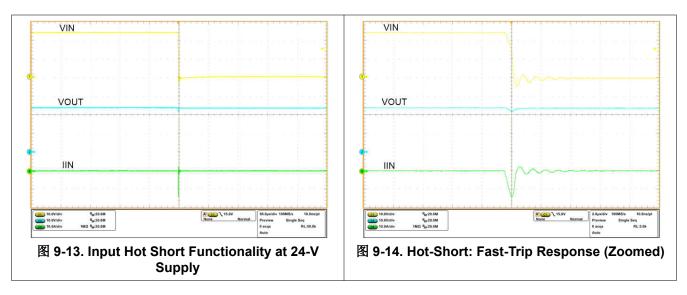

#### 9.3.6 Reverse Current Protection

The device monitors  $V_{(IN)}$  and  $V_{(OUT)}$  to provide true reverse current blocking when a reverse condition or input power failure condition is detected. The reverse comparator turns OFF the internal FET within 310 ns (typical) as

FXAS

**NSTRUMENTS**

www.ti.com.cn

soon as  $V_{(IN)} - V_{(OUT)}$  falls below - 2.6 V. The reverse comparator turns on within 63 µs (typical) after the differential forward voltage  $V_{(IN)} - V_{(OUT)}$  exceeds 115 mV.  $\mathbb{E}$  9-13 and  $\mathbb{E}$  9-14 illustrate the behavior of the system during input hot short circuit condition.

The reverse comparator architecture has a supply line noise immunity resulting in a robust performance in noisy environments. This feature is achieved by controlling the turn OFF time of the internal FET based on the over-drive differential voltage  $V_{(IN)} - V_{(OUT)}$  over  $V_{(REVTH)}$ . Higher the over-drive, faster the turn OFF time,  $t_{REV(dly)}$ . Figure 7-22 shows the reverse current blocking response time versus over-drive voltage.

#### 9.3.7 FAULT Response

The FLT open-drain output asserts (active low) under the following conditions:

- · Fault events such as undervoltage, overvoltage, over load, reverse current and thermal shutdown conditions

- The device enters low current shutdown mode when SHDN is pulled low

- During start-up when the internal FET GATE is not fully enhanced

The device is designed to eliminate false reporting by using an internal *de-glitch* circuit for fault conditions without the need for an external circuitry.

The FLT signal can also be used as a Power Good indicator to the downstream loads like DC/DC converters. An internal Power Good (PGOOD) signal is ORd with the fault logic. During start-up, when the device is operating in dVdT mode, PGOOD and FLT it remains low and is de-asserted after the dVdT mode is completed and the internal FET is fully enhanced. The PGOOD signal has deglitch time incorporated to ensure that internal FET is fully enhanced before heavy load is applied by the downstream converters. Rising deglitch delay is determined by  $t_{PGOOD(degl)} = Maximum \{(750 + 573 \times C_{(dVdT)}), t_{PGOODR}\}$ , where  $C_{(dVdT)}$  is in nF and  $t_{PGOOD(degl)}$  is in  $\mu$ s. FLT can be left open or connected to RTN when not used.  $V_{(IN)}$  falling below 3.4 V resets FLT.

#### 9.3.8 IN, OUT, RTN, and GND Pins

TI recommends a ceramic bypass capacitor close to the device from IN to GND to alleviate bus transients. The recommended input operating voltage range is 4.5 to 60 V.  $V_{(OUT)}$ , in the ON condition, is calculated using  $\pi$   $\pm$  4.

$$V(OUT) = V(IN) - (RON \times I(OUT))$$

Where,

• RON is the total ON resistance of the internal FETs.

23

Submit Document Feedback

(4)

GND pin must be connected to the system ground. RTN is the device ground reference for all the internal control blocks. Connect the TPS2662x family support components:  $R_{(ILIM)}$ ,  $C_{(dVdT)}$  and resistors for UVLO and OVP with respect to the RTN pin. Internally, the device has reverse input polarity protection block between RTN and the GND terminal. Connecting RTN pin to GND pin disables the reverse polarity protection feature and the TPS2662x gets permanently damaged when operated under this fault event.

### 9.3.9 Thermal Shutdown

The device has a built-in overtemperature shutdown circuitry designed to protect the internal FETs, if the junction temperature exceeds  $T_{(TSD)}$ . After the thermal shutdown event, depending upon the mode of fault response, the device either latches off or commences an auto-retry cycle 512 ms after  $T_J < (T_{(TSD)} - 13.5^{\circ}C)$ . During the thermal shutdown, the fault pin FLT pulls low to indicate a fault condition.

# 9.4 Device Functional Modes

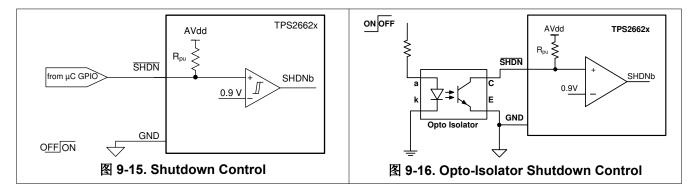

# 9.4.1 Low Current Shutdown Control (SHDN)

The internal FETs and the load current can be switched off by pulling the SHDN pin below 0.9-V threshold with a micro-controller GPIO pin or can be controlled remotely with an opto-isolator device as shown in 8 9-15 and 8 9-16. The device quiescent current reduces to 10  $\mu$  A (typical) in SHUTDOWN state. To assert SHDN low, the pull down must sink at least 10  $\mu$ A at 400 mV. To enable the device, SHDN must be pulled up to at least 1.8 V. After the device is enabled, the internal FETs turn on with dVdT mode.

# **10** Application and Implementation

备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客 户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

### **10.1 Application Information**

The TPS2662x family is an industrial eFuse, typically used for Hot-Swap and power rail protection applications. The device operates from 4.5 V to 60 V with programmable current limit, overvoltage, undervoltage and reverse polarity protections. The device aids in controlling inrush current and provides robust protection against reverse current and field miss-wiring conditions for systems such as PLC I/O modules and sensor power supplies. The device also provides robust protection for multiple faults on the system rail.

The *Detailed Design Procedure* section can be used to select component values for the device.

Alternatively, the *WEBENCH*<sup>®</sup> software can be used to generate a complete design. The WEBENCH<sup>®</sup> software uses an iterative design procedure and accesses a comprehensive database of components when generating a design. Additionally, a spreadsheet design tool, *TPS2662 Design Calculator*, is available in the web product folder.

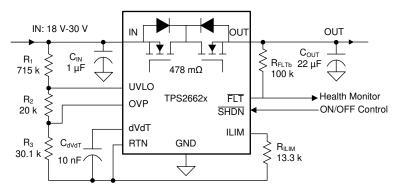

### **10.2 Typical Application**

图 10-1. 24-V, 500-mA eFuse Input Protection Circuit for PLC I/O Module

#### **10.2.1 Design Requirements**

$\frac{10-1}{10}$  shows the design requirements for TPS2662x.

| 表 10-1. Design Requirements |

|-----------------------------|

|-----------------------------|

|                    | DESIGN PARAMETER               | EXAMPLE VALUE |

|--------------------|--------------------------------|---------------|

| V <sub>(IN)</sub>  | Typical input voltage          | 24 V          |

| V <sub>(UV)</sub>  | Undervoltage lockout set point | 18 V          |

| V <sub>(OV)</sub>  | Overvoltage cutoff set point   | 30 V          |

| T <sub>(SU)</sub>  | Load during start-up           | 96 Ω          |

| I <sub>(LIM)</sub> | Current limit                  | 500 mA        |

| C <sub>(OUT)</sub> | Load capacitance               | 22 µF         |

| T <sub>A</sub>     | Maximum ambient temperature    | 125°C         |

#### **10.2.2 Detailed Design Procedure**

#### 10.2.2.1 Step-by-Step Design Procedure

To begin the design process, the designer must know the following parameters:

- Input operating voltage range

- Maximum output capacitance

- Maximum current limit

- Load during start-up

- Maximum ambient temperature

This design procedure below seeks to control junction temperature of the device in both steady state and start-up conditions by proper selection of the output ramp-up time and associated support components. The designer can adjust this procedure to fit the application and design criteria.

#### 10.2.2.2 Programming the Current Limit Threshold R<sub>(ILIM)</sub> Selection

The R<sub>(ILIM)</sub> resistor at the ILIM pin sets the over load current limit. the current limit can be set using 方程式 5.

$$R_{\rm ILIM} = \frac{6.636}{I_{\rm LIM}} = 13.27 \, \rm k\Omega$$

(5)

where

• I<sub>LIM</sub> = 500 mA

Choose the closest standard 1% resistor value:  $R_{(ILIM)}$  = 13.3 k  $\Omega$ .

#### 10.2.2.3 Undervoltage Lockout and Overvoltage Set Point

The undervoltage lockout (UVLO) and overvoltage trip point are adjusted using an external voltage divider network of  $R_1$ ,  $R_2$  and  $R_3$  connected between IN, UVLO, OVP and RTN pins of the device. The values required for setting the undervoltage and overvoltage are calculated by solving 5 Rt 6 and 5 Rt 7.

$$V(OVPR) = \frac{R_3}{R_1 + R_2 + R_3} \times V(OV)$$

(6)

$$V(UVLOR) = \frac{R_2 + R_3}{R_1 + R_2 + R_3} \times V(UV)$$

(7)

For minimizing the input current drawn from the power supply  $\{I_{(R123)} = V_{(IN)} / (R_1 + R_2 + R_3)\}$ , TI recommends to use higher value resistance for  $R_1$ ,  $R_2$  and  $R_3$ .

However, the leakage current due to external active components connected at resistor string can add error to these calculations. So, the resistor string current,  $I(R_{123})$  must be chosen to be 20 times greater than the leakage current of UVLO and OVP pins.

From the device electrical specifications,  $V_{(OVPR)} = 1.19$  V and  $V_{(UVLOR)} = 1.19$  V. From the design requirements,  $V_{(OV)}$  is 30 V and  $V_{(UV)}$  is 18 V. To solve the equation, first choose the value of  $R_3 = 30.1$  kΩ and use f $R_{\pm}$  6 to solve for ( $R_1 + R_2$ ) = 728.7 kΩ. Use f $R_{\pm}$  7 and value of ( $R_1 + R_2$ ) to solve for  $R_2 = 20.05$  kΩ and finally  $R_1 = 708.6$  kΩ.

Choose the closest standard 1% resistor values:  $R_1 = 715 \text{ k}\Omega$ ,  $R_2 = 20 \text{ k}\Omega$ , and  $R_3 = 30.1 \text{ k}\Omega$ .

#### 10.2.2.4 Setting Output Voltage Ramp Time—(t<sub>dVdT</sub>)

For a successful design, the junction temperature of the device must be kept below the absolut -maximum rating during dynamic (start-up) and steady state conditions. The dynamic power dissipation is often an order magnitude greater than the steady state power dissipation. It is important to determine the right start-up time and

the inrush current limit for the system to avoid thermal shutdown during start-up with and without load. The rampup capacitor  $C_{(dVdT)}$  is calculated considering the two possible cases:

#### 10.2.2.4.1 Case 1: Start-Up Without Load—Only Output Capacitance C<sub>(OUT)</sub> Draws Current During Start-Up

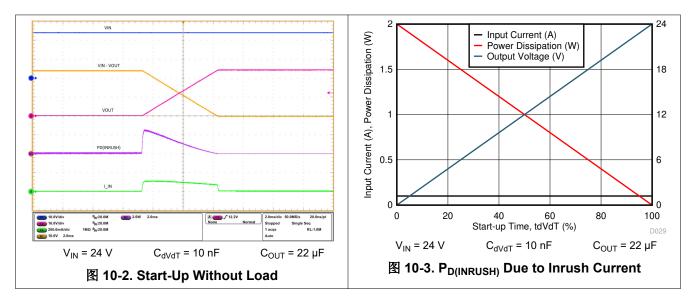

During start-up, as the output capacitor charges, the voltage difference across the internal FET decreases, and the power dissipation decreases. Typical ramp-up of the output voltage, inrush current and instantaneous power dissipated in the device during start-up are shown in Figure 10-2. The average power dissipated in the device during start-up is equal to the area of triangular plot (red curve in Figure 10-3) averaged over  $t_{dVdT}$ .

The inrush current is determined as shown in 方程式 8.

$$I = C \times \frac{dV}{dT} \ge I(\text{INRUSH}) = C(\text{OUT}) \times \frac{V(\text{IN})}{t dV dT}$$

(8)

Average power dissipated during start-up is given by 方程式 9.

$P\text{D}(\text{INRUSH}) = 0.5 \times V(\text{IN}) \times I(\text{INRUSH})$

方程式 9 assumes that the load does not draw any current until the output voltage reaches its final value.

#### 10.2.2.4.2 Case 2: Start-Up With Load —Output Capacitance C(OUT) and Load Draws Current During Start-Up

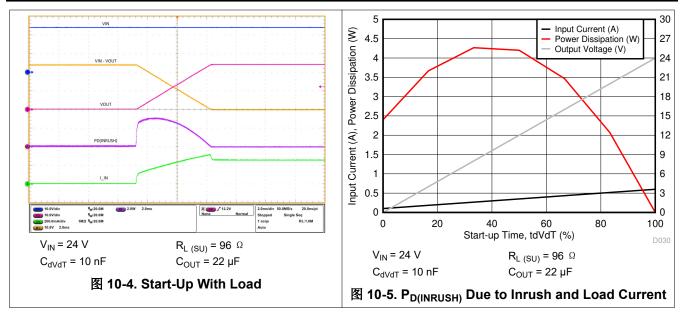

When the load draws current during the turn-on sequence, additional power is dissipated in the device. Considering a resistive load RL(SU) during start-up, typical ramp-up of output voltage, Figure 10-4 shows load current and the instantaneous power dissipation in the device. Figure 10-5 plots Instantaneous power dissipation with respect to time.

(9)

The additional power dissipation during start-up is calculated using 方程式 10.

$$PD(LOAD) = \frac{1}{6} \times \frac{V(IN)^2}{RL(SU)}$$

(10)

Total power dissipated in the device during start-up is given by 方程式 11.

PD(STARTUP) = PD(INRUSH) + PD(LOAD)(11)

Total current during start-up is given by 方程式 12.

$$\mathbf{I}(\text{STARTUP}) = \mathbf{I}(\text{INRUSH}) + \mathbf{I}L(t)$$

For the design example under discussion,

Select the inrush current  $I_{(INRUSH)} = 0.1$  A and  $t_{dVdT}$  calculated using  $\overline{5}$  Register that 3 is 5.28 ms.

For a given start-up time,  $C_{dVdT}$  capacitance value calculated using 方程式 2 is 10.7 nF for  $t_{dVdT}$  = 5.28 ms and  $V_{IN}$  = 24 V.

Choose the closest standard value: 10.0 nF and 16-V capacitor.

(12)

The inrush power dissipation due to output capacitor alone is calculated using  $\overline{\beta}$  程式 9 and it is 1.2 W. Considering the start-up with 96- $\Omega$  load, the additional power dissipation calculated using  $\overline{\beta}$  程式 10 is 1 W. The total device power dissipation during start-up is 2.2 W

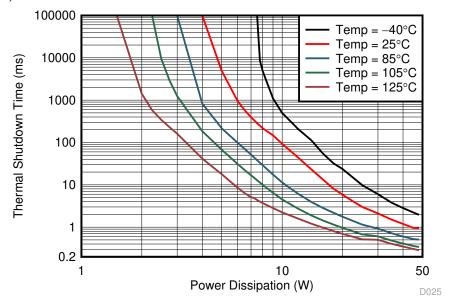

The power dissipation with or without load, for a selected start-up time must not exceed the thermal shutdown limits as shown in  $\boxed{8}$  10-6.

From the thermal shutdown limit graph, at  $T_A = 125^{\circ}C$ , thermal shutdown time for 2.2 W is close to 580 ms. It is safe to have a minimum 30% margin to allow for variation of the system parameters such as load, component tolerance, input voltage and layout. Selected 10-nF  $C_{dVdT}$  capacitor and 5.28-ms start-up time ( $t_{dVdT}$ ) are well within the limit for successful start-up with 96- $\Omega$  load.

Higher value C<sub>(dVdT)</sub> capacitor can be selected to further reduce the power dissipation during start-up.

图 10-6. Thermal Shutdown Time vs Power Dissipation

#### 10.2.2.4.3 Support Component Selections - R<sub>FLT</sub> and C<sub>(IN)</sub>

The R<sub>FLT</sub> Absolute Maximum Ratings serves as pull-up for the open-drain fault output. The current sink by this pin must not exceed 10 mA (see the Absolute Maximum Ratings table). TI recommends typical resistance value in the range of 10 k $\Omega$  to 100 k $\Omega$  for R<sub>FLT</sub>. The C<sub>IN</sub> is a local bypass capacitor to suppress noise at the input. TI recommends typical capacitance value in the range of 0.1 µF to 1 µF for C<sub>(IN)</sub>.

#### 10.2.3 Application Curves

# 10.3 System Examples

#### 10.3.1 Field Supply Protection in PLC, DCS I/O Modules

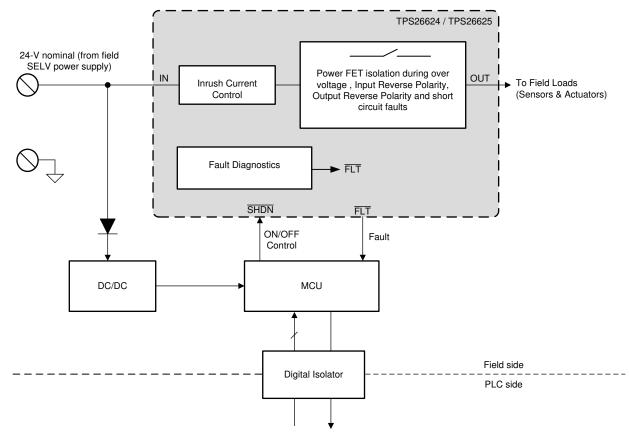

图 10-13. Power Delivery Circuit Block Diagram in I/O Modules

The PLC or Distributed Control System (DCS) I/O modules are often connected to an external field power supply to support higher power requirements of the field loads like sensors and actuators. Power-supply faults or miswiring can damage the loads or cause the loads not to operate correctly. The TPS26624 and TPS26625 can be used as a front end protection circuit to protect and provide stable supply to the field loads. Undervoltage, overvoltage, and input and output side reverse polarity protection features of these devices prevent the loads to experience voltages outside the operating range, which can permanently damage the loads.

Field power supply is often connected to multiple I/O modules that can deliver more current than a single I/O module can handle. Overcurrent protection scheme of the TPS2662x family limits the current from the power supply to the module so that the maximum current does not rise above what the board is designed for. Fast short-circuit protection scheme isolates the faulty load from the field supply quickly and prevents the field supply to dip and cause interrupts in the other I/O modules connected to the same field supply. High accurate (±5% at 0.88 A) current limit facilitates more I/O modules to be connected to field supply. Fault indication (FLT) features facilitate continuous load monitoring.

The TPS26624 and TPS26625 also acts as a smart diode with protection against reverse current during output side miswiring. Reverse current can potentially damage the field power supply and cause the I/O modules to run hot or can cause permanent damage.

If the field power supply is connected in reverse polarity on the input side (which is not unlikely as field power supplies are usually connected with screw terminals), field loads can permanently get damaged due to the reverse voltage. Also, during the installation the field power supply can be miswired on the output side instead of on the input side which can damage the upstream power supply and electronics. The input and output reverse polarity protection feature of the TPS26624 and TPS26625 prevents the reverse voltage to appear at the load side as well as supply side offering complete system protection during field miswiring.

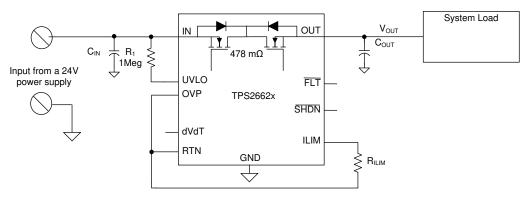

#### 10.3.2 Simple 24-V Power Supply Path Protection

With the TPS2662x, a simple 24-V power supply path protection can be realized using a minimum of four external components as shown in the schematic diagram in 🕅 10-14. The external components required are: a 1Meg  $\Omega$  R<sub>(1)</sub> resistor across IN and UVLO pins, a R<sub>(ILIM)</sub> resistor to program the current limit, C<sub>(IN)</sub> and C<sub>(OUT)</sub> capacitors.

图 10-14. TPS2662x Configured for a Simple 24-V Supply Path Protection

Protection features with this configuration include:

- Load and device protection from reverse input polarity fault down to 60 V

- Upstream supply and device protection from reverse output polarity fault down to (60 VIN) V with TPS26624 and TPS26625 variants

- Protection from 60 V from the external SELV supply: overvoltage Clamp at 38 V with TPS26622 and TPS26623 variants

- · Inrush current control with 24 V and 660-µs output voltage slew rate

- Reverse Current Blocking

- Accurate current limiting with auto-retry with TPS26621, TPS26623, TPS26625 variants

- Accurate current limiting with latch-off with TPS26620, TPS26622, TPS26624 variants

#### 10.3.3 Power Stealing in Smart Thermostat