Support & ക training

ZHCSMU6B - AUGUST 2020 - REVISED SEPTEMBER 2021

TPS37-Q1 适用于汽车的具有可编程检测和复位延迟功能的宽 VIN 65V 双通道过 压和欠压(OV和UV)检测器

### 1 特性

ŦF

**TEXAS**

**INSTRUMENTS**

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 1: 40°C 至 +125°C 环境工作 温度范围 T<sub>A</sub>

- 器件 HBM ESD 分类等级 2

- 器件 CDM ESD 分类等级 C7B

- 宽电源电压范围:2.7V至65V

- SENSE 和 RESET 引脚为 65V 等级

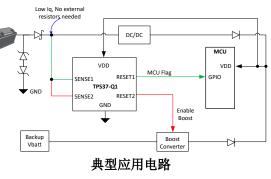

- 低静态电流:1µA(典型值)

- 灵活而广泛的电压阈值选项

- 表 13-1

- 2.7V 至 36V (最高精度 1.5%)

- 800mV 选项 (最高精度 1%)

- 内置迟滞 (V<sub>HYS</sub>)

- 百分比选项: 2% 至 13% (阶跃 1%)

- 固定选项:V<sub>TH</sub> < 8V = 0.5V、1V、1.5V、 2V、2.5V

- 可编程复位延时时间

- 10nF = 12.8ms 10 µ F = 12.8s

- 可编程检测延时时间

- 10nF = 1.28ms、10 μ F = 1.28s

- 手动复位 (MR) 特性

- 输出复位锁存特性

- 输出拓扑:开漏或推挽

### 2 应用

- 远程信息处理控制单元 •

- 紧急呼叫系统 ٠

- 音频放大器

- 音响主机和组合仪表 •

- 传感器融合和摄像头

- 车身控制模块

### 3 说明

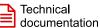

TPS37-Q1 是一款 65V 输入电压检测器,

IDD 为1µA,精度为1%,并具有10µs 的快速检测 时间。该器件可直接连接到

12V/24V 汽车电池系统,用于持续监测过压 (OV) 和欠 压 (UV) 条件;由于使用内部电阻分压器,它的总体解 决方案尺寸非常小。由于提供了广泛的迟滞电压选项, 因此可以忽略冷启动、启停和各种汽车电池电压瞬变。 SENSE 引脚上的内置迟滞可在监测电源电压轨时防止 出现错误的复位信号。

通过单独的 VDD 和 SENSE 引脚,可实现高可靠性汽 车系统所需的冗余,并且 SENSE 可以监控比 VDD 更 高和更低的电压。SENSE 引脚的高阻抗输入支持使用 可选的外部电阻器。通过 CTSx 和 CTRx 引脚,可以 对 RESET 信号的上升沿和下降沿进行延迟调整。此 外, CTSx 可忽略受监控电压轨上的电压干扰, 从而充 当去抖动器;CTRx 具有手动复位 (MR) 的作用,可用 于强制系统复位。

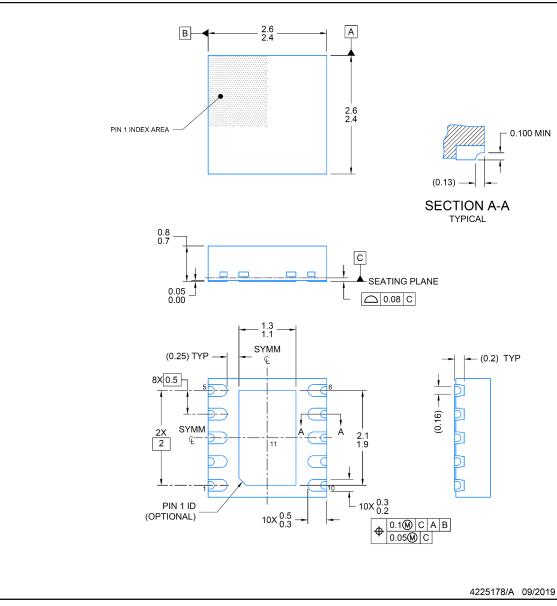

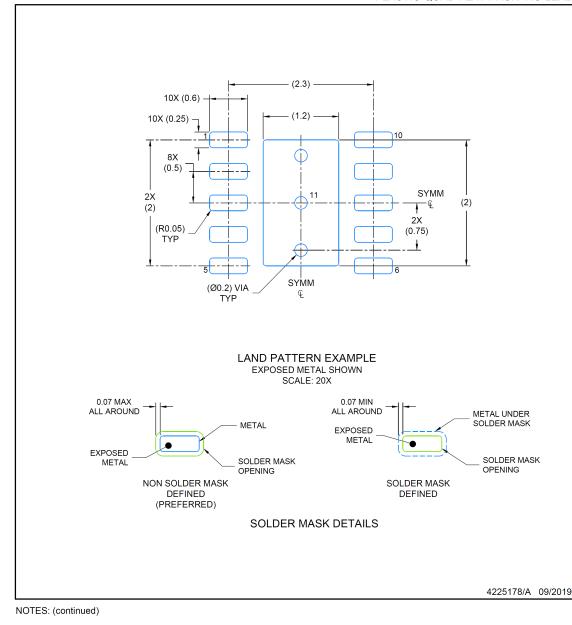

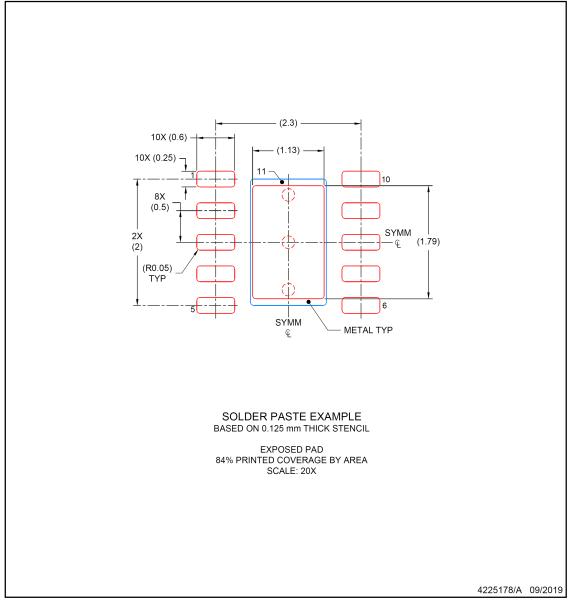

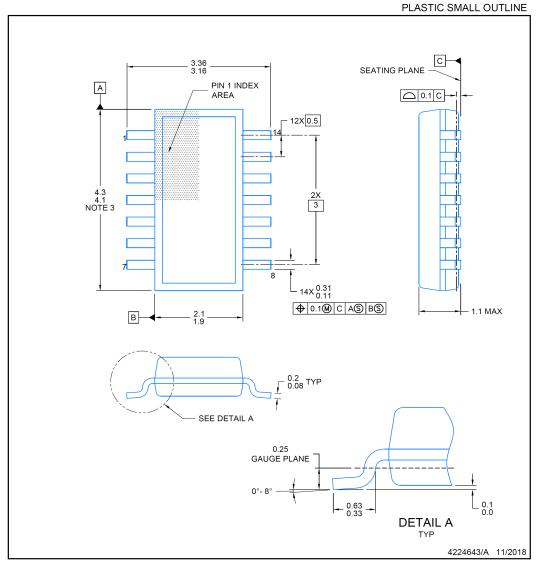

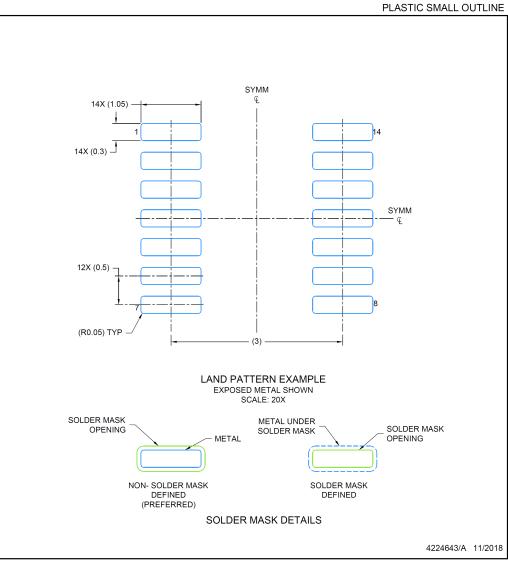

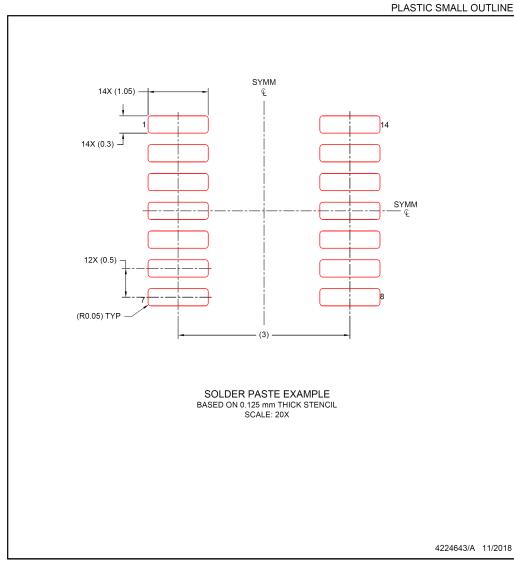

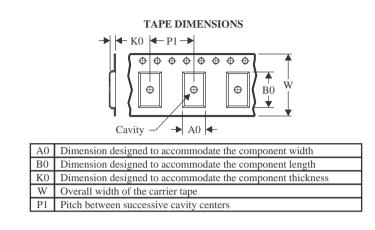

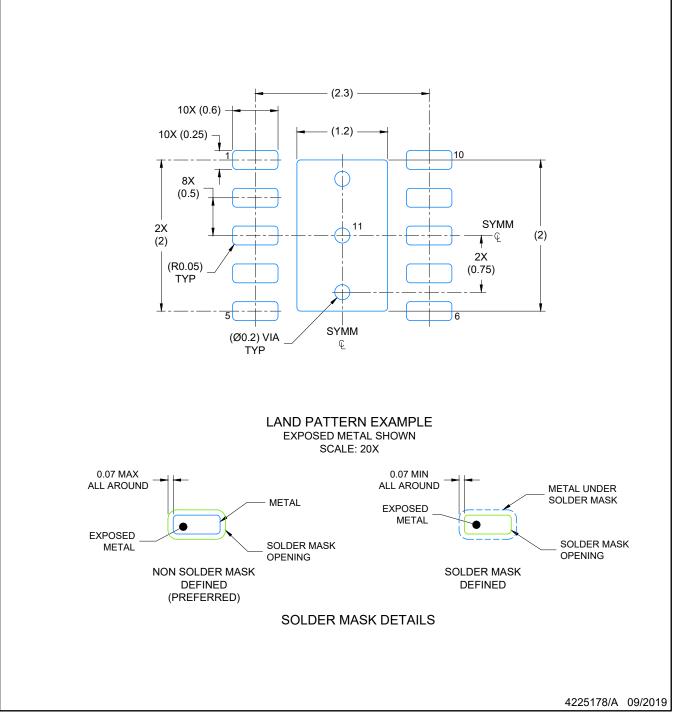

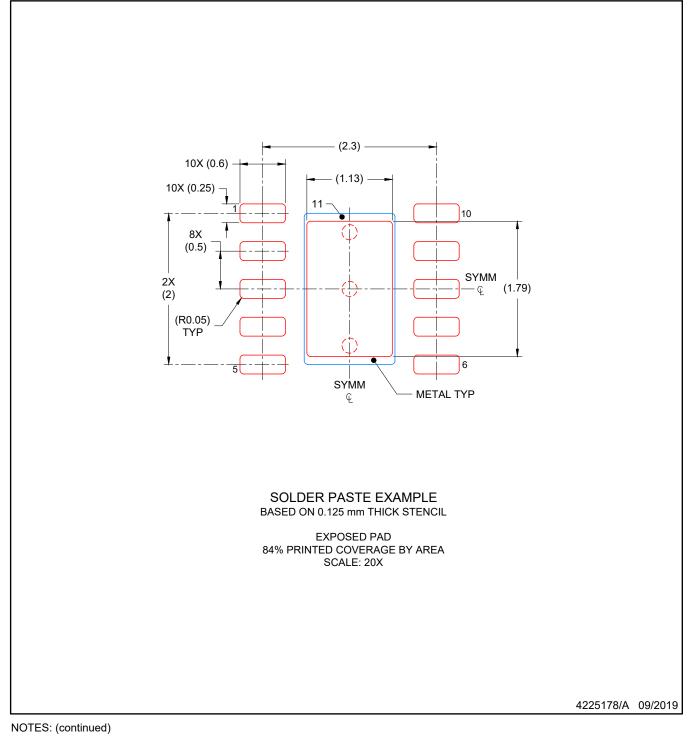

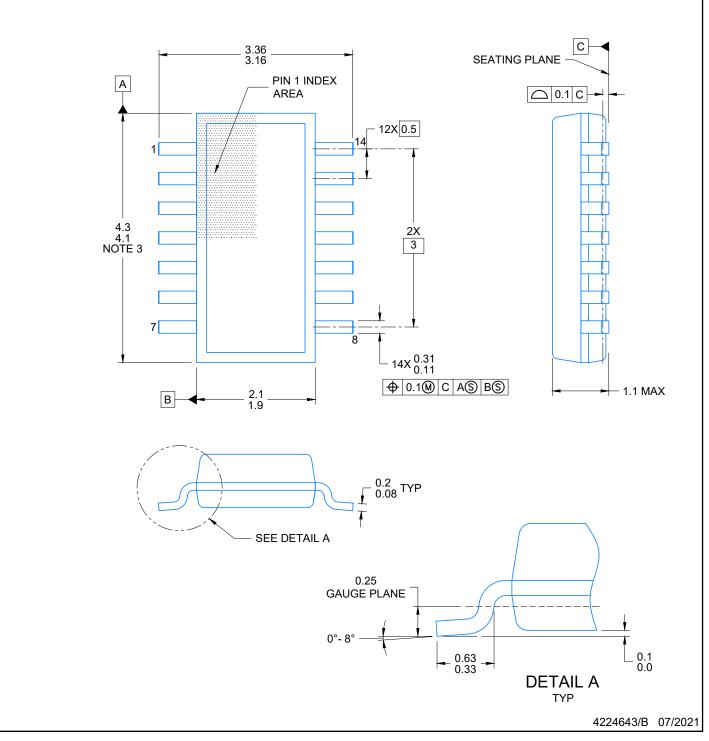

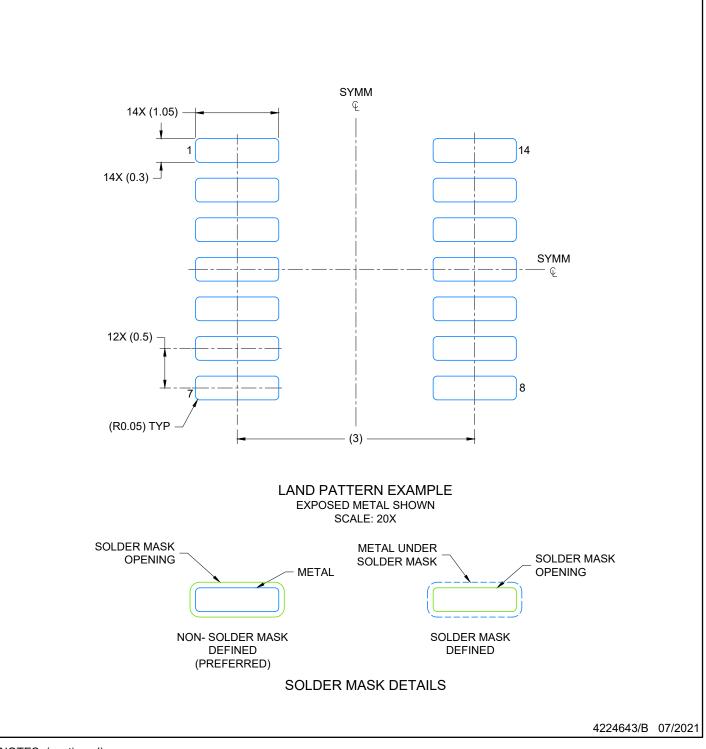

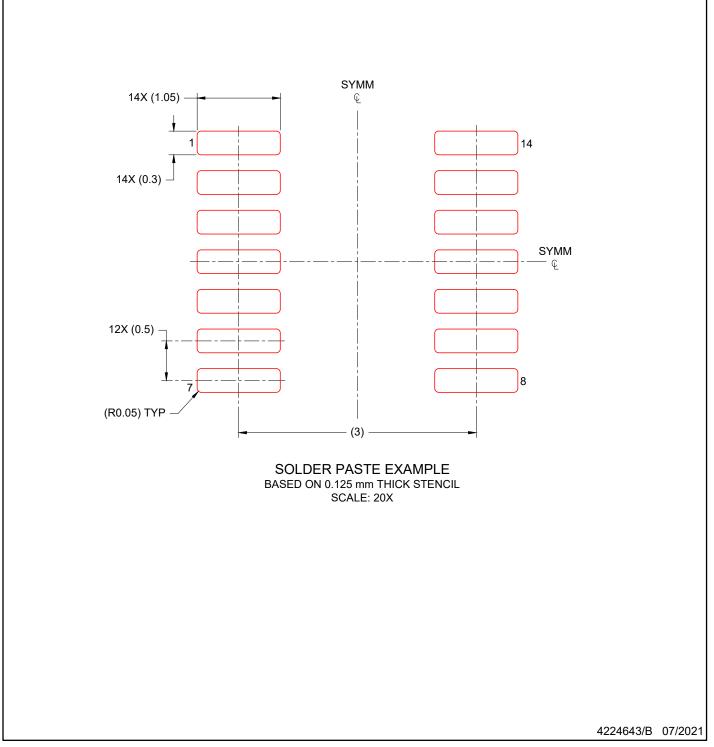

TPS37-Q1 采用 WSON 或 SOT-23 封装。WSON 封 装具有可湿性侧面,便于进行自动光学检测 (AOI) 和低 分辨率 X 射线检测。根据 IEC60664 中的指南,中心 垫片是不导电的,以增加 VDD 和 GND 之间的爬电距 廚。

#### 哭凪信自

| 器件型号     | 封装 (1)                           | 封装尺寸(标称值)       |

|----------|----------------------------------|-----------------|

| TPS37-Q1 | WSON (10) (DSK)                  | 2.5mm × 2.5mm   |

| TPS37-Q1 | SOT-23 (14) (DYY) <sup>(2)</sup> | 4.1 mm × 1.9 mm |

有关封装详细信息,请参阅数据表末尾的机械制图附录。 (1)

产品预发布 (2)

### **Table of Contents**

| 1 特性                     |                    |

|--------------------------|--------------------|

| 2 应用                     |                    |

| 3 说明                     |                    |

| 4 Revision History       | 2                  |

|                          | 4                  |

|                          | Functions5         |

| 7 Specifications         | 7                  |

| 7.1 Absolute Maximum     | Ratings7           |

| 7.2 ESD Ratings          | 7                  |

|                          | rating Conditions7 |

| 7.4 Thermal Information  |                    |

| 7.5 Electrical Character | stics8             |

|                          | s 10               |

| 7.7 Timing Diagrams      |                    |

| 7.8 Typical Characterist | cs13               |

|                          |                    |

|                          |                    |

| 8.2 Functional Block Dia | ıgram16            |

| 8.3 Feature Description  |                    |

| 0 Davias Eurotianal Madea                   | 25              |

|---------------------------------------------|-----------------|

| 9 Device Functional Modes                   |                 |

| 10 Application and Implementation           |                 |

| 10.1 Adjustable Voltage Thresholds          | 26              |

| 10.2 Application Information                | 27              |

| 10.3 Typical Application                    | 27              |

| 11 Power Supply Recommendations             | 29              |

| 11.1 Power Dissipation and Device Operation | <mark>29</mark> |

| 12 Layout                                   | 30              |

| 12.1 Layout Guidelines                      |                 |

| 12.2 Layout Example                         |                 |

| 12.3 Creepage Distance                      |                 |

| 13 Device and Documentation Support         | 32              |

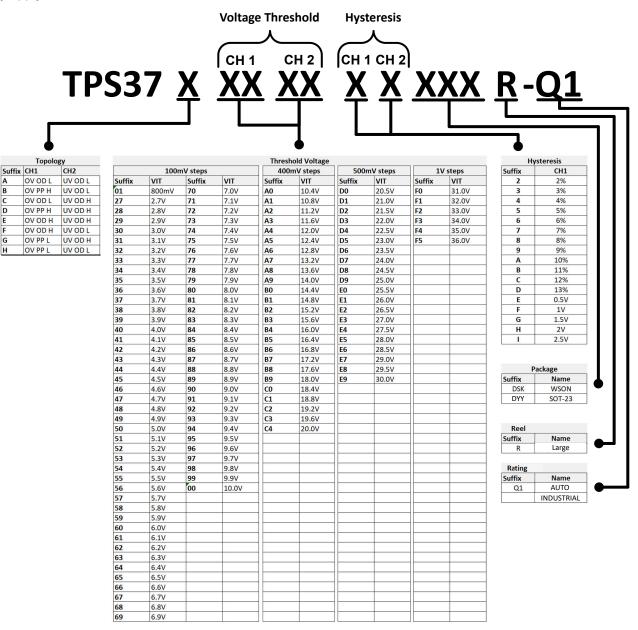

| 13.1 Device Nomenclature                    |                 |

| 13.2 支持资源                                   |                 |

| 13.3 Trademarks                             |                 |

| 13.4 Electrostatic Discharge Caution        |                 |

| 13.5 术语表                                    |                 |

| 14 Mechanical, Packaging, and Orderable     |                 |

| Information                                 | 33              |

|                                             |                 |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision A (January 2021) to Revision B (September 2021)                      | Page      |

|---|-------------------------------------------------------------------------------------------|-----------|

| • | 更新了数据表的标题并删除了器件型号中的"x"                                                                    |           |

| • | 更新了典型 IDD 与 VDD 曲线,并添加了 DYY 封装作为产品预发布                                                     |           |

| • | Edited Device Comparison Table and added DYY package                                      |           |

| • |                                                                                           |           |

| • | Added SENSEx undervoltage (UV) and overvoltage (OV) timing diagrams                       |           |

| • |                                                                                           |           |

| • | Updated Functional Block Diagram                                                          |           |

| • | Edited both Power Cycle figures (SENSE Outside and With in Nominal Voltage)               |           |

| • | Moved Common Hysteresis Lookup Table to SENSE Hysteresis section and added hysteresis exa | amples 19 |

| • | Added min and max reset time delay equations                                              |           |

|   | Added min and max sense time delay equations                                              |           |

|   | Edited manual reset (MR) timing diagram                                                   |           |

| • |                                                                                           |           |

| • | Added equations to solve for R1 and schematic figure                                      |           |

| • | Updated layout guidelines and example drawing. Added DYY example drawing                  |           |

| С | hanges from Revision * (August 2020) to Revision A (January 2021)                         | Page      |

| • | APL 更新                                                                                    | 1         |

| • | 添加了典型电源电流与 VDD 曲线并修改了"说明"部分                                                               |           |

| • | APL 更新                                                                                     | 1               |  |

|---|--------------------------------------------------------------------------------------------|-----------------|--|

|   | 添加了典型电源电流与 VDD 曲线并修改了"说明"部分                                                                |                 |  |

| • | Edited Device Comparison Table                                                             | 4               |  |

|   | Edited both Power Cycle figures (SENSE Outside and Within Nominal Voltage)                 |                 |  |

| • | Corrected the Hysteresis titles for both Undervoltage figures                              | 19              |  |

| • | Corrected Channel 1 of TPS37E from Open-Drain Low to Open-Drain High in Output Logic table | 21              |  |

| • | Added reset time delay discharge guideline                                                 | <mark>22</mark> |  |

| • | Added sense time delay discharge guideline                                                 | 23              |  |

| • | Added Device Functional Modes tables                                                       | 25              |  |

|   |                                                                                            |                 |  |

### **5** Device Comparison

Contact TI sales representatives or consult TI's E2E forum for details and availability; minimum order quantities may apply.

- 1. Sense logic: OV = overvoltage; UV = undervoltage

- Reset topology: PP = Push-Pull; OD = Open-Drain 2.

- Reset logic: L = Active-Low; H = Active-High 3.

- A to I hysteresis options are only available for 2.9 V to 9 V threshold options 4.

- 5. Product Preview (DYY) package

A

В

D

E

F

G

н

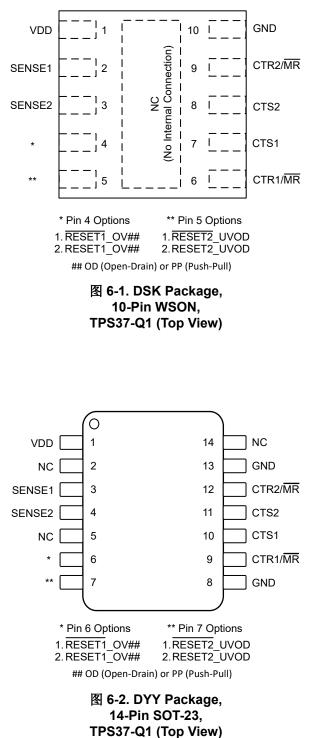

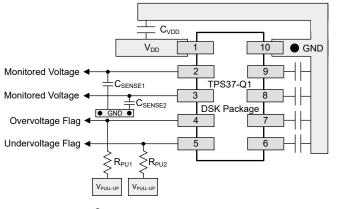

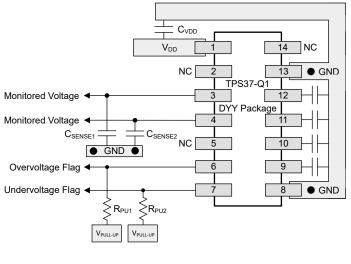

### **6** Pin Configuration and Functions

**ADVANCE INFORMATION**

**PRODUCT PREVIEW**

|                   | 表 6-1. Pin Functions |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------------|----------------------|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN               | WSON<br>(DSK)        | SOT23<br>(DYY) | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| NAME              | PIN<br>NUM.          | PIN<br>NUM.    |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| VDD               | 1                    | 1              | I   | Input Supply Voltage: Bypass with a 0.1 µF capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SENSE1            | 2                    | 3              | I   | This pin is connected to the voltage that will be monitored for fixed variants or to a resistor divider for the adjustable variant. When the voltage on SENSE1 pin transitions above the upper threshold voltage of $V_{IT+}$ , RESET1/RESET1 asserts after the sense time delay, set by CTS1. When the voltage on the SENSE1 pin transitions below the upper threshold voltage of $V_{IT+}$ - $V_{HYS}$ , RESET1/RESET1 deasserts after the reset time delay, set by CTR1. For noisy applications, placing a 10 nF to 100 nF ceramic capacitor close to this pin may be needed for optimum performance.                      |  |  |

| SENSE2            | 3                    | 4              | I   | This pin is connected to the voltage that will be monitored for fixed variants or to a resistor divider for the adjustable variant. When the voltage on SENSE2 pin transitions below the lower threshold voltage of V <sub>IT-</sub> , RESET2/RESET2 asserts after the sense time delay, set by CTS2. When the voltage on the SENSE2 pin transitions above the lower threshold voltage of V <sub>IT-</sub> + V <sub>HYS</sub> , RESET2/RESET2 deasserts after the reset time delay, set by CTR2. For noisy applications, placing a 10 nF to 100 nF ceramic capacitor close to this pin may be needed for optimum performance. |  |  |

| RESET1/<br>RESET1 | 4                    | 6              | 0   | Output Reset Signal For Channel 1: See 节 5 for output topology options. RESET1/RESET1 asserts when SENSE1 rises outside of the upper voltage threshold. RESET1/RESET1 remains asserted for the reset time delay period after SENSE1 transitions out of an overvoltage (OV) fault condition. For active low open-drain reset output, an external pullup resistor is required. Do not place external pullup resistors on push-pull outputs.<br>Reset output signal for: SENSE1<br>Sensing Topology: Overvoltage (OV)<br>Output topology: Open Drain or Push Pull, Active Low or Active High                                     |  |  |

| RESET2/<br>RESET2 | 5                    | 7              | 0   | Output Reset Signal For Channel 2: See <sup>††</sup> 5 for output topology options. RESET2/RESET2 asserts when SENSE2 falls outside of the lower voltage threshold. RESET2/RESET2 remains asserted for the reset time delay period after SENSE2 transitions out of an undervoltage (UV) fault condition. For active low open-drain reset output, an external pullup resistor is required. Reset output signal for: SENSE2 Sensing Topology: Undervoltage (UV) Output topology: Open Drain, Active Low or Active High                                                                                                          |  |  |

| CTR1/ MR          | 6                    | 9              | -   | Channel 1 RESET Time Delay: User-programmable reset time delay for RESET1/RESET1. Connect<br>an external capacitor for adjustable time delay or leave the pin floating for the shortest delay.<br>Manual Reset: If this pin is driven low, the RESET1/RESET1 output will reset and become asserted.<br>The pin can be left floating or be connected to a capacitor. This pin should not be driven high.                                                                                                                                                                                                                       |  |  |

| CTR2/ MR          | 9                    | 12             | -   | Channel 2 RESET Time Delay: User-programmable reset time delay for RESET2/RESET2. Connect<br>an external capacitor for adjustable time delay or leave the pin floating for the shortest delay.<br>Manual Reset: If this pin is driven low, the RESET2/RESET2 output will reset and become asserted.<br>The pin can be left floating or be connected to a capacitor. This pin should not be driven high.                                                                                                                                                                                                                       |  |  |

| GND               | 10                   | 8, 13          | -   | Ground. All GND pins must be electrically connected to the board ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| NC                | PAD                  | 2, 5, 14       | -   | The PAD for the <b>DSK</b> package is not internally connected, the PAD can be connected to GND or be left floating. For the <b>DYY</b> package, NC stands for "No Connect". The pins are to be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| CTS1              | 7                    | 10             | 0   | <b>Channel 1 SENSE Time Delay:</b> Capacitor programmable sense delay: CTS1 pin offers a user-<br>adjustable sense delay time when asserting a reset condition. Connecting this pin to a ground-<br>referenced capacitor sets the RESET1/RESET1 delay time to assert.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| CTS2              | 8                    | 11             | 0   | <b>Channel 2 SENSE Time Delay:</b> Capacitor programmable sense delay: CTS2 pin offers a user-<br>adjustable sense delay time when asserting a reset condition. Connecting this pin to a ground-<br>referenced capacitor sets the RESET2/RESET2 delay time to assert.                                                                                                                                                                                                                                                                                                                                                         |  |  |

### **7** Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range, unless otherwise noted (1)

|                            |                                                                               | MIN   | MAX | UNIT |

|----------------------------|-------------------------------------------------------------------------------|-------|-----|------|

| Voltage                    | $VDD, V_{SENSE1}, V_{SENSE2}, V_{RESET1}, V_{RESET2}, V_{RESET1}, V_{RESET2}$ | - 0.3 | 70  |      |

| Voltage                    | V <sub>CTS1</sub> , V <sub>CTS2</sub> , V <sub>CTR1</sub> , V <sub>CTR2</sub> | - 0.3 | 6   |      |

| Current                    | IRESET1, IRESET2, IRESET1, IRESET2                                            |       | 10  | mA   |

| Temperature <sup>(2)</sup> | Operating junction temperature, $T_J$                                         | - 40  | 150 | °C   |

| Temperature <sup>(2)</sup> | Operating Ambient temperature, T <sub>A</sub>                                 | - 40  | 150 | °C   |

| Temperature <sup>(2)</sup> | Storage, T <sub>stg</sub>                                                     | - 65  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) As a result of the low dissipated power in this device, it is assumed that  $T_J = T_A$ .

### 7.2 ESD Ratings

|                    |                         |                                                         | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> |                         | Charged device model (CDM), per AEC Q100-011            | ±750  | v    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|         |                                                                                                                    | MIN  | NOM MAX | UNIT |

|---------|--------------------------------------------------------------------------------------------------------------------|------|---------|------|

| Voltage | V <sub>DD</sub>                                                                                                    | 2.7  | 65      | V    |

| Voltage | $V_{\text{SENSE1}}, V_{\text{SENSE2}}, V_{\text{RESET1}}, V_{\text{RESET2}}, V_{\text{RESET1}}, V_{\text{RESET2}}$ | 0    | 65      | V    |

| Voltage | V <sub>CTS1</sub> , V <sub>CTS2</sub> , V <sub>CTR1</sub> , V <sub>CTR2</sub>                                      | 0    | 5.5     | V    |

| Current | IRESET1, IRESET2, IRESET1, IRESET2                                                                                 | 0    | ±5      | mA   |

| TJ      | Junction temperature (free air temperature)                                                                        | - 40 | 125     | °C   |

### 7.4 Thermal Information

|                        |                                              | TPS37-Q1 |      |

|------------------------|----------------------------------------------|----------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DSK      | UNIT |

|                        |                                              | 10-PIN   |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 87.4     | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 76.3     | °C/W |

| R <sub>θ JB</sub>      | Junction-to-board thermal resistance         | 54.2     | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 4.8      | °C/W |

| ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 54.2     | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 34.8     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Electrical Characteristics

At  $V_{DD(MIN)} \le V_{DD} \le V_{DD (MAX)}$ , CTR1/ $\overline{MR}$  = CTR2/ $\overline{MR}$  = CTS1 = CTS2 = open, output reset pull-up resistor  $R_{PU}$  = 10 k  $\Omega$ , voltage  $V_{PU}$  = 5.5 V, and load  $C_{LOAD}$  = 10 pF. The operating free-air temperature range  $T_A$  = - 40°C to 125°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C and VDD = 16 V and  $V_{IT}$  = 6.5 V ( $V_{IT}$  refers to  $V_{ITN}$  or  $V_{ITP}$ ).

|                                | PARAMETER                                                                                                             | TEST CONDITIONS                                                                                                                                                    | MIN                | ТҮР   | MAX   | UNIT |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|-------|------|

| VDD                            |                                                                                                                       |                                                                                                                                                                    |                    |       |       |      |

| V <sub>DD</sub>                | Supply Voltage                                                                                                        |                                                                                                                                                                    | 2.7                |       | 65    | V    |

| UVLO <sup>(1)</sup>            | Under Voltage Lockout                                                                                                 | V <sub>DD</sub> Falling below V <sub>DD (MIN)</sub>                                                                                                                | ·                  |       | 2.7   | V    |

| V <sub>POR</sub>               | Power on Reset Voltage <sup>(2)</sup><br>RESET, Active Low<br>(Open-Drain, Push-Pull)                                 | V <sub>OL(MAX)</sub> = 300 mV<br>I <sub>OUT (Sink)</sub> = 15 μA                                                                                                   |                    |       | 1.4   | V    |

| V <sub>POR</sub>               | Power on Reset Voltage <sup>(2)</sup><br>RESET, Active High<br>(Push-Pull)                                            | $V_{OH(MIN)} = 0.8 \times V_{DD}$<br>$I_{OUT (Source)} = 15 \ \mu A$                                                                                               |                    |       | 1.4   | V    |

| I <sub>DD</sub>                | Supply current into VDD pin                                                                                           | $\label{eq:VIT} \begin{array}{ c c c } V_{IT} = 800 \text{ mV} \\ V_{DD \ (MIN)} \leqslant V_{DD} \leqslant V_{DD \ (MAX)} \end{array}$                            |                    | 1     | 2.6   | μA   |

|                                |                                                                                                                       | $\begin{array}{l} V_{IT} \texttt{=} \texttt{2.7 V to 36 V} \\ V_{DD \ (MIN)} \leqslant V_{DD} \leqslant V_{DD \ (MAX)} \end{array}$                                |                    | 1     | 2     | μA   |

| SENSE (Inp                     | out)                                                                                                                  |                                                                                                                                                                    | ·                  |       | ·     |      |

| I <sub>SENSE</sub>             | Input current<br>(SENSE1, SENSE2)                                                                                     | V <sub>IT</sub> = 800 mV                                                                                                                                           |                    |       | 100   | nA   |

| SENSE                          | Input current<br>(SENSE1, SENSE2)                                                                                     | V <sub>IT</sub> < 10 V                                                                                                                                             |                    |       | 0.8   | μA   |

| I <sub>SENSE</sub>             | Input current<br>(SENSE1, SENSE2)                                                                                     | 10 V < V <sub>IT</sub> < 26 V                                                                                                                                      |                    |       | 1.2   | μA   |

| I <sub>SENSE</sub>             | Input current<br>(SENSE1, SENSE2)                                                                                     | V <sub>IT</sub> > 26 V                                                                                                                                             |                    |       | 2     | μA   |

| .,                             | Input Threshold Negative<br>(Undervoltage)                                                                            | V <sub>IT</sub> = 2.7 V to 36 V                                                                                                                                    | -1.5               |       | 1.5   | %    |

| V <sub>ITN</sub>               |                                                                                                                       | V <sub>IT</sub> = 800 mV <sup>(3)</sup>                                                                                                                            | 0.792              | 0.800 | 0.808 | V    |

|                                | Input Threshold Positive                                                                                              | V <sub>IT</sub> = 2.7 V to 36 V                                                                                                                                    | -1.5               |       | 1.5   | %    |

| V <sub>ITP</sub>               | (Övervoltage)                                                                                                         | V <sub>IT</sub> = 800 mV <sup>(3)</sup>                                                                                                                            | 0.792              | 0.800 | 0.808 | V    |

|                                |                                                                                                                       | V <sub>IT</sub> = 0.8 V and 2.7 V to 36 V<br>V <sub>HYS</sub> Range = 2% to 13%<br>(1% step)                                                                       | -1.5               |       | 1.5   | %    |

| V <sub>HYS</sub>               | Hysteresis Accuracy <sup>(4)</sup>                                                                                    | $ \begin{array}{c} V_{IT} = 2.7 \ V \ to \ 8 \ V \\ V_{HYS} = 0.5 \ V, \ 1 \ V, \ 1.5 \ V, \ 2 \ V, \\ 2.5 \ V \\ V_{IT} - V_{HYS} \geqslant 2.4 \ V \end{array} $ | -1.5               |       | 1.5   | %    |

| RESET (Ou                      | tput)                                                                                                                 |                                                                                                                                                                    |                    |       |       |      |

|                                | Open-Drain leakage                                                                                                    | V <sub>RESET</sub> = 5.5 V<br>V <sub>ITN</sub> < V <sub>SENSE</sub> < V <sub>ITP</sub>                                                                             |                    |       | 300   | nA   |

| I <sub>lkg(OD)</sub>           | (RESET1, RESET2)                                                                                                      | V <sub>RESET</sub> = 65 V<br>V <sub>ITN</sub> < V <sub>SENSE</sub> < V <sub>ITP</sub>                                                                              |                    |       | 300   | nA   |

| V <sub>OL</sub> <sup>(5)</sup> | Low level output voltage                                                                                              | $\begin{array}{c} 2.7 \ V \leqslant VDD \leqslant 65 \ V \\ I_{RESET} = 5 \ mA \end{array}$                                                                        |                    |       | 300   | mV   |

| V <sub>OH_DO</sub>             | High level output voltage<br>dropout<br>(V <sub>DD</sub> - V <sub>OH</sub> = V <sub>OH_DO</sub> )<br>(Push-Pull only) | $2.7 \text{ V} \leq \text{VDD} \leq 65 \text{ V}$<br>I <sub>RESET</sub> = 500 uA                                                                                   |                    |       | 43    | mV   |

| V <sub>OH</sub> <sup>(5)</sup> | High level output voltage<br>(Push-Pull only)                                                                         | $\begin{array}{c} \text{2.7 V} \leqslant \text{VDD} \leqslant \text{65 V} \\ \text{I}_{\text{RESET}} = 5 \text{ mA} \end{array}$                                   | 0.8V <sub>DD</sub> |       |       | V    |

### 7.5 Electrical Characteristics (continued)

At  $V_{DD(MIN)} \le V_{DD} \le V_{DD (MAX)}$ , CTR1/ $\overline{MR}$  = CTR2/ $\overline{MR}$  = CTS1 = CTS2 = open, output reset pull-up resistor  $R_{PU}$  = 10 k  $\Omega$ , voltage  $V_{PU}$  = 5.5 V, and load  $C_{LOAD}$  = 10 pF. The operating free-air temperature range  $T_A$  = - 40°C to 125°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C and VDD = 16 V and  $V_{IT}$  = 6.5 V ( $V_{IT}$  refers to  $V_{ITN}$  or  $V_{ITP}$ ).

|                    | PARAMETER                                                    | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT  |

|--------------------|--------------------------------------------------------------|-----------------|------|------|------|-------|

| Capacitor          | Timing (CTS, CTR)                                            |                 |      |      | I    |       |

| R <sub>CTR</sub>   | Internal resistance<br>(CTR1 / MR , CTR2 / MR )              |                 | 877  | 1000 | 1147 | Kohms |

| R <sub>CTS</sub>   | Internal resistance<br>(C <sub>TS1,</sub> C <sub>TS2</sub> ) |                 | 88   | 100  | 122  | Kohms |

| Manual Re          | eset (MR)                                                    |                 |      |      |      |       |

| V <sub>MR_IH</sub> | CTR1 / MR and<br>CTR2 / MR pin<br>logic high input           | VDD = 2.7 V     | 2000 |      |      | mV    |

| V <sub>mr_ih</sub> | CTR1 / MR and<br>CTR2 / MR pin<br>logic high input           | VDD = 65 V      | 2500 |      |      | mV    |

| V <sub>MR_IL</sub> | CTR1 / MR and<br>CTR2 / MR pin<br>logic low input            | VDD = 2.7 V     |      |      | 1300 | mV    |

| V <sub>MR_IL</sub> | CTR1 / MR and<br>CTR2 / MR pin<br>logic low input            | VDD = 65 V      |      |      | 1300 | mV    |

(1) When V\_{DD} voltage falls below UVLO, reset is asserted for Output 1 and Output 2. V\_{DD} slew rate  $\leq$  100 mV /  $\mu$ s

(2)  $V_{POR}$  is the minimum  $V_{DD}$  voltage for a controlled output state. Below VPOR, the output cannot be determined.  $V_{DD}$  dv/dt  $\leq$  100mV/µs (3) For adjustable voltage guidelines and resistor selection refer to Adjustable Voltage Thresholds in Application and Implementation

section

(4) Hysteresis is with respect to V<sub>ITP</sub> and V<sub>ITN</sub> voltage threshold. V<sub>ITP</sub> has negative hysteresis and V<sub>ITN</sub> has positive hysteresis.

(5) For  $V_{OH}$  and  $V_{OL}$  relation to output variants refer to **Timing Figures after the Timing Requirement Table**

### 7.6 Timing Requirements

At  $V_{DD(MIN)} \le V_{DD} \le V_{DD (MAX)}$ , CTR1/ $\overline{MR}$  = CTR2/ $\overline{MR}$  = CTS1 = CTS2 = open <sup>(1)</sup>, output reset pull-up resistor  $R_{PU}$  = 10 k  $\Omega$ , voltage  $V_{PU}$  = 5.5V, and  $C_{LOAD}$  = 10 pF. VDD and SENSE slew rate = 1V / µs. The operating free-air temperature range  $T_A$  = - 40°C to 125°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C and VDD = 16 V and  $V_{IT}$  = 6.5 V ( $V_{IT}$  refers to either  $V_{ITN}$  or  $V_{ITP}$ ).

|                  | PARAMETER                                              | TEST CONDITIONS                                                                                    | MIN | TYP | MAX | UNIT |

|------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Common ti        | ming parameters                                        |                                                                                                    |     |     |     |      |

| t <sub>ctr</sub> | Reset release time delay                               | VIT = 2.7 V to 36 V<br>$C_{CTR1} = C_{CTR2} = Open$<br>20% Overdrive from Hysteresis               |     |     | 100 | μs   |

|                  | (CTR1/MR, CTR2/MR) <sup>(2)</sup>                      | VIT = 800 mV<br>C <sub>CTR1</sub> = C <sub>CTR2</sub> = Open<br>20% Overdrive from Hysteresis      |     |     | 40  | μs   |

| t <sub>CTS</sub> | Sense detect time delay<br>(CTS1, CTS2) <sup>(3)</sup> | VIT = 2.7 V to 36 V<br>$C_{CTS1} = C_{CTS2} = Open$<br>20% Overdrive from V <sub>IT</sub>          |     | 34  | 90  | μs   |

|                  |                                                        | VIT = 800 mV<br>C <sub>CTS1</sub> = C <sub>CTS2</sub> = Open<br>20% Overdrive from V <sub>IT</sub> | 8   |     | 11  | μs   |

| t <sub>SD</sub>  | Startup Delay <sup>(4)</sup>                           | C <sub>CTR1/MR</sub> = C <sub>CTR2/MR</sub> = Open                                                 |     |     | 2   | ms   |

(1) C<sub>CTR1</sub> = Reset delay channel 1, C<sub>CTR2</sub> = Reset delay channel 2,

C<sub>CTS1</sub> = Sense delay channel 1, C<sub>CTS2</sub> = Sense delay channel 2

(2) CTR Reset detect time delay: Overvoltage active-LOW output is measure from V<sub>ITP - HYS</sub> to V<sub>OH</sub> Undervoltage active-LOW output is measure from V<sub>ITP - HYS</sub> to V<sub>OH</sub> Overvoltage active-HIGH output is measure from V<sub>ITP - HYS</sub> to V<sub>OL</sub> Undervoltage active-HIGH output is measure from V<sub>ITP - HYS</sub> to V<sub>OL</sub>

#### (3) **CTS Sense detect time delay:** Active-low output is measure from V<sub>IT</sub> to V<sub>OL</sub> (or V<sub>Pullup</sub>) Active-high output is measured from V<sub>IT</sub> to V<sub>OH</sub> V<sub>IT</sub> refers to either V<sub>ITN</sub> or V<sub>ITP</sub>

# (4) During the power-on sequence, VDD must be at or above V<sub>DD (MIN)</sub> for at least t<sub>SD</sub> before the output is in the correct state based on V<sub>SENSE</sub>.

t<sub>SD</sub> time includes the propagation delay (C<sub>CTR1</sub> = C<sub>CTR2</sub> = Open). Capaicitor in C<sub>CTR1</sub> or C<sub>CTR2</sub> will add time to t<sub>SD</sub>.

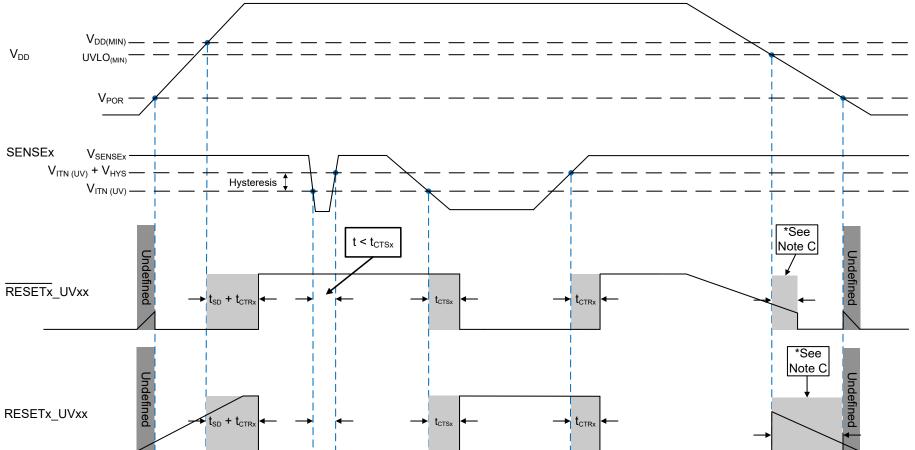

### 7.7 Timing Diagrams

- A. For open-drain output option, the timing diagram assumes the RESETx\_UVOD / RESETx\_UVOD pin is connected via an external pull-up resistor to VDD.

- B. Be advised that 🕅 7-1 shows the VDD falling slew rate is slow or the VDD decay time is much larger than the propagation detect delay (t<sub>CTRx</sub>) time.

- C. RESETx\_UVxx / RESETx\_UVxx is asserted when VDD goes below the UVLO(MIN) threshold after the time delay, t<sub>CTRx</sub>, is reached.

### 图 7-1. SENSEx Undervoltage (UV) Timing Diagram

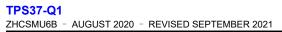

A. For open-drain output option, the timing diagram assumes the RESETx\_OVOD / RESETx\_OVOD pin is connected via an external pull-up resistor to VDD.

B. Be advised that 🗏 7-2 shows the VDD falling slew rate is slow or the VDD decay time is much larger than the propagation detect delay (t<sub>CTRx</sub>) time.

C. RESETx\_OVxx / RESETx\_OVxx is asserted when VDD goes below the UVLO<sub>(MIN)</sub> threshold after the time delay, t<sub>CTRx</sub>, is reached.

#### 图 7-2. SENSEx Overvoltage (OV) Timing Diagram

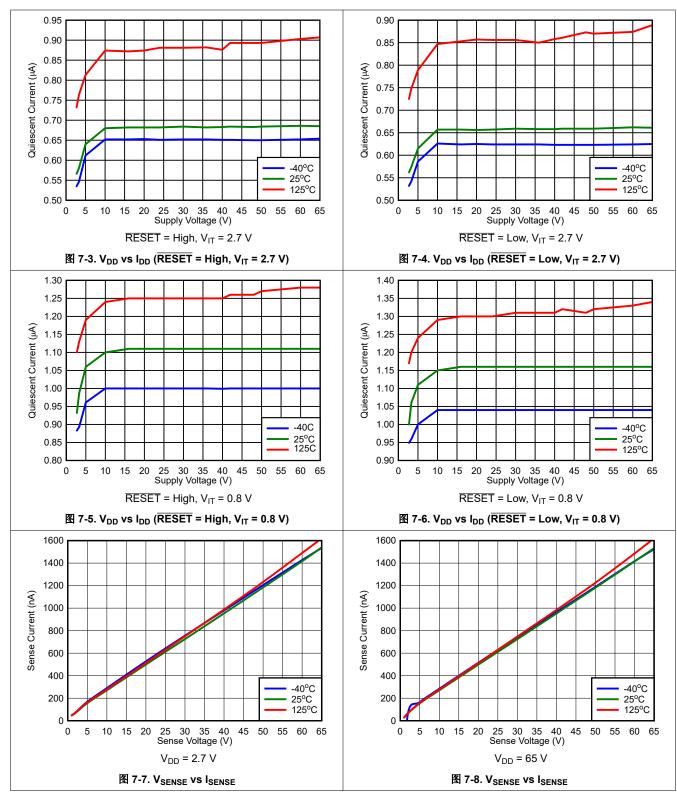

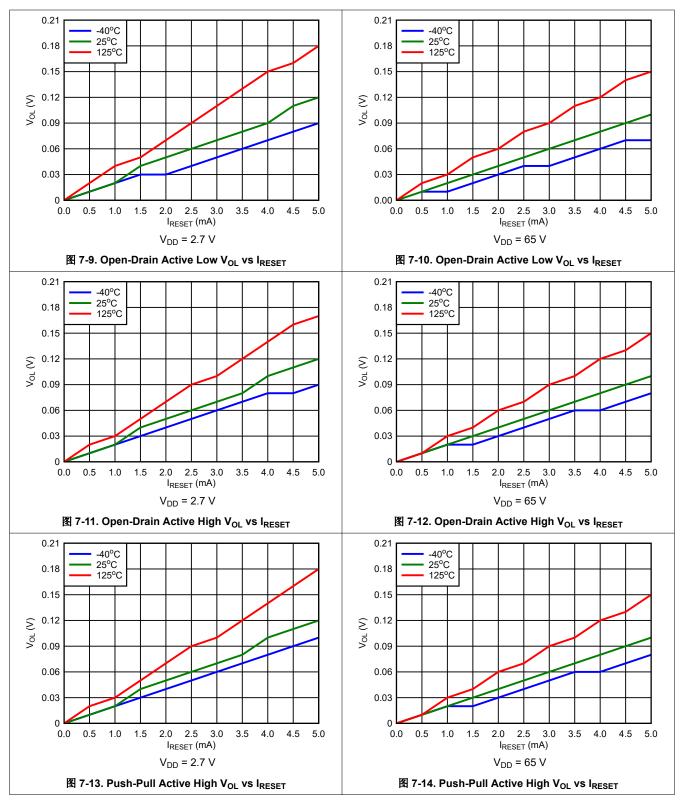

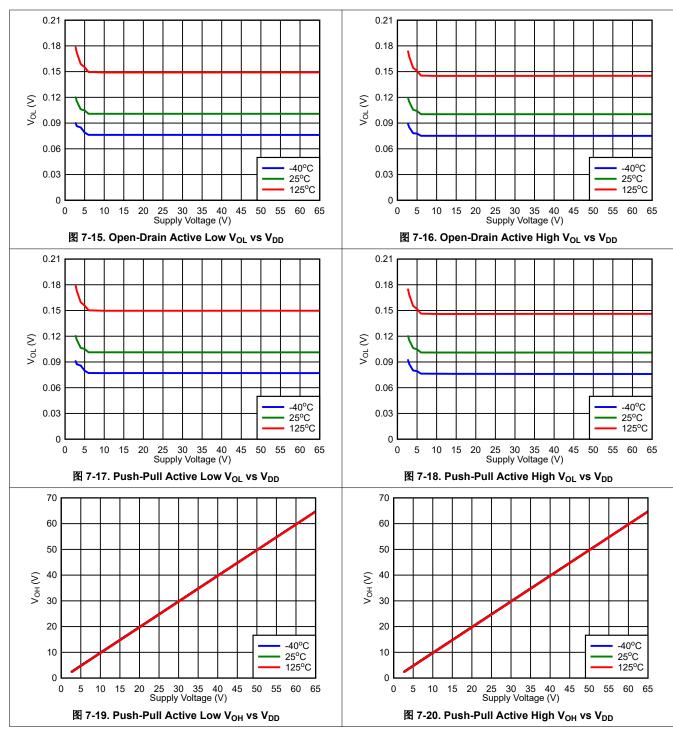

### 7.8 Typical Characteristics

Typical characteristics show the typical performance of the TPS37-Q1 device. Test conditions are  $T_A = 25^{\circ}C$ ,  $R_{PU} = 100 \text{ k}\Omega$ ,  $C_{Load} = 50 \text{ pF}$ , unless otherwise noted.

**ADVANCE INFORMATION**

### 7.8 Typical Characteristics (continued)

Typical characteristics show the typical performance of the TPS37-Q1 device. Test conditions are  $T_A = 25^{\circ}C$ ,  $R_{PU} = 100 \text{ k}\Omega$ ,  $C_{Load} = 50 \text{ pF}$ , unless otherwise noted.

### 7.8 Typical Characteristics (continued)

Typical characteristics show the typical performance of the TPS37-Q1 device. Test conditions are  $T_A = 25^{\circ}C$ ,  $R_{PU} = 100 \text{ k}\Omega$ ,  $C_{Load} = 50 \text{ pF}$ , unless otherwise noted.

### 8 Detailed Description

### 8.1 Overview

**ADVANCE INFORMATION**

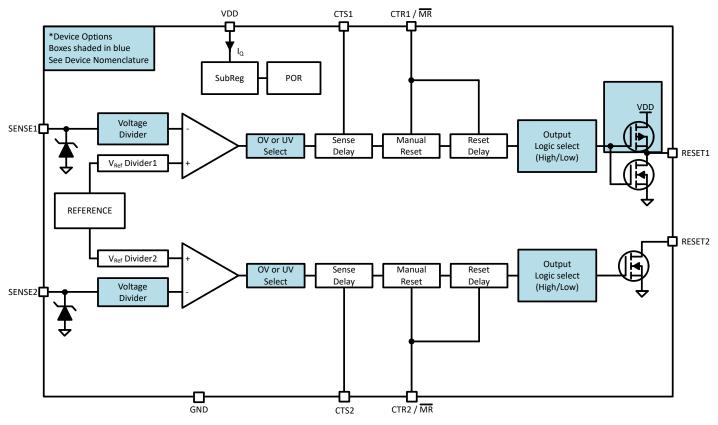

The TPS37-Q1 is a family of high voltage and low quiescent current reset IC with fixed threshold voltage. Voltage divider is integrated to eliminate the need for external resistors and eliminate leakage current that comes with resistor dividers. However, it can also support external resistor if required by application, the lowest threshold 800 mV (bypass internal resistor ladder) is recommenced for external resistors use case to take advantage of faster detection time and lower I<sub>SENSE</sub> current.

VDD, SENSE and RESET pins can support 65 V continuous operation; both VDD and SENSE voltage levels can be independent of each other, meaning VDD pin can be connected at 2.7 V while SENSE pins are connected to a higher voltage. One thing of note, the TPS37-Q1 does not have clamps within the device so external circuits or devices must be added to limit the voltages to the absolute max limit.

Additional features include programmable sense time delay (CTS1, CTS2) and reset delay time and manual reset (CTR1 /  $\overline{MR}$ , CTR2 /  $\overline{MR}$ ).

### 8.2 Functional Block Diagram

图 8-1. Functional Block Diagram <sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Refer to  $\ddagger 5$  for complete list of topologies and output logic combination

### 8.3 Feature Description

### 8.3.1 Input Voltage (VDD)

VDD operating voltage ranges from 2.7 V to 65 V. An input supply capacitor is not required for this device; however, if the input supply is noisy good analog practice is to place a 0.1  $\mu$ F capacitor between the VDD and GND.

VDD needs to be at or above  $V_{DD(MIN)}$  for at least the start-up time delay (t<sub>SD</sub>) for the device to be fully functional.

VDD voltage is independent of  $V_{\text{SENSE}}$  and  $V_{\text{RESET}}$ , meaning that VDD can be higher or lower than the other pins.

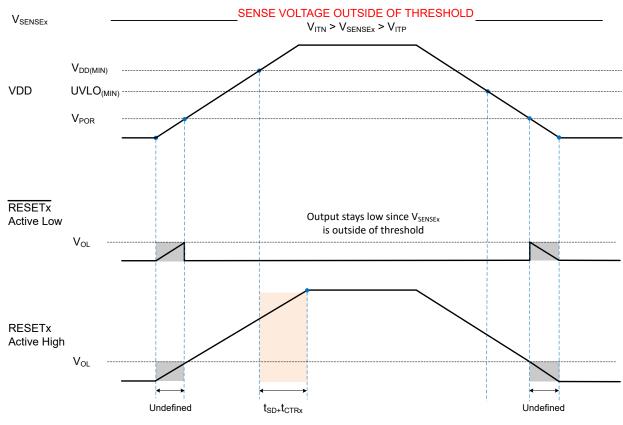

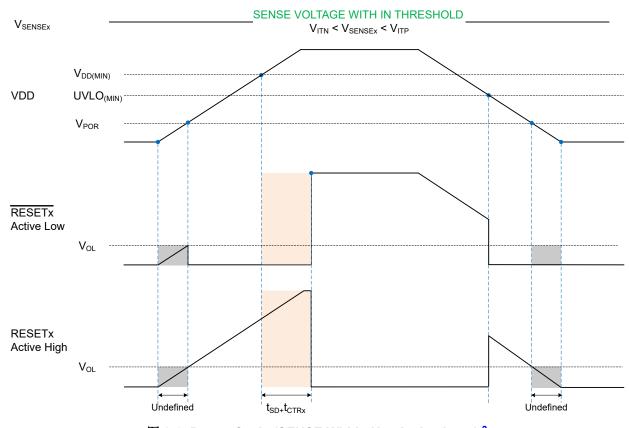

#### 8.3.1.1 Undervoltage Lockout (V<sub>POR</sub> < V<sub>DD</sub> < UVLO)

When the voltage on VDD is less than the UVLO voltage, but greater than the power-on reset voltage (V<sub>POR</sub>), the output pins will be in reset, regardless of the voltage at SENSE pins.

#### 8.3.1.2 Power-On Reset ( $V_{DD} < V_{POR}$ )

When the voltage on VDD is lower than the power on reset voltage ( $V_{POR}$ ), the output signal is undefined and is not to be relied upon for proper device function.

图 8-2. Power Cycle (SENSE Outside of Nominal voltage)<sup>2</sup>

<sup>&</sup>lt;sup>2</sup> Figure assumes an external pull-up resistor is connected to the reset pin via VDD

图 8-3. Power Cycle (SENSE Within Nominal voltage)<sup>3</sup>

<sup>&</sup>lt;sup>3</sup> Figure assumes an external pull-up resistor is connected to the reset pin via VDD

#### 8.3.2 SENSE

The TPS37-Q1 high voltage family integrates two voltage comparators, a precision reference voltage and trimmed resistor divider. This configuration optimizes device accuracy because all resistor tolerances are accounted for in the accuracy and performance specifications. Device also has built-in hysteresis that provides noise immunity and ensures stable operation.

Channels are independent of each other, meaning that SENSE1 and SENSE2 and respective outputs can be connected to different voltage rails.

Although not required in most cases, for noisy applications good analog design practice is to place a 10 nF to 100 nF bypass capacitor at the SENSEx inputs in order to reduce sensitivity to transient voltages on the monitored signal. SENSE1 and SENSE2 pins can be connected directly to VDD pin.

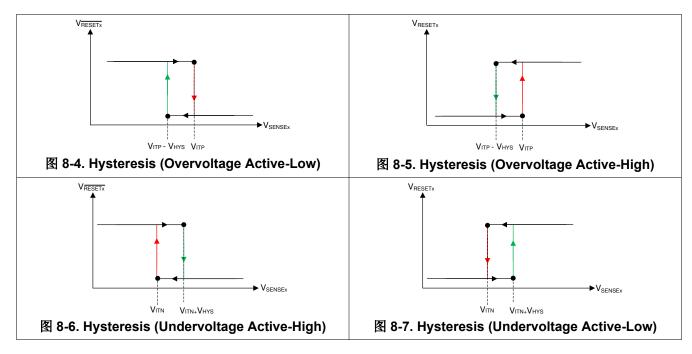

#### 8.3.2.1 SENSE Hysteresis

Built-in hysteresis to avoid erroneous output reset release. The hysteresis is opposite to the threshold voltage; for overvoltage options the hysteresis is subtracted from the positive threshold ( $V_{ITP}$ ), for undervoltage options hysteresis is added to the negative threshold ( $V_{ITN}$ ).

|                  | TARGET       |                     | DEVICE ACTUAL HYSTERESIS OPTION |

|------------------|--------------|---------------------|---------------------------------|

| DETECT THRESHOLD | TOPOLOGY     | RELEASE VOLTAGE (V) | Device Actual Histeresis of How |

| 18.0 V           | Overvoltage  | 17.5 V              | -3%                             |

| 18.0 V           | Overvoltage  | 16.0 V              | -11%                            |

| 17.0 V           | Overvoltage  | 16.5 V              | -3%                             |

| 16.0 V           | Overvoltage  | 15.0 V              | -6%                             |

| 15.0 V           | Overvoltage  | 14.0 V              | -7%                             |

| 6.0 V            | Undervoltage | 6.5 V               | 0.5 V                           |

| 5.5 V            | Undervoltage | 6 V                 | 0.5 V                           |

| 8 V              | Undervoltage | 9 V                 | 1 V                             |

| 5 V              | Undervoltage | 7.5 V               | 2.5 V                           |

#### 表 8-1. Common Hysteresis Lookup Table

**8-1** shows a sample of hysteresis and voltage options for the TPS37-Q1. For threshold voltages ranging from 2.7 V to 8 V, one option is to select a fixed hysteresis value ranging from 0.5 V to 2.5 V in increments of 0.5 V. Additionally, a second option can be selected where the hysteresis value is a percentage of the threshold voltage. The percentage of voltage hysteresis ranges from 2% to 13%.

Knowing the amount of hysteresis voltage, the release voltage for the undervoltage (UV) channel is  $(V_{\text{ITN}(UV)} + V_{\text{HYS}})$  and for the overvoltage (OV) channel is  $(V_{\text{ITP}(OV)} - V_{\text{HYS}})$ . For a visual understanding of the UV and OV release voltage, see SENSEx Undervoltage (UV) Timing Diagram and SENSEx Overvoltage (OV) Timing Diagram. The accuracy of the release voltage, or stated in the  $\ddagger$  7.5 as *Hysteresis Accuracy* is ±1.5%. Expanding what is shown in  $\frac{1}{28}$  8-1, below are a few voltage hysteresis examples that include the hysteresis accuracy:

Undervoltage (UV) Channel

V<sub>ITN</sub> = 0.8 V

Voltage Hysteresis (V<sub>HYS</sub>) = 5% = 40 mV

Hysteresis Accuracy = ±1.5% = 39.4 mV or 40.6 mV

Release Voltage =  $V_{ITN}$  +  $V_{HYS}$  = 839.4 mV to 840.6 mV

Overvoltage (OV) Channel

V<sub>ITP</sub> = 8 V

Voltage Hysteresis (V<sub>HYS</sub>) = 2 V

Hysteresis Accuracy =  $\pm 1.5\%$  = 1.97 V or 2.03 V

Release Voltage =  $V_{ITN}$  +  $V_{HYS}$  = 9.97 V to 10.03 V

#### 8.3.3 Output Logic Configurations

TPS37-Q1 has two channels with separate sense pins and reset pins that can be configured independently of each other. Channel 1 is available as Open-Drain and Push-Pull while channel 2 is only available as Open-Drain topology.

The available output logic configuration combinations are shown in  $\frac{1}{8}$  8-2.

| DESCRIPTION                                                     | NOMENCLATURE           | VAI                | .UE                |  |  |  |  |  |

|-----------------------------------------------------------------|------------------------|--------------------|--------------------|--|--|--|--|--|

| GPN                                                             | TPS37-Q1 (+ topology)  | CHANNEL 1          | CHANNEL 2          |  |  |  |  |  |

| Topology (OV and UV only)                                       | TPS37A-Q1              | OV OD L            | UV OD L            |  |  |  |  |  |

| both channels are either OV or UV                               | TPS37B-Q1              | OV PP H            | UV OD L            |  |  |  |  |  |

| <ul> <li>UV = Undervoltage</li> <li>OV = Overvoltage</li> </ul> | TPS37C-Q1              | OV OD L            | UV OD H            |  |  |  |  |  |

|                                                                 | TPS37D-Q1              | OV PP H            | UV OD H            |  |  |  |  |  |

| • PP = Push-Pull                                                | TPS37E-Q1              | OV OD H            | UV OD H            |  |  |  |  |  |

| • OD = Open-Drain                                               | TPS37F-Q1              | OV PP H            | UV OD L            |  |  |  |  |  |

| L = Active low                                                  | TPS37G-Q1              | OV OD L            | UV OD H            |  |  |  |  |  |

| H = Active high                                                 | TPS37H-Q1              | OV OD H            | UV OD L            |  |  |  |  |  |

| <ul> <li>OD = Open-Drain</li> <li>L = Active low</li> </ul>     | TPS37F-Q1<br>TPS37G-Q1 | OV PP H<br>OV OD L | UV OD L<br>UV OD H |  |  |  |  |  |

### 表 8-2. TPS37-Q1 Output Logic

### 8.3.3.1 Open-Drain

Open-drain output requires an external pull-up resistor to hold the voltage high to the required voltage logic. Connect the pull-up resistor to the proper voltage rail to enable the output to be connected to other devices at the correct interface voltage levels.

To select the right pull-up resistor consider system  $V_{OH}$  and the ( $I_{lkg}$ ) current provided in the electrical characteristics, high resistors values will have a higher voltage drop affecting the output voltage high. The open-drain output can be connected as a wired-AND logic with other open-drain signals such as another TPS37-Q1 open-drain output pin.

#### 8.3.3.2 Push-Pull

Push-Pull output does not require an external resistor since is the output is internally pulled-up to VDD during  $V_{OH}$  condition and output will be connected to GND during  $V_{OH}$  condition.

#### 8.3.3.3 Active-High (RESET)

RESET (active-high), denoted with no bar above the pin label. RESET remains low ( $V_{OL}$ , deasserted) as long as sense voltage is in normal operation within the threshold boundaries and VDD voltage is above UVLO. To assert a reset sense pins needs to meet the condition below:

- For undervoltage variant the SENSE voltage need to cross the lower boundary (V<sub>ITN</sub>).

- For overvoltage variant the SENSE voltage needs to cross the upper boundary (V<sub>ITP</sub>).

#### 8.3.3.4 Active-Low (RESET)

**RESET** (active low) denoted with a bar above the pin label. **RESET** remains high voltage ( $V_{OH}$ , deasserted) (open-drain variant  $V_{OH}$  is measured against the pullup voltage) as long as sense voltage is in normal operation within the threshold boundaries and VDD voltage is above UVLO. To assert a reset sense pins needs to meet the condition below:

- For undervoltage variant the SENSE voltage need to cross the lower boundary (V<sub>ITN</sub>).

- For overvoltage variant the SENSE voltage needs to cross the upper boundary (V<sub>ITP</sub>).

#### 8.3.4 User-Programmable Reset Time Delay

TPS37-Q1 has adjustable reset release time delay with external capacitors. Channel timing are independent of each other.

- A capacitor in CTR1 / MR program the reset time delay of Output 1.

- A capacitor in CTR2 / MR program the reset time delay of Output 2.

- No capacitor on these pins gives the fastest reset delay time indicated in the  $\ddagger$  7.6.

#### 8.3.4.1 Reset Time Delay Configuration

The time delay ( $t_{CTR}$ ) can be programmed by connecting a capacitor between CTR1 pin and GND, CTR2 for channel 2. In this section CTRx represent either channel 1 or channel 2.

The relationship between external capacitor C<sub>CTRx EXT (typ)</sub> and the time delay t<sub>CTRx (typ)</sub> is given by 方程式 1.

$t_{\text{CTRx (typ)}} = -\ln (0.28) \times R_{\text{CTRx (typ)}} \times C_{\text{CTRx}_{\text{EXT (typ)}}} + t_{\text{CTRx (no cap)}}$

(1)

R<sub>CTRx (typ)</sub> = is in kilo ohms (kOhms)

$C_{CTRx\_EXT (typ)}$  = is given in microfarads (  $\mu$  F)

$t_{CTRx (typ)}$  = is the reset time delay

The reset delay varies according to three variables: the external capacitor ( $C_{CTRx\_EXT}$ ), CTR pin internal resistance ( $R_{CTRx}$ ) provided in  $\ddagger$  7.5, and a constant. The minimum and maximum variance due to the constant is show in 5程式 2 and 5程式 3:

$$t_{\text{CTRx}(\text{min})} = -\ln(0.31) \times R_{\text{CTRx}(\text{min})} \times C_{\text{CTRx}_{\text{EXT}}(\text{min})} + t_{\text{CTRx}(\text{no cap}(\text{min}))}$$

(2)

$$t_{\text{CTRx (max)}} = -\ln(0.25) \times R_{\text{CTRx (max)}} \times C_{\text{CTRx}_{\text{EXT (max)}}} + t_{\text{CTRx (no cap (max))}}$$

(3)

The recommended maximum reset delay capacitor for the TPS37-Q1 is limited to 10  $\mu$  F as this ensures enough time for the capacitor to fully discharge when a voltage fault occurs. Also, having a too large of a capacitor value can cause very slow charge up (rise times) and system noise can cause the the internal circuit to trip earlier or later near the threshold. This leads to variation in time delay where it can make the delay accuracy worse in the presence of system noise.

When a voltage fault occurs, the previously charged up capacitor discharges and if the monitored voltage returns from the fault condition before the delay capacitor discharges completely, the delay will be shorter than expected. The capacitor will begin charging from a voltage above zero and resulting in shorter than expected time delay. A larger delay capacitor can be used so long as the capacitor has enough time to fully discharge during the duration of the voltage fault. To ensure the capacitor is fully discharged, the time period or duration of the voltage fault needs to be greater than 5% of the programmed reset time delay.

#### 8.3.5 User-Programmable Sense Delay

TPS37-Q1 has adjustable sense release time delay with external capacitors. Channel timing are independent of each other. Sense delay is used as a de-glitcher or ignoring known transients.

- A capacitor in CTS1 program the excursion detection on SENSE1.

- A capacitor in CTS2 program the excursion detection on SENSE2.

- No capacitor on these pins gives the fastest detection time indicated in the  $\ddagger$  7.6.

#### 8.3.5.1 Sense Time Delay Configuration

The time delay ( $t_{CTS}$ ) can be programmed by connecting a capacitor between CTS1 pin and GND, CTS2 for channel 2. In this section CTSx represent either channel 1 or channel 2.R

The relationship between external capacitor  $C_{CTSx EXT (typ)}$  and the time delay  $t_{CTSx (typ)}$  is given by  $\overline{5}$  at 4.

$t_{\text{CTSx (typ)}}$  = -In (0.28) x R<sub>CTSx (typ)</sub> x C<sub>CTSx\_EXT (typ)</sub> +  $t_{\text{CTSx (no cap)}}$

(4)

(6)

R<sub>CTSx</sub> = is in kilo ohms (kOhms)

$C_{CTSX EXT}$  = is given in microfarads (  $\mu$  F)

$t_{CTSx}$  = is the sense time delay

The sense delay varies according to three variables: the external capacitor ( $C_{CTSx\_EXT}$ ), CTS pin internal resistance ( $R_{CTSx}$ ) provided in  $\ddagger$  7.5, and a constant. The minimum and maximum variance due to the constant is show in 5程式 5 and 5程式 6:

$$t_{\text{CTSx (min)}} = -\ln (0.31) \times R_{\text{CTSx (min)}} \times C_{\text{CTSx}_{\text{EXT (min)}}} + t_{\text{CTSx (no cap (min))}}$$

(5)

The recommended maximum sense delay capacitor for the TPS37-Q1 is limited to 10  $\mu$  F as this ensures enough time for the capacitor to fully discharge when a voltage fault occurs. Also, having a too large of a capacitor value can cause very slow charge up (rise times) and system noise can cause the the internal circuit to trip earlier or later near the threshold. This leads to variation in time delay where it can make the delay accuracy worse in the presence of system noise.

When a voltage fault occurs, the previously charged up capacitor discharges and if the monitored voltage returns from the fault condition before the delay capacitor discharges completely, the delay will be shorter than expected. The capacitor will begin charging from a voltage above zero and resulting in shorter than expected time delay. A larger delay capacitor can be used so long as the capacitor has enough time between fault events to fully discharge during the duration of the voltage fault. To ensure the capacitor is fully discharged, the time period or time duration between fault events needs to be greater than 10% of the programmed sense time delay.

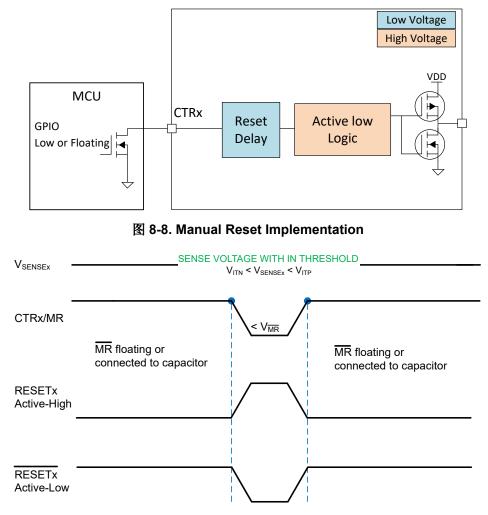

#### 8.3.6 Manual RESET (CTR1 / MR) and (CTR2 / MR) Input

The manual reset input allows a processor or other logic circuits to initiate a reset. In this section  $\overline{MR}$  is a generic reference to (CTR1 /  $\overline{MR}$ ) and (CTR2 /  $\overline{MR}$ ). A logic low on  $\overline{MR}$  causes  $\overline{RESET1}$  to assert on reset output. After  $\overline{MR}$  is left floating,  $\overline{RESET1}$  will release the reset if the voltage at SENSE1 pin is at nominal voltage.  $\overline{MR}$  should not be driven high, this pin should be left floating or connected to a capacitor to GND, this pin can be left unconnected if is not used.

If the logic driving the  $\overline{MR}$  cannot tri-state (floating and GND) then a logic-level FET should be used as illustrated in  $\underline{\otimes}$  8-8.

#### 图 8-9. Manual Reset Timing Diagram

#### 表 8-3. MR Functional Table

| MR        | SENSE ON NOMINAL VOLTAGE | RESET STATUS                                                       |

|-----------|--------------------------|--------------------------------------------------------------------|

| Low       | Yes                      | Reset asserted                                                     |

| Floating  | Yes                      | Fast reset release when SENSE voltage goes back to nominal voltage |

| Capacitor | Yes                      | Programmable reset time delay                                      |

| High      | Yes                      | NOT Recommended                                                    |

### 9 Device Functional Modes

|                                              | S                                       | ENSE                                                                                                                                                                                                                    |                                |                                    | OUTPUT <sup>(2)</sup> |  |  |  |  |

|----------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------|-----------------------|--|--|--|--|

| DESCRIPTION                                  | PREVIOUS<br>CONDITION CURRENT CONDITION |                                                                                                                                                                                                                         | CTR <sup>(1)</sup> / MR PIN    | VDD PIN                            | (RESET PIN)           |  |  |  |  |

| Normal Operation                             | SENSE > V <sub>ITN(UV)</sub>            | SENSE > V <sub>ITN(UV)</sub>                                                                                                                                                                                            | Open or capacitor<br>connected | $V_{DD} > V_{DD(MIN)}$             | High                  |  |  |  |  |

| Undervoltage<br>Detection                    | SENSE > V <sub>ITN(UV)</sub>            | SENSE < V <sub>ITN(UV)</sub>                                                                                                                                                                                            | Open or capacitor<br>connected | $V_{DD} > V_{DD(MIN)}$             | Low                   |  |  |  |  |

| Undervoltage<br>Detection                    | SENSE < V <sub>ITN(UV)</sub>            | $V_{\text{N}(\text{UV})} \qquad \text{SENSE} > V_{\text{ITN}(\text{UV})} \qquad \begin{array}{c} \text{Open or capacitor} \\ \text{connected} \end{array} \qquad V_{\text{DD}} > V_{\text{DD}(\text{MIN})} \end{array}$ |                                | $V_{DD} > V_{DD(MIN)}$             | Low                   |  |  |  |  |

| Normal Operation                             | SENSE < V <sub>ITN(UV)</sub>            | SENSE > V <sub>ITN(UV)</sub> + HYS                                                                                                                                                                                      | Open or capacitor<br>connected | $V_{DD} > V_{DD(MIN)}$             | High                  |  |  |  |  |

| Manual Reset                                 | SENSE > V <sub>ITN(UV)</sub>            | SENSE > V <sub>ITN(UV)</sub>                                                                                                                                                                                            | Low                            | $V_{DD} > V_{DD(MIN)}$             | Low                   |  |  |  |  |

| UVLO Engaged                                 | SENSE > V <sub>ITN(UV)</sub>            | SENSE > V <sub>ITN(UV)</sub>                                                                                                                                                                                            | Open or capacitor<br>connected | $V_{POR} < V_{DD} < V_{DD(MIN)}$   | Low                   |  |  |  |  |

| Below V <sub>POR</sub> ,<br>Undefined Output | SENSE > V <sub>ITN(UV)</sub>            | SENSE > V <sub>ITN(UV)</sub>                                                                                                                                                                                            | Open or capacitor<br>connected | V <sub>DD</sub> < V <sub>POR</sub> | Undefined             |  |  |  |  |

### 表 9-1. Undervoltage Detect Functional Mode Truth Table

(1) Reset time delay is ignored in the truth table.

(2) Open-drain active low output requires an external pull-up resistor to a pull-up voltage.

#### 表 9-2. Overvoltage Detect Functional Mode Truth Table

|                                              | S                                       | ENSE                               |                                                              |                                           | OUTPUT <sup>(2)</sup> |  |  |  |

|----------------------------------------------|-----------------------------------------|------------------------------------|--------------------------------------------------------------|-------------------------------------------|-----------------------|--|--|--|

| DESCRIPTION                                  | PREVIOUS<br>CONDITION CURRENT CONDITION |                                    | CTR <sup>(1)</sup> / MR PIN                                  | VDD PIN                                   | (RESET PIN)           |  |  |  |

| Normal Operation                             | SENSE < V <sub>ITN(OV)</sub>            | SENSE < V <sub>ITN(OV)</sub>       | SENSE < VITN(OV)Open or capacitor<br>connectedVDD > VDD(MIN) |                                           | High                  |  |  |  |

| Overvoltage<br>Detection                     | SENSE < V <sub>ITN(OV)</sub>            | SENSE > V <sub>ITN(OV)</sub>       | Open or capacitor<br>connected                               | $V_{DD} > V_{DD(MIN)}$                    | Low                   |  |  |  |

| Overvoltage<br>Detection                     | SENSE > V <sub>ITN(OV)</sub>            | SENSE < V <sub>ITN(OV)</sub>       | Open or capacitor<br>connected                               |                                           |                       |  |  |  |

| Normal Operation                             | SENSE > V <sub>ITN(OV)</sub>            | SENSE < V <sub>ITN(OV)</sub> - HYS | Open or capacitor<br>connected                               | $V_{DD} > V_{DD(MIN)}$                    | High                  |  |  |  |

| Manual Reset                                 | SENSE < V <sub>ITN(OV)</sub>            | SENSE < V <sub>ITN(OV)</sub>       | Low                                                          | $V_{DD} > V_{DD(MIN)}$                    | Low                   |  |  |  |

| UVLO Engaged                                 | SENSE < V <sub>ITN(OV)</sub>            | SENSE < V <sub>ITN(OV)</sub>       | Open or capacitor connected                                  | V <sub>POR</sub> < V <sub>DD</sub> < UVLO | Low                   |  |  |  |

| Below V <sub>POR</sub> ,<br>Undefined Output | SENSE < V <sub>ITN(OV)</sub>            | SENSE < V <sub>ITN(OV)</sub>       | Open or capacitor<br>connected                               | V <sub>DD</sub> < V <sub>POR</sub>        | Undefined             |  |  |  |

(1) Reset time delay is ignored in the truth table.

(2) Open-drain active low output requires an external pull-up resistor to a pull-up voltage.

### 10 Application and Implementation

#### Note

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客 户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

#### 10.1 Adjustable Voltage Thresholds

方程式 7 illustrates an example of how to adjust the voltage threshold with external resistor dividers. The resistors can be calculated depending on the desired voltage threshold and device part number. TI recommends using the 0.8 V voltage threshold device when using an adjustable voltage variant. This variant bypasses the internal resistor ladder.

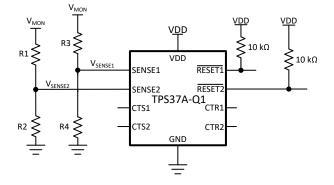

For example, consider a 12 V rail being monitored V<sub>MON</sub> for undervoltage (UV) using channel 2 of the TPS37A010122DSKRQ1 variant. Using 方程式 7 and shown in 图 10-1, R<sub>1</sub> is the top resistor of the resistor divider that is between V<sub>MON</sub> and V<sub>SENSE2</sub>, R<sub>2</sub> is the bottom resistor that is between V<sub>SENSE2</sub> and GND, V<sub>MON</sub> is the voltage rail that is being monitored and V<sub>SENSE2</sub> is the input threshold voltage. The monitored UV threshold, denoted as V<sub>MON</sub>, where the device will assert a reset signal occurs when V<sub>SENSE2</sub> = V<sub>IT-(UV)</sub> or, for this example, V<sub>MON</sub> = 10.8V which is 90% from 12 V. Using 方程式 7 and assuming R<sub>2</sub> = 10k  $\Omega$ , R<sub>1</sub> can be calculated shown in 方程式 8 where I<sub>R1</sub> is represented in 方程式 9:

$$V_{\text{SENSE2}} = V_{\text{MON-}} \times (R_2 \div (R_1 + R_2)) \tag{7}$$

$$R_1 = (V_{MON-} - V_{SENSE2}) \div I_{R1}$$

(8)

$$I_{R1} = I_{R2} = V_{SENSE2} \div R_2 \tag{9}$$

Substituting  $\overline{\beta}$ 程式 9 into  $\overline{\beta}$ 程式 8 and solving for R<sub>1</sub> in  $\overline{\beta}$ 程式 7, R<sub>1</sub> = 125k  $\Omega$ . The TPS37A010122DSKRQ1 is typically meant to monitor a 0.8 V rail with ±2% voltage threshold hysteresis. For the reset signal to become deasserted, V<sub>MON</sub> would need to go above V<sub>IT-</sub> + V<sub>HYS</sub>. For this example, V<sub>MON</sub> = 11.016 V when the reset signal becomes deasserted.

There are inaccuracies that must be taken into consideration while adjusting voltage thresholds. Aside from the tolerance of the resistor divider, there is an internal resistance of the SENSE pin that may affect the accuracy of the resistor divider. Although expected to be very high impedance, users are recommended to calculate the values for the design specifications. The internal SENSE resistance  $R_{SENSE}$  can be calculated by the SENSE voltage  $V_{SENSE}$  divided by the SENSE current  $I_{SENSE}$  as shown in 方程式 11.  $V_{SENSE}$  can be calculated using 方程式 7 depending on the resistor divider and monitored voltage.  $I_{SENSE}$  can be calculated using 方程式 10.

$$I_{\text{SENSE}} = [(V_{\text{MON}} - V_{\text{SENSE}}) \div R_1] - (V_{\text{SENSE}} \div R_2)$$

(10)

$R_{SENSE} = V_{SENSE} \div I_{SENSE}$

图 10-1. Adjustable Voltage Threshold with External Resistor Dividers

(11)

### **10.2 Application Information**

The following sections describe in detail how to properly use this device, depending on the requirements of the final application.

#### **10.3 Typical Application**

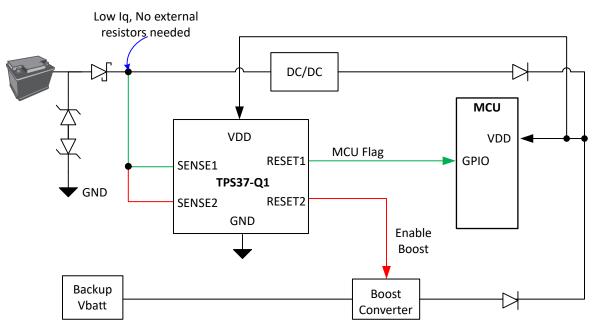

#### 10.3.1 Design 1: Automotive Off-Battery Monitoring

The initial power stage in automotive applications starts with the 12 V battery. Variation of the battery voltage is common between 9 V and 16 V. Furthermore, if cold-cranking and load dump conditions are considered, voltage transients can occur as low as 3 V and as high as 42 V. In this design example, we are highlighting the ability for low power, direct off-battery voltage supervision.  $\mathbb{K}$  10-2 illustrates an example of how the TPS37-Q1 is monitoring the battery voltage while being powered by it, as well. For more information, read this *application report* on how to achieve low I<sub>Q</sub> voltage supervision in automotive, wide-V<sub>IN</sub> applications.

图 10-2. Fast Start Window Supervisor with Direct Off-Battery Monitoring

### 10.3.1.1 Design Requirements

This design requires voltage supervision on a 12 V power supply voltage rail with possibility of the 12 V rail rising up as high as 42 V. The undervoltage fault occurs when the power supply voltage drops below 7.7 V.

| PARAMETER                                 | DESIGN REQUIREMENT                                                                           | DESIGN RESULT                                                                                                                    |

|-------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Power Rail Voltage Supervision            | Monitor 12-V power supply for undervoltage condition, trigger a undervoltage fault at 7.7 V. | TPS37-Q1 provides voltage monitoring with 1.5% max accuracy with adjustable/non-adjustable variations.                           |

| Maximum Input Power                       | Operate with power supply input up to 42 V.                                                  | The TPS37-Q1 can support a VDD of up to 65 V.                                                                                    |

| Output logic voltage                      | Open-Drain Output Topology                                                                   | An open-drain output is recommended to provide<br>the correct reset signal, but a push-pull can also be<br>used.                 |

| Maximum system current consumption        | 2 μA max when power supply is at 12 V typical                                                | TPS37-Q1 allows for $I_Q$ to remain low with support of up to 65 V. This allows for no external resistor divider to be required. |

| Voltage Monitor Accuracy                  | Maximum voltage monitor accuracy of 1.5%.                                                    | The TPS37-Q1 has 1.5% maximum voltage monitor accuracy.                                                                          |

| Delay when returning from fault condition | RESET delay of at least 420 ms when returning from a undervoltage fault.                     | C <sub>CTR</sub> = 0.33 μF sets 422 ms delay                                                                                     |

### 10.3.1.2 Detailed Design Procedure

The primary advantage of this application is being able to directly monitor a voltage on an automotive battery without needing external resistor dividers on the SENSEx inputs. This keeps the overall  $I_Q$  of the design low while still achieving the desired rail monitoring.

As shown in [8] 10-2, rail monitoring is done by connecting SENSE1 and SENSE2 inputs directly to the battery rail after the TVS protection diodes. The TPS37-Q1 that is being used in this example is a fixed voltage variant where SENSE1 and SENSE 2 threshold voltages have been set internally by the factory. Word of caution, the TVS protection diodes must be chosen such that the transient voltages on the monitored rails do not exceed the absolute max limit listed in  $\ddagger$  7.1.

To use this configuration, the specific voltage threshold variation of the device must be chosen according to the application. In this configuration, the '77' variation must be chosen for 7.7 V as shown in  $\frac{13}{12}$ .

The device being able to handle 65 V on VDD means the monitored voltage rail can go as high as 42 V for the application transients and not violate the recommended maximum for the supervisor as it usually would. This is useful when monitoring a voltage rail that has a wide range that may go much higher than the nominal rail voltage such as in this case. Good design practice recommends using a 0.1  $\mu$ F capacitor on the VDD pin and this capacitance may need to increase if using an adjustable version with a resistor divider.

### **11 Power Supply Recommendations**

These devices are designed to operate from an input supply with a voltage range between 1.4 V ( $V_{POR}$ ) to 65 V (max operation). Good analog design practice recommends placing a minimum 0.1  $\mu$ F ceramic capacitor as near as possible to the VDD pin.

#### **11.1 Power Dissipation and Device Operation**

The permissible power dissipation for any package is a measure of the capability of the device to pass heat from the power source, the junctions of the IC, to the ultimate heat sink, the ambient environment. Thus, the power dissipation is dependent on the ambient temperature and the thermal resistance across the various interfaces between the die junction and ambient air.

The maximum continuous allowable power dissipation for the device in a given package can be calculated using 方程式 12:

| $P_{D\text{-}MAX} = ((T_{J\text{-}MAX} - T_{A}) / R_{\theta}_{JA})$ | (12) |

|---------------------------------------------------------------------|------|

|                                                                     |      |

The actual power being dissipated in the device can be represented by 方程式 13:

| $P_D = V_{DD} \times I_{DD} + p_{RESET}$ | (13) |

|------------------------------------------|------|

|                                          |      |

p<sub>RESET</sub> is calculated by 方程式 14 or 方程式 15

$p_{\text{RESET}(\text{PUSHPULL})} = \text{VDD} - \text{V}_{\text{RESET}} \times \text{I}_{\text{RESET}}$

$p_{\text{RESET (OPEN-DRAIN)}} = V_{\text{RESET}} \times I_{\text{RESET}}$

方程式 12 and 方程式 13 establish the relationship between the maximum power dissipation allowed due to thermal consideration, the voltage drop across the device, and the continuous current capability of the device. These two equations should be used to determine the optimum operating conditions for the device in the application.

In applications where lower power dissipation (P<sub>D</sub>) and/or excellent package thermal resistance (R  $_{\theta}$  JA) is present, the maximum ambient temperature (T<sub>A-MAX</sub>) may be increased.

In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature ( $T_{A-MAX}$ ) may have to be de-rated.  $T_{A-MAX}$  is dependent on the maximum operating junction temperature ( $T_{J-MAX-OP} = 125^{\circ}$ C), the maximum allowable power dissipation in the device package in the application ( $P_{D-MAX}$ ), and the junction-to ambient thermal resistance of the part/package in the application ( $R_{0,JA}$ ), as given by  $\overline{\beta}$ 程式 16:

$T_{A-MAX} = (T_{J-MAX-OP} - (R_{\theta}_{JA} \times P_{D-MAX}))$

(16)

(14)

(15)

### 12 Layout

### 12.1 Layout Guidelines

- Make sure that the connection to the VDD pin is low impedance. Good analog design practice is to place a greater than 0.1 μF ceramic capacitor as near as possible to the VDD pin.

- To further improve the noise immunity on the SENSEx pins, placing a 10 nF to 100 nF capacitor between the SENSEx pins and GND can reduce the sensitivity to transient voltages on the monitored signal.

- If a capacitor is used on CTS1, CTS2, CTR1, or CTR2, place these components as close as possible to the respective pins. If the capacitor adjustable pins are left unconnected, make sure to minimize the amount of parasitic capacitance on the pins to less than 5 pF.

- For open-drain variants, place the pull-up resistors on RESET1 and RESET2 pins as close to the pins as possible.

- When laying out metal traces, separate high voltage traces from low voltage traces as much as possible. If high and low voltage traces need to run close by, spacing between traces should be greater than 20 mils (0.5 mm).