**TPS650864**

ZHCSG44E - JUNE 2017 - REVISED DECEMBER 2022

# TPS650864 适用于 Xilinx<sup>®</sup> MPSoC 和 FPGA 的可配置多轨 PMU

# 1 特性

**TEXAS**

5.6V 至 21V 的宽 V<sub>IN</sub> 范围

INSTRUMENTS

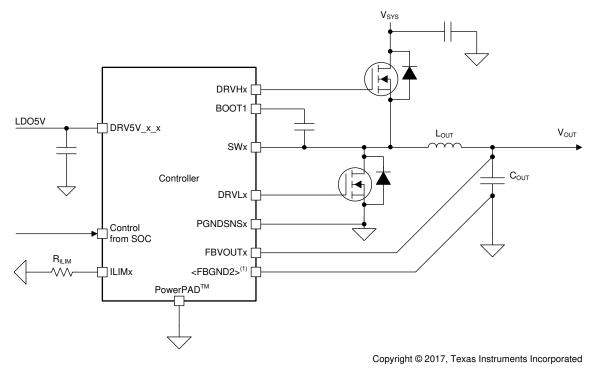

- 三个采用 D-CAP2™ 拓扑的 可变输出电压同步降压控制器

- 使用外部 FET 的可扩展输出电流,支持可选电 流限制

- 在 0.41V 至 1.67V 之间以 10mV 为步长或 在 1V 至 3.575V 之间以 25mV 为步长的 I<sup>2</sup>C DVS 控制

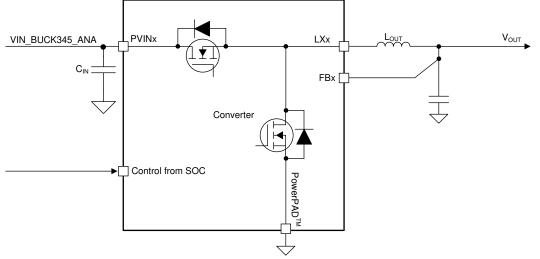

- 三个采用 DCS-Control 拓扑的可变输出电压同步降 压转换器

- 输入电压范围为 3V 至 5.5 V

- 输出电流高达 3A

- 在 0.41V 至 1.67V 之间以 10mV 为步长或 在 0.425V 至 3.575V 之间以 25mV 为步长的 I<sup>2</sup>C DVS 控制

- 三个具有可调节输出电压的 LDO 稳压器

- LDOA1: I<sup>2</sup>C 可选电压的范围为 1.35V 至 3.3V,输出电流可高达 200mA

- LDOA2 和 LDOA3: I<sup>2</sup>C 可选电压的范围为 0.7V 至 1.5V,每个的输出电流可高达 600mA

- 用于 DDR 存储器终端的 VTT LDO

- 三个具有压摆率控制功能的负载开关

- 输出电流高达 300mA, 压降小于标称输入电压 的 1.5%

- 输入电压为 1.8V 时, R<sub>DSON</sub> < 96m Ω

- 5V 固定输出电压 LDO (LDO5)

- 用于 SMPS 的栅极驱动器和 LDOA1 的电源

- 可自动切换至外部 5V 降压以实现更高效率

- 内置可通过工厂 OTP 编程功能实现的灵活性和可配 置性

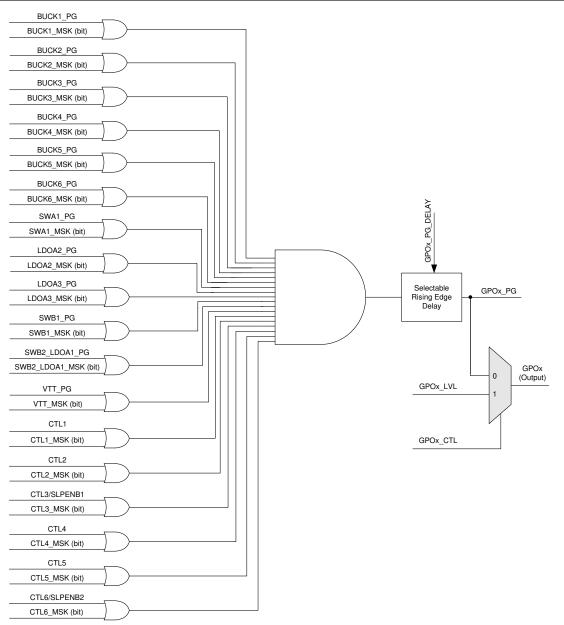

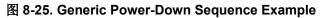

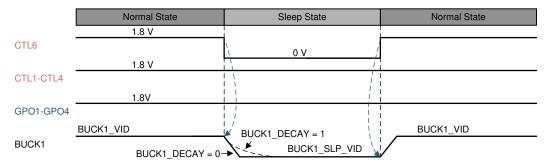

- 六个 GPI 引脚均可配置为启用 ( CTL1 至 CTL6)任意所选电压轨或使其进入睡眠模式 (CTL3 和 CTL6)

- 四个 GPO 引脚均可配置为指示任意所选轨道的 电源正常

- 漏极开路中断输出引脚

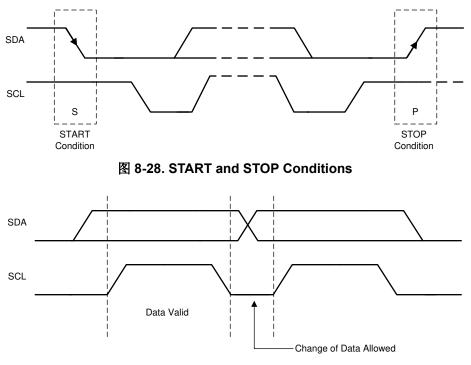

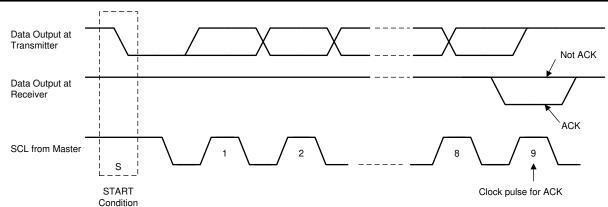

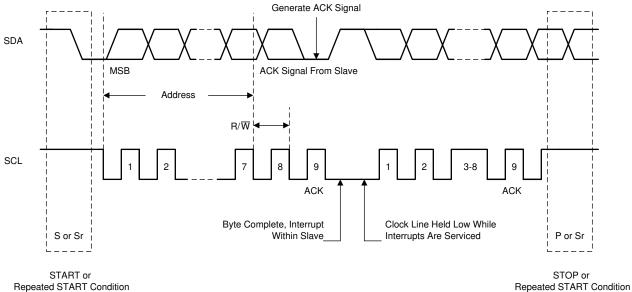

- I<sup>2</sup>C 接口支持标准模式 (100kHz)、快速模式 (400kHz) 和超快速模式 (1MHz)

# 2 应用

- 可编程逻辑控制器

- 机器视觉摄像机

- 视频监控

- 测试和测量

- 嵌入式 PC

- 运动控制

- 便携式超声波设备

# 3 说明

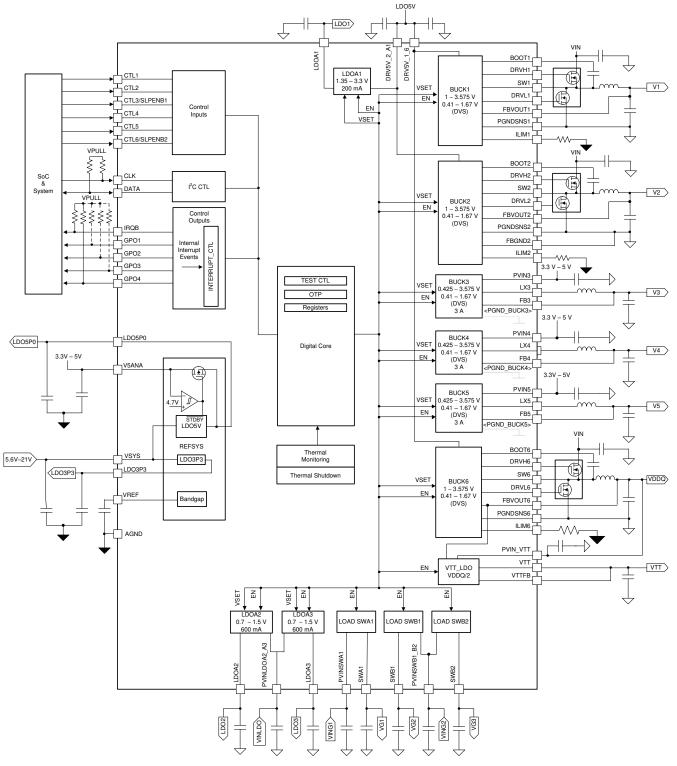

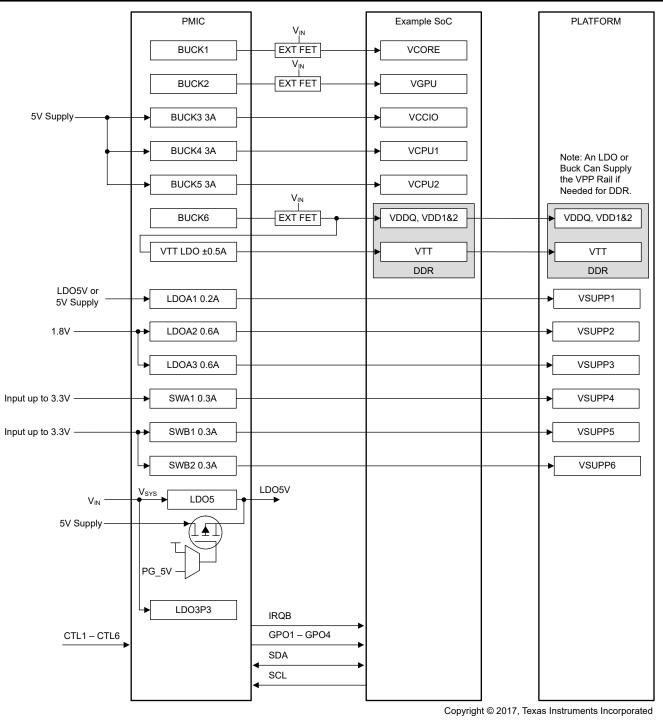

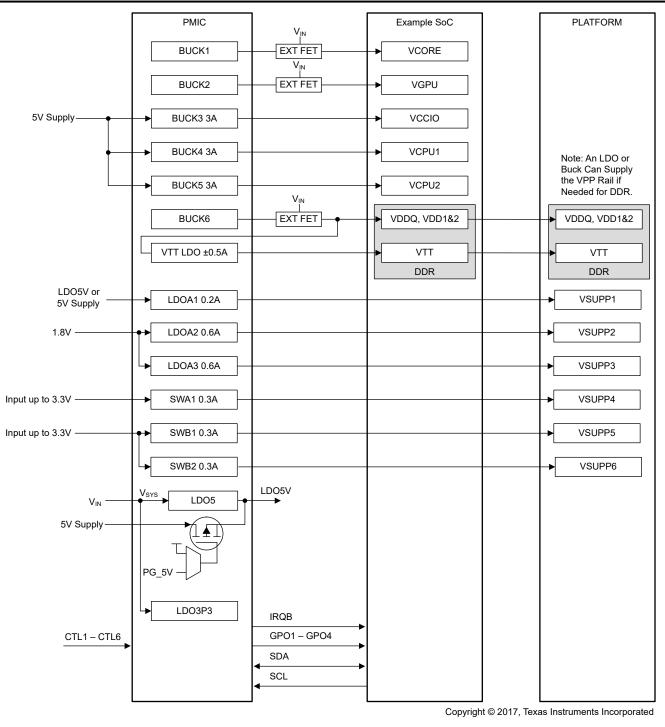

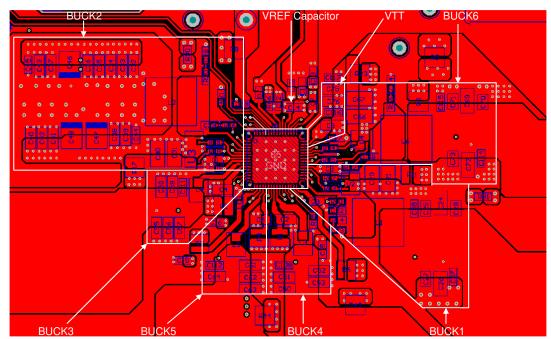

TPS650864 器件系列是一款单芯片电源管理 IC (PMIC),专为 Xilinx Zyng<sup>®</sup> 多处理器片上系统 (MPSoC) 和现场可编程门阵列 (FPGA) 系列而设计。 TPS650864 器件的输入电压范围为 5.6V 至 21V, 支 持广泛的应用(请参阅器件比较表)。该器件适用于壁 式供电应用或 2、3、4 节串联锂离子电池包 (NVDC 或非 NVDC 电源架构)。有关 5V 输入电源的信息, 请参阅典型应用部分。D-CAP2和 DCS-Control 高频 稳压器采用小型无源器件,用于减小解决方案尺寸。 D-CAP2 和 DCS-Control 拓扑具有出色的瞬态响应性 能,非常适用于具有快速负载开关的处理器内核和系统 内存电压轨。I<sup>2</sup>C 接口可通过嵌入式控制器 (EC) 或 SoC 进行轻松控制。PMIC 的尺寸为 8mm × 8mm, 采 用单行 VQFN 封装,所带的散热垫可改善散热功能。

#### 器件信息<sup>(1)</sup>

| 器件型号                     | 封装        | 封装尺寸 (标称值)      |

|--------------------------|-----------|-----------------|

| TPS650864 <sup>(2)</sup> | VQFN (64) | 8.00mm x 8.00mm |

如需更多信息,请参阅机械、封装和可订购信息部分。 (1)

有关器件选项,请参阅器件比较表。 (2)

#### TPS650864 ZHCSG44E - JUNE 2017 - REVISED DECEMBER 2022

# **Table of Contents**

| 1 | 特性1                                              |

|---|--------------------------------------------------|

| 2 | 应用1                                              |

| 3 | 说明1                                              |

|   | Revision History                                 |

| 5 | Device Comparison Table5                         |

|   | Pin Configuration and Functions                  |

|   | Specifications                                   |

|   | 7.1 Absolute Maximum Ratings                     |

|   | 7.2 ESD Ratings                                  |

|   | 7.3 Recommended Operating Conditions10           |

|   | 7.4 Thermal Information10                        |

|   | 7.5 Electrical Characteristics: Total Current    |

|   | Consumption10                                    |

|   | 7.6 Electrical Characteristics: Reference and    |

|   | Monitoring System11                              |

|   | 7.7 Electrical Characteristics: Buck Controllers |

|   | 7.8 Electrical Characteristics: Synchronous Buck |

|   | Converters13                                     |

|   | 7.9 Electrical Characteristics: LDOs             |

|   | 7.10 Electrical Characteristics: Load Switches   |

|   | 7.11 Digital Signals: I <sup>2</sup> C Interface |

|   | 7.12 Digital Input Signals (CTLx)                |

|   | 7.13 Digital Output Signals (IRQB, GPOx)         |

|   | 7.14 Timing Requirements                         |

|   | 7.15 Switching Characteristics                   |

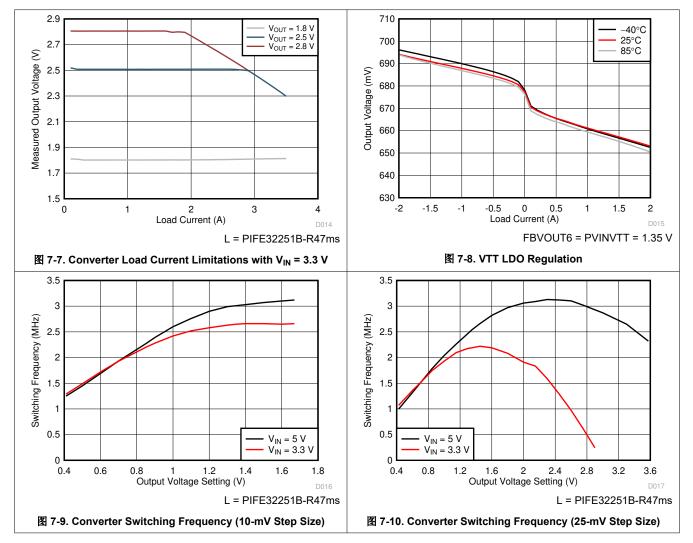

| ~ | 7.16 Typical Characteristics                     |

| 8 | Detailed Description                             |

|   | 8.1 Overview                                     |

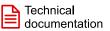

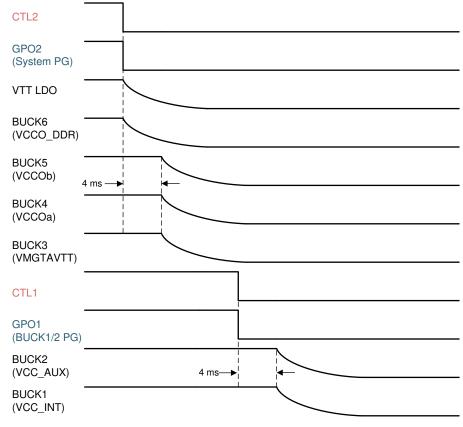

| 8.2 Functional Block Diagram                  |                 |

|-----------------------------------------------|-----------------|

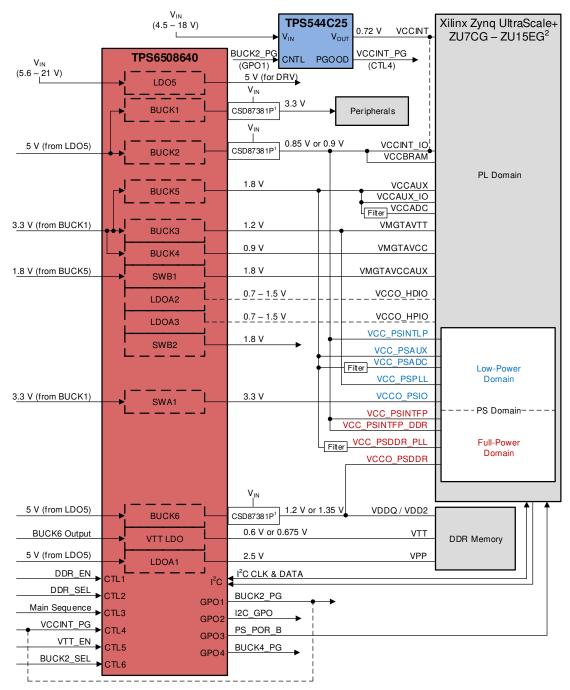

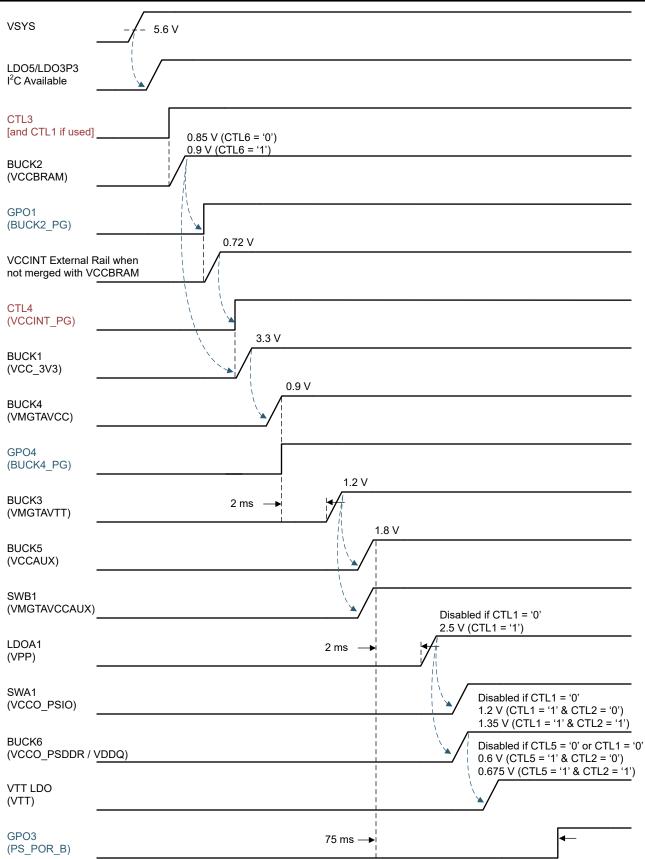

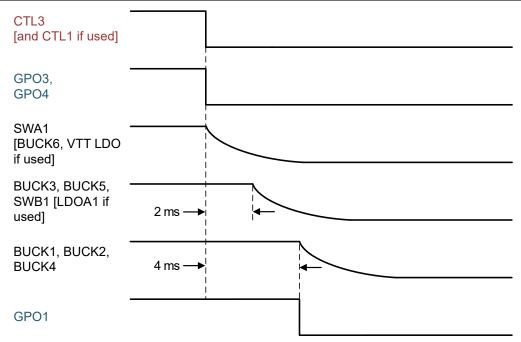

| 8.3 TPS6508640 Design and Settings            | <mark>24</mark> |

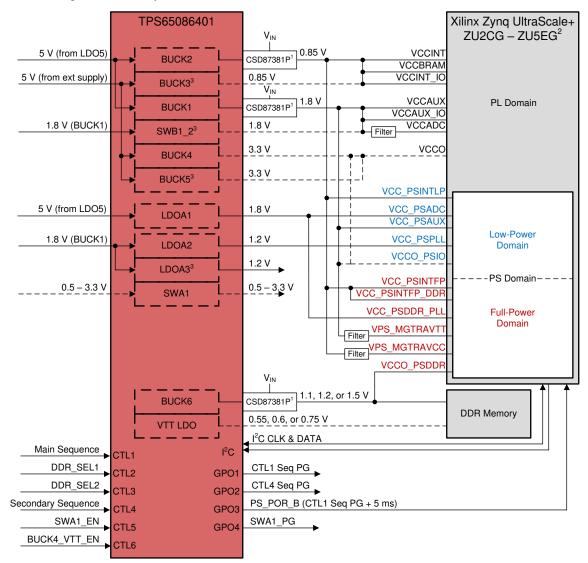

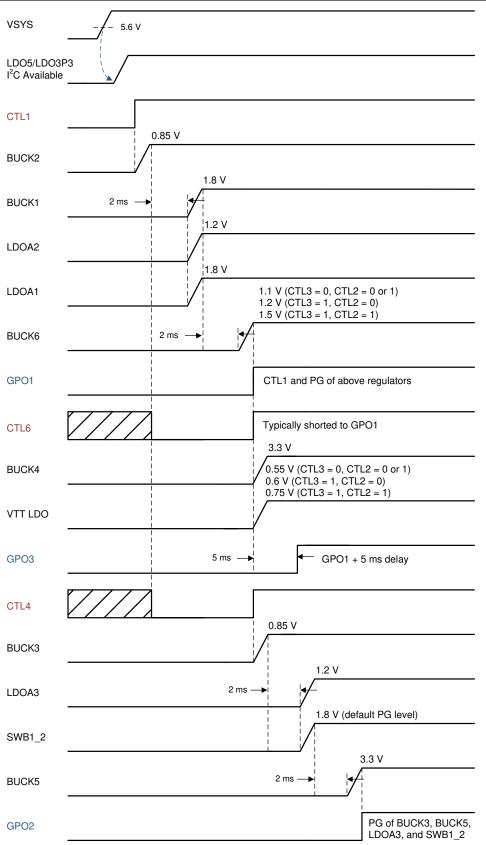

| 8.4 TPS65086401 Design and Settings           | 29              |

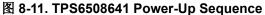

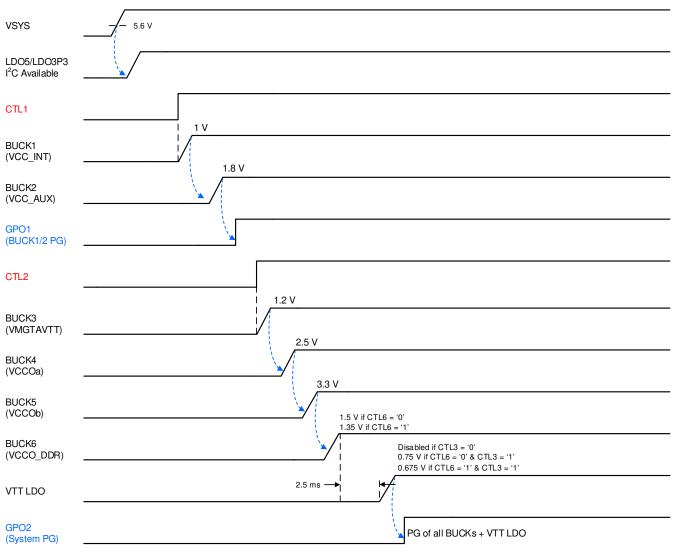

| 8.5 TPS6508641 Design and Settings            |                 |

| 8.6 TPS65086470 Design and Settings           |                 |

| 8.7 SMPS Voltage Regulators                   | 43              |

| 8.8 LDOs and Load Switches                    |                 |

| 8.9 Power Goods (PGOOD or PG) and GPOs        |                 |

| 8.10 Power Sequencing and VR Control          |                 |

| 8.11 Device Functional Modes                  |                 |

| 8.12 I <sup>2</sup> C Interface               | <mark>58</mark> |

| 8.13 Register Maps                            |                 |

| 9 Applications, Implementation, and Layout    |                 |

| 9.1 Application Information                   |                 |

| 9.2 Typical Application                       |                 |

| 9.3 Power Supply Coupling and Bulk Capacitors |                 |

| 9.4 Do's and Don'ts                           |                 |

| 10 Device and Documentation Support           |                 |

| 10.1 Device Support                           |                 |

| 10.2 Documentation Support                    |                 |

| 10.3 接收文档更新通知                                 |                 |

| 10.4 支持资源                                     |                 |

| 10.5 Trademarks                               |                 |

| 10.6 Electrostatic Discharge Caution          |                 |

| 10.7 术语表                                      | 120             |

| 11 Mechanical, Packaging, and Orderable       |                 |

| Information                                   | 121             |

|                                               |                 |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| C | nanges from Revision D (November 2020) to Revision E (December 2022) Page                                                                                          |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

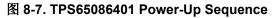

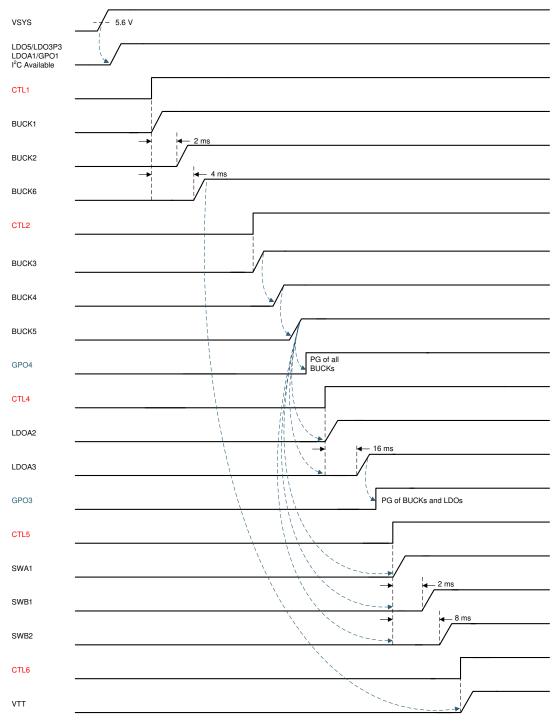

| • | Changed the power-up sequence for TPS6508640 in the <i>TPS6508640 Power-Up Sequence</i> diagram                                                                    |

| • | Changed the OTP_VERSION[1:0] bits from 01 to 10 for the TPS6508640 device in the DEVICEID2 Register table                                                          |

| • | Changed the OTP_VERSION[1:0] bits from 00 to 01 for the TPS65086401 and TPS6506470 devices in the<br>DEVICEID2 Register table                                      |

| С | nanges from Revision C (June 2018) to Revision D (November 2020) Page                                                                                              |

| • | 更新了整个文档中的表格、图和交叉参考的编号格式1                                                                                                                                           |

| • | Changed the incorrect LX3 pin description from <i>connect to ground when not in use</i> to <i>leave floating when not in use</i> in the <i>Pin Functions</i> table |

| • | Removed the line above the LDOA1 block in the PMIC Functional Block Diagram                                                                                        |

| • | Removed incorrect VREF notes from the middle and right DDR blocks in the Power Map Example figure 22                                                               |

| • | Added when configured as push-pull, LDO3P3 is used for logic-level high to the Power Good Tree figure description                                                  |

| • | Changed the bit values for BUCK4_MODE bits in the BUCK4CTRL Register table from 0 to 1 for the TPS65086401 and TPS65086470 devices                                 |

| • | Changed the bit values for BUCK5_MODE bits in the BUCK5CTRL Register table from 0 to 1 for the TPS65086401 and TPS65086470 devices                                 |

TPS650864 ZHCSG44E - JUNE 2017 - REVISED DECEMBER 2022

| C | nanges from Revision B (December 2017) to Revision C (June 2018)                                                                                                                                 | Page     |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| • | 向数据手册添加了 TPS6508640 和 TPS6508641                                                                                                                                                                 |          |

| • | Added typical MPSoC variants to Device Comparison Table                                                                                                                                          | <b>5</b> |

| • | Added BUCKx_MODE test condition for quiescent current                                                                                                                                            | 13       |

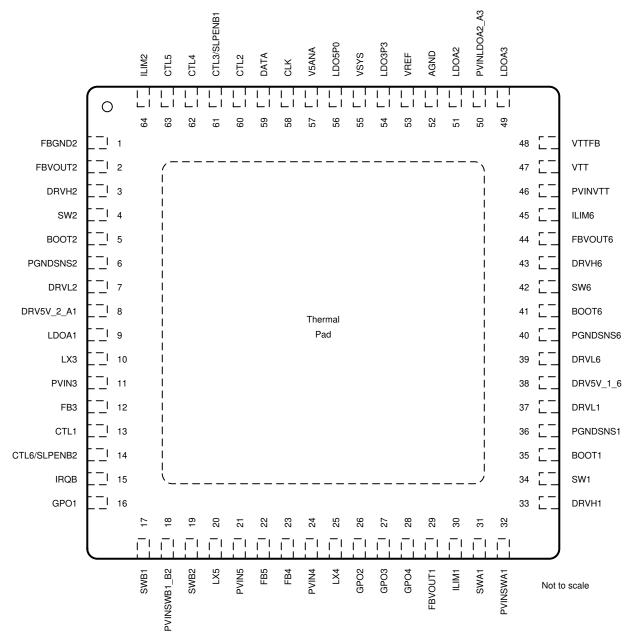

| • | Added BUCKx_MODE information to relevant graphs                                                                                                                                                  | 19       |

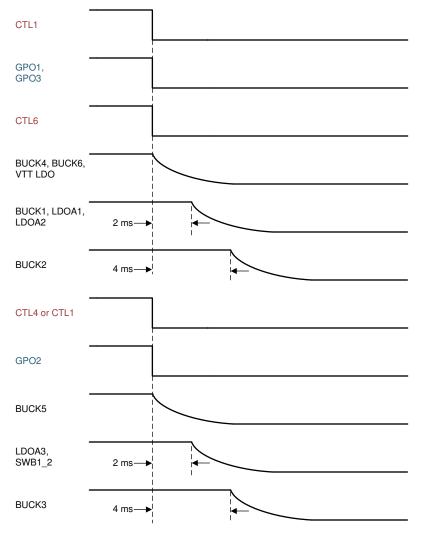

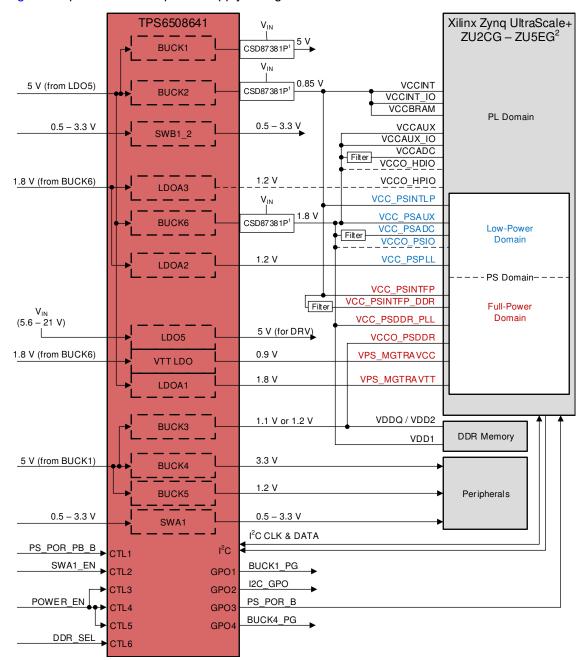

| • | Changed the TPS65086401 Power Map Example in the TPS65086401 Design and Settings section                                                                                                         | 29       |

| • | Changed the TPS65086470 Power Map Example in the TPS65086470 Design and Settings section                                                                                                         |          |

| • | Added information regarding ILIM resistor minimum value for Force PWM condition                                                                                                                  | 50       |

| С | nanges from Revision A (November 2017) to Revision B (December 2017)                                                                                                                             | Page     |

| • | Changed TPS65086401 from preview to production data                                                                                                                                              | 5        |

| С | nanges from Revision * (February 2017) to Revision A (November 2017)                                                                                                                             | Page     |

| • | 将器件状态从"产品预发布"更改为"量产数据"                                                                                                                                                                           | 1        |

| • | Added pin connection when unused                                                                                                                                                                 | 6        |

| • | Changed the TPS65086401 Power Map Example in the TPS65086401 Design and Settings section                                                                                                         | 29       |

| • | Fixed SWB1 and SWB2 current to 0.4A from 0.3A                                                                                                                                                    | 39       |

| • | Changed typo from TPS6508470 to TPS65086470                                                                                                                                                      | 42       |

| • | Changed description to <i>Sleep State</i> from <i>Connected Standby</i> for consistency in the <i>Sleep State Entry Exit</i> section                                                             |          |

| • | Changed the description of all PGOODs in the note in the <i>Sleep State Entry and Exit</i> section from <i>sta stay</i> because the behavior can vary based on the part-number specific settings | •        |

| • | Added failure to reach power good within 10 ms as emergency shutdown condition to the <i>Emergency Shutdown</i> section                                                                          |          |

| • | Changed bit 0 in the BUCK3VID Register register to Read only (R)                                                                                                                                 |          |

| • | Changed the PG_DELAY2: 2nd Power Good Delay Register description from GPO3 to GPO1, GPO2,                                                                                                        |          |

٠

# **5** Device Comparison Table

**5**-1 lists a brief summary of the default values for each part number stored in one-time programmable (OTP) memory. A full summary of each part number can be found in the applications section linked in the *SECTION* column. The step size is indicated by the values in parenthesis. If alternate voltages are available through pin-strapping, they are separated with a comma.

| PART NUMBER | APPLICATION                                             | BUCK1            | BUCK2                    | BUCK3                   | BUCK4            | BUCK5            | BUCK6                             | LDOA1 | LDOA2 | LDOA3 | SECTION |

|-------------|---------------------------------------------------------|------------------|--------------------------|-------------------------|------------------|------------------|-----------------------------------|-------|-------|-------|---------|

| TPS6508640  | Xilinx Zynq<br>Ultrascale+<br>ZU7 - ZU15 <sup>(1)</sup> | 3.3 V<br>(25 mV) | 0.85 V, 0.9 V<br>(10 mV) | 1.2 V<br>(25 mV)        | 0.9 V<br>(25 mV) | 1.8 V<br>(25 mV) | 1.2 V, 1.35 V<br>(10 mV)          | 2.5 V | 1.5 V | 1.2 V | 节 8.3   |

| TPS65086401 | Xilinx Zynq<br>Ultrascale+<br>ZU2 - ZU5 <sup>(1)</sup>  | 1.8 V<br>(25 mV) | 0.85 V<br>(10 mV)        | 0.85 V<br>(25 mV)       | 3.3 V<br>(25 mV) | 3.3 V<br>(25 mV) | 1.5 V, 1.2 V,<br>1.1 V<br>(10 mV) | 1.8 V | 1.2 V | 1.2 V | 节 8.4   |

| TPS6508641  | Xilinx Zynq<br>Ultrascale+<br>ZU2 - ZU5 <sup>(1)</sup>  | Ext FB           | 0.85 V<br>(10 mV)        | 1.1 V, 1.2 V<br>(25 mV) | 3.3 V<br>(25 mV) | 1.2 V<br>(25 mV) | 1.8 V<br>(25 mV)                  | 1.8 V | 1.2 V | 1.2 V | 节 8.5   |

| TPS65086470 | Xilinx<br>Artix 7 <sup>(1)</sup>                        | 1 V<br>(10 mV)   | 1.8 V<br>(25 mV)         | 1.2 V<br>(25 mV)        | 2.5 V<br>(25 mV) | 3.3 V<br>(25 mV) | 1.35 V, 1.5 V<br>(25 mV)          | 1.8 V | 0.7 V | 0.7 V | 节 8.6   |

#### 表 5-1. Default Values

(1) Indicates the original intent of the part number. Parts can be used for alternate applications.

# 6 Pin Configuration and Functions

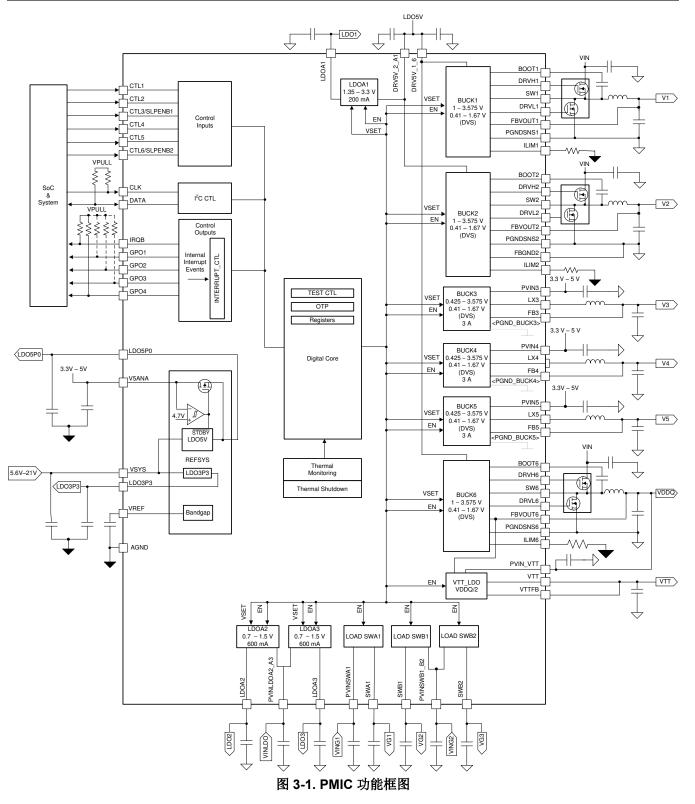

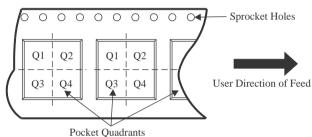

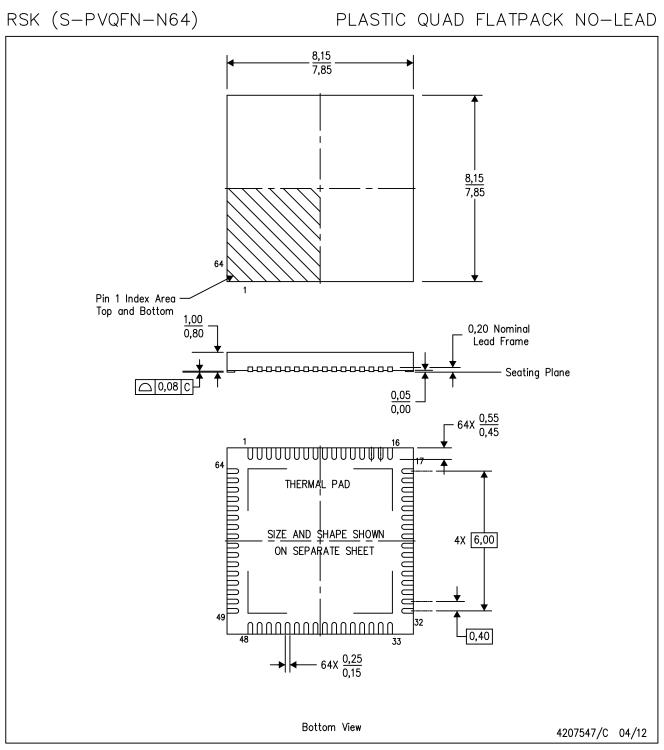

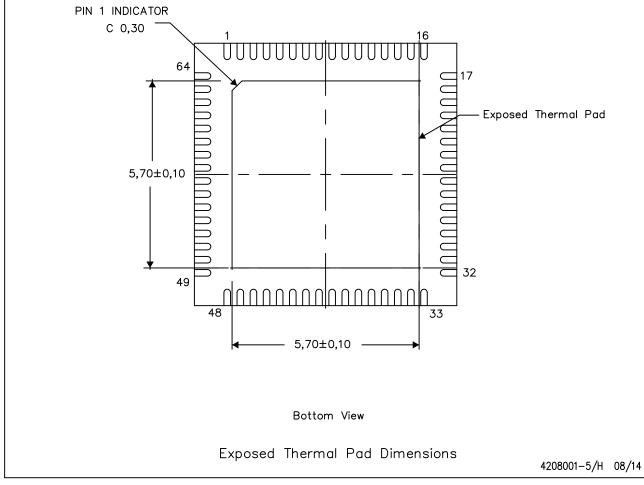

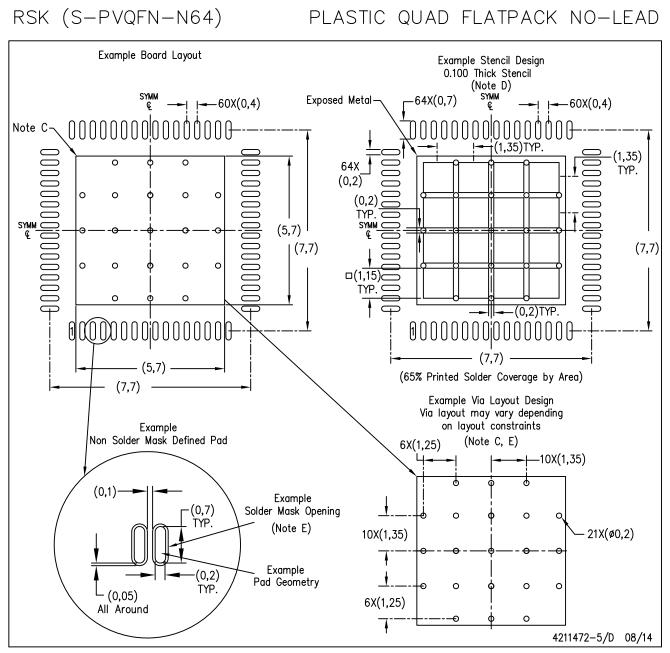

8 6-1 shows the 64-pin RSK Plastic Quad Flatpack No-Lead package.

The thermal pad must be connected to the system power ground plane.

### 图 6-1. 64-Pin RSK VQFN With Exposed Thermal Pad (Top View)

#### 表 6-1. Pin Functions

| DESCRIPTION                             |  |  |  |

|-----------------------------------------|--|--|--|

|                                         |  |  |  |

|                                         |  |  |  |

| erminal of output capacitor. Connect to |  |  |  |

| ninal of output capacitor. Connect to   |  |  |  |

| ISE.                                    |  |  |  |

|                                         |  |  |  |

## 表 6-1. Pin Functions (continued)

|       | PIN             | I/O | DESCRIPTION                                                                                                                                                                                              |  |  |  |  |

|-------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO.   | NAME            | 1/0 | DESCRIPTION                                                                                                                                                                                              |  |  |  |  |

| 4     | SW2             | I   | Switch node connection for BUCK2 controller. Connect to ground when not in use.                                                                                                                          |  |  |  |  |

| 5     | BOOT2           | I   | Bootstrap pin for BUCK2 controller. Connect a 100-nF ceramic capacitor between this pin and SW2 pin. Leave floating when not in use.                                                                     |  |  |  |  |

| 6     | PGNDSNS2        | I   | Power GND connection for BUCK2. Connect to ground terminal of external low-side FET. Connect to ground when not in use.                                                                                  |  |  |  |  |

| 7     | DRVL2           | 0   | Low-side gate driver output for BUCK2 controller. Leave floating when not in use.                                                                                                                        |  |  |  |  |

| 8     | DRV5V_2_A1      | I   | 5-V supply to BUCK2 gate driver and LDOA1. Bypass to ground with a 2.2-μF (typical) ceramic capacitor. Shorted on board to LDO5P0 pin typically. Bypass not required if BUCK2 and LDOA1 are not in use.  |  |  |  |  |

| 10    | LX3             | 0   | Switch node connection for BUCK3 converter. Leave floating when not in use.                                                                                                                              |  |  |  |  |

| 11    | PVIN3           | I   | Power input to BUCK3 converter. Bypass to ground with a 10-µF (typical) ceramic capacitor. Bypass not required if BUCK3 is not in use.                                                                   |  |  |  |  |

| 12    | FB3             | I   | Remote feedback sense for BUCK3 converter. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                          |  |  |  |  |

| 20    | LX5             | 0   | Switch node connection for BUCK5 converter. Leave floating when not in use.                                                                                                                              |  |  |  |  |

| 21    | PVIN5           | I   | Power input to BUCK5 converter. Bypass to ground with a 10-µF (typical) ceramic capacitor. Bypass not required if BUCK5 is not in use.                                                                   |  |  |  |  |

| 22    | FB5             | I   | Remote feedback sense for BUCK5 converter. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                          |  |  |  |  |

| 23    | FB4             | I   | Remote feedback sense for BUCK4 converter. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                          |  |  |  |  |

| 24    | PVIN4           | I   | Power input to BUCK4 converter. Bypass to ground with a 10-µF (typical) ceramic capacitor. Bypass not required if BUCK4 is not in use.                                                                   |  |  |  |  |

| 25    | LX4             | 0   | Switch node connection for BUCK4 converter. Leave floating when not in use.                                                                                                                              |  |  |  |  |

| 29    | FBVOUT1         | I   | Remote feedback sense for BUCK1 controller. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                         |  |  |  |  |

| 30    | ILIM1           | I   | Current limit set pin for BUCK1 controller. Fit a resistor from this pin to ground to set current limit of external low-side FET. Connect to ground when BUCK1 not in use.                               |  |  |  |  |

| 33    | DRVH1           | 0   | High-side gate driver output for BUCK1 controller. Leave floating when not in use.                                                                                                                       |  |  |  |  |

| 34    | SW1             | I   | Switch node connection for BUCK1 controller. Connect to ground when not in use.                                                                                                                          |  |  |  |  |

| 35    | BOOT1           | I   | Bootstrap pin for BUCK1 controller. Connect a 100-nF ceramic capacitor between this pin and SW1 pin. Leave floating when not in use.                                                                     |  |  |  |  |

| 36    | PGNDSNS1        | I   | Power GND connection for BUCK1. Connect to ground terminal of external low-side FET. Connect to ground when not in use.                                                                                  |  |  |  |  |

| 37    | DRVL1           | 0   | Low-side gate driver output for BUCK1 controller. Leave floating when not in use.                                                                                                                        |  |  |  |  |

| 38    | DRV5V_1_6       | I   | 5-V supply to BUCK1 and BUCK6 gate drivers. Bypass to ground with a 2.2-μF (typical) ceramic capacitor. Shorted on board to LDO5P0 pin typically. Bypass not required if BUCK1 and BUCK6 are not in use. |  |  |  |  |

| 39    | DRVL6           | 0   | Low-side gate driver output for BUCK6 controller. Leave floating when not in use.                                                                                                                        |  |  |  |  |

| 40    | PGNDSNS6        | I   | Power GND connection for BUCK6. Connect to ground terminal of external low-side FET. Connect to ground when not in use.                                                                                  |  |  |  |  |

| 41    | BOOT6           | I   | Bootstrap pin for BUCK6 controller. Connect a 100-nF ceramic capacitor between this pin and SW6 pin. Leave floating when not in use.                                                                     |  |  |  |  |

| 42    | SW6             | I   | Switch node connection for BUCK6 controller. Connect to ground when not in use.                                                                                                                          |  |  |  |  |

| 43    | DRVH6           | 0   | High-side gate driver output for BUCK6 controller. Leave floating when not in use.                                                                                                                       |  |  |  |  |

| 44    | FBVOUT6         | I   | Remote feedback sense for BUCK6 controller and reference voltage for VTT LDO regulation. Connect to positive terminal of output capacitor. Connect to ground when not in use.                            |  |  |  |  |

| 45    | ILIM6           | I   | Current limit set pin for BUCK6 controller. Fit a resistor from this pin to ground to set current limit of external low-side FET. Connect to ground when BUCK6 not in use.                               |  |  |  |  |

| 64    | ILIM2           | I   | Current limit set pin for BUCK2 controller. Fit a resistor from this pin to ground to set current limit of external low-side FET. Connect to ground when BUCK2 not in use.                               |  |  |  |  |

| LDO A | ND LOAD SWITCHE | s   |                                                                                                                                                                                                          |  |  |  |  |

| 9     | LDOA1           | 0   | LDOA1 output. Bypass to ground with a 4.7-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                                |  |  |  |  |

| 17    | SWB1            | 0   | Output of load switch B1. Bypass to ground with a 0.1-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                    |  |  |  |  |

| 18    | PVINSWB1_B2     | I   | Power supply to load switch B1 and B2. Bypass to ground with a 1-µF (typical) ceramic capacitor to improve transient performance. Connect to ground when not in use.                                     |  |  |  |  |

| 19    | SWB2            | 0   | Output of load switch B2. Bypass to ground with a 0.1-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                    |  |  |  |  |

| 31    | SWA1            | 0   | Output of load switch A1. Bypass to ground with a 0.1-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                    |  |  |  |  |

## 表 6-1. Pin Functions (continued)

| NO.   | NAME                  | 1.0                                                                                                                                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 32    | PVINSWA1              | I                                                                                                                                     | Power supply to load switch A1. Bypass to ground with a 1-µF (typical) ceramic capacitor to improve transient performance. Connect to ground when not in use.                                                                                                                                                                                       |  |  |  |  |

| 46    | PVINVTT               | I                                                                                                                                     | Power supply to VTT LDO. Bypass to ground with a 10-µF (minimum) ceramic capacitor. Bypass not required if VTT LDO is not in use.                                                                                                                                                                                                                   |  |  |  |  |

| 47    | VTT                   | 0                                                                                                                                     | Output of load VTT LDO. Bypass to ground with 2× 22-µF (minimum) ceramic capacitors. Leave floating when not in use.                                                                                                                                                                                                                                |  |  |  |  |

| 48    | VTTFB                 | I                                                                                                                                     | Remote feedback sense for VTT LDO. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                                                                                                                                                                             |  |  |  |  |

| 49    | LDOA3                 | 0                                                                                                                                     | Output of LDOA3. Bypass to ground with a 4.7-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                                                                                                                                                                        |  |  |  |  |

| 50    | PVINLDOA2_A3          | I                                                                                                                                     | Power supply to LDOA2 and LDOA3. Bypass to ground with a 4.7-µF (typical) ceramic capacitor. Connect to ground when not in use.                                                                                                                                                                                                                     |  |  |  |  |

| 51    | LDOA2                 | 0                                                                                                                                     | Output of LDOA2. Bypass to ground with a 4.7-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                                                                                                                                                                        |  |  |  |  |

| 54    | LDO3P3                | 0                                                                                                                                     | Output of 3.3-V internal LDO. Bypass to ground with a 4.7-µF (typical) ceramic capacitor.                                                                                                                                                                                                                                                           |  |  |  |  |

| 56    | LDO5P0                | 0                                                                                                                                     | Output of 5-V internal LDO or an internal switch that connects this pin to V5ANA. Bypass to ground with a 4.7-µF (typical) ceramic capacitor.                                                                                                                                                                                                       |  |  |  |  |

| 57    | V5ANA                 | I                                                                                                                                     | Bias used by converters (BUCK3, BUCK4, and BUCK5) for regulation. Must be same supply as PVINx. Also has an internal load switch that connects this pin to LDO5P0 pin if 5-V is used. Bypass this pin with an optional ceramic capacitor to improve transient performance.                                                                          |  |  |  |  |

| INTER | FACE                  |                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 13    | CTL1                  | I                                                                                                                                     | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin.                                                                                                                                                                                                                        |  |  |  |  |

| 14    | CTL6/SLPENB2          | I                                                                                                                                     | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. Alternatively, when configured to active-low sleep enable, a group of VRs chosen can be entered into (L) or out of (H) sleep state where their output voltages may be different from those in normal state.            |  |  |  |  |

| 15    | IRQB                  | 0                                                                                                                                     | Open-drain output interrupt pin. Refer to # 8.13.4, IRQ: PMIC Interrupt Register, for definitions.                                                                                                                                                                                                                                                  |  |  |  |  |

| 16    | GPO1                  | 0                                                                                                                                     | General purpose output that can be configured to either open-drain or push-pull arrangement. Regardless of the configuration, the pin can be programmed either to reflect Power Good status of VRs of any choice or to be controlled by an I <sup>2</sup> C register bit by the user, which then can be used as an enable signal to an external VR. |  |  |  |  |

| 26    | GPO2                  | 0                                                                                                                                     | General purpose output that can be configured to either open-drain or push-pull arrangement. Regardless of the configuration, the pin can be programmed either to reflect Power Good status of VRs of any choice or to be controlled by an I <sup>2</sup> C register bit by the user, which then can be used as an enable signal to an external VR. |  |  |  |  |

| 27    | GPO3                  | 0                                                                                                                                     | General purpose output that can be configured to either open-drain or push-pull arrangement. Regardless of the configuration, the pin can be programmed either to reflect Power Good status of VRs of any choice or to be controlled by an I <sup>2</sup> C register bit by the user, which then can be used as an enable signal to an external VR. |  |  |  |  |

| 28    | GPO4                  | 0                                                                                                                                     | Open-drain output that can be configured to reflect Power Good status of VRs of any choice or to be controlled by an I <sup>2</sup> C register bit by the user, which then can be used as an enable signal to an external VR.                                                                                                                       |  |  |  |  |

| 58    | CLK                   | I                                                                                                                                     | I <sup>2</sup> C clock                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 59    | DATA                  | I/O                                                                                                                                   | I <sup>2</sup> C data                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 60    | CTL2                  | I                                                                                                                                     | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin.                                                                                                                                                                                                                        |  |  |  |  |

| 61    | CTL3/SLPENB1          | I                                                                                                                                     | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. Alternatively, when configured to active-low sleep enable, a group of VRs chosen can be entered into (L) or out of (H) sleep state where their output voltages may be different from those in normal state.            |  |  |  |  |

| 62    | CTL4                  | I                                                                                                                                     | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin.                                                                                                                                                                                                                        |  |  |  |  |

| 63    | CTL5                  | I                                                                                                                                     | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin.                                                                                                                                                                                                                        |  |  |  |  |

| REFE  | RENCE                 |                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 52    | AGND                  | —                                                                                                                                     | Analog ground. Do not connect to the thermal pad ground on top layer. Connect to ground of VREF capacitor.                                                                                                                                                                                                                                          |  |  |  |  |

| 53    | VREF                  | 0                                                                                                                                     | Band-gap reference output. Stabilize it by connecting a 100-nF (typical) ceramic capacitor between this pin and quiet ground.                                                                                                                                                                                                                       |  |  |  |  |

| 55    | VSYS                  | VSYS I System voltage detection and input to internal LDOs (3.3 V and 5 V). Bypass to ground with a 1-µF (typical) ceramic capacitor. |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| THER  | MAL PAD               |                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| _     | Thermal pad<br>(PGND) | _                                                                                                                                     | Connect to PCB ground plane using multiple vias for good thermal and electrical performance.                                                                                                                                                                                                                                                        |  |  |  |  |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                                                                                  | MIN                | MAX | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|------|

| ANALOG                                                                                                                                           | -                  |     |      |

| Input voltage from battery, VSYS                                                                                                                 | - 0.3              | 28  | V    |

| PVIN3, PVIN4, PVIN5, LDO5P0, DRV5V_1_6, DRV5V_2_A1, DRVL1, DRVL2, DRVL6                                                                          | - 0.3              | 7   | V    |

| V5ANA                                                                                                                                            | - 0.3              | 6   | V    |

| PGNDSNS1, PGNDSNS2, PGNDSNS6, AGND, FBGND2                                                                                                       | - 0.3              | 0.3 | V    |

| DRVH1, DRVH2, DRVH6, BOOT1, BOOT2, BOOT6                                                                                                         | - 0.3              | 34  | V    |

| SW1, SW2, SW6                                                                                                                                    | - 5 <sup>(2)</sup> | 28  | V    |

| LX3, LX4, LX5                                                                                                                                    | - 2 <sup>(3)</sup> | 8   | V    |

| Differential voltage, BOOTx to SWx                                                                                                               | - 0.3              | 5.5 | V    |

| VREF, LDO3P3, FBVOUT1, FBVOUT2, FBVOUT6, FB3, FB4, FB5, ILIM1, ILIM2, ILIM6, PVINVTT, VTT, VTTFB, PVINSWA1, SWA1, PVINSWB1_B2, SWB1, SWB2, LDOA1 | - 0.3              | 3.6 | V    |

| PVINLDOA2_A3, LDOA2, LDOA3                                                                                                                       | - 0.3              | 3.3 | V    |

| DIGITAL IO                                                                                                                                       |                    |     |      |

| DATA, CLK, GPO1-GPO3                                                                                                                             | - 0.3              | 3.6 | V    |

| CTL1-CTL6, GPO4, IRQB                                                                                                                            | - 0.3              | 7   | V    |

| Storage temperature, T <sub>stg</sub>                                                                                                            | - 40               | 150 | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Transient for less than 5 ns

(3) Transient for less than 20 ns

## 7.2 ESD Ratings

|      |                         |                                                                  | VALUE | UNIT |

|------|-------------------------|------------------------------------------------------------------|-------|------|

| V    | Electrostatic discharge | Human Body Model (HBM), per ANSI/ESDA/JEDEC JS001 <sup>(1)</sup> | ±1000 | V    |

| VESD |                         | Charged Device Model (CDM), per JESD22-C101 <sup>(2)</sup>       | ±250  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                           | MIN   | NOM     | MAX             | UNIT |

|-----------------------------------------------------------|-------|---------|-----------------|------|

| ANALOG                                                    |       |         |                 |      |

| VSYS                                                      | 5.6   | 13      | 21              | V    |

| VREF                                                      | - 0.3 |         | 1.3             | V    |

| PVIN3, PVIN4, PVIN5, LDO5P0, V5ANA, DRV5V_1_6, DRV5V_2_A1 | - 0.3 |         | 5.5             | V    |

| PGNDSNS1, PGNDSNS2, PGNDSNS6, AGND, FBGND2                | - 0.3 |         | 0.3             | V    |

| DRVH1, DRVH2, DRVH6, BOOT1, BOOT2, BOOT6                  | - 0.3 |         | 26.5            | v    |

| DRVL1, DRVL2, DRVL6                                       | - 0.3 |         | 5.5             | V    |

| SW1, SW2, SW6                                             | - 1   |         | 21              | V    |

| LX3, LX4, LX5                                             | - 1   |         | 5.5             | V    |

| FBVOUT1, FBVOUT2, FBVOUT6, FB3, FB4, FB5                  | - 0.3 |         | 3.6             | V    |

| LDO3P3, ILIM1, ILIM2, ILIM6, LDOA1                        | - 0.3 |         | 3.3             | V    |

| PVINVTT                                                   | - 0.3 | BUCK6 F | BVOUT6          | V    |

| VTT, VTTFB                                                | - 0.3 | F       | 0.5 ×<br>BVOUT6 | V    |

| PVINSWA1, SWA1, PVINSWB1_B2, SWB1, SWB2                   | - 0.3 |         | 3.6             | V    |

| PVINLDOA2_A3                                              | - 0.3 |         | 1.8             | V    |

| LDOA2, LDOA3                                              | - 0.3 |         | 1.5             | V    |

| DIGITAL IO                                                |       |         | I               |      |

| DATA, CLK, CTL1 - CTL6, GPO1 - GPO4, IRQB                 | - 0.3 |         | 3.3             | V    |

| СНІР                                                      |       |         |                 |      |

| Operating ambient temperature, T <sub>A</sub>             | - 40  | 27      | 85              | °C   |

| Operating junction temperature, T <sub>J</sub>            | - 40  | 27      | 125             | °C   |

### 7.4 Thermal Information

|                        |                                              | TPS650864  |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RSK (VQFN) | UNIT |

|                        |                                              | 64 PINS    |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 25.8       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 11.3       | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 4.4        | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ψJB                    | Junction-to-board characterization parameter | 4.4        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 0.7        | °C/W |

(1) For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics: Total Current Consumption

over recommended free-air temperature range and over recommended input voltage range (typical values are at  $T_A = 25^{\circ}C$ ) (unless otherwise noted)

|                 | PARAMETER                                                                                         | TEST CONDITIONS                                            | MIN | TYP | MAX | UNIT |

|-----------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

| I <sub>SD</sub> | PMIC shutdown current that includes I <sub>Q</sub> for references, LDO5, LDO3P3, and digital core | $V_{SYS}$ = 13 V, all functional output rails are disabled |     | 65  |     | μA   |

## 7.6 Electrical Characteristics: Reference and Monitoring System

over recommended free-air temperature range and over recommended input voltage range (typical values are at  $T_A = 25^{\circ}C$ ) (unless otherwise noted)

|                              | PARAMETER                                                               | TEST CONDITIONS                                                                   | MIN    | ТҮР  | MAX  | UNIT |

|------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------|------|------|------|

| REFERENCE                    |                                                                         |                                                                                   |        |      |      |      |

|                              | Band-gap reference voltage                                              |                                                                                   |        | 1.25 |      | V    |

| V <sub>REF</sub>             | Accuracy                                                                |                                                                                   | - 0.5% |      | 0.5% |      |

| C <sub>VREF</sub>            | Band-gap output capacitor                                               |                                                                                   | 0.047  | 0.1  | 0.22 | μF   |

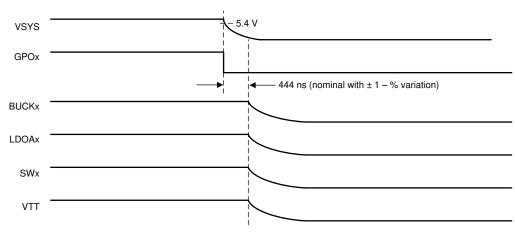

| V <sub>SYS_UVLO_5V</sub>     | VSYS UVLO threshold for LDO5                                            | V <sub>SYS</sub> falling                                                          | 5.24   | 5.4  | 5.56 | V    |

| V <sub>SYS_UVLO_5V_HYS</sub> | VSYS UVLO threshold hysteresis for LDO5                                 | V <sub>SYS</sub> rising above<br>V <sub>SYS_UVLO_5V</sub>                         |        | 200  |      | mV   |

| V <sub>SYS_UVLO_3V</sub>     | VSYS UVLO threshold for LDO3P3                                          | V <sub>SYS</sub> falling                                                          | 3.45   | 3.6  | 3.75 | V    |

| V <sub>SYS_UVLO_3V_HYS</sub> | VSYS UVLO threshold hysteresis for LDO3P3                               | V <sub>SYS</sub> rising above<br>V <sub>SYS_UVLO_3V</sub>                         |        | 150  |      | mV   |

| T <sub>CRIT</sub>            | Critical threshold of die temperature                                   | T <sub>J</sub> rising                                                             | 130    | 145  | 160  | °C   |

| T <sub>CRIT_HYS</sub>        | Hysteresis of T <sub>CRIT</sub>                                         | T <sub>J</sub> falling                                                            |        | 10   |      | °C   |

| T <sub>HOT</sub>             | Hot threshold of die temperature                                        | T <sub>J</sub> rising                                                             | 110    | 115  | 120  | °C   |

| T <sub>HOT_HYS</sub>         | Hysteresis of T <sub>HOT</sub>                                          | T <sub>J</sub> falling                                                            |        | 10   |      | °C   |

| LDO5                         |                                                                         |                                                                                   |        |      |      |      |

| V <sub>IN</sub>              | Input voltage at V <sub>SYS</sub> pin                                   |                                                                                   | 5.6    | 13   | 21   | V    |

| V <sub>OUT</sub>             | DC output voltage                                                       | I <sub>OUT</sub> = 10 mA                                                          | 4.9    | 5    | 5.1  | V    |

| Ιουτ                         | DC output current                                                       |                                                                                   |        | 100  | 180  | mA   |

| ОСР                          | Overcurrent protection                                                  | Measured with output shorted to ground                                            | 200    |      |      | mA   |

| V <sub>TH_PG</sub>           | Power Good assertion threshold in percentage of target V <sub>OUT</sub> | V <sub>OUT</sub> rising                                                           |        | 94%  |      |      |

| V <sub>TH_PG_HYS</sub>       | Power Good deassertion hysteresis                                       | V <sub>OUT</sub> rising or falling                                                |        | 4%   |      |      |

| la                           | Quiescent current                                                       | V <sub>IN</sub> = 13 V, I <sub>OUT</sub> = 0 A                                    |        | 20   |      | μA   |

| C <sub>OUT</sub>             | External output capacitance                                             |                                                                                   | 2.7    | 4.7  | 10   | μF   |

| 5ANA-to-LDO5P                | LOAD SWITCH                                                             |                                                                                   |        |      |      |      |

| R <sub>DSON</sub>            | On resistance                                                           | $V_{IN}$ = 5 V, measured from<br>V5ANA pin to LDO5P0 pin at<br>$I_{OUT}$ = 200 mA |        |      | 1    | Ω    |

| V <sub>TH_PG</sub>           | Power Good threshold for external 5-<br>V supply                        | V <sub>V5ANA</sub> rising                                                         |        | 4.7  |      | V    |

| V <sub>TH_HYS_PG</sub>       | Power Good threshold hysteresis for external 5-V supply                 | V <sub>V5ANA</sub> falling                                                        |        | 100  |      | mV   |

| LKG                          | Leakage current                                                         | Switch disabled,<br>$V_{V5ANA} = 5 V, V_{LDO5} = 0 V$                             |        |      | 10   | μA   |

| LDO3P3                       |                                                                         |                                                                                   |        |      |      |      |

| V <sub>IN</sub>              | Input voltage at V <sub>SYS</sub> pin                                   |                                                                                   | 5.6    | 13   | 21   | V    |

|                              | DC output voltage                                                       | I <sub>OUT</sub> = 10 mA                                                          |        | 3.3  |      | V    |

| V <sub>OUT</sub>             | Accuracy                                                                | V <sub>IN</sub> = 13 V,<br>I <sub>OUT</sub> = 10 mA                               | - 3%   |      | 3%   |      |

| оит                          | DC output current                                                       |                                                                                   |        |      | 40   | mA   |

| IOCP                         | Overcurrent protection                                                  | Measured with output shorted to ground                                            | 70     |      |      | mA   |

| V <sub>TH_PG</sub>           | Power Good assertion threshold in percentage of target V <sub>OUT</sub> | V <sub>OUT</sub> rising                                                           |        | 92%  |      |      |

| V <sub>TH_PG_HYS</sub>       | Power Good deassertion hysteresis                                       | V <sub>OUT</sub> falling                                                          |        | 3%   |      |      |

# 7.6 Electrical Characteristics: Reference and Monitoring System (continued)

over recommended free-air temperature range and over recommended input voltage range (typical values are at  $T_A = 25^{\circ}C$ ) (unless otherwise noted)

|                  | PARAMETER                   | TEST CONDITIONS                                   | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------|---------------------------------------------------|-----|-----|-----|------|

| IQ               | Quiescent current           | V <sub>IN</sub> = 13 V,<br>I <sub>OUT</sub> = 0 A |     | 20  |     | μA   |

| C <sub>OUT</sub> | External output capacitance |                                                   | 2.2 | 4.7 | 10  | μF   |

## 7.7 Electrical Characteristics: Buck Controllers

| F                                 | PARAMETER                                                                                                  | TEST CONDITIONS                                                                                                                     | MIN              | TYP     | MAX    | UNIT  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|--------|-------|

| BUCK1, BUCK                       | 2, BUCK6                                                                                                   |                                                                                                                                     | •                |         |        |       |

| V <sub>IN</sub>                   | Power input voltage for external HSD FET                                                                   |                                                                                                                                     | 5.6              | 13      | 21     | V     |

|                                   | DC output voltage VID                                                                                      | VID step size = 10 mV, BUCKx_VID[6:0]<br>progresses from 0000001 to 1111111                                                         | 0.41             | See     | 1.67   | V     |

|                                   | range and options                                                                                          | VID step size = 25 mV, BUCKx_VID[6:0]<br>progresses from 0000001 to 1111111                                                         | 1 <sup>(1)</sup> | See 节 5 | 3.575  | V     |

| V <sub>OUT</sub>                  | DC output voltage accuracy                                                                                 | V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V,<br>I <sub>OUT</sub> = 100 mA to 7 A                                          | - 2%             |         | 2%     |       |

|                                   | Total output voltage<br>accuracy (DC + ripple) in<br>DCM                                                   | $I_{OUT}$ = 10 mA, $V_{OUT} \le$ 1 V                                                                                                | - 30             |         | 40     | mV    |

| V <sub>FB_EXT_BUCK1</sub>         | Feedback regulation voltage                                                                                | Applies only to the Buck1 Controller if<br>programmed for external feedback voltage<br>adjustability                                | 384              | 400     | 416    | mV    |

| I <sub>FB_LKG_BUCK1</sub>         | Feedback pin leakage current                                                                               | Applies only to the Buck1 Controller if<br>programmed for external feedback voltage<br>adjustability                                |                  |         | 65     | nA    |

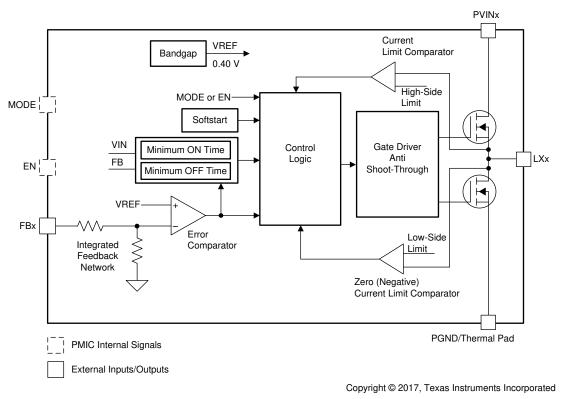

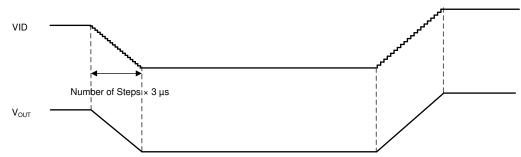

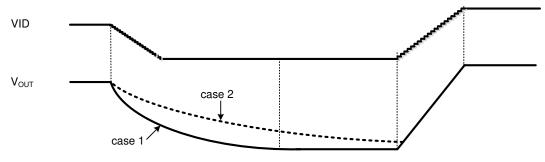

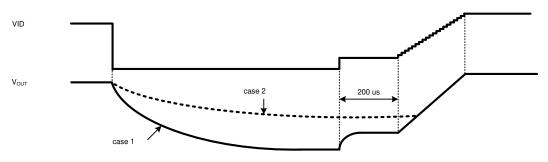

|                                   | Output DVS slew rate                                                                                       | VID step size = 10 mV                                                                                                               | 2.5              | 3.125   |        | mV/µs |

| SR(V <sub>OUT</sub> )             | Oulput DVS siew rate                                                                                       | VID step size = 25 mV                                                                                                               | 3.125            | 4       |        | mv/µs |

| I <sub>LIM_LSD</sub>              | Low-side output valley<br>current limit accuracy<br>(programmed by external<br>resistor R <sub>LIM</sub> ) |                                                                                                                                     | - 15%            |         | 15%    |       |

| ILIMREF                           | Source current out of ILIM1 pin                                                                            | T = 25°C                                                                                                                            | 45               | 50      | 55     | μA    |

| V <sub>LIM</sub>                  | Voltage at ILIM1 pin                                                                                       | V <sub>LIM</sub> = R <sub>LIM</sub> × I <sub>LIMREF</sub>                                                                           | 0.2              |         | 2.25   | V     |

| $\Delta V_{OUT} / \Delta V_{IN}$  | Line regulation                                                                                            | V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V,<br>I <sub>OUT</sub> = 7 A                                                    | - 0.5%           |         | 0.5%   |       |

| $\Delta V_{OUT} / \Delta I_{OUT}$ | Load regulation                                                                                            | $V_{IN} = 13 V, V_{OUT} = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V, I_{OUT} = 0 A to 7 A, referenced to V_{OUT} at I_{OUT} = I_{OUT_MAX}$ | 0%               |         | 1%     |       |

|                                   | Power Good deassertion                                                                                     | V <sub>OUT</sub> rising                                                                                                             | 105.5%           | 108%    | 110.5% |       |

| V <sub>TH_PG</sub>                | threshold in percentage of target $V_{OUT}$                                                                | V <sub>OUT</sub> falling                                                                                                            | 89.5%            | 92%     | 94.5%  |       |

| P                                 | Driver DRVH resistance                                                                                     | Source, IDRVH =  - 50 mA                                                                                                            |                  | 3       |        | Ω     |

| R <sub>DSON_DRVH</sub>            |                                                                                                            | Sink, IDRVH = 50 mA                                                                                                                 |                  | 2       |        | Ω     |

| P                                 | Driver DRVL resistance                                                                                     | Source, IDRVL = - 50 mA                                                                                                             |                  | 3       |        | Ω     |

| R <sub>DSON_DRVL</sub>            |                                                                                                            | Sink, IDRVL = 50 mA                                                                                                                 |                  | 0.4     |        | Ω     |

|                                   | • • • • • • •                                                                                              | BUCKx_DISCHG[1:0] = 01                                                                                                              |                  | 100     |        | Ω     |

| R <sub>DIS</sub>                  | Output auto-discharge<br>resistance                                                                        | BUCKx_DISCHG[1:0] = 10                                                                                                              |                  | 200     |        | Ω     |

|                                   |                                                                                                            | BUCKx_DISCHG[1:0] = 11                                                                                                              |                  | 500     |        | Ω     |

## 7.7 Electrical Characteristics: Buck Controllers (continued)

over recommended input voltage range,  $T_A = -40^{\circ}$ C to +85°C and  $T_A = 25^{\circ}$ C for typical values (unless otherwise noted)

|                      | PARAMETER                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------------|--------------------------------|-----------------|-----|-----|-----|------|

| C <sub>BOOT</sub>    | Bootstrap capacitance          |                 |     | 100 |     | nF   |

| R <sub>ON_BOOT</sub> | Bootstrap switch ON resistance |                 |     |     | 20  | Ω    |

(1) BUCKx\_VID[6:0] = 0000001 - 0011000

### 7.8 Electrical Characteristics: Synchronous Buck Converters

|                                   | PARAMETER                                                                     | TEST CONDITIONS                                                                                                   | MIN    | TYP    | MAX   | UNIT  |

|-----------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------|--------|-------|-------|

| BUCK3, BUCK4                      | 4, BUCK5                                                                      |                                                                                                                   |        |        | ·     |       |

| V <sub>IN</sub>                   | Power input voltage                                                           |                                                                                                                   | 3.0    |        | 5.5   | V     |

|                                   | DC output voltage VID range                                                   | VID step size = 10 mV,<br>BUCKx_VID[6:0] progresses from<br>0000001 to 1111111                                    | 0.41   | See #5 | 1.67  | V     |

|                                   | and options                                                                   | VID step size = 25 mV,<br>BUCKx_VID[6:0] progresses from<br>0000001 to 1111111                                    | 0.425  | See    | 3.575 | v     |

| V                                 |                                                                               | V <sub>IN</sub> = 5.0 V, V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5,<br>1.8, 2.5, 3.3 V,<br>I <sub>OUT</sub> = 1.5 A    | - 2%   |        | 2%    |       |

| Vout                              |                                                                               | V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5,<br>1.8 V,<br>I <sub>OUT</sub> = 1.5 A              | - 2%   |        | 2%    |       |

|                                   | DC output voltage accuracy                                                    | V <sub>IN</sub> = 5.0 V, V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5,<br>1.8 V, 2.5, 3.3 V,<br>I <sub>OUT</sub> = 100 mA | - 2.5% |        | 2.5%  |       |

|                                   |                                                                               | V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5,<br>1.8 V,<br>I <sub>OUT</sub> = 100 mA             | - 2.5% |        | 2.5%  |       |

| V <sub>DCM</sub>                  | Total output voltage accuracy (DC + ripple) in DCM                            | $V_{\text{IN}}$ = 5.0 V, $I_{\text{OUT}}$ = 10 mA, $V_{\text{OUT}} \leqslant 1$ V                                 | - 30   |        | 40    | mV    |

|                                   | Outout DVO alcounts                                                           | VID step size = 10 mV                                                                                             | 2.5    | 3.125  |       |       |

| SR(V <sub>OUT</sub> )             | Output DVS slew rate                                                          | VID step size = 25 mV                                                                                             | 3.125  | 4      |       | mV/µs |

| I <sub>OUT</sub>                  | Continuous DC output current                                                  |                                                                                                                   |        |        | 3     | А     |

| I <sub>IND_LIM</sub>              | HSD FET current limit                                                         |                                                                                                                   | 4.3    |        | 7     | А     |

| l <sub>Q</sub>                    | Quiescent current                                                             | V <sub>IN</sub> = 5 V, V <sub>OUT</sub> = 1 V,<br>BUCKx_MODE = 0b                                                 |        | 35     |       | μA    |

| $\Delta V_{OUT} / \Delta V_{IN}$  | Line regulation                                                               | V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5, 1.8,<br>2.5, 3.3 V, I <sub>OUT</sub> = 1.5 A                                | - 0.5% |        | 0.5%  |       |

| $\Delta V_{OUT} / \Delta I_{OUT}$ | Load regulation                                                               |                                                                                                                   | - 0.2% |        | 2%    |       |

|                                   | Power Good deassertion                                                        | V <sub>OUT</sub> rising                                                                                           |        | 108%   |       |       |

| V <sub>TH_PG</sub>                | threshold in percentage of target V <sub>OUT</sub>                            | V <sub>OUT</sub> falling                                                                                          |        | 92%    |       |       |

| V <sub>TH_HYS_PG</sub>            | Power Good reassertion<br>hysteresis entering back into<br>V <sub>TH_PG</sub> | V <sub>OUT</sub> rising or falling                                                                                |        | 3%     |       |       |

# 7.8 Electrical Characteristics: Synchronous Buck Converters (continued)

over recommended input voltage range,  $T_A = -40^{\circ}C$  to +85°C and  $T_A = 25^{\circ}C$  for typical values (unless otherwise noted)

|                  | PARAMETER                           | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |  |

|------------------|-------------------------------------|------------------------|-----|-----|-----|------|--|

| R <sub>DIS</sub> |                                     | BUCKx_DISCHG[1:0] = 01 |     | 100 |     |      |  |

|                  | Output auto-discharge<br>resistance | BUCKx_DISCHG[1:0] = 10 |     | 200 |     | Ω    |  |

|                  |                                     | BUCKx_DISCHG[1:0] = 11 |     | 500 |     |      |  |

## 7.9 Electrical Characteristics: LDOs

|                                            | PARAMETER                                             | TEST CONDITIONS                                                                   | MIN                                                 | TYP     | MAX  | UNIT |

|--------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------|---------|------|------|

| LDOA1                                      |                                                       |                                                                                   |                                                     |         |      |      |

| V <sub>IN</sub>                            | Input voltage                                         |                                                                                   | 4.5                                                 | 5       | 5.5  | V    |

|                                            | DC output voltage                                     | Set by LDOA1_VID[3:0]                                                             | 1.35                                                | See 节 5 | 3.3  | V    |

| V <sub>OUT</sub>                           | Accuracy                                              | I <sub>OUT</sub> = 0 to 200 mA                                                    | - 2%                                                |         | 2%   | V    |

| I <sub>OUT</sub>                           | DC output current                                     |                                                                                   |                                                     |         | 200  | mA   |

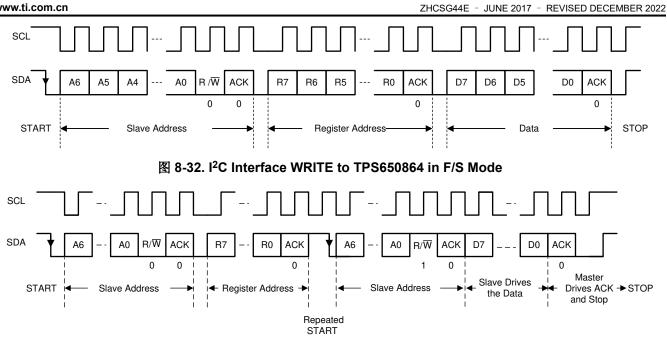

| $\Delta V_{OUT} / \Delta V_{IN}$           | Line regulation                                       | I <sub>OUT</sub> = 40 mA                                                          | - 0.5%                                              |         | 0.5% |      |