**TOSHIBA Bi-CMOS Integrated Circuit Silicon Monolithic**

# TB9081FG

Automotive GATE-driver for Brushless motor

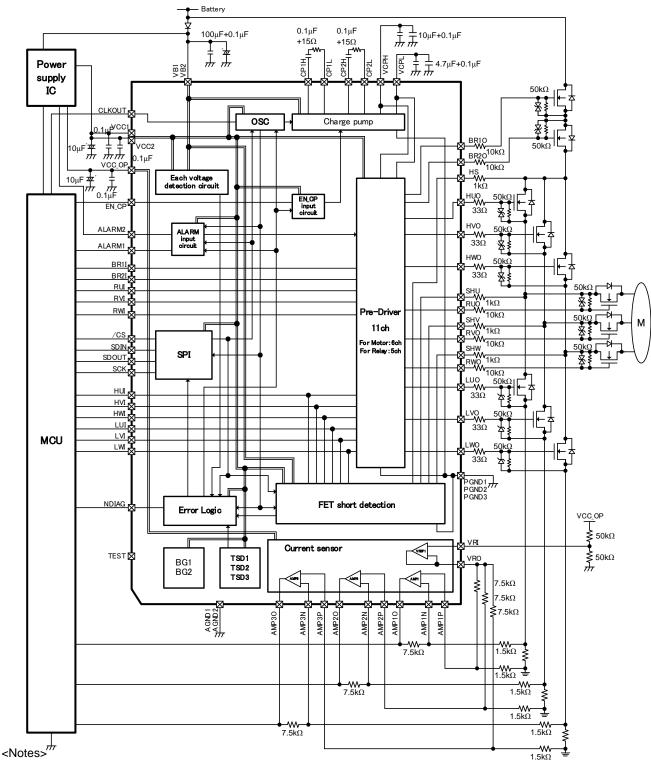

TB9081FG is Pre-driver IC automotive for brushless motor. Fail-safe relay pre-drivers are also built in in addition to 3-phase pre-drivers.

The charge pump, the motor current detection circuit, the oscillator, and the SPI communication circuit are built in.

The miscellaneous abnormal detections are carried and the operation after failure detection conditions and failure detections can be set up. About each setup, these can set up through a SPI communication.

Also, it has built-in ABIST / LBIST functions for diagnosing the normal operation of the miscellaneous abnormal detection function.

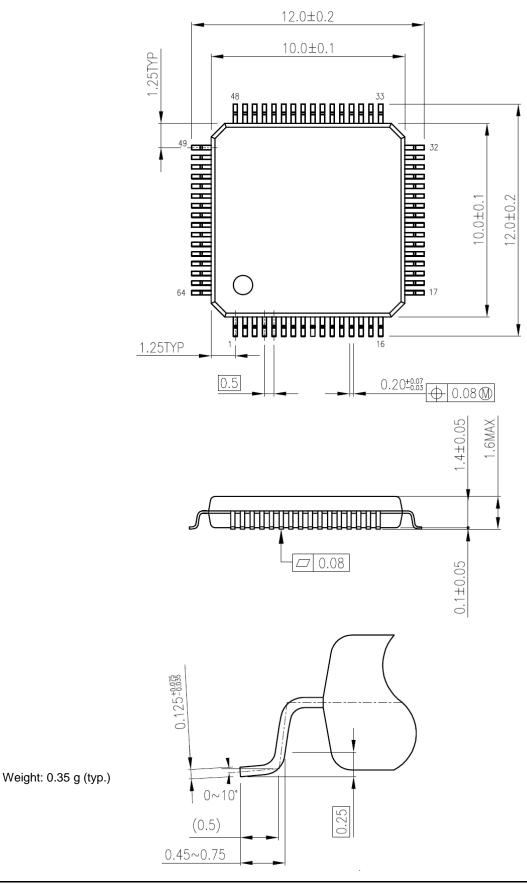

Weight: 0.35 g (typ.)

### Features

- 3-phase pre-drivers : PWM control to 20kHz

- Build-in fail-safe relay pre-drivers

TOSHIBA

- Build-in Charge Pump

- High response Current Detection circuit

- Miscellaneous-abnormal-detection circuits (Under voltage (VB, VCC) / Over voltage (VCC) / Over temp. / FET short-circuit detection)

- Build-in ABIST/LBIST functions

- Operating voltage range : VB=4.5 to 28V, VCC=3.0 to 5.5V

- Operational temperature range : -40 to 125°C

- Package : LQFP-64pin (0.5mm pitch)

- AEC-Q100 Qualified

- TM-SIL<sup>™</sup>

- Developed according to ISO 26262 ASIL-D

- Safety Manual and Safety Analysis Report

- > Functional redundancy and built-in ABIST and LBIST

- > SPI interface with CRC check

The product(s) is/are compatible with RoHS regulations (EU directive 2011 / 65 / EU) as indicated, if any, on the packaging label ("[[G]]/RoHS COMPATIBLE", "[[G]]/RoHS [[Chemical symbol(s) of controlled substance(s)]]", "RoHS COMPATIBLE" or "RoHS COMPATIBLE, [[Chemical symbol(s) of controlled substance(s)]]>MCV").

Table of contents

Internal block diagram

Package pin layout (top view)

Pin description

**Functional descriptions**

- (1) Charge pump circuit

- (2) Pre-drivers

- (3) Current detector

- (4) Oscillator/divider

- (5) Abnormal detection circuit

- (5-1) VB1/VB2 under voltage detection

- (5-2) VCC1/VCC2 under voltage detection

- (5-3) VCC1/VCC2 over voltage detection

- (5-4) Over temperature detection

- (5-5) Short-circuit detection

- (5-6) Oscillation frequency monitoring

- (6) ALARM input circuit

- (7) EN\_CP input circuit

- (8) ABIST function

- (9) SPI Communication circuit

- (9-1) SPI communication operation

- (9-2) Register map

Absolute maximum ratings

Electrical characteristics

Reference circuit diagram

PACKAGE

Revision history

RESTRICTIONS ON PRODUCT USE

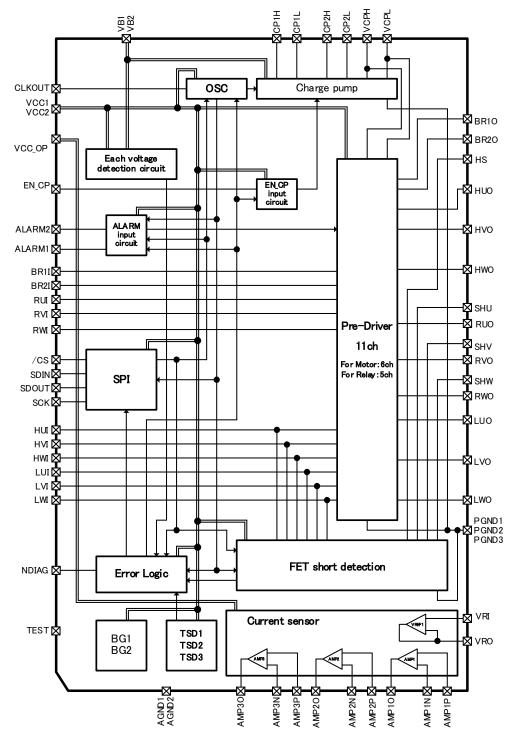

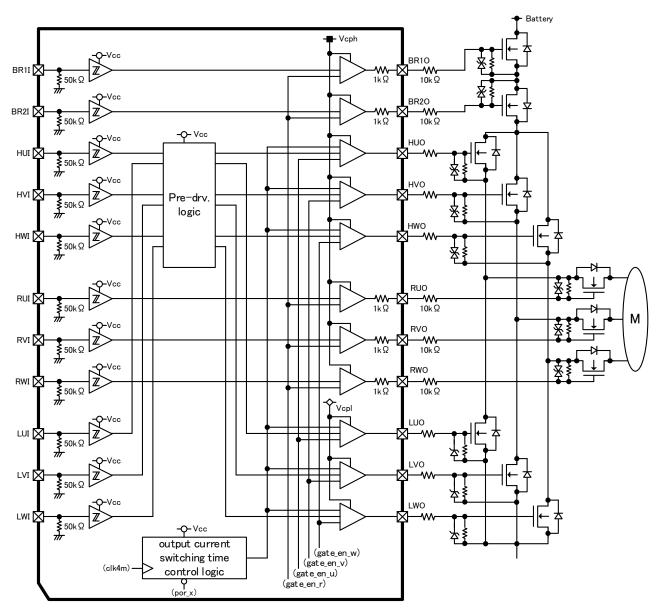

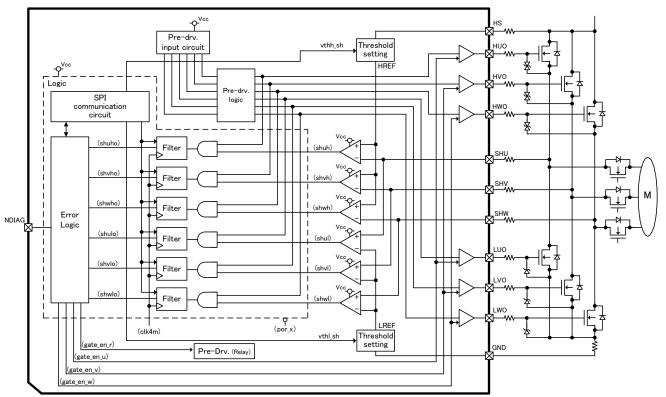

## Internal block diagram

Notes 1: Some of the functional blocks, circuit, or constants in the block diagram may be omitted or simplified for explanatory purpose. (including individual block diagram)

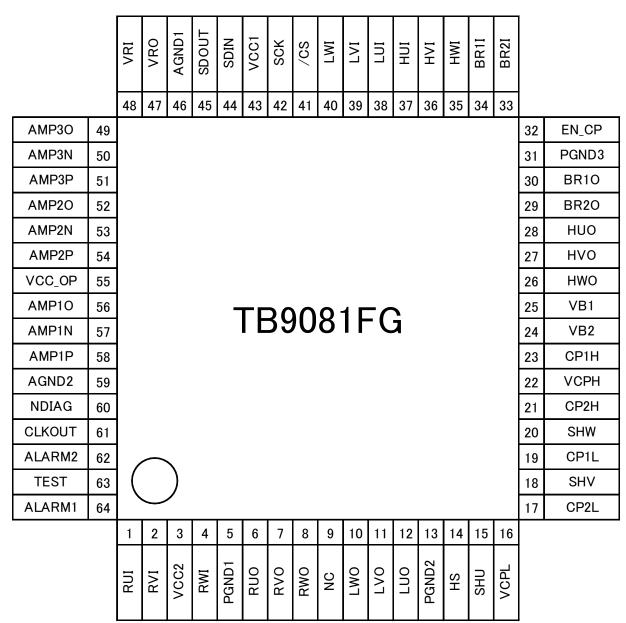

### Package pin layout (top view)

## **Pin description**

| Pin No.  | Symbol         | Input/output        | Definition                                                                      | Pull-Up   | /Down        | Notes          |

|----------|----------------|---------------------|---------------------------------------------------------------------------------|-----------|--------------|----------------|

| 1        | RUI            | IN                  | U-Phase Motor Relay Input                                                       | Pull-Down | 50kΩ         | -              |

| 2        | RVI            | IN                  | V-Phase Motor Relay Input                                                       | Pull-Down | 50kΩ         | -              |

| 3        | VCC2           | Power supply        | Power supply 2 (3.3V or 5V)                                                     | -         | -            | -              |

| 4        | RWI            | IN                  | W-Phase Motor Relay Input                                                       | Pull-Down | $50k\Omega$  | -              |

| 5        | PGND1          | GND                 | Power GND1                                                                      | -         | -            | -              |

| 6        | RUO            | OUT                 | U-Phase Motor Relay Output                                                      | -         | -            | push-pull      |

| 7        | RVO            | OUT                 | V-Phase Motor Relay Output                                                      | -         | -            | push-pull      |

| 8        | RWO            | OUT                 | W-Phase Motor Relay Output                                                      | -         | -            | push-pull      |

| 9        | NC             | -                   | -                                                                               | -         | -            | -              |

| 10       | LWO            | OUT                 | Pre-Driver Output LW                                                            | -         | -            | push-pull      |

| 11       | LVO            | OUT                 | Pre-Driver Output LV                                                            | -         | -            | push-pull      |

| 12       | LUO            | OUT                 | Pre-Driver Output LU                                                            | -         | -            | push-pull      |

| 13       | PGND2          | GND                 | Power GND2                                                                      | -         | -            | -              |

| 14<br>15 | HS<br>SHU      | IN<br>IN            | High-side Drain Input<br>Motor Connect PIN U-phase                              | -         | -            | -              |

| 15       | VCPL           |                     | Charge-pump voltage (for low sides)                                             |           | -            | -              |

| 10       | CP2L           | Power supply<br>OUT | 2nd Charge Pump Drive Output                                                    | -         | -            | -<br>push-pull |

| 18       | SHV            | IN                  | Motor Connect PIN V-phase                                                       | -         | -            | pusii-puii     |

| 10       | CP1L           | OUT                 | 1st Charge Pump Drive Output                                                    | -         | -            | -<br>push-pull |

| 20       | SHW            | IN                  | Motor Connect PIN W-phase                                                       | -         | -            | -              |

| 20       | CP2H           | IN/OUT              | 2nd Charge Pump Output                                                          |           |              | _              |

| 22       | VCPH           | Power supply        | Charge-pump voltage (for high sides)                                            | -         | -            | -              |

| 23       | CP1H           | IN/OUT              | 1st Charge Pump Output                                                          | -         | -            | -              |

| 24       | VB2            | Power supply        | Power Supply2 (Battery 12V)                                                     | -         | -            | -              |

| 25       | VB1            | Power supply        | Power Supply1 (Battery 12V)                                                     | -         | -            | -              |

| 26       | HWO            | OUT                 | Pre-Driver Output HW                                                            | -         | -            | push-pull      |

| 27       | HVO            | OUT                 | Pre-Driver Output HV                                                            | -         | -            | push-pull      |

| 28       | HUO            | OUT                 | Pre-Driver Output HU                                                            | -         | -            | push-pull      |

| 29       | BR2O           | OUT                 | BR2 Power supply relay Output                                                   | -         | -            | push-pull      |

| 30       | BR10           | OUT                 | BR1 Power supply relay Output                                                   | -         | -            | push-pull      |

| 31       | PGND3          | GND                 | Power GND 3                                                                     | -         | -            | -              |

| 32       | EN_CP          | IN                  | Charge-pump enable signal                                                       | Pull-Down | 50kΩ         | -              |

| 33       | BR2I           | IN                  | BR2 Power supply relay Input                                                    | Pull-Down | 50kΩ         | -              |

| 34       | BR1I           | IN                  | BR1 Power supply relay Input                                                    | Pull-Down | $50 k\Omega$ | -              |

| 35       | HWI            | IN                  | Pre-Driver Input HW                                                             | Pull-Down | $50 k\Omega$ | -              |

| 36       | HVI            | IN                  | Pre-Driver Input HV                                                             | Pull-Down | $50 k\Omega$ | -              |

| 37       | HUI            | IN                  | Pre-Driver Input HU                                                             | Pull-Down | $50k\Omega$  | -              |

| 38       | LUI            | IN                  | Pre-Driver Input LU                                                             | Pull-Down | $50 k\Omega$ | -              |

| 39       | LVI            | IN                  | Pre-Driver Input LV                                                             | Pull-Down | $50 k\Omega$ | -              |

| 40       | LWI            | IN                  | Pre-Driver Input LW                                                             | Pull-Down | $50 k\Omega$ | -              |

| 41       | /CS            | IN                  | SPI chip select                                                                 | Pull-Up   | $50k\Omega$  | -              |

| 42       | SCK            | IN                  | SPI clock input                                                                 | Pull-Down | $50k\Omega$  | -              |

| 43       | VCC1           | Power supply        | Power supply 1 (3.3V or 5V)                                                     | -         | -            | -              |

| 44       | SDIN           | IN                  | SPI input                                                                       | Pull-Down | $50 k\Omega$ | -              |

| 45       | SDOUT          | OUT                 | SPI Output                                                                      | -         | -            | push-pull      |

| 46       | AGND1          | GND                 | The GND 1 for analog circuits                                                   | -         | -            | -              |

| 47       | VRO            | OUT                 | Reference voltage amplifier Output                                              | -         | -            | -              |

| 48       | VRI            | IN                  | Reference voltage amplifier input                                               | -         | -            | -              |

| 49<br>50 | AMP30          | OUT                 | Current-detection amplifier Output 3                                            | -         | -            | push-pul       |

| 50       | AMP3N          | IN                  | Current-detection amplifier input 3 (-)                                         | -         | -            | -              |

| 51<br>52 | AMP3P<br>AMP2O | IN<br>OUT           | Current-detection amplifier input 3 (+)<br>Current-detection amplifier Output 2 | -         | -            | -<br>push-pul  |

| 52<br>53 | AMP20<br>AMP2N | IN                  | Current-detection amplifier Output 2<br>Current-detection amplifier input 2 (-) | -         | -            | pusn-pui       |

| 53<br>54 | AMP2N<br>AMP2P | IN                  | Current-detection amplifier input 2 (-)                                         | -         | -            | -              |

| 54<br>55 | VCC_OP         | Power supply        | The power supply for Current-detection amplifier (5V/3.3V)                      | -         | -            | -              |

| 55<br>56 | AMP10          | OUT                 | Current-detection amplifier Output 1                                            | -         | -            | -<br>push-pul  |

| 57       | AMP10          | IN                  | Current-detection amplifier input 1 (-)                                         | -         | -            | -              |

| 58       | AMP1P          | IN                  | Current-detection amplifier input 1 (+)                                         | -         | -            | -              |

| 59       | AGND2          | GND                 | The ground 2 for analog circuits                                                | -         | -            | -              |

| 60       | NDIAG          | OUT                 | Error Output Pin                                                                | -         | -            | push-pul       |

| 61       | CLKOUT         | OUT                 | Clock output                                                                    | -         | -            | push-pul       |

| 62       | ALARM2         | IN                  | Pre-driver enable 2                                                             | Pull-Down | 50kΩ         | -              |

|          |                |                     | Test terminal                                                                   | Pull-Down | 50kΩ         |                |

| 63       | TEST           | IN                  | Testienninai                                                                    |           | ;)()K()      | -              |

## •Description of an internal signal name

| Internal signal | Description                                               | St            | ate                 |

|-----------------|-----------------------------------------------------------|---------------|---------------------|

| name            | Description                                               | Н             | L                   |

| abst_pass       | Normal signal of ABIST                                    | ABIST normal  | ABIST abnormal      |

| abst_end        | End signal of ABIST                                       | ABIST end     | ABIST<br>unfinished |

| gate_en_u       | Pre-driver output enabling signal (U phase)               | Enable        | Disable             |

| gate_en_v       | Pre-driver output enabling signal (V phase)               | Enable        | Disable             |

| gate_en_w       | Pre-driver output enabling signal (W phase)               | Enable        | Disable             |

| gate_en_r       | Pre-driver output enabling signal (relay)                 | Enable        | Disable             |

| gate_off_u      | Error output signal (Pre-driver output enabling, U phase) | Enable        | Disable             |

| gate_off_v      | Error output signal (Pre-driver output enabling, V phase) | Enable        | Disable             |

| gate_off_w      | Error output signal (Pre-driver output enabling, W phase) | Enable        | Disable             |

| gate_off_r      | Error output signal (Pre-driver output enabling, relay)   | Enable        | Disable             |

| cp_en           | Enabling signal for charge pump circuit                   | Enable        | Disable             |

| cp_off          | Error output signal (charge pump circuit enabling)        | Enable        | Disable             |

| vbl1            | VB1/VB2 under voltage detection signal 1                  | Detection     | Release             |

| vbl2            | VB1/VB2 under voltage detection signal 2                  | Detection     | Release             |

| vcl1            | VCC1/VCC2 under voltage detection signal 1                | Detection     | Release             |

| vcl2            | VCC1/VCC2 under voltage detection signal 2                | Detection     | Release             |

| por_x           | Internal reset signal                                     | Reset release | Reset               |

| vch             | VCC1/VCC2 over voltage detection signal                   | Detection     | Release             |

| vphh            | VCPH clamp voltage detection signal                       | Detection     | Release             |

| tsd1det         | Over temperature detection signal1                        | Detection     | Release             |

| tsd2det         | Over temperature detection signal2                        | Detection     | Release             |

| tsd3det         | Over temperature detection signal3                        | Detection     | Release             |

| shuho           | Short-circuit detection signal (U phase low side)         | Detection     | Release             |

| shvho           | Short-circuit detection signal (V phase low side)         | Detection     | Release             |

| shwho           | Short-circuit detection signal (W phase low side)         | Detection     | Release             |

| shulo           | Short-circuit detection signal (U phase high side)        | Detection     | Release             |

| shvlo           | Short-circuit detection signal (V phase high side)        | Detection     | Release             |

| shwlo           | Short-circuit detection signal (W phase high side)        | Detection     | Release             |

## <Usage power supply/GND list>

| Symbol | Pin name          | Function/Application                                          |

|--------|-------------------|---------------------------------------------------------------|

| Vb     | VB1,VB2           | Battery power supply                                          |

| Vcc    | VCC1,VCC2         | External 5V/3.3V power supply                                 |

| Vccop  | VCC_OP            | The power supply for current detection<br>amplifier (5V/3.3V) |

| Vcph   | VCPH              | Charge pump voltage (for high sides)                          |

| Vcpl   | VCPL              | Charge pump voltage (for low sides)                           |

| AGND   | AGND1,AGND2       | GND for analog circuitry                                      |

| PGND   | PGND1,PGND2,PGND3 | Power GND                                                     |

## **Functional descriptions**

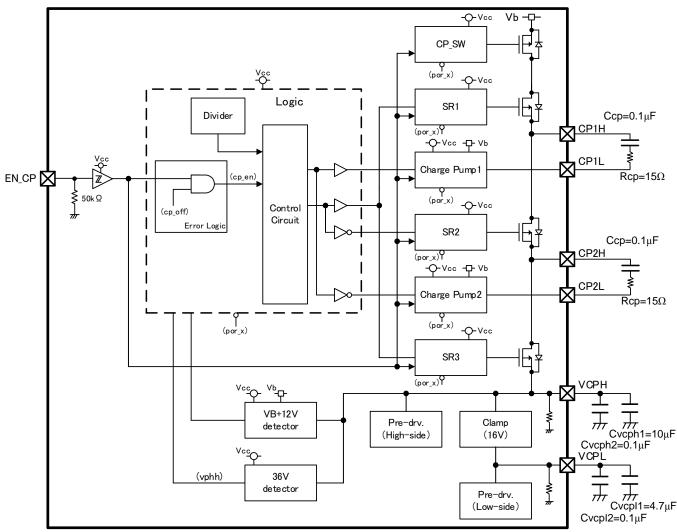

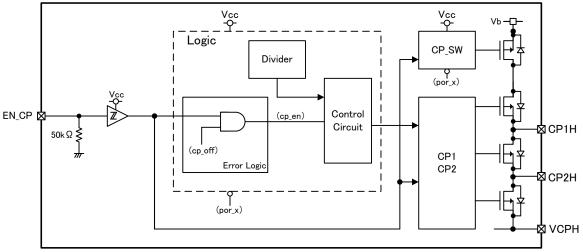

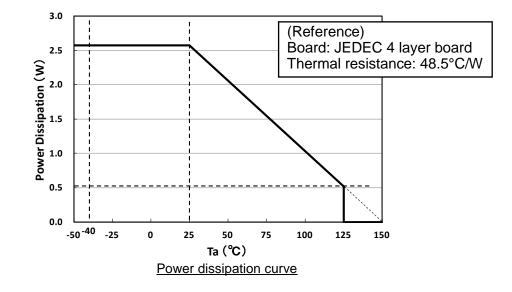

## (1) Charge pump circuit

TB9081FG build in Charge pump for Pre-Drivers and it can control external Nch MOSFETs directly. Two charge pump voltages the object for the high side drive of a motor and the object for the relay drive of a motor, and for the low side drive of a motor is generated.

The charge pump voltage (Vcph) for a high side drive and a relay drive control by an internal circuit, and if Vcph goes up to Vb+12V (Typ.), a charge pump will suspend operation. Furthermore, in consideration of an overvoltage state, if Vcph goes up to 37V (Typ.), a charge pump will stop, and if Vcph is less than 36.5V (Typ.), a charge pump will resume operation.

The charge pump voltage (Vcpl) for a low side drive is generated from Vcph. If Vcpl goes up to 16V (Typ.), a clamp will start and it will not become the voltage more than clamp voltage.

It is possible to build the switching circuit (CP\_SW) in the Vb side of a charge pump circuit, to make a transistor turn off by CP\_SW, and to stop the supply to Vcph from Vb. Vcc voltage turns off the transistor of CP\_SW on condition of the conditions as for which below Vcc voltage detection voltage becomes, or EN\_CP=L. For details, please refer to a (7) EN\_CP circuit.

Moreover, it is possible to operate or stop a charge pump by terminal EN\_CP. The charge pump operates at the time of EN\_CP="H", and it stops at the time of EN\_CP="L" and also suspends the supply to Vcph from Vb.

A Vcph output voltage is set to 0V at the time of the charge-pump stop by EN\_CP="L."

When the charge pump is stopped by the control in the IC, Vcph output voltage will become the "Vb-3VF".

Fig.1- a Charge pump circuit Block Diagram

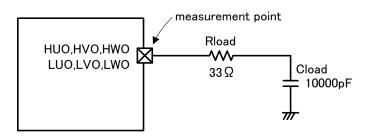

## (2) Pre-drivers

TB9081FG has the pre-driver circuit it is for the motor relay drive, for the power relay drive, for the low-side drive of the motor and for the high-side drive of the motor. Each pre-driver circuit has a respective input and output terminals are controlled by a signal inputted to the input terminals.

Fig.2- a Pre-driver circuit Block Diagram

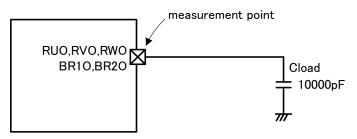

<A power supply relay drive circuit, a motor relay drive circuit>

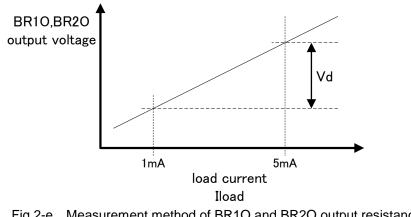

A power supply relay drive circuit is a circuit which controls FET for a relay on the battery power-supply side.

A motor relay drive circuit is a circuit which controls FET for a relay on the motor side.

A truth table is shown in table 2-a and 2-b. Refer to the (6) ALARM input circuit for the details of the internal signal (gate\_en\_r) in a truth table.

Moreover, resistance  $1k\Omega$  is built in the output of a power supply relay drive and a motor relay drive.

Furthermore, the diode for prevention of backflow at the time of reverse connection is built in the output of a power supply relay drive circuit.

- Table 2- a Input/output truth table 1 (power supply relay drive circuit)

- Power supply relay drive circuit 1

| Input | Internal signal | Output | Notoo |

|-------|-----------------|--------|-------|

| BR1I  | (gate_en_r)     | BR1O   | Notes |

| L     | Н               | L      | -     |

| Н     | Н               | Н      | -     |

| *     | L               | L      | -     |

\*:Don't care

- Power supply relay drive circuit 2

| Input        | Internal signal | Output | Notoo |

|--------------|-----------------|--------|-------|

| BR2I         | (gate_en_r)     | BR2O   | Notes |

| L            | Н               | L      | -     |

| Н            | Н               | Н      | -     |

| *            | L               | L      | -     |

| * Dault saus |                 |        |       |

\*:Don't care

- Table 2- b Input/output truth table 2 (motor relay drive circuit)

- Motor relay drive circuit 1 (U phase)

| Input | Internal signal | Output | Natao |

|-------|-----------------|--------|-------|

| RUI   | (gate_en_r)     | RUO    | Notes |

| L     | Н               | L      | -     |

| Н     | Н               | Н      | -     |

| *     | L               | L      | -     |

\*:Don't care

- Motor relay drive circuit 2 (V phase)

| Input | Internal signal | Output | Notoo |

|-------|-----------------|--------|-------|

| RVI   | (gate_en_r)     | RVO    | Notes |

| L     | Н               | L      | -     |

| Н     | Н               | Н      | -     |

| *     | L               | L      | -     |

\*:Don't care

- Motor relay drive circuit 3 (W phase)

| Input | Internal signal | Output | Notoo |

|-------|-----------------|--------|-------|

| RWI   | (gate_en_r)     | RWO    | Notes |

| L     | Н               | L      | -     |

| Н     | Н               | Н      | -     |

| *     | L               | L      | -     |

\*:Don't care

#### <A high side drive circuit, a low side drive circuit>

A high side drive circuit is a circuit which drives FET of the high side of a motor. A low side drive circuit is a circuit which drives FET of the low side of a motor. A high side drive circuit and a low side drive circuit built in each 3ch.

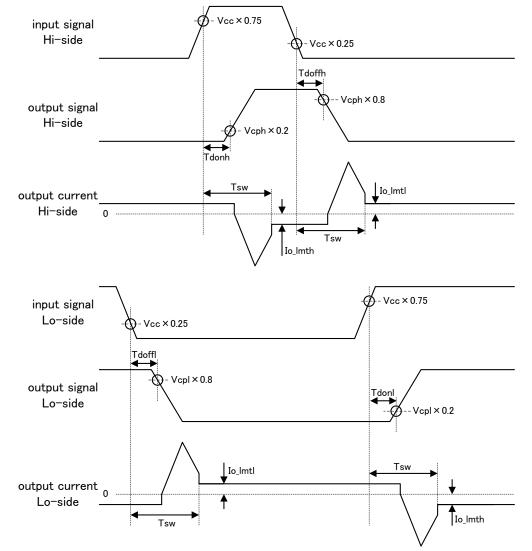

An input signal (HUI/HVI/HWI, LUI/LVI/LWI) is changed by a control block, and output (HUO/HVO/HWO, LUO/LVO/LWO) is outputted. A truth table is shown in table 2-c. Refer to the (6) ALARM input circuit for the details of the internal signal (gate\_en\_u, gate\_en\_v, gate\_en\_w) in a truth table.

When HUI/LUI, HVI/LVI, and HWI/LWI are H/H, an output will be L/L (prohibition input). The operation at the time of prohibition input detection can be set up through a SPI communication.

Moreover, the current at the time of Turn on/Turn off of a high side drive circuit and a low side drive circuit is the current limit after 8  $\mu$ s (typ.). This current-limiting time can be set up a 3 value or no limit time through a SPI communication.

When gate\_en\_u, gate\_en\_v, and gate\_en\_w switch from "H" to "L" by the failure detection and ALARM1 or ALARM2 outputting low, and then, the high side drive circuit and the low side drive circuit output high, it switches to "L". At this time, it has an output current capability which is decided by the ON resistance and the gate resistance of the output driver during the current limit time. However, only Vcc under voltage detection, the output current capability will be the output limit current lolmtl even within the current limit time.

- Table 2- c Input/output truth table 3 (a high side drive circuit, a low side drive circuit)

- FET drive circuit 1 (U phase)

| Inp | but | Internal<br>signal | Out      | tput     | Notes              |

|-----|-----|--------------------|----------|----------|--------------------|

| HUI | LUI | (gate_en_u)        | HUO      | LUO      |                    |

| L   | L   | Н                  | L        | L        | -                  |

| L   | Н   | Н                  | L        | Н        | -                  |

| Н   | L   | Н                  | Н        | L        | -                  |

| Н   | Н   | Н                  | <u>L</u> | <u>L</u> | Inhibit input mode |

| *   | *   | L                  | L        | L        | -                  |

\*: Don't care

- FET drive circuit 2 (V phase)

| Inp | but | Internal<br>signal | Out | tput | Notes              |

|-----|-----|--------------------|-----|------|--------------------|

| HVI | LVI | (gate_en_v)        | HVO | LVO  |                    |

| L   | L   | Н                  | L   | L    | -                  |

| L   | Н   | Н                  | L   | Н    | -                  |

| Н   | L   | Н                  | Н   | L    | -                  |

| Н   | Н   | Н                  | L   | L    | Inhibit input mode |

| *   | *   | L                  | L   | L    | -                  |

\*: Don't care

- FET drive circuit 3 (W phase)

| Inp | but | Internal<br>signal | Out      | tput     | Notes              |

|-----|-----|--------------------|----------|----------|--------------------|

| HWI | LWI | (gate_en_w)        | HWO      | LWO      |                    |

| L   | L   | Н                  | L        | L        | -                  |

| L   | Н   | Н                  | L        | Н        | -                  |

| Н   | L   | Н                  | Н        | L        | -                  |

| Н   | Н   | Н                  | <u>L</u> | <u>L</u> | Inhibit input mode |

| *   | *   | L                  | L        | L        | -                  |

\*: Don't care

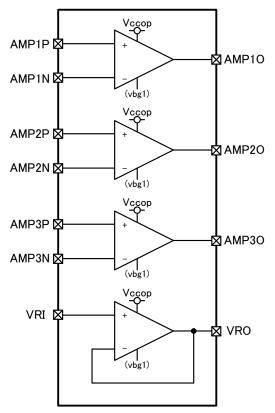

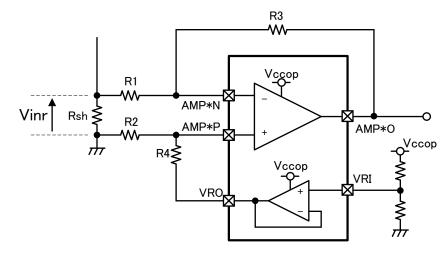

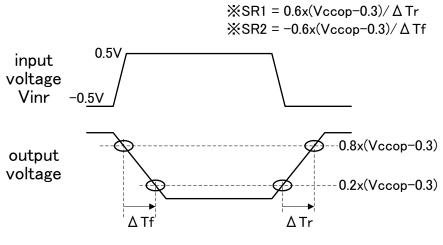

## (3) Current detector

TB9081FG are built three amplifiers for motor-current detection and one amplifier for reference voltage generation (Fig3- a).

The amplifiers for motor-current detection can amplify the difference voltage which produces according to the current which flows through the shunt resistance connected to the motor actuator.

The amplifier for reference voltage generation is used as buffer amplifier for reference voltage generation.

As an external configuration of the current detection, it is available in either 1 shunt configuration or 3 shunt configuration.

Fig.3- a Motor-current detection circuit Block Diagram

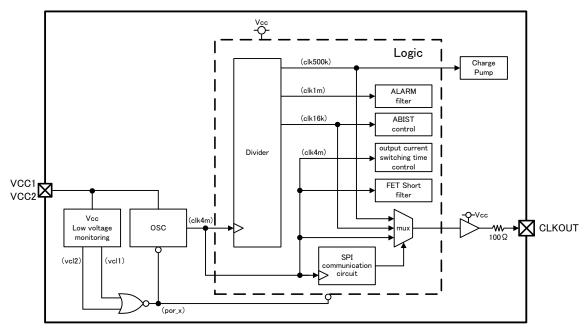

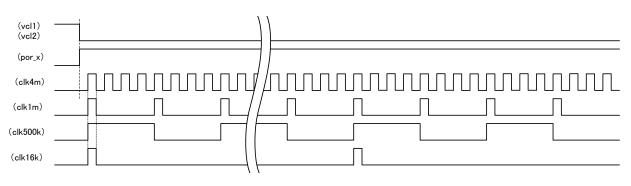

### (4) Oscillator /divider

The oscillator has composition with built-in CR, and an Oscillation frequency is Fc=4MHz (typ.). An oscillator will start operation after internal signal (por\_x) release.

4 MHz (clk4m) is used as the system clock of a logic circuit, and an operation clock of the digital filter of the short-circuit detector of external FET.

Clock 1MHz (clk1m), it is used as an operation clock of the digital filter of an ALARM detector.

Clock 500kHz (clk500k), it is used as an operation clock of a charge pump.

Clock 16kHz (clk16k), it is used as an operation clock of ABIST.

CLKOUT output (terminal) will output a clock set by the SPI (clk4m, clk500k, clk16k).

Fig.4- a Oscillator, divider Block Diagram

<Timing chart of divider>

Fig.4-b Timing chart of divider

### (5) Abnormal detection circuit

TB9081FG is built in miscellaneous abnormal detection circuit, such as the under voltage detection (VB1, VB2, VCC1, VCC2), over voltage detection (VCC1, VCC2), over temperature detection, external FET short-circuit detection and frequency abnormal detection.

The contents of a monitoring function list and the internal signal are shown below.

The details of operation are indicated in (5-1) and after.

When failure detection turns off the pre-driver circuit, the short-circuit detection function becomes invalid. When the operation returns from the abnormalities after that and the operation of a pre-driver circuit returns, a short-circuit detection function becomes effective again.

NDIAG SPI Initial Monitoring Setup Register ABIST **Operation in detection** \* Note 2 function Setup bit value writing \* Note 4 \*Note 1 \*Note 5 \_ L hold Valid 00 0 pre-driver circuit OFF VB1/VB2 01 Ο Ο pre-driver circuit OFF Т Under voltage 1\* pre-driver circuit OFF \_ Ο н Invalid L \_ \_ VCC1/VCC2 Pre-driver / charge pump / dividing circuit Under voltage OFF Valid 00 Pre-driver / charge pump circuit continued \_ Ο Ο L hold operation VCC1/VCC2 01 Pre-driver circuit OFF Ο Over voltage 10 Pre-driver / charge pump circuit OFF 11 pre-driver / charge pump circuit OFF-hold Valid 0 00 Ο L hold Pre-driver / charge pump circuit continued operation Over 01 pre-driver circuit OFF \_ temperature 10 0 pre-driver / charge pump circuit OFF 11 pre-driver / charge pump circuit OFF-hold Valid 000 Ο L hold Pre-driver / charge pump circuit continued \_ operation 001 Pre-driver-circuit(only detection phase ) OFF 010 Ο Pre-driver circuit (only detection phase) OFF-hold 011 Pre-driver circuit (all phases) OFF External FET \_ Short-circuit 100 Pre-driver circuit (all phases) OFF-hold \_ 101 Pre-driver (all phases) / charge pump circuit \_ OFF 110 \_ Pre-driver (all phases) / charge pump circuit OFF-hold 111 No detection н Valid 000 0 0 L hold Pre-driver / charge pump circuit continued operation (Low 001 Pre-driver circuit OFF \_ frequency) Abnormalities 010 Pre-driver / charge pump circuit OFF \_ in frequency 011 Pre-driver / charge pump OFF-hold \_ 1\*\* 0 No detection Н Valid 0 Ο Pre-driver OFF, when inputting inhibit н Pre-driver signals. prohibition charge pump circuit continued operation input 1 Pre-driver OFF, when inputting inhibit \_ Ο L hold detection signals. \*Note 3 charge pump circuit continued operation SPI Invalid Pre-driver / charge pump circuit continued \_ 0 L hold communication operation error

Monitoring function list

\*:don't care

- Note 1) It describes about Pre-driver, charge pump and divider. The definition of OFF and OFF-hold is as follows. OFF: the operation after returning from an abnormal state is possible. OFF-hold: Hold OFF even after returning from an abnormal state.

- Note 2) It describes about NDIAG operation in detection.

- The `L hold` hold the output NDIAG=L even after releasing from the abnormal detection.

- Note 3) If register setting=0, there is no register writing and NDIAG becomes H, even in case of the abnormal detection.

- If register setting=1, it has register writing and NDIAG becomes L, in case of the abnormal detection.

- Note 4) if set to other than `L hold` in NDIAG, register will be cleared and NDIAG=H by recovering from the abnormal detection,

- Note 5) Both Pre-driver circuit (all phases) OFF and Pre-driver circuit OFF turn off power relay and motor relay Pre-driver. Pre-driver-circuit(only detection phase) OFF turns off the high side and the low side Pre-driver of detected phase only.

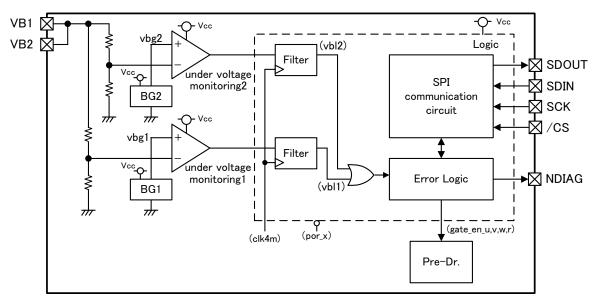

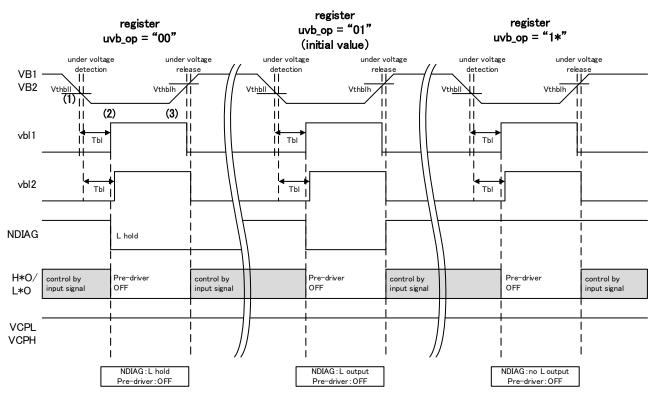

### (5-1) VB1/VB2 under voltage detection

Under voltage detection of VB1/VB2 is performed. Two detection comparators and two filters are built in. If at least one filter outputs "H", under voltage detection is performed. The band gap voltage recognized as the reference of a detection comparator is generated from a separate band gap circuit (BG1 and BG2).

Fig.5-1a VB1/VB2 under voltage detection Block Diagram

### A-(1) Under voltage of Vb

If VB1 voltage and VB2 voltage are less than the threshold value of the under voltage detection voltage (vthbll), L detection comparator of Vb outputs "H".

### ➤ A-(2) Under voltage detection of Vb

After the detection filter time (Tbl), Vb under voltage detection signal (vbl1 and vbl2) outputs high, the under voltage state is detected, and the pre-driver circuit is turned off. The oscillating circuit and the charge pump circuit are not turned off.

The pre-driver circuit holds OFF until the under voltage is released.

The NDIAG output state after detection can be chosen among the 3 modes through SPI communication.

A setup does not become effective even if the mode is changed in Vb under voltage detection state. The setup becomes effective after Vb under voltage is released and the register (uvb) is cleared.

#### > A-(3) Return of Vb voltage (under voltage release)

If VB1 voltage and VB2 voltage exceed vthblh, Vb under voltage detection signal (vbl1 and vbl2) outputs low, the under voltage state is released, and the pre-driver circuit recovers to the normal operation. In case NDIAG outputs low, it outputs high when the register (uvb) is cleared through SPI communication.

During under voltage detection, NDIAG outputs low because the register (uvb) is not cleared.

Fig.5-1b Timing chart of VB1/VB2 under voltage detection

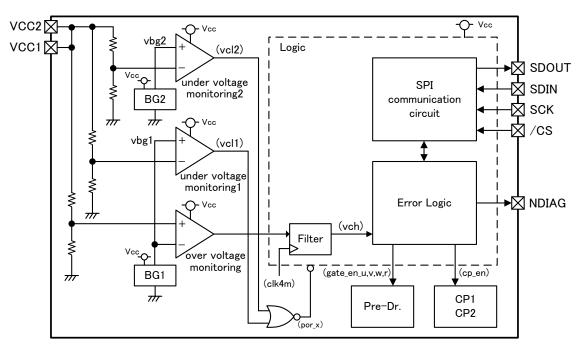

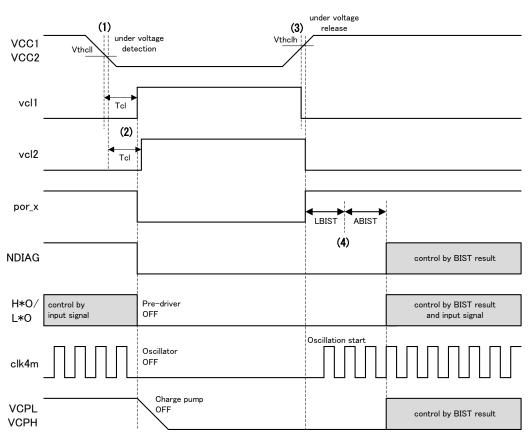

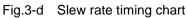

## (5-2) VCC1/VCC2 under voltage detection

Under voltage detection of VCC1/VCC2 is performed. Two detection comparators are built in. If at least one comparator outputs "H", under voltage detection is performed. The band gap voltage recognized as the reference of a detection comparator is generated from a separate band gap circuit (BG1 and BG2).

Fig.5-2a VCC1/VCC2 under voltage detection Block Diagram

### ➤ B-(1) Under voltage of Vcc

VCC1 voltage and VCC2 voltage are less than the threshold value of the under voltage detection voltage (vthcll).

### ➤ B-(2) Under voltage detection of Vcc

After the response relaxation time (Tcl), Vcc under voltage detection signal (vcl1 and vcl2) outputs high, the under voltage state is detected, por\_x outputs low, and NDIAG outputs low. Then, the pre-driver circuit, the charge pump, and the oscillating circuit are turned off.

Each circuit holds OFF until the under voltage is released.

### B-(3) Return of Vcc voltage (under voltage release)

If VCC1 voltage and VCC2 voltage exceed vthclh, Vcc under voltage detection signal (vcl1 and vcl2) outputs low, and the under voltage state is released.

### B-(4) Recover of normal operation

After LBIST and ABIST are performed, the normal operation recovers in case the judgment of BIST "OK". The charge pump circuit starts operation and the pre-driver circuit is turned on. In case the judgment of BIST "NG", the charge pump circuit and the pre-driver circuit do not operate. NDIAG outputs high in the judgment of "OK", and low in the judgment of "NG".

Fig.5-2b Timing chart of VCC1/VCC2 under voltage detection

\* When Vcc is lower than the detection voltage of Vcc under voltage further, IC will be the stand-by state. In the stand-by state, functions other than Vcc under voltage detection are turned off.

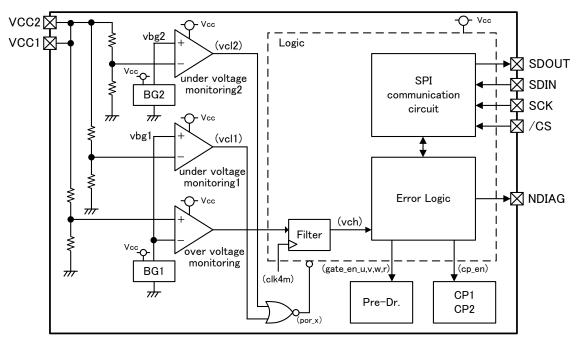

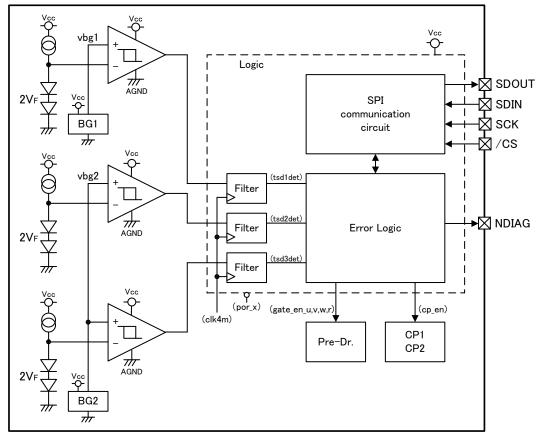

## (5-3) VCC1/VCC2 over voltage detection

Over voltage detection of VCC1/VCC2 is performed. The detection comparator and the filter are built in. If the filter outputs high, over voltage detection is performed.

Fig.5-3a VCC1/VCC2 over voltage detection Block Diagram

#### C-(1) Vcc voltage rise

If VCC1 voltage and VCC2 voltage exceed the threshold value of over voltage detection (vthchh), H detection comparator of Vcc outputs high.

C-(2) Over voltage detection of Vcc

After the detection filter time (Tch), Vcc over voltage detection signal (vch) outputs high and NDIAG outputs low.

The operation after detection can be chosen among 4 modes through SPI communication.

A setup does not become effective even if the mode is changed in Vcc over voltage detection state. The setup becomes effective after Vcc over voltage is released and the register (ovc) is cleared.

### >C-(3) Return of Vcc voltage (over voltage release)

If VCC1 voltage and VCC2 voltage are less than vthchl, Vcc over voltage detection signal (vch) outputs low and the over voltage is released.

In the case of register ovc\_op is 11, even if the over voltage is released, each circuit continues OFF and NDIAG keeps outputting low. When the register (ovc\_op) is 00, 01, and 10, each circuit operates normally and NDIAG keeps outputting low. When the register (ovc) is cleared through SPI communication, each circuit operates normally and NDIAG outputs high.

During over voltage detection, the register (ovc) is not cleared and NDIAG outputs low.

Fig.5-3b Timing chart of VCC1/VCC2 over voltage detection

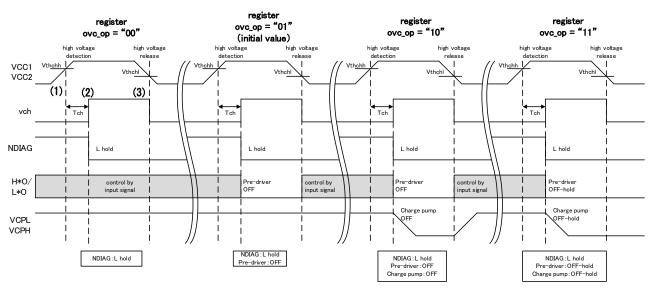

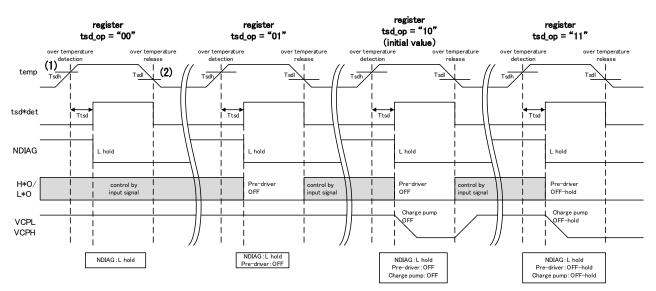

### (5-4) Over temperature detection

Three over temperature detection comparators are built in. Three detection comparators and three filters are built in. If at least one filter outputs high, the over temperature detection becomes effective.

The band gap voltage recognized as the reference of a detection comparator is generated from two band gap circuits (BG1 and BG2).

When chip temperature exceeds 170°C, the comparator switches and the over temperature is detected. The operation after detection can be chosen among 4 modes through SPI communication. When IC internal temperature becomes 160°C or less, the over temperature detection is released.

Fig.5-4a Over temperature detection Block Diagram

21

### D-(1) Over temperature detection

If the temperature exceeds Tsdh, after the detection filter time (Ttsd), the over temperature detection signal (tsd1 to 3det) outputs high, and the over temperature is detected.

The operation after detection can be chosen among 4 modes through SPI communication.

A setup does not become effective even if the mode is changed during over temperature state. The setup becomes effective when the over temperature state is released and the register (tsd\*det) is cleared.

### D-(2) Release of over temperature detection

If temperature is less than Tsdl, the over temperature detection signal (tsd1 to 3det) outputs low, and the over temperature detection is released.

When register (tsd\_op) is 11, even if the over temperature detection is released, each circuit continues OFF and NDIAG leeps outputting low. When the register (tsd\_op) is 00, 01, and 10, each circuit operates normally. However, NDIAG holds low. When the register (tsd\*det) is cleared through SPI communication, each circuit operates normally and NDIAG outputs high.

During over temperature detection, the register (tsd\*det) is not cleared and NDIAG outputs low.

Fig.5-4b Timing chart of over temperature detection

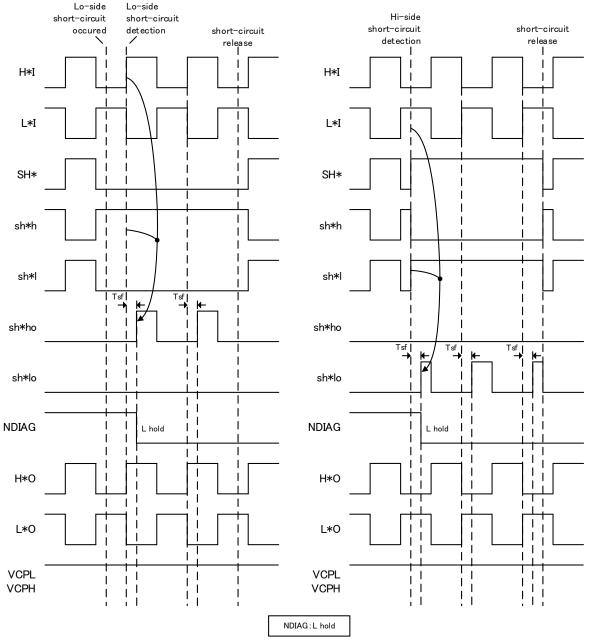

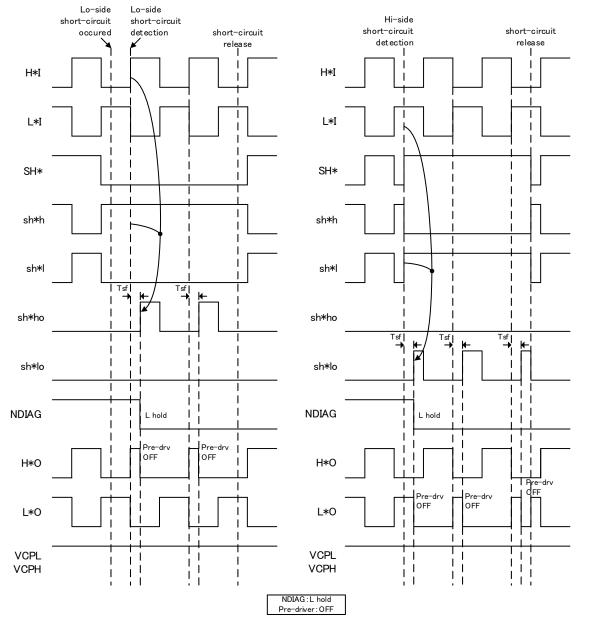

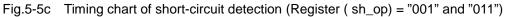

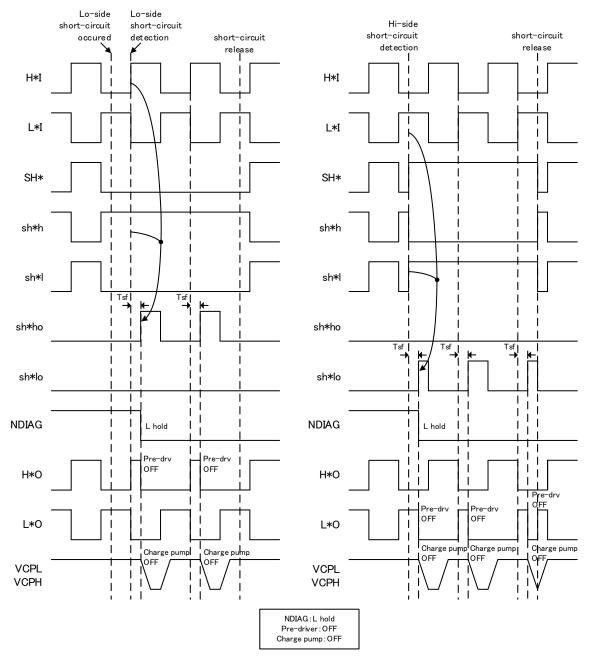

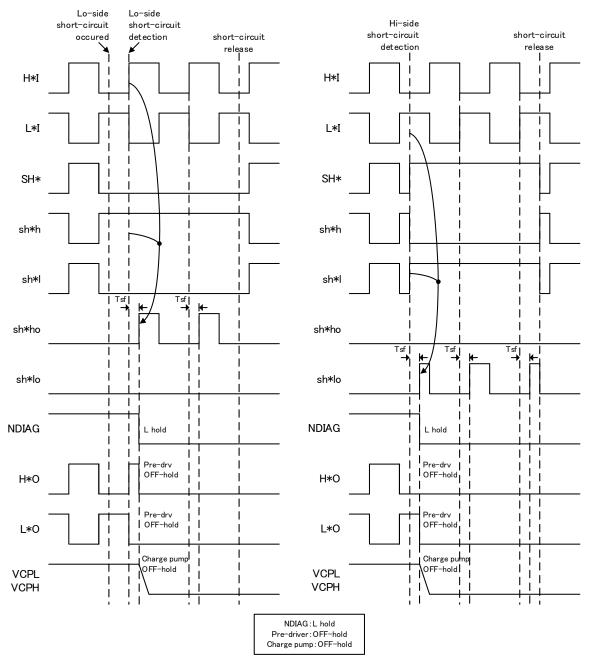

### (5-5) Short-circuit detection

Short-circuit of external MOSFET is detected by monitoring the dorain terminal and the source terminal of the external MOSFET.

When short-circuit is detected, the operation after detection can be chosen among 8 modes through SPI communication.

Moreover, detection threshold voltage and detection time can be set from four values through SPI communication.

At the time of short-circuit detection release, in case that the register (sh\_op) is 010, 100, and 110, even if short-circuit detection is released, each circuit continues OFF and NDIAG holds L. When the register (tsd\_op) is 000, 001, 011, and 101, each circuit operates normally, but NDIAG holds L. When the register (sc\*\*) is cleared through SPI communication, each circuit operates normally and NDIAG outputs high.

Fig.5-5a Short-circuit detection Block Diagram

#### •Table5-5a Short-circuit detection state

| Comparator input | Comparator output | Input signal | Abnormal condition                   |

|------------------|-------------------|--------------|--------------------------------------|

| SHU > LREF       | shul = H          | LUI = H      | External MOSFET short-circuit of HUO |

| SHV > LREF       | shvl = H          | LVI = H      | External MOSFET short-circuit of HVO |

| SHW > LREF       | shwl = H          | LWI = H      | External MOSFET short-circuit of HWO |

| SHU < HREF       | shuh = H          | HUI = H      | External MOSFET short-circuit of LUO |

| SHV < HREF       | shvh = H          | HVI = H      | External MOSFET short-circuit of LVO |

| SHW < HREF       | shwh = H          | HWI = H      | External MOSFET short-circuit of LWO |

\* HREF = HS- Vthh\_sh (detection threshold voltage of the High side), LREF = Vthl\_sh (detection threshold voltage of the Low side)

\* The detection threshold voltage of the High side is specified between HS and SH\* of the IC terminal.

Please set up the threshold value of HREF in consideration of the generating voltage by external resistance of HS terminal and SH\* terminal, and the voltage between drain and source of MOSFET of the High side.

\* The detection threshold voltage of the Low side is specified between SH\* and PGND(s) of the IC terminal.Please set up the threshold value of LREF in consideration of the generating voltage by external resistance of SH\* terminal, the generating voltage by the shunt resistance for current detection, and the voltage between drain and source of MOSFET of the Low side.

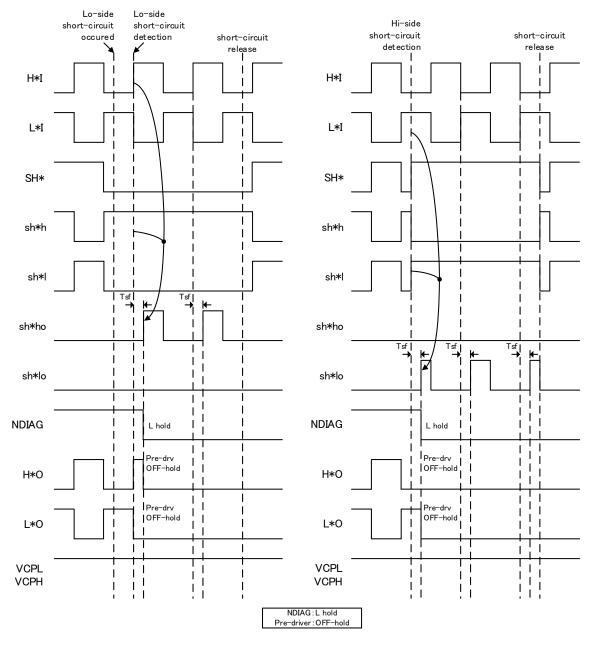

register sh\_op = "000"

Fig.5-5b Timing chart of short-circuit detection (Register (sh\_op) = "000")

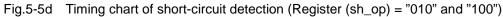

### register sh\_op = "001", "011"

\* "001" : Pre-driver OFF in only a detection phase. "011": Pre-driver OFF in all phase

register sh\_op = "010"(initial value), "100"

\*"010": Pre-driver OFF in only a detection phase "100": Pre-driver OFF in all phase

register sh\_op = "101"

Fig.5-5e Timing chart of short-circuit detection (Register (sh\_op) = "101")

register sh\_op = "110"

Fig.5-5f Timing chart of short-circuit detection (Register (sh\_op) = "110")

### (5-6) Oscillating frequency monitoring

It detects the abnormality in frequency when oscillating frequency is low and high.

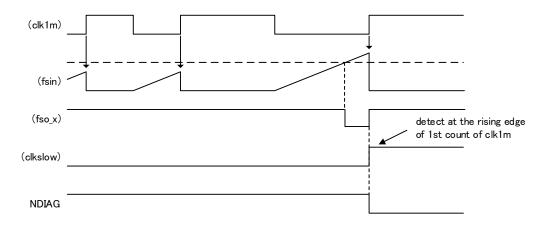

The low frequency detection circuit of oscillating frequency resets the input of a comparator for every clk1m. If the frequency becomes low and reset is overdue, the output of a comparator is reversed and the abnormality in frequency is detected at the rising edge of the following clk1m.

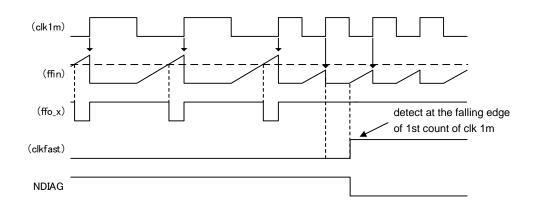

In the high frequency detection circuit of the oscillating frequency, a comparator repeats H/L output for every clk1m. When oscillating frequency becomes high, a detection comparator continues outputting H, and the detection comparator continues outputting H at the falling edge of 1st count of clk1m, the abnormality in high frequency is detected.

The operation in failure detection can be chosen among 5 modes through SPI communication.

A setup does not become effective even if the mode is changed in the frequency failure detection state. The setup becomes effective after the abnormality in frequency are released and the register (err\_of and err\_uf) is cleared.

Abnormality of frequency is not detected in case that the register (ferr\_op) is 1\*\*.

When frequency failure detection is released, in case that the register (ferr\_op) is 011, even if frequency failure detection is released, each circuit continues OFF and NDIAG holds L. In case that the register (ferr\_op) is 000, 001, and 010, each circuit recovers to the normal operation. However, NDIAG holds L. When the register (err\_of and err\_uf) is cleared through SPI communication, each circuit recovers to the normal operation and NDIAG outputs high.

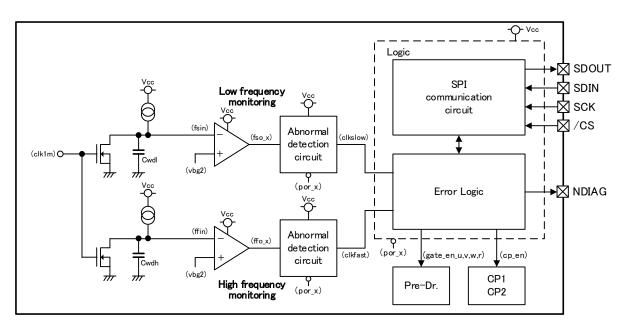

Fig.5-6a Frequency monitoring circuit

Fig.5-6b Timing chart of frequency monitoring (Low frequency)

Fig.5-6c Timing chart of frequency monitoring (High frequency)

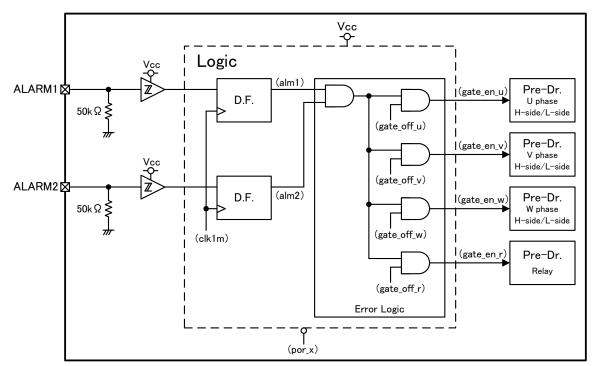

### (6) ALARM input circuit

As an input terminal of an ALARM signal, TB9081FG have two terminals of ALARM1 and ALARM2. An ALARM signal controls Enable/Disable of the Pre-drivers (a FET drive circuit, a motor relay drive

circuit, a power supply relay drive circuit).

In the case of ALARM1= "L" or ALARM2= "L", the Pre-drivers will be Disable. In the case of ALARM1="H" and ALARM2="H", Enable/Disable is decided by the input and internal signal of each Pre-drivers.

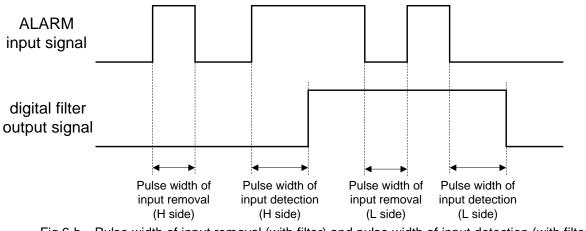

Also, the input side of the ALARM1 and ALARM2 terminal has a built-in digital filter (D.F.) for noise removal. Digital filter time can be set through the SPI communication.

If ALARM1="L" or ALARM2="L" is detected, the short-circuit detection function is enabled.

Fig.6-a FET drive circuit control Block Diagram

| Table 6-a | FET drive circuit control truth table |  |

|-----------|---------------------------------------|--|

|           |                                       |  |

| Input  | signal | Internal input signal |              |              |              |              |             | Internal control signal |             |             |                    |  |

|--------|--------|-----------------------|--------------|--------------|--------------|--------------|-------------|-------------------------|-------------|-------------|--------------------|--|

| ALARM1 | ALARM2 | (por_x)               | (gate_off_u) | (gate_off_v) | (gate_off_w) | (gate_off_r) | (gate_en_u) | (gate_en_v)             | (gate_en_w) | (gate_en_r) | circuit            |  |

| L      | *      | *                     | *            | *            | *            | *            | L           | L                       | L           | L           | Disable            |  |

| *      | L      | *                     | *            | *            | *            | *            | L           | L                       | L           | L           | Disable            |  |

| *      | *      | L                     | *            | *            | *            | *            | L           | L                       | L           | L           | Disable            |  |

| н      | Н      | Н                     | L            | -            | -            | -            | L           | -                       | -           | -           | U phase<br>Disable |  |

| н      | Н      | Н                     | Н            | -            | -            | -            | Н           | -                       | -           | -           | U phase<br>Enable  |  |

| н      | Н      | Н                     | -            | L            | -            | -            | -           | L                       | -           | -           | V phase<br>Disable |  |

| н      | н      | Н                     | -            | Н            | -            | -            | -           | Н                       | -           | -           | V phase<br>Enable  |  |

| н      | Н      | Н                     | -            | -            | L            | -            | -           | -                       | L           | -           | W phase<br>Disable |  |

| н      | Н      | Н                     | -            | -            | Н            | -            | -           | -                       | Н           | -           | W phase<br>Enable  |  |

| Н      | Н      | Н                     | -            | -            | -            | L            | -           | -                       | -           | L           | Relay Disable      |  |

| Н      | Н      | Н                     | -            | -            | -            | Н            | -           | -                       | -           | Н           | Relay Enable       |  |

(Note 1) "\*": Don't care

(Note 2) Although "-":gate\_off\_\* and gate\_en\_\* have logic dependence in phase, the logic dependence to other phase is nothing.

## (7) EN\_CP input circuit

EN\_CP signal controls Enable/Disable of a charge pump circuit.

In the case of input signal EN\_CP= "L", the charge pump circuit will be Disable. In the case of EN\_CP="H", Enable/Disable of the charge pump circuit is decided by an internal signal.

Also, the charge pump SW circuit (CP\_SW) will be Disable in case of input signal EN\_CP = "L" or the internal signal (por\_x) = "L". In the case of EN\_CP = (por\_x) = "H", it will be Enable.

Fig.7-a EN\_CP input circuit Block Diagram

| Table 7-a Cha | ge-pump-circuit control truth table |

|---------------|-------------------------------------|

|---------------|-------------------------------------|

| Input signal | I Internal input signal |          | Internal control signal | Charge pump | Charge pump |  |

|--------------|-------------------------|----------|-------------------------|-------------|-------------|--|

| EN_CP        | (por_x)                 | (cp_off) | (cp_en)                 | circuit     | SW circuit  |  |

| L            | *                       | *        | L                       | Disable     | Disable     |  |

| Н            | L                       | *        | L                       | Disable     | Disable     |  |

| Н            | Н                       | L        | L                       | Disable     | Enable      |  |

| Н            | Н                       | Н        | Н                       | Enable      | Enable      |  |

(Note) "\*":Don't care

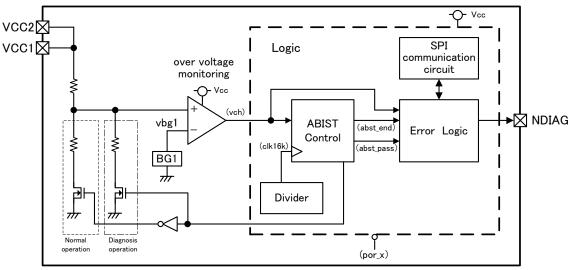

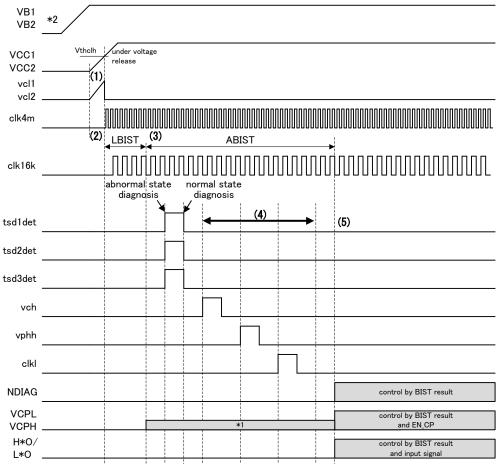

## (8) ABIST function

At the time of IC starting, it is diagnosed whether miscellaneous abnormal detection is functioning normally.

At the time of IC starting, a divider starts operation after VCC1/VCC2 under voltage release, and it starts diagnosis of ABIST after LBIST completion. Diagnosis of ABIST is performed even when a judgment of LBIST is NG.

At the time of ABIST starting, the input voltage of the comparator is changed by the switch for diagnosis, and each detection comparator is reversed. Then, the diagnosis is performed. Diagnosis is performed in order synchronizing with a clock (clk16k), and diagnostic information is input to the ABIST judgment circuit. Also, NDIAG=L is kept during the diagnosis.

After completion of all diagnosis, the IC switches to the normal operation. When the abnormal detection is not diagnosed, NDIAG will be H. When the abnormal detection is diagnosed, NDIAG will be L and keep the diagnosis information.

A diagnostic part is as follows.

VCC1/VCC2 over voltage detection, VCPH clamp voltage detection, over temperature detection, and frequency abnormal detection (low frequency side)

Fig.8-a ABIST Block Diagram (VCC1/VCC2 over voltage detection)

|   | Input signal | CP_SW circuit |        |         |         |  |  |  |  |

|---|--------------|---------------|--------|---------|---------|--|--|--|--|

|   | EN CP        | Before        | During | ABIST   | ABIST   |  |  |  |  |

|   | EN_CP        | ABIST         | ABIST  | OK      | NG      |  |  |  |  |

| ĺ | L            | Disable       | Enable | Disable | Disable |  |  |  |  |

|   | Н            | Enable        | Enable | Enable  | Enable  |  |  |  |  |

Table 8-a Circuit operation truth table (CP\_SW circuit)

Table 8-b Circuit operation truth table (charge pump circuit)

| Input signal | Charge pump circuit |                 |             |             |  |  |  |

|--------------|---------------------|-----------------|-------------|-------------|--|--|--|

| EN_CP        | Before<br>ABIST     | During<br>ABIST | ABIST<br>OK | ABIST<br>NG |  |  |  |

| L            | Disable             | Disable         | Disable     | Disable     |  |  |  |

| Н            | Disable             | Disable         | Enable      | Disable     |  |  |  |

Table 8-c Circuit operation truth table (pre-driver circuit)

| Input                 | signal | Pre-diver circuit |                 |             |             |  |  |

|-----------------------|--------|-------------------|-----------------|-------------|-------------|--|--|

| ALARM1                | ALARM2 | Before<br>ABIST   | During<br>ABIST | ABIST<br>OK | ABIST<br>NG |  |  |

| L                     | *      | Disable           | Disable         | Disable     | Disable     |  |  |

| *                     | L      | Disable           | Disable         | Disable     | Disable     |  |  |

| Н                     | Н      | Disable           | Disable         | Enable      | Disable     |  |  |

| (Note)"*": Don't care |        |                   |                 |             |             |  |  |

<ABIST whole operation / startup operation>

≻ H-(1) IC startup

At the time of IC starting, the divider is started the operation by the release of Vcc under voltage.

H-(2) LBIST running

OSHIBA

The divider starts the operation and starts the LBIST.

H-(3) ABIST start up

The ABIST is started after the LBIST.

The detection comparator is changed every 2clk of clk16k, and diagnosed whether the detection comparator is outputting the failure detection signal correctly.

The comparator for an over temperature detection is diagnosed to the beginning.

H-(4) Diagnosis

Each comparator is diagnosed as follows.

VCC1/VCC2 over voltage, VCPH cramp voltage, and a frequency monitoring (low frequency) > H-(5) ABIST completion

When all detection comparator diagnosis is completed, the IC switches to the normal operation mode, and the charge pump circuit starts the operation. Then the pre-driver can be ON. Also, the diagnosis result is output to the NDIAG.

In the case of the diagnosis NG, the charge pump circuit and the pre-driver circuit are kept OFF.

#### Fig.8-b ABIST timing chart

- \*1 Regardless of EN\_CP input signals, Vcph is equal to Vcpl=Vb-3VF (Vcpl<=16V) during running the ABIST.

- \*2 There is no start order of VB1/2, and VCC1/2.

- The slew rate of Vb and Vcc should be use in the following range. Less than Vb= $8V/\mu s$

- Less than Vcc= $0.3V/\mu s$

- \*3 When an abnormal detection of vphh is diagnosed, if Vb is lower than Vcc, maximum 10μA current flows in the cycle of 2clk of clk16k (125μs).

- \*4 The running time of LBIST and ABIST is about 2.4ms (typ.).

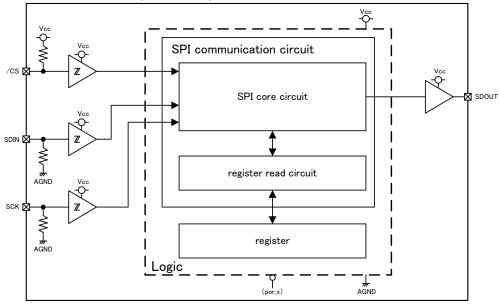

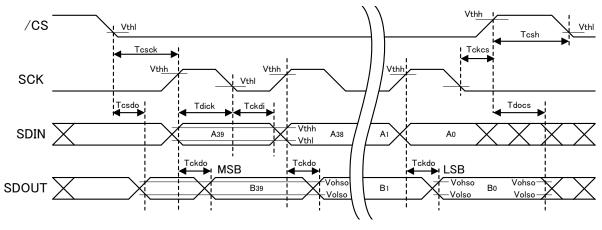

### (9) SPI Communication circuit

The SPI communication circuit consists of an SPI core circuit and a register read circuit block. Only when /CS is L, communication with a microcomputer is attained. A microcomputer writes data in SDIN at the rising edge of a clock, and IC reads data at the following falling edges. Moreover, IC writes data in SDOUT at the rising edge of a clock, and a microcomputer reads data at the following falling edges. SDIN receives the data bit from a microcomputer in order from MSB to LSB. SDOUT transmits a data bit to a microcomputer in order from MSB to LSB. An output is push-pull composition and will be a Hi-Z at the time of /CS="H". Moreover, inside IC, the /CS terminal have pull-up by resistance, and the SDIN and SCK terminal have pull-down by resistance.

Fig.9-a SPI Communication circuit Block Diagram

### (9-1) SPI Communication operation

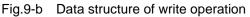

When /CS is L, the serial data are transmitted or received synchronizing with the SCK. When /CS is H, the SDOUT output will be a high impedance. The data length is 40 bits. As a function, there are two kinds, the read operation and the write operation, and the write / read operation can be selected with "RW" bit. "Dummy" bit does not influence the operations.

#### <Write operation>

The data structure of the write operation is shown in Fig.9-b.

SDIN is consist of "RW" bit, "Address" bit, "Dummy" bit (2 bits), "Data" bit, "CRC" bit, and "Dummy" bit (16bits). "RW" bit is the bit to select the write or the read operation, and when "RW" bit='1,' the write operation is selected. "Address" bit is the bit to specify the address, and "Data" bit is the write data bit. Data of "Data" bit is written to "Address" bit. "CRC" bit is calculated by the micro controller, according to 16 bits of "RW" bit, "Address" bit, "Dummy" bit (2bits), and "Data" bit.

#### SDOUT is all "Dummy" bit.

In addition, perform the read operation after writing and confirm the correct data are written. Even if data are written to the empty bits, the data are not written.

| /CS   |               |                |                 |             |                      |              |  |  |  |  |  |

|-------|---------------|----------------|-----------------|-------------|----------------------|--------------|--|--|--|--|--|

| SCK _ |               |                |                 |             |                      |              |  |  |  |  |  |

| SDIN  | RW            | Address (5bit) | Dummy<br>(2bit) | Data (8bit) | CRC (8bit)           | Dummy(16bit) |  |  |  |  |  |

| SDOUT | Dummy (40bit) |                |                 |             |                      |              |  |  |  |  |  |

| -     |               |                |                 |             | ructure of write one | ration       |  |  |  |  |  |

#### <Read operation>

The data structure of the read operation is shown in Fig.9-c.

SDIN is consist of "RW" bit, "Address" bit, "Dummy" bit (10 bits), "CRC" bit and "Dummy" bit (16 bits). "RW" bit is the bit to select the write or the read operation, and at when "RW" bit='0', the read operation is selected. "Address" bit is the bit to specify the address, and the data are read from the address of "Address" bit. "CRC" bit is calculated by the micro controller, according to 16 bits of "RW" bit, "Address "bit, and "Dummy" bit (10 bits).

SDOUT is consist of "Dummy" bit (8 bits), "Data" bit, "Dummy" bit (16 bits), and "CRC" bit. The data read from the address of "Address" bit of the SDIN is output to "Data" bit. "CRC" bit outputs the value which is calculated from 8 bits of "Data" bit by the IC.

| /CS - | 7                                                                                                                                                                                                                                                                                                                                                                                                          |             |       |              |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|--------------|--|--|--|--|--|--|

| SCK   |                                                                                                                                                                                                                                                                                                                                                                                                            |             |       |              |  |  |  |  |  |  |

| SDIN  | RW         Address (5bit)         Dummy (10bit)         CRC (8bit)         Dummy (16bit)                                                                                                                                                                                                                                                                                                                   |             |       |              |  |  |  |  |  |  |

| _     |                                                                                                                                                                                                                                                                                                                                                                                                            |             |       |              |  |  |  |  |  |  |

| SDOUT | Dummy (8bit)                                                                                                                                                                                                                                                                                                                                                                                               | Data (8bit) | Dummy | Dummy(16bit) |  |  |  |  |  |  |

| An    | SDOUT     Dummy (8bit)     Data (8bit)     Dummy (16bit)     CRC (8bit)       Fig.9-c     Data structure of read operation             CRC error judgment>       An error judgment is performed by the CRC to confirm the data communication correctly.       The generation polynomial used for the calculation is the following.       x <sup>8</sup> +x <sup>4</sup> +x <sup>3</sup> +x <sup>2</sup> +1 |             |       |              |  |  |  |  |  |  |

In the case of CRC error, the operation is the following.

(1) In the case of write operation

The write data are not written to the IC.

| /cs                                                  |                     |     |     |   |           |              |     | CRC | error | When CRC error, data is not written in the IC |

|------------------------------------------------------|---------------------|-----|-----|---|-----------|--------------|-----|-----|-------|-----------------------------------------------|

| SDIN                                                 | W Adr1<br>Adr1 Data | CRC | Dum | ] | W<br>Adr2 | Adr2<br>Data | CRC |     | Dum   | X <b>≁</b>                                    |

| SDOUT                                                |                     | Dum |     | ] |           |              | Dum |     |       | ]                                             |

| Fig. 0. d. CPC error in the energy of write energian |                     |     |     |   |           |              |     |     |       |                                               |

Fig.9-d CRC error in the case of write operation

(2)In the case of read operation

Incorrect data are written to the CRC bit of the SCOUT in the same frame.

Then the micro controller detects a CRC error.

<In the case of Vcc under voltage detection>

The SPI communication cannot perform when Vcc under voltage is detected. And then, the SDOUT is fixed to 'L' (at the write and the read operation).

#### <Fail judgment>

In the following cases at the SPI communication, the IC judges it as a communication error, and 1 is written to err\_spi which is the register of the SPI communication error.

- (1) Access to the address which has no register

- (2) When data length is except 40 bits

#### (9-2) SPI Register Map

#### Table9-2aconfig 1(Address : 0x01)

| bit     | 7    | 7 6     |  | 5 4     |   | 3 2 1 |   |   |

|---------|------|---------|--|---------|---|-------|---|---|

| Symbol  | df_a | df_alm1 |  | df_alm2 |   | sh_op |   |   |

| DEFAULT | 1    | 1 1     |  | 1       | 0 | 1     | 0 | 0 |

| bit | Symbol  | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | df_alm1 | R/W | setting of ALARM1 Digital Filtering Time (H-side/L-side) (Fc=4MHz typ.)<br>"00" = (16x2 <sup>2</sup> /Fc) + (1/Fc)<br>"01" = (1000x2 <sup>2</sup> /Fc) + (1/Fc)<br>"10" = (2000x2 <sup>2</sup> /Fc) + (1/Fc)<br>"11" = (4000x2 <sup>2</sup> /Fc) + (1/Fc)                                                                                                                                                                                                                                                                                                     |

| 5:4 | df_alm2 | R/W | setting of ALARM2 Digital Filtering Time (H-side/L-side) (Fc=4MHz(typ.)<br>"00" = $(16x2^2/Fc) + (1/Fc)$<br>"01" = $(1000x2^2/Fc) + (1/Fc)$<br>"10" = $(2000x2^2/Fc) + (1/Fc)$<br>"11" = $(4000x2^2/Fc) + (1/Fc)$                                                                                                                                                                                                                                                                                                                                             |

| 3:1 | sh_op   | R/W | Response of Short circuit Detection<br>"000" = NDIAG: L (Hold)<br>"001" = NDIAG: L (Hold), Detected Phase Pre-Driver OFF (During detection)<br>"010" = NDIAG: L (Hold), Detected Phase Pre-Driver OFF (Hold)<br>"011" = NDIAG: L (Hold), All (eleven) Pre-Driver OFF (During detection)<br>"100" = NDIAG: L (Hold), All (eleven) Pre-Driver OFF (Hold)<br>"101" = NDIAG: L (Hold), All (eleven) Pre-Driver and Charge Pump OFF (During detection)<br>"110" = NDIAG: L (Hold), All (eleven) Pre-Driver and Charge Pump OFF (Hold)<br>"111" = Detection disable |

#### Table 9-2b config2 (Address : 0x02)

| bit     | 7 | 6 | 5 | 4   | 3   | 2   | 1   | 0     |

|---------|---|---|---|-----|-----|-----|-----|-------|

| Symbol  | - | - | - | ovc | _op | tsd | _op | pl_op |

| DEFAULT | 0 | 0 | 0 | 0   | 1   | 1   | 0   | 0     |

| bit | Symbol | R/W | Function                                                                                                                                                                                                                                                                                                                                           |

|-----|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:3 | ovc_op | R/W | Response of VCC1/VCC2 Over Voltage Detection<br>"00" = NDIAG:output "L" (Hold)<br>"01" = NDIAG:output "L" (Hold), All (eleven) Pre-Driver OFF<br>"10" = NDIAG:output "L" (Hold), All (eleven) Pre-Driver and Charge Pump OFF (During detection)<br>"11" = NDIAG:output "L" (Hold), All (eleven) Pre-Driver and Charge Pump OFF (Hold)              |

| 2:1 | tsd_op | R/W | Response of Over Temperature Detection<br>"00" = NDIAG:output "L" (Hold)<br>"01" = NDIAG:output "L" (Hold), All (eleven) Pre-Driver OFF (During detection)<br>"10" = NDIAG:output "L" (Hold), All (eleven) Pre-Driver and Charge Pump OFF (During detection)<br>"11" = NDIAG:output "L" (Hold), All (eleven) Pre-Driver and Charge Pump OFF (Hold) |

| 0   | pl_op  | R/W | Response of Prohibit Pre-Driver Output setting Detection<br>"0" = NDAIG:no outpu, During Prohibit input, Detected Phase Pre-Driver OFF<br>"1" = NDIAG:output "L" (Hold), During Prohibit input, Detected Phase Pre-Driver OFF                                                                                                                      |

Prohibit Pre-Driver Output Setting

: In case that High-side and Low-side Input of the same Phase are "H", the both High-side and Low-side Output are forced to be "L"

#### Table9-2cconfig3(Address : 0x03)

| bit     | 7   | 6      | 5 4 |        | 3 2 1 |         |   | 0 |

|---------|-----|--------|-----|--------|-------|---------|---|---|

| Symbol  | uvb | uvb_op |     | co_sel |       | ferr_op |   |   |

| DEFAULT | 0   | 1      | 0   | 0      | 1     | 0       | 0 | 0 |

| bit | Symbol  | R/W | Function                                                                                                                                                                                                                                                                                                                                                                   |

|-----|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | uvb_op  | R/W | Response of VB1/VB2 Low Voltage Detection<br>"00" = NDIAG:output "L" (Hold), All (eleven) Pre-Driver OFF (During detection)<br>"01" = NDIAG:output "L", All (eleven) Pre-Driver OFF (During detection)<br>"1*" = NDIAG:output "H", All (eleven) Pre-Driver OFF (During detection)                                                                                          |

| 5:4 | co_sel  | R/W | setting Monitoring Output Signal of "CLKOUT"<br>"00" = output "L"<br>"01" = clk4m 4MHz (typ.)<br>"10" = clk500k 500kHz(typ.)<br>"11" = clk16k 16kHz(typ.)                                                                                                                                                                                                                  |

| 3:1 | ferr_op | R/W | Response of Internal OSC Over/Low Frequency Detectioin<br>000 = NDIAG:output "L" (Hold)<br>001 = NDIAG:output "L" (Hold), All (eleven) Pre-Driver OFF (During detection)<br>010 = NDIAG:output "L" (Hold), All (eleven) Pre-Driver and Charge Pump OFF(During detection)<br>011 = NDIAG:output "L" (Hold), All (eleven) Pre-Driver and Charge Pump OFF (Hold)<br>1** = nop |

\* : don't care

Table9-2dconfig4(Address : 0x04)

| bit     | 7 | 6 | 5     | 4 | 3 | 2   | 1       | 0 |

|---------|---|---|-------|---|---|-----|---------|---|

| Symbol  | - |   | df_sh |   |   | _sh | vthl_sh |   |

| DEFAULT | 0 | 0 | 0     | 1 | 0 | 0   | 0       | 1 |

| bit | Symbol  | R/W | Function                                                                                                                                                       |

|-----|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4 | df_sh   | R/W | setting Digital Filtering Time of Short Circuit Detection (typ. at 4MHz)<br>"000" = 6μs<br>"001" = 8μs<br>"010" = 10μs<br>"011" = 12μs<br>"1**" = no Filtering |

| 3:2 | vthh_sh | R/W | setting Threshold Voltage of Short Circuit Detection (Hi-side)<br>"00" = 0.5V<br>"01" = 0.75V<br>"10" = 1.0V<br>"11" = 1.25V                                   |

| 1:0 | vthl_sh | R/W | setting Threshold Voltage of Short Circuit Detection (Lo-side)<br>"00" = 0.5V<br>"01" = 0.75V<br>"10" = 1.0V<br>"11" = 1.25V                                   |

\* : don't care

#### Table9-2econfig5(Address:0x05)

| bit     | 7     | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|-------|---------|---------|---------|---------|---------|---------|---------|

| Symbol  | rebst | diag_dg | shuh_dg | shul_dg | shvh_dg | shvl_dg | shwh_dg | shwl_dg |

| DEFAULT | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| bit | Symbol  | R/W | Function                                                                                                                                                                                    |

|-----|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | rebst   | R/W | BIST restart request by SPI Command<br>"0": nop<br>"1": restart BIST                                                                                                                        |

| 6   | diag_dg | R/W | NDIAG Diagnosis Check by SPI Command<br>"0": nop (NDIAG normal Operation)<br>"1": Forced output "L" from PIN"NDIAG"                                                                         |

| 5   | shuh_dg | R/W | Short Circuit Detection Diagnosis Check by SPI Command (U-Phase Lo-side)<br>"0": nop (Short Detection Norma Operation)<br>"1": Forced Short Circuit Detection (output "L" from PIN"NDIAG")  |

| 4   | shul_dg | R/W | Short Circuit Detection Diagnosis Check by SPI Command (U-Phase Hi-side)<br>"0": nop (Short Detection Norma Operation)<br>"1": Forced Short Circuit Detection (output "L" from PIN"NDIAG")  |

| 3   | shvh_dg | R/W | Short Circuit Detection Diagnosis Check by SPI Command (V-Phase Lo-side))<br>"0": nop (Short Detection Norma Operation)<br>"1": Forced Short Circuit Detection (output "L" from PIN"NDIAG") |

| 2   | shvl_dg | R/W | Short Circuit Detection Diagnosis Check by SPI Command (V-Phase Hi-side)<br>"0": nop (Short Detection Norma Operation)<br>"1": Forced Short Circuit Detection (output "L" from PIN"NDIAG")  |

| 1   | shwh_dg | R/W | Short Circuit Detection Diagnosis Check by SPI Command (W-Phase Lo-side)<br>"0": nop (Short Detection Norma Operation)<br>"1": Forced Short Circuit Detection (output "L" from PIN"NDIAG")  |

| 0   | shwl_dg | R/W | Short Circuit Detection Diagnosis Check by SPI Command (W-Phase Hi-side))<br>"0": nop (Short Detection Norma Operation)<br>"1": Forced Short Circuit Detection (output "L" from PIN"NDIAG") |

- BIST restart by SPI Reg. "rebst" is enable when LBIST or ABIST is failure. In normal operation and LBIST/ABIST passed, the Write "rebst"=1 is ignored and do not restart BIST.

- Forced Short Circuit Detection:

- Output "L" from PIN "NDIAG"

- each detected Phase Pre-Driver OFF according to the setting by SPI Reg.

- "sh\_op"(address 0x01 bit1-3)

- Charge Pump OFF according to the setting by SPI Reg. "sh\_op"(config1)

- To write "0" into the SPI Reg. "sh\*\*\_dg", the above detection response are reset and return to normal operation.

- In case of SPI Reg. "sh\_op"="111"(config1), the above Short Circuit Detection Diagnosis does not performed, even write "1" into the above each Short Circuit Detection Diagnosis register.

#### Table9-2fconfig6(Address : 0x06)

| bit     | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|---------|---|---|---|---|---|---|-----|-----|

| Symbol  | - | - | - | - | - | - | t_i | lim |

| DEFAULT | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0   |

| bit | Symbol | R/W | Function                                                                                                                                                |

|-----|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | t_ilim | R/W | seting time of Current Limit disable after Turn On/Off (typ. at 4MHz)<br>"00" = 8μs<br>"01" = 16μs<br>"10" = 32μs<br>"11" = Always Current Limit enable |

The Current Limit is available for each Output of Pre-driver (HUO,HVO,HWO,LUO,LVO,LWO) (refer "Electrical characteristics"). These Current Limit are disabled the above period which is set by SPI Reg. "t\_ilim". For example, when "t\_ilim" is set "00", during  $8\mu$ s(typ.) after Turn On/Turn Off, there is no Current Limit and after  $8\mu$ s(typ.) passed, the Current Limit which is shown in the spec. is enable.

Current Limit of Turn On : lo\_lmth = 1mA (typ.) Current Limit of Turn Off : lo\_lmtl = 10mA (typ.)

#### Table9-2gstatus1(Address : 0x07)

| bit     | 7   | 6 | 5   | 4 | 3 | 2 | 1 | 0 |

|---------|-----|---|-----|---|---|---|---|---|

| NAME    | uvb | - | ovc | - | - | - | _ | - |

| DEFAULT | 0   | 0 | 0   | 0 | 0 | 0 | 0 | 0 |

| bit | Symbol | R/W | Function                                                                                         |

|-----|--------|-----|--------------------------------------------------------------------------------------------------|