CMOS Digital Integrated Circuit Silicon Monolithic

## TC358746AXBG/TC358748XBG

#### **Mobile Peripheral Devices**

#### Overview

The MIPI® CSI-2 to Parallel port and Parallel port to CSI-2 (TC358746AXBG/TC358748XBG) is a bridge device that converts MIPI data transfers from devices such as a camera to an application processor over a Parallel port interface. All internal registers can be access through I<sup>2</sup>C or SPI (in CSI out case only).

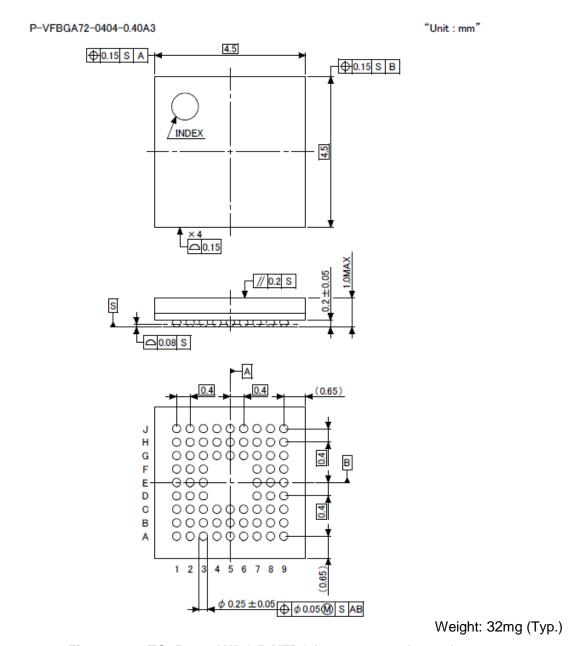

# TC358746AXBG P-VFBGA72-0404-0.40A3

Weight: 32 mg (Typ.)

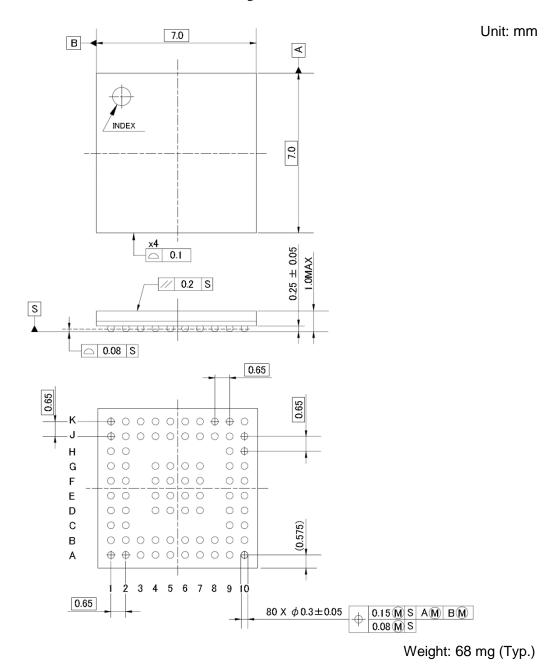

# P-VFBGA80-0707-0.65-001

Weight: 68 mg (Typ.)

#### **Features**

- CSI-2 TX/RX Interface

- → MIPI CSI-2 compliant (Version 1.01 Revision 0.04 2 April 2009)

- ♦ Configurable to TX or RX controller

- ♦ Supports up to 1Gbps per data lane

- ♦ Supports up to 4 data lanes

- Supports video data formats

- RX: RAW8/10/12/14, YUV422 (CCIR/ITU 8/10-bit), RGB888/666/565 and User-Defined 8-bit

- TX: YUV422 (CCIR/ITU 8/10-bit), YUV444, RGB888/666/565 and RAW8/10/12/14

- Parallel Port Interface

- ♦ Supports data formats

- 24-bit bus un-packed format (Both Input and Output mode)

- RGB888/666/565, RAW8/10/12/14 and YUV422 8-bit (on 8/16-bit data bus) and 10-bit data formats.

- > YUV444 (Parallel Input mode only)

- YUV422 8-bit ITU BT.656 and ITU BT.601 (Parallel input mode only)

- ➤ Up to 100 MHz PCLK frequency for Output mode, and 166 MHz for Input mode.

- I<sup>2</sup>C Slave Interface (CS = L)

- Support for normal (100 kHz), fast mode (400 kHz) and special mode (1 MHz)

- ♦ Configure all TC358746AXBG/TC358748XBG internal registers

- SPI Slave Interface (Only applicable in CSIOut configuration, MSEL = H, and CS = H)

- SPI interface support for up to 25 MHz operation.

- ♦ Configure all TC358746AXBG/TC358748XBG internal registers

#### • GPIO signals

- ♦ 3 GPIO signals

- Three GPIO signals can be configured as control signals (MCLK, CXRST, XShutdown) for CSI-2 RX device.

- Or one GPIO signal can be configured as INT signal for Parallel interface.

#### System

- Clock and power management support to achieve low power states.

- Power supply inputs

- ♦ I/O: 1.8 V 3.3 V

## Table of content

| REFERENCES                                                                                                                           | 5                           |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 1. Overview                                                                                                                          | 6                           |

| 2. Features                                                                                                                          | 8                           |

| 2.1. Typical Power Consumption                                                                                                       | 9                           |

| 3. External Pins                                                                                                                     | 10                          |

| 3.1. TC358746AXBG pinout description                                                                                                 | 10                          |

| 3.2. TC358746AXBG BGA72 pin Count Summary                                                                                            | 11                          |

| 3.3. TC358748XBG BGA80 Pin Count Summary                                                                                             | 11                          |

| 3.4. TC358746AXBG Pin Layout                                                                                                         | 12                          |

| 3.5. TC358748XBG Pin Layout                                                                                                          | 13                          |

| 4. Package                                                                                                                           | 14                          |

| 4.1. TC358746AXBG Package                                                                                                            | 14                          |

| 4.2. TC358748XBG Package                                                                                                             | 15                          |

| 5. Electrical Characteristics                                                                                                        | 16                          |

| 5.1. Absolute Maximum Ratings                                                                                                        | 16                          |

| 5.2. Operating Condition                                                                                                             | 16                          |

| 5.3. DC Electrical Specification                                                                                                     | 17                          |

| 6. Revision History                                                                                                                  | 18                          |

| RESTRICTIONS ON PRODUCT USE                                                                                                          | 19                          |

|                                                                                                                                      |                             |

| Table of Figures                                                                                                                     |                             |

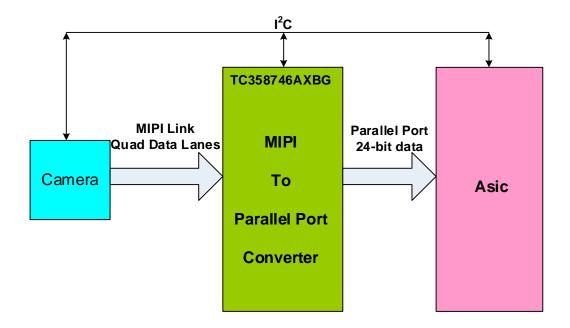

| Figure 1.1 System Overview with TC358746AXBG/TC358748XBG in CSI-                                                                     | -2 RX to Parallel Port      |

| Configuration                                                                                                                        | 6                           |

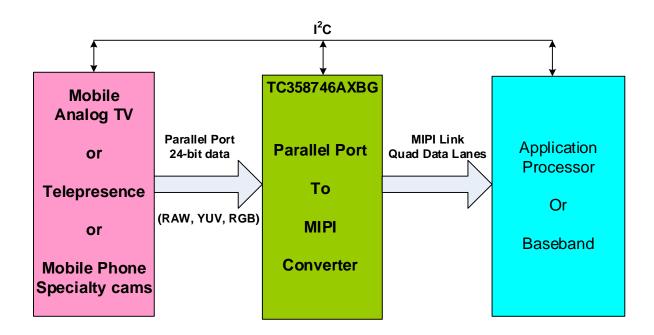

| Figure 1.2 System Overview with TC358746AXBG/TC358748XBG in Para<br>Configuration                                                    | llel Port to CSI-2 TX.<br>7 |

| Figure 3.1 TC358746AXBG BGA72-Pin Layout (Top View)                                                                                  | 12                          |

| Figure 3.2 TC358748XBG 80-Pin Layout (Top View)Figure 4.1 TC358746AXBG P-VFBGA72-0404-0.40A3 package                                 |                             |

| Figure 4.2 TC358748XBG P-VFBGA80-0707-0.65-001 package                                                                               |                             |

|                                                                                                                                      |                             |

| List of Tables                                                                                                                       |                             |

| Table 3.1 TC358746AXBG/ TC358748XBG Functional Signal List                                                                           | 10                          |

| Table 3.2 TC358746AXBG BGA 72Pin Count Summary                                                                                       | 11                          |

| Table 3.3 TC358748XBG BGA 80 Pin Count Summary                                                                                       | 11                          |

| Table 4.1 TC358746AXBG P-VFBGA72-0404-0.40A3 Mechanical Dimension Table 4.2 TC358748XBG P-VFBGA80-0707-0.65-001 Mechanical Dimension |                             |

| Table 6.1 Revision History                                                                                                           |                             |

• MIPI and SLIMbus are registered trademarks of MIPI Alliance, Inc.

#### 1 NOTICE OF DISCLAIMER

- 2 The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled

- 3 by any of the authors or developers of this material or MIPI. The material contained herein is provided on

- 4 an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS

- 5 AND WITH ALL FAULTS, and the authors and developers of this material and MIPI hereby disclaim all

- 6 other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if

- any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of

- 8 accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of

- 9 negligence.

- All materials contained herein are protected by copyright laws, and may not be reproduced, republished,

- distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express

- 12 prior written permission of MIPI Alliance. MIPI, MIPI Alliance and the dotted rainbow arch and all related

- 13 trademarks, tradenames, and other intellectual property are the exclusive property of MIPI Alliance and

- cannot be used without its express prior written permission.

- 15 ALSO, THERE IS NO WARRANTY OF CONDITION OF TITLE, QUIET ENJOYMENT, QUIET

- 16 POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD

- 17 TO THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT. IN NO EVENT WILL ANY

- 18 AUTHOR OR DEVELOPER OF THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT OR

- 19 MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE

- 20 GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL,

- 21 CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER

- 22 CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR

- 23 ANY OTHER AGREEMENT, SPECIFICATION OR DOCUMENT RELATING TO THIS MATERIAL,

- 24 WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH

- 25 DAMAGES.

- Without limiting the generality of this Disclaimer stated above, the user of the contents of this Document is

- 27 further notified that MIPI: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the

- 28 contents of this Document; (b) does not monitor or enforce compliance with the contents of this Document;

- and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance

- 30 with the contents of this Document. The use or implementation of the contents of this Document may

- 31 involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents,

- 32 patent applications, or copyrights owned by one or more parties, whether or not Members of MIPI. MIPI

- does not make any search or investigation for IPR, nor does MIPI require or request the disclosure of any

- 34 IPR or claims of IPR as respects the contents of this Document or otherwise.

- 35 Questions pertaining to this document, or the terms or conditions of its provision, should be addressed to:

- 36 MIPI Alliance, Inc.

- 37 c/o IEEE-ISTO

- 38 445 Hoes Lane

- 39 Piscataway, NJ 08854

- 40 Attn: Board Secretary

#### **REFERENCES**

- MIPI D-PHY, "MIPI\_D-PHY\_specification\_v01-00-00, May 14, 2009"

MIPI CSI-2, "MIPI Alliance Standard for Camera Serial Interface 2 (CSI-2) Version 1.01 Revision Nov 2010"

- 3. I<sup>2</sup>C bus specification, version 2.1, January 2000, Philips Semiconductor

2020-12-14 5 / 19

#### 1. Overview

The MIPI CSI-2 to Parallel port and Parallel port to CSI-2 (TC358746AXBG/TC358748XBG) is a bridge device that converts MIPI data transfers from devices such as a camera to an application processor over a Parallel port interface. All internal registers can be access through I<sup>2</sup>C or SPI (in CSI out case only).

There are several system configurations where TC358746AXBG/TC358748XBG are typically be used

- CSI-2 TX with Parallel Input mode for Analog TV, Tele-presence Type, and Specialty/Older Cameras application. In this mode, TC358746AXBG/TC358748XBG (Parallel to CSI-2 converter) is a bridge device that converts parallel data transfers to an application over a MIPI CSI-2 interface. Toshiba Bridge Chip provides a low power bridge solution to efficiently translate parallel transfers to serial transfers.

- CSI-2 RX with Parallel output mode for scanner application. In this mode, TC358746AXBG/TC358748XBG (CSI-2 to Parallel converter) is a bridge device that converts serial data transfers from devices such as a camera to an application processor over a parallel interface. Toshiba Bridge Chip provides a low power bridge solution to efficiently translate serial transfers to parallel transfers.

Figure 1.1 System Overview with TC358746AXBG/TC358748XBG in CSI-2 RX to Parallel Port Configuration

Figure 1.2 System Overview with TC358746AXBG/TC358748XBG in Parallel Port to CSI-2 TX Configuration

#### 2. Features

Below are the main features supported by TC358746AXBG/TC358748XBG.

- CSI-2 TX/RX Interface

- ♦ MIPI CSI-2 compliant (Version 1.01 Revision 0.04 2 April 2009)

- ♦ Configurable to TX or RX controller

- ♦ Supports up to 1Gbps per data lane

- Supports up to 4 data lanes

- Supports video data formats

- RX: RAW8/10/12/14, YUV422 (CCIR/ITU 8/10-bit), RGB888/666/565 and User-Defined 8-bit

- TX: YUV422 (CCIR/ITU 8/10-bit), YUV444, RGB888/666/565 and RAW8/10/12/14

- Parallel Port Interface

- Supports data formats

- 24-bit bus un-packed format (Both Input and Output mode)

- RGB888/666/565, RAW8/10/12/14 and YUV422 8-bit (on 8/16-bit data bus) and 10-bit data formats.

- > YUV444 (Parallel Input mode only)

- YUV422 8-bit ITU BT.656 and ITU BT.601 (Parallel input mode only)

- ♦ Up to 100 MHz PCLK frequency for Output mode, and 166 MHz for Input mode.

- I<sup>2</sup>C Slave Interface (CS = L)

- ♦ Support for normal (100 kHz), fast mode (400 kHz) and special mode (1 MHz)

- ♦ Configure all TC358746AXBG/TC358748XBG internal registers

- SPI Slave Interface (Only applicable in CSIOut configuration, MSEL = H, and CS = H)

- ♦ SPI interface support for up to 25 MHz operation.

- ♦ Configure all TC358746AXBG/TC358748XBG internal registers

- GPIO signals

- ♦ 3 GPIO signals

- Three GPIO signals can be configured as control signals (MCLK, CXRST, XShutdown) for CSI-2 RX device.

- Or one GPIO signal can be configured as INT signal for Parallel interface.

- System

- Clock and power management support to achieve low power states.

- Power supply inputs

- ♦ Core and MIPI D-PHY: 1.2 V

- ♦ I/O: 1.8 V 3.3 V

## 2.1. Typical Power Consumption

| Parallel_In → CSI_Out, 500 MHz CSICLk, 1080P @60fps     |       |       |      |       |  |  |  |

|---------------------------------------------------------|-------|-------|------|-------|--|--|--|

| VDDIO (3.3 V) VDDC (1.2 V) VDD_MIPI (1.2 V) Total Power |       |       |      |       |  |  |  |

| Current (mA)                                            | 0.44  | 40.4  | 24.5 |       |  |  |  |

| Power (mW)                                              | 1.452 | 48.48 | 29.4 | 79.33 |  |  |  |

| CSI_In → Parallel_Out, 500 MHz CSICLk, 100 MHz PClk ColorBar @60fps |       |       |       |       |  |  |  |

|---------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|

| VDDIO (3.3 V) VDDC (1.2 V) VDD_MIPI (1.2 V) Total Power             |       |       |       |       |  |  |  |

| Current (mA)                                                        | 18.9  | 13.9  | 12.3  |       |  |  |  |

| Power (mW)                                                          | 62.37 | 16.68 | 14.76 | 93.81 |  |  |  |

#### 3. External Pins

## 3.1. TC358746AXBG pinout description

TC358746AXBG/TC358748XBG resides in BGA pin packages. The following table gives the signals of TC358746AXBG/TC358748XBG and their function.

Table 3.1 TC358746AXBG/ TC358748XBG Functional Signal List

|                                    | -: ··                    | I/     | 0                                                                                                                                                                                                                                                                                                                              | _    | Initial                                                                                                                                                                                                                                                       | = - 4                                                                                                                                                                                                                                                                                                                   |      |

|------------------------------------|--------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Group                              | Pin Name                 | MSEL=0 | MSEL=1                                                                                                                                                                                                                                                                                                                         | Туре | (O)                                                                                                                                                                                                                                                           | Function                                                                                                                                                                                                                                                                                                                | Note |

|                                    | RESX                     | I      | I                                                                                                                                                                                                                                                                                                                              | Sch  | -                                                                                                                                                                                                                                                             | System reset input, active low                                                                                                                                                                                                                                                                                          | -    |

|                                    | REFCLK                   | 1      | I                                                                                                                                                                                                                                                                                                                              | N    | -                                                                                                                                                                                                                                                             | Reference clock input (6MHz – 40MHz)                                                                                                                                                                                                                                                                                    | -    |

|                                    | MSEL                     | I      | I                                                                                                                                                                                                                                                                                                                              | N    | -                                                                                                                                                                                                                                                             | Mode Select 1'b0: CSI-2 RX in -> Par_out 1'b1: Par_in -> CSI-2 TX                                                                                                                                                                                                                                                       | -    |

| System:<br>Reset &<br>Clock<br>(4) | CS                       | I      | Chip Select, active low MSEL= 0 (CSI-2 RX in -> Par_out) - When CS = 0, chip selected Normal operation - When CS = 1, chip not selected Cannot access to internal registers and optionally Parallel output ports can be tri-sta when 0x0004[15] is set MSEL= 1 (Par_in -> CSI-2 TX) - CS = 0, I <sup>2</sup> C I/F is selected |      | MSEL= 0 (CSI-2 RX in -> Par_out) - When CS = 0, chip selected Normal operation - When CS = 1, chip not selected Cannot access to internal registers and optionally Parallel output ports can be tri-state when 0x0004[15] is set MSEL= 1 (Par_in -> CSI-2 TX) | -                                                                                                                                                                                                                                                                                                                       |      |

|                                    | MIPI_CP                  | I      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI clock positive                                                                                                                                                                                                                                                                                                 | -    |

|                                    | MIPI_CN                  | I      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI clock negative                                                                                                                                                                                                                                                                                                 | -    |

|                                    | MIPI_D0P                 | ı      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI Data 0 positive                                                                                                                                                                                                                                                                                                | -    |

|                                    | MIPI_D0N                 | 1      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI Data 0 negative                                                                                                                                                                                                                                                                                                | -    |

| MIPI-CSI                           | MIPI_D1P                 | ı      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI Data 1 positive                                                                                                                                                                                                                                                                                                | _    |

| (10)                               | MIPI_D1N                 | 1      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI Data 1 negative                                                                                                                                                                                                                                                                                                | _    |

|                                    | MIPI_D2P                 | ı      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI Data 2 positive                                                                                                                                                                                                                                                                                                | -    |

|                                    | MIPI_D2N                 | I      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI Data 2 negative                                                                                                                                                                                                                                                                                                | -    |

|                                    | MIPI_D3P                 | I      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI Data 3 positive                                                                                                                                                                                                                                                                                                | -    |

|                                    | MIPI_D3N                 | I      | 0                                                                                                                                                                                                                                                                                                                              | PHY  | LP11                                                                                                                                                                                                                                                          | MIPI-CSI Data 3 negative                                                                                                                                                                                                                                                                                                | -    |

| I2C I/F                            | I2C_SCL                  | I      | - 1                                                                                                                                                                                                                                                                                                                            | Sch  | -                                                                                                                                                                                                                                                             | I <sup>2</sup> C serial clock or SPI_SCLK                                                                                                                                                                                                                                                                               | 4 mA |

| (2)                                | I2C_SDA                  | l      | l                                                                                                                                                                                                                                                                                                                              | Sch  | -                                                                                                                                                                                                                                                             | I <sup>2</sup> C serial data or SPI_MOSI                                                                                                                                                                                                                                                                                | 4 mA |

| Parallel                           | PD[23:0]                 | 0      | I                                                                                                                                                                                                                                                                                                                              | N    | L                                                                                                                                                                                                                                                             | Parallel Port Data - PD[23:12] can configure to be GPIO[15:4]                                                                                                                                                                                                                                                           | 4 mA |

| Port I/F                           | VVALID                   | 0      | I                                                                                                                                                                                                                                                                                                                              | N    | Н                                                                                                                                                                                                                                                             | Parallel port VVALID signal                                                                                                                                                                                                                                                                                             | 4 mA |

| (27)                               | HVALID                   | 0      | 1                                                                                                                                                                                                                                                                                                                              | N    | L                                                                                                                                                                                                                                                             | Parallel port HVALID signal                                                                                                                                                                                                                                                                                             | 4 mA |

|                                    | PCLK                     | 0      | 1                                                                                                                                                                                                                                                                                                                              | N    | L                                                                                                                                                                                                                                                             | Parallel Port Clock signal                                                                                                                                                                                                                                                                                              | 4 mA |

| GPIO (3)                           | GPIO[2:0]                | I      | ı                                                                                                                                                                                                                                                                                                                              | N    | -                                                                                                                                                                                                                                                             | GPIO[2:0] signals  CSI-2 RX in -> Par_out  - (GPIO[0] option to become MCLK signal)  - (GPIO[1] option to become CXRST or INT)  - (GPIO[2] option to become XShutdown)  Par_in -> CSI-2 TX  - (GPIO[0] option to become MCLK signal)  - (GPIO[1] option to become SPI_SS or INT)  - (GPIO[2] option to become SPI_MISO) | 4 mA |

|                                    | VDDC (1.2 V)             | NA     | -                                                                                                                                                                                                                                                                                                                              | -    | -                                                                                                                                                                                                                                                             | VDD for Internal Core (2)                                                                                                                                                                                                                                                                                               | -    |

| POWER                              | VDDIO (1.8 V –<br>3.3 V) | NA     | -                                                                                                                                                                                                                                                                                                                              | -    | -                                                                                                                                                                                                                                                             | VDDIO is for IO power supply (3)                                                                                                                                                                                                                                                                                        | -    |

| (9)                                | VDD_MIPI<br>(1.2 V)      | NA     | -                                                                                                                                                                                                                                                                                                                              | -    | -                                                                                                                                                                                                                                                             | VDD for the MIPI CSI2 (2)                                                                                                                                                                                                                                                                                               | -    |

| Ground<br>NOTE1                    | vss                      | NA     | -                                                                                                                                                                                                                                                                                                                              | -    | -                                                                                                                                                                                                                                                             | Ground                                                                                                                                                                                                                                                                                                                  | -    |

NOTE1: TC358746AXBG = 17, TC358748XBG = 25

## 3.2. TC358746AXBG BGA72 pin Count Summary

Table 3.2 TC358746AXBG BGA 72Pin Count Summary

| Group Name        | Pin<br>Count | Notes                   |

|-------------------|--------------|-------------------------|

| SYSTEM            | 4            | -                       |

| MIPI-CSI          | 10           | -                       |

| I2C I/F           | 2            | -                       |

| GPIO              | 3            | -                       |

| Parallel Port I/F | 27           | -                       |

| POWER             | 9            | IO, MIPI and Core Power |

| GROUND            | 17           | -                       |

| TOTAL             | 72           |                         |

## 3.3. TC358748XBG BGA80 Pin Count Summary

Table 3.3 TC358748XBG BGA 80 Pin Count Summary

| Group Name        | Pin<br>Count | Notes                   |

|-------------------|--------------|-------------------------|

| SYSTEM            | 4            | -                       |

| MIPI-CSI          | 10           | -                       |

| I2C I/F           | 2            | -                       |

| GPIO              | 3            | -                       |

| Parallel Port I/F | 27           | -                       |

| POWER             | 9            | IO, MIPI and Core Power |

| GROUND            | 25           | -                       |

| TOTAL             | 80           |                         |

## 3.4. TC358746AXBG Pin Layout

| A1   | A2   | А3    | A4   | <b>A</b> 5 | А6    | A7       | A8       | А9       |

|------|------|-------|------|------------|-------|----------|----------|----------|

| VSS  | PD17 | PD19  | PD21 | PD23       | GPIO2 | I2C SCL  | MSEL     | VSS      |

| B1   | B2   | В3    | В4   | <b>B</b> 5 | В6    | В7       | B8       | В9       |

| VDDC | PD16 | PD18  | PD20 | PD22       | GPIO1 | I2C SDA  | RESX     | VDDIO    |

| C1   | C2   | С3    | C4   | C5         | C6    | C7       | C8       | C9       |

| PD15 | PD14 | VSS   | VSS  | VSS        | VSS   | VDD MIPI | MIPI D3P | MIPI D3N |

| D1   | D2   | D3    |      |            |       | D7       | D8       | D9       |

| PD13 | PD12 | VSS   |      |            |       | VSS      | MIPI_D2P | MIPI_D2N |

| E1   | E2   | E3    |      |            |       | E7       | E8       | E9       |

| VSS  | VSS  | VDDC  |      |            |       | VDD MIPI | MIPI CP  | MIPI CN  |

| F1   | F2   | F3    |      |            |       | F7       | F8       | F9       |

| VSS  | VSS  | VSS   |      |            |       | VSS      | MIPI D1P | MIPI D1N |

| G1   | G2   | G3    | G4   | G5         | G6    | G7       | G8       | G9       |

| PD11 | PD10 | VDDIO | VSS  | VSS        | VDDIO | VDDIO    | MIPI_D0P | MIPI_D0N |

| H1   | H2   | Н3    | H4   | Н5         | Н6    | H7       | Н8       | Н9       |

| VDDC | PD8  | PD6   | PD4  | PD2        | PD0   | PCLK     | HVALID   | cs       |

| J1   | J2   | J3    | J4   | J5         | J6    | J7       | J8       | J9       |

| VSS  | PD9  | PD7   | PD5  | PD3        | PD1   | REFCLK   | VVALID   | GPIO0    |

Figure 3.1 TC358746AXBG BGA72-Pin Layout (Top View)

## 3.5. TC358748XBG Pin Layout

| A1    | A2   | А3   | <b>A</b> 4 | <b>A</b> 5 | <b>A</b> 6 | A7        | <b>A8</b> | Α9       | A10      |

|-------|------|------|------------|------------|------------|-----------|-----------|----------|----------|

| VSS   | PD17 | PD19 | PD21       | PD23       | GPIO2      | VDDC      | I2C_SCL   | MSEL     | VSS      |

| B1    | B2   | В3   | B4         | B5         | В6         | B7        | B8        | В9       | B10      |

| VDDC  | PD16 | PD18 | PD20       | PD22       | GPIO1      | VSS       | I2C_SDA   | RESX     | VDDIO    |

| C1    | C2   | C3   | C4         | C5         | C6         | C7        | C8        | С9       | C10      |

| PD15  | PD14 |      |            |            |            |           |           | MIPI_D3P | MIPI_D3N |

| D1    | D2   | D3   | D4         | D5         | D6         | D7        | D8        | D9       | D10      |

| PD13  | PD12 |      | VSS        | VSS        | VSS        | VSS       |           | MIPI_D2P | MIPI_D2N |

| E1    | E2   | E3   | E4         | <b>E</b> 5 | E6         | E7        | E8        | E9       | E10      |

| PD11  | PD10 |      | VSS        | VSS        | VSS        | VSS       |           | VSS      | VDD_MIPI |

| F1    | F2   | F3   | F4         | F5         | F6         | F7        | F8        | F9       | F10      |

| PD9   | PD8  |      | VSS        | VSS        | VSS        | VSS       |           | MIPI_CP  | MIPI_CN  |

| G1    | G2   | G3   | G4         | G5         | G6         | <b>G7</b> | G8        | G9       | G10      |

| PD7   | PD6  |      | VSS        | VSS        | VSS        | VSS       |           | MIPI_D1P | MIPI_D1N |

| H1    | H2   | Н3   | H4         | H5         | Н6         | H7        | Н8        | Н9       | H10      |

| VDDIO | VSS  |      |            |            |            |           |           | VSS      | VDD_MIPI |

| J1    | J2   | J3   | J4         | J5         | J6         | J7        | J8        | J9       | J10      |

| PD4   | PD2  | PD0  | VSS        | VSS        | PCLK       | HVALID    | CS        | MIPI_D0P | MIPI_D0N |

| K1    | K2   | К3   | K4         | <b>K</b> 5 | K6         | К7        | K8        | К9       | K10      |

| PD5   | PD3  | PD1  | VDDC       | VDDIO      | REFCLK     | VVALID    | GPIO0     | VDDIO    | VSS      |

Figure 3.2 TC358748XBG 80-Pin Layout (Top View)

## 4. Package

#### 4.1. TC358746AXBG Package

The packages for TC358746AXBG are described in the figures below.

Figure 4.1 TC358746AXBG P-VFBGA72-0404-0.40A3 package

Table 4.1 TC358746AXBG P-VFBGA72-0404-0.40A3 Mechanical Dimension

| Dimension           | Min      | Тур.                      | Max     |

|---------------------|----------|---------------------------|---------|

| Solder ball pitch   | - 0.4 mm |                           | -       |

| Solder ball height  | 0.15 mm  | 0.2 mm                    | 0.25 mm |

| Package dimension - |          | 4.5 x 4.5 mm <sup>2</sup> | -       |

| Package height      | -        | -                         | 1.0 mm  |

#### 4.2. TC358748XBG Package

The packages for TC358748XBG are described in the figures below.

Figure 4.2 TC358748XBG P-VFBGA80-0707-0.65-001 package

Table 4.2 TC358748XBG P-VFBGA80-0707-0.65-001 Mechanical Dimension

| Dimension           | Min              | Тур.                          | Max     |

|---------------------|------------------|-------------------------------|---------|

| Solder ball pitch   | -                | 0.65 mm                       | -       |

| Solder ball height  | 0.20 mm          | 0.25 mm                       | 0.30 mm |

| Package dimension - |                  | $7.0 \times 7.0 \text{ mm}^2$ | -       |

| Package height      | Package height - |                               | 1.0 mm  |

## 5. Electrical Characteristics

## 5.1. Absolute Maximum Ratings

VSS= 0V reference

| Parameter                               | Symbol                | Rating               | Unit |

|-----------------------------------------|-----------------------|----------------------|------|

| Supply voltage<br>(1.8V - Digital IO)   | VDDIO                 | -0.3 to +3.9         | V    |

| Supply voltage<br>(1.2V – Digital Core) | VDDC                  | -0.3 to +1.8         | V    |

| Supply voltage<br>(1.2V – MIPI CSI PHY) | VDD_MIPI              | -0.3 to +1.8         | V    |

| Input voltage<br>(CSI IO)               | $V_{IN\_CSI}$         | -0.3 to VDD_MIPI+0.3 | V    |

| Output voltage (CSI IO)                 | $V_{\text{OUT\_CSI}}$ | -0.3 to VDD_MIPI+0.3 | V    |

| Input voltage<br>(Digital IO)           | $V_{\text{IN\_IO}}$   | -0.3 to VDDIO+0.3    | V    |

| Output voltage<br>(Digital IO)          | V <sub>OUT_IO</sub>   | -0.3 to VDDIO+0.3    | V    |

| Junction temperature                    | Tj                    | 125                  | °C   |

| Storage temperature                     | Tstg                  | -40 to +125          | °C   |

## **5.2. Operating Condition**

VSS= 0V reference

| Parameter                                                        | Symbol   | Min  | Тур. | Max  | Unit      |

|------------------------------------------------------------------|----------|------|------|------|-----------|

| Supply voltage (1.8V – Digital IO)                               | VDDIO    | 1.65 | 1.8  | 1.95 | V         |

| Supply voltage (3.3V – Digital IO)                               | VDDIO    | 3.0  | 3.3  | 3.6  | V         |

| Supply voltage (1.2V – Digital Core)                             | VDDC     | 1.1  | 1.2  | 1.3  | V         |

| Supply voltage (1.2V – MIPI CSI PHY)                             | VDD_MIPI | 1.1  | 1.2  | 1.3  | V         |

| Operating temperature (ambient temperature with voltage applied) | Та       | -30  | +25  | +85  | °C        |

| Supply Noise Voltage                                             | $V_{SN}$ | -    | -    | 100  | $mV_{pp}$ |

#### 5.3. DC Electrical Specification

| Parameter                                                                                        | Symbol                    | Min       | Тур. | Max       | Unit |

|--------------------------------------------------------------------------------------------------|---------------------------|-----------|------|-----------|------|

| Input voltage, High level input Note1                                                            | V <sub>IH</sub>           | 0.7 VDDIO | -    | VDDIO     | ٧    |

| Input voltage, Low level input Note1                                                             | V <sub>IL</sub>           | 0         | -    | 0.3 VDDIO | ٧    |

| Input voltage High level<br>CMOS Schmitt Trigger<br>Note1, Note2                                 | V <sub>IHS</sub>          | 0.7 VDDIO | -    | VDDIO     | V    |

| Input voltage Low level CMOS Schmitt Trigger                                                     | V <sub>ILS</sub>          | 0         | -    | 0.3 VDDIO | V    |

| Output voltage High level                                                                        | V <sub>OH</sub>           | 0.8 VDDIO | -    | VDDIO     | V    |

| (Condition: IOH = -0.4mA) Output voltage Low level                                               | V <sub>OL</sub>           | 0         | -    | 0.2 VDDIO | V    |

| (Condition: IOL = 2mA)                                                                           |                           |           |      |           |      |

| Input leak current, High level (Normal IO or Pull-up IO) (Condition: VIN = +VDDIO, VDDIO = 3.6V) | I <sub>ILH1</sub> (Note4) | -10       | -    | 10        | μΑ   |

| Input leak current, High level (Pull-down IO) (Condition: VIN = +VDDIO, VDDIO = 3.6V)            | I <sub>ILH2</sub> (Note4) | -         | -    | 100       | μΑ   |

| Input leak current, Low level (Normal IO or Pull-down IO) (Condition: VIN = 0V, VDDIO = 3.6V)    | I <sub>ILL1</sub> (Note5) | -10       | -    | 10        | μA   |

| Input leak current, Low level (Pull-up IO) (Condition: VIN = 0V, VDDIO = 3.6V)                   | I <sub>ILL2</sub> (Note5) | -         | -    | 200       | μΑ   |

Note1: Each power source is operating within recommended operation condition.

Note2: Current output value is specified to each IO buffer individually. Output voltage changes with output

current value.

Note4: Normal pin or Pull-up IO pin applied VDDIO supply voltage to Vin (input voltage)

Note5: Normal pin or Pull-down IO pin applied VSSIO (0V) to Vin (input voltage)

## 6. Revision History

Table 6.1 Revision History

| Revision | Date       | Description                                                                                                                                                                                                            |  |  |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0.91     | 2014-05-29 | Newly released                                                                                                                                                                                                         |  |  |

| 1.11     | 2015-10-07 | <ol> <li>Remove Fail safe I2C pad operation</li> <li>Change HSync/VSync to HVALID/VVALID</li> <li>Update table 3-1 for I/O init direction and its output value</li> </ol>                                              |  |  |

| 1.12     | 2016-04-01 | <ol> <li>Packages' weight is cut off after the decimal point.</li> <li>TC358746A's package code:         P-VFBGA72-0505-0.40-001 → P-VFBGA72-0404-0.40A3     </li> <li>Replaced TC358746A's package drawing</li> </ol> |  |  |

| 1.4      | 2017-02-07 | Corrected condition in 2.1.Typical Power Consumption.                                                                                                                                                                  |  |  |

| 1.5      | 2017-02-23 | Corrected Typo in Table 4.1.                                                                                                                                                                                           |  |  |

| 1.6a     | 2017-10-11 | Changed header, footer and the last page. Changed corporate name.                                                                                                                                                      |  |  |

| 1.85     | 2020-12-14 | Modified Table 3.1 VVALID initial value                                                                                                                                                                                |  |  |

#### RESTRICTIONS ON PRODUCT USE

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE

EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH

MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT

("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes,

without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life

supporting medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling

equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, and devices

related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT.

For details, please contact your TOSHIBA sales representative or contact us via our website.

- · Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE

FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY

WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR

LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND

LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO

SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of

Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled

substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES

OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION

https://toshiba.semicon-storage.com/

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Specialised category:

Click to view products by Toshiba manufacturer:

Other Similar products are found below:

CY7C910-51LMB MC33689DPEWR2 MC33975ATEKR2 MEC1632-AUE NVT4555UKZ RKSAS4 HMC677G32 LPC47N207-JV FTP-637DSL633R SM712GX04LF04-BA MC33689DPEW PCA9704PWJ NCN5192MNRG MCW1001A-I/SS HOA6241-001

SC74HC4066ADTR2G AS3935-BQFT NCN5120MNTWG NCN5150DR2G NCN8025MTTBG C100N50Z4A DG407AK/883B SRT2-ATT01 TDA8035HN/C1/S1J LTC1694CS5#TRMPBF TLE9221SXXUMA2 DS90UB947TRGCRQ1 SP510ECF-L NCS2300MUTAG

HMC677LP5E HMC677LP5ETR LTC1756EGN#PBF LTC1955EUH#PBF LTC6820HMS#3ZZTRPBF MXL1543BCAI MAX3170CAI+

XL1192D ST8024CTR TLE9221SX KTU1109EFAA-TR CH368L CH7307C-DEF LTC1694CS5#TRPBF LTC1694IS5#TRM LTS 25-NP

73S8024RN-20IMF 73S8024RN-IL/F 78P2352-IGT/F DS2406+ DS2413P+