## **TOSHIBA**

# 32 Bit RISC Microcontroller TX03 Series

TMPM332FWUG

**TOBHIBA CORPORATION**

ARM, ARM Powered, AMBA, ADK, ARM9TDMI, TDMI, PrimeCell, RealView, Thumb, Cortex, Coresight, ARM9, ARM926EJ-S, Embedded Trace Macrocell, ETM, AHB, APB, and KEIL are registered trademarks or trademarks of ARM Limited in the EU and other countries.

## <u>Introduction: Notes on the description of SFR (Special Function Register) under this specification</u>

An SFR (Special Function Register) is a control register for periperal circuits (IP).

The SFR addressses of IPs are described in the chapter on memory map, and the details of SFR are given in the chapter of each IP.

Definition of SFR used in this specification is in accordance with the following rules.

- a. SFR table of each IP as an example

- · SFR tables in each chapter of IP provides register names, addresses and brief descriptions.

- All registers have a 32-bit unique address and the addresses of the registers are defined as follows, with some exceptions: "Base address + (Unique) address"

Base Address = 0x0000\_0000

| Register name    | Address(Base+) |        |

|------------------|----------------|--------|

| Control register | SAMCR          | 0x0004 |

|                  |                | 0x000C |

Note: SAMCR register address is 32 bits wide from the address 0x0000\_0004 (Base Address(0x00000000) + unique address (0x0004)).

Note: The register shown above is an example for explanation purpose and not for demonstration purpose. This register does not exist in this microcontroller.

- b. SFR(register)

- Each register basically consists of a 32-bit register (some exceptions).

- The description of each register provides bits, bit symbols, types, initial values after reset and functions.

#### 1.2.2 SAMCR(Control register)

|             | 31   | 30 | 29 | 28 | 27    | 26 | 25 | 24  |

|-------------|------|----|----|----|-------|----|----|-----|

| bit symbol  | -    | -  | -  | -  | -     | -  | -  | -   |

| After reset | 0    | 0  | 0  | 0  | 0     | 0  | 0  | 0   |

|             | 23   | 22 | 21 | 20 | 19    | 18 | 17 | 16  |

| bit symbol  | -    | -  | -  | -  | -     | -  | -  | -   |

| After reset | 0    | 0  | 0  | 0  | 0     | 0  | 0  | 0   |

|             | 15   | 14 | 13 | 12 | 11    | 10 | 9  | 8   |

| bit symbol  | -    | -  | -  | -  | -     | -  | МС | DDE |

| After reset | 0    | 0  | 0  | 0  | 0     | 0  | 0  | 0   |

|             | 7    | 6  | 5  | 4  | 3     | 2  | 1  | 0   |

| bit symbol  | MODE |    |    |    | TDATA |    |    |     |

| After reset | 0    | 0  | 0  | 1  | 0     | 0  | 0  | 0   |

| Bit   | Bit Symbol | Туре | Function                                                                                                                                                   |

|-------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-10 | _          | R    | "0" can be read.                                                                                                                                           |

| 9-7   | MODE[2:0]  | R/W  | Operation mode settings  000 : Sample mode 0  001 : Sample mode 1  010 : Sample mode 2  011 : Sample mode 3  The settings other than those above: Reserved |

| 6-0   | TDATA[6:0] | W    | Transmitted data                                                                                                                                           |

Note: The Type is divided into three as shown below.

R / W READ WRITE

R READ

W WRITE

## c. Data descriptopn

Meanings of symbols used in the SFR description are as shown below.

- x:channel numbers/ports

- · n,m:bit numbers

### d. Register descriptoption

Registers are described as shown below.

• Register name <Bit Symbol>

Exmaple: SAMCR<MODE>="000" or SAMCR<MODE[2:0]>="000"

<MODE[2:0]> indicates bit 2 to bit 0 in bit symbol mode (3bit width).

· Register name [Bit]

Example: SAMCR[9:7]="000"

It indicates bit 9 to bit 7 of the register SAMCR (32 bit width).

| TMPM332FWUG |

|-------------|

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

## Revision History

| Date      | Revision | Comment          |  |

|-----------|----------|------------------|--|

| 2010/6/11 | 1        | First Release    |  |

| 2010/10/6 | 2        | Contents Revised |  |

## **Table of Contents**

Introduction: Notes on the description of SFR (Special Function Register) under this specification

| TM          | IPM332FWUG                                                                         |    |

|-------------|------------------------------------------------------------------------------------|----|

| 1           | .1 Features                                                                        | 1  |

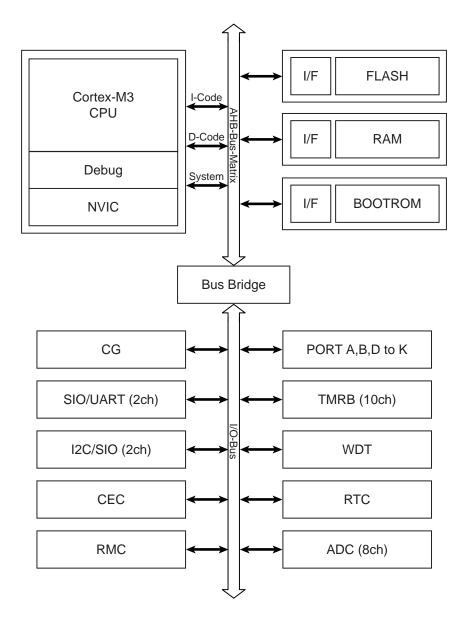

| 1           | .2 Block Diagram                                                                   | 3  |

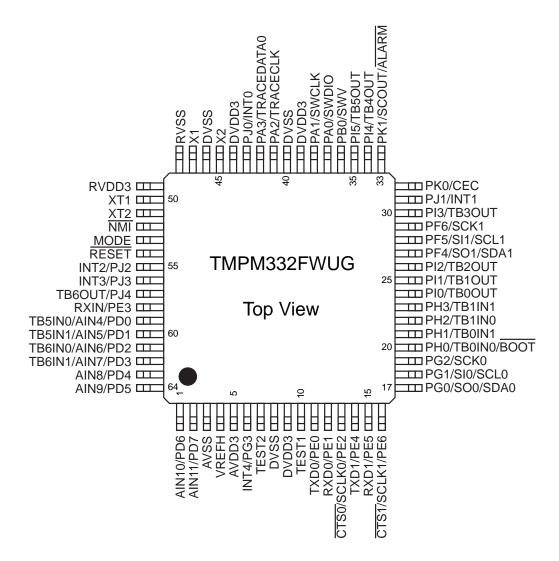

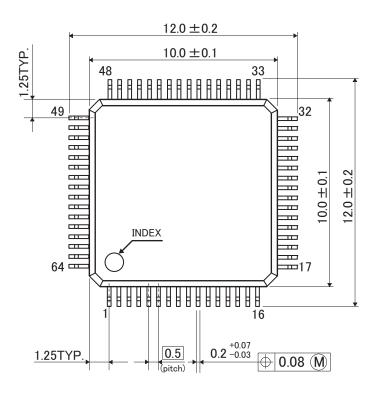

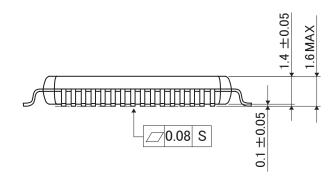

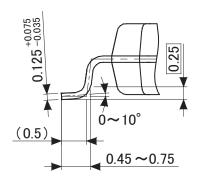

| 1           | .3 Pin Layout (Top view)                                                           | 4  |

| 1           | .4 Pin names and Functions                                                         | 5  |

|             | 1.4.1 Sorted by Pin                                                                |    |

| 1           | 1.5 Pin Numbers and Power Supply Pins                                              |    |

| 2. P        | Processor Core                                                                     |    |

| 2           | 2.1 Information on the processor core                                              | 15 |

| 2           | 2.2 Configurable Options                                                           |    |

| 2           | 2.3 Exceptions/ Interruptions                                                      | 15 |

|             | 2.3.1 Number of Interrupt Inputs                                                   |    |

|             | 2.3.2 Number of Priority Level Interrupt Bits                                      |    |

|             | 2.3.4 SYSRESETREQ.                                                                 |    |

|             | 2.3.5 LOCKUP                                                                       |    |

| 2           | 2.3.6 Auxiliary Fault Status register                                              |    |

|             | 2.5 Power Management.                                                              |    |

|             | 2.6 Exclusive access                                                               |    |

|             | ACCESSION DATES                                                                    |    |

| 3. <u>C</u> | Debug Interface                                                                    |    |

| 3           | 3.1 Specification Overview                                                         | 19 |

| 3           | 3.2 SW-DP                                                                          | 19 |

| 3           | 3.3 ETM                                                                            | 19 |

| 3           | 3.4 Pin Functions                                                                  | 20 |

| 3           | 3.5 Peripheral Functions in Halt Mode                                              | 20 |

| 3           | 3.6 Reset Vector Break                                                             | 21 |

| 3           | 3.7 Connection with a Debug Tool                                                   | 21 |

|             | 3.7.1 About connection with debug tool                                             |    |

|             | 3.7.2 Important points of using debug interface pins used as general-purpose ports | 21 |

|             | Jamary Man                                                                         |    |

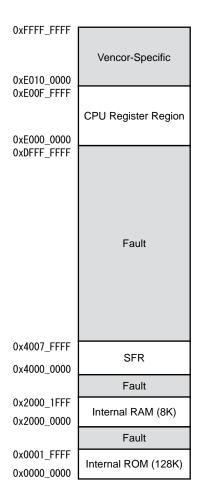

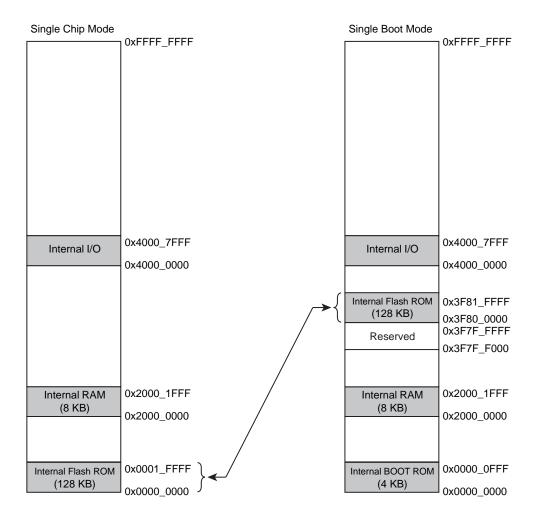

|    | <b>4.1 Memory map</b>                                                                |    |

|----|--------------------------------------------------------------------------------------|----|

|    | 4.2 SFR area detail.                                                                 |    |

|    |                                                                                      |    |

| 5. | Reset                                                                                |    |

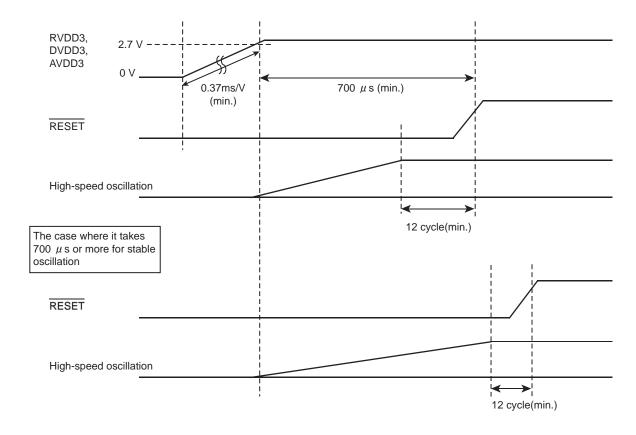

|    | 5.1 Cold reset                                                                       | 27 |

|    | 5.2 Warm reset                                                                       | 28 |

|    | 5.2.1 Reset period                                                                   |    |

|    | 5.2.2 After reset                                                                    | 28 |

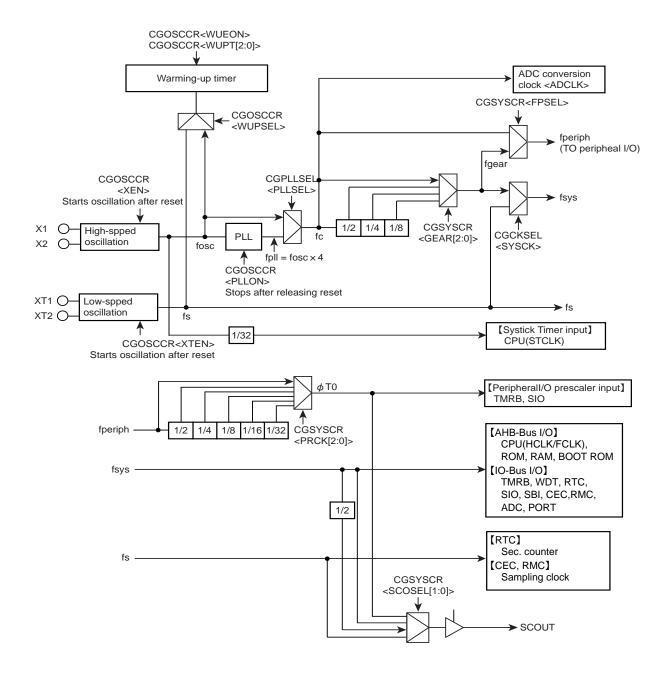

| 6. | Clock/Mode control                                                                   |    |

|    | 6.1 Features                                                                         | 20 |

|    |                                                                                      |    |

|    | 6.2 Registers                                                                        |    |

|    | 6.2.1 Register List                                                                  |    |

|    | 6.2.3 CGOSCCR (Oscillation control register)                                         |    |

|    | 6.2.4 CGSTBYCR (Standby control register)                                            |    |

|    | 6.2.5 CGPLLSEL (PLL Selection Register)                                              |    |

|    | 6.2.6 CGCKSEL (System clock selection register)                                      |    |

|    | 6.3 Clock control.                                                                   |    |

|    | 6.3.1 Clock System Block Diagram.                                                    |    |

|    | 6.3.2 Initial Values after Reset                                                     |    |

|    | 6.3.4 Clock Multiplication Circuit (PLL)                                             |    |

|    | 6.3.5 Warm-up function                                                               |    |

|    | 6.3.6 System Clock                                                                   | 40 |

|    | 6.3.6.1 High speed clock 6.3.6.2 Low speed clock                                     |    |

|    | 6.3.7 Prescaler Clock Control                                                        | 40 |

|    | 6.3.8 System Clock Pin Output Function                                               |    |

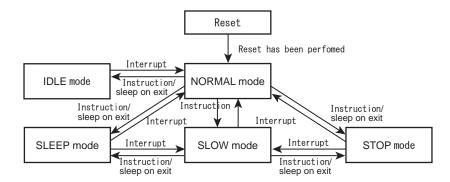

|    | 6.4 Modes and Mode Transitions                                                       | 42 |

|    | 6.4.1 Mode Transitions                                                               | 42 |

|    | 6.5 Operation mode                                                                   | 43 |

|    | 6.5.1 NORMAL mode                                                                    |    |

|    | 6.5.2 SLOW mode                                                                      |    |

|    | 6.6 Low Power Consumption Modes                                                      |    |

|    | 6.6.1 IDLE mode                                                                      |    |

|    | 6.6.2 SLEEP mode                                                                     |    |

|    | 6.6.4 Low power Consumption Mode Setting                                             |    |

|    | 6.6.5 Operational Status in Each Mode                                                |    |

|    | 6.6.6 Releasing the Low Power Consumption Mode                                       |    |

|    | 6.6.7 Warm-up                                                                        |    |

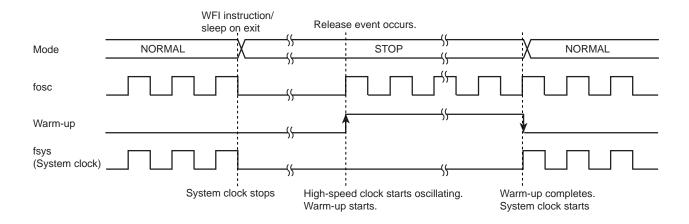

|    | 6.6.8 Clock Operations in Mode Transition                                            | 49 |

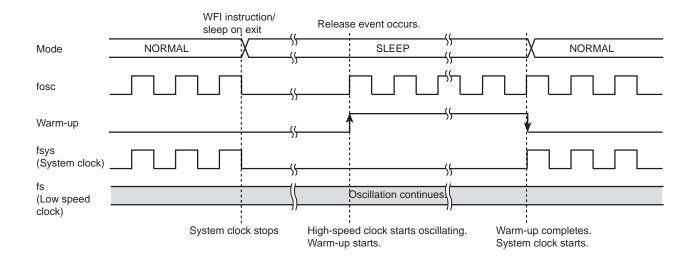

|    | 6.6.8.2 Transition of operation modes: NORMAL → SLEEP → NORMAL                       |    |

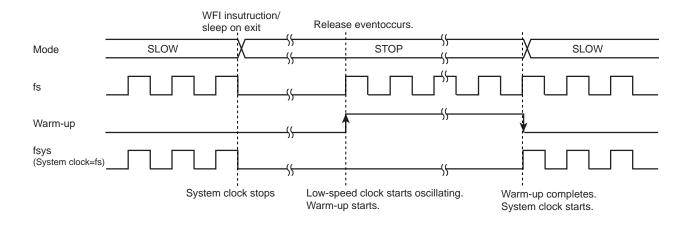

|    | 6.6.8.3 Transition of operation modes: $SLOW \rightarrow STOP \rightarrow SLOW$      |    |

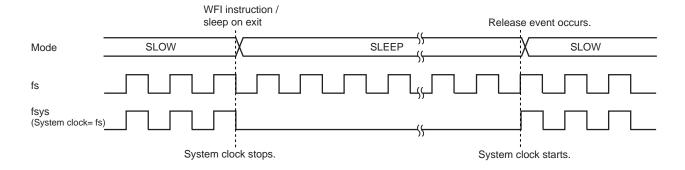

|    | 6.6.8.4 Transition of operation modes: SLOW $\rightarrow$ SLEEP $\rightarrow$ SLOW   |    |

| 7. | Exceptions                                                                           |    |

|    | 7.1 Overview                                                                         |    |

|    | 7.1.1 Exception Types                                                                |    |

|    | 7.1.2 Handling Flowchart.                                                            |    |

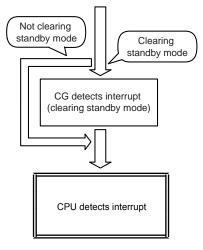

|    | 7.1.2.1 Exception Request and Detection                                              |    |

|    | 7.1.2.2 Exception Handling and Branch to the Interrupt Service Routine (Pre-emption) |    |

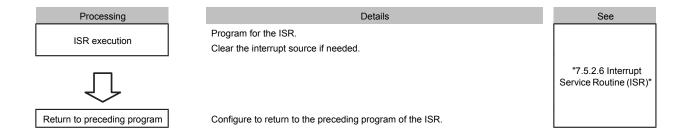

|     | 7.1.2.3 Executing an ISR 7.1.2.4 Exception exit                                                             |     |

|-----|-------------------------------------------------------------------------------------------------------------|-----|

| 7.2 | Reset Exceptions.                                                                                           | 57  |

| 7.3 | Non-Maskable Interrupts (NMI)                                                                               |     |

|     | 1 ( )                                                                                                       |     |

| 7.4 | SysTick                                                                                                     |     |

| 7.5 | Interrupts                                                                                                  |     |

| 7.: | 5.1 Interrupt Sources                                                                                       | 59  |

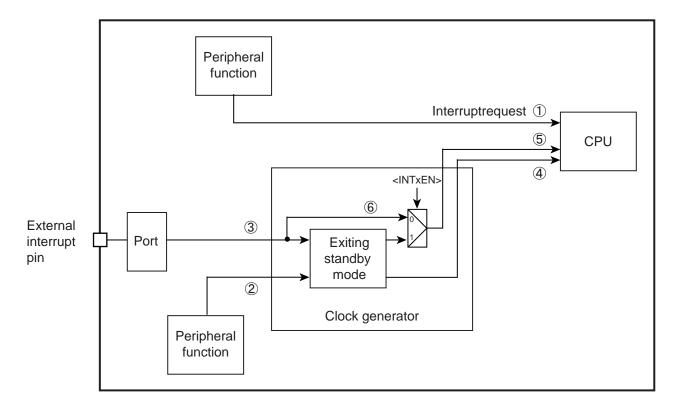

|     | 7.5.1.1 Interrupt Route 7.5.1.2 Generation                                                                  |     |

|     | 7.5.1.3 Transmission                                                                                        |     |

|     | 7.5.1.4 Precautions when using external interrupt pins                                                      |     |

|     | 7.5.1.5 List of Interrupt Sources 7.5.1.6 Active level                                                      |     |

| 7   | 5.2 Interrupt Handling                                                                                      | 63  |

| ,   | 7.5.2.1 Flowchart                                                                                           |     |

|     | 7.5.2.2 Preparation                                                                                         |     |

|     | 7.5.2.3 Detection by Clock Generator 7.5.2.4 Detection by CPU                                               |     |

|     | 7.5.2.5 CPU processing                                                                                      |     |

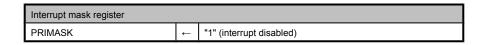

|     | 7.5.2.6 Interrupt Service Routine (ISR)                                                                     |     |

| 7.6 | Exception/Interrupt-Related Registers                                                                       | 68  |

| 7.  | 6.1 Register List                                                                                           | 68  |

| 7.  | 6.2 NVIC Registers                                                                                          | 69  |

|     | 7.6.2.1 SysTick Control and Status Register                                                                 |     |

|     | 7.6.2.2 SysTick Reload Value Register 7.6.2.3 SysTick Current Value Register                                |     |

|     | 7.6.2.4 SysTick Calibration Value Register                                                                  |     |

|     | 7.6.2.5 Interrupt Set-Enable Register 1                                                                     |     |

|     | 7.6.2.6 Interrupt Set-Enable Register 2 7.6.2.7 Interrupt Clear-Enable Register 1                           |     |

|     | 7.6.2.8 Interrupt Clear-Enable Register 2                                                                   |     |

|     | 7.6.2.9 Interrupt Set-Pending Register 1                                                                    |     |

|     | 7.6.2.10 Interrupt Set-Pending Register 2 7.6.2.11 Interrupt Clear-Pending Register 1                       |     |

|     | 7.6.2.11 Interrupt Clear-Pending Register 1 7.6.2.12 Interrupt Clear-Pending Register 2                     |     |

|     | 7.6.2.13 Interrupt Priority Register                                                                        |     |

|     | 7.6.2.14 Vector Table Offset Register                                                                       |     |

|     | 7.6.2.15 Application Interrupt and Reset Control Register 7.6.2.16 System Handler Priority Register         |     |

|     | 7.6.2.17 System Handler Photity Register 7.6.2.17 System Handler Control and State Register                 |     |

| 7.  | 6.3 Clock generator registers                                                                               | 88  |

|     | 7.6.3.1 CGIMCGA(CG Interrupt Mode Control Register A)                                                       |     |

|     | 7.6.3.2 CGIMCGB(CG Interrupt Mode Control Register B)                                                       |     |

|     | 7.6.3.3 CGIMCGC(CG Interrupt Mode Control Register C) 7.6.3.4 CGIMCGD(CG Interrupt Mode Control Register D) |     |

|     | 7.6.3.5 CGICRCG(CG Interrupt Request Clear Register)                                                        |     |

|     | 7.6.3.6 CGNMIFLG(NMI Flag Register)                                                                         |     |

|     | 7.6.3.7 CGRSTFLG (Reset Flag Register)                                                                      |     |

|     |                                                                                                             |     |

|     |                                                                                                             |     |

| Inp | out/Output Ports                                                                                            |     |

| P   |                                                                                                             |     |

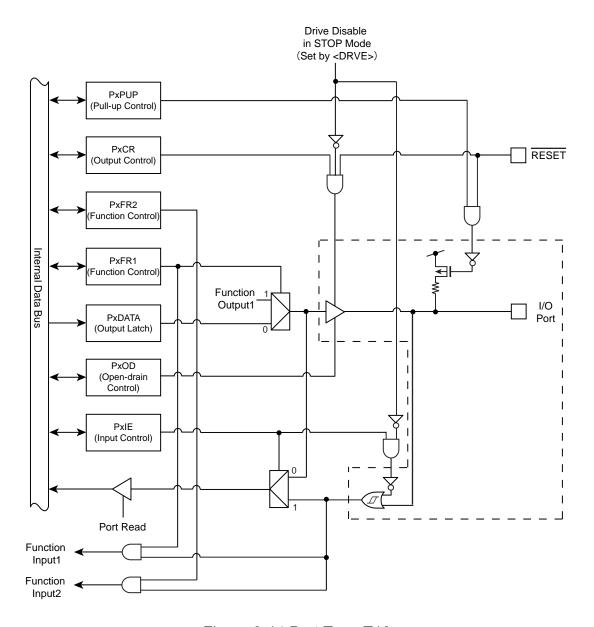

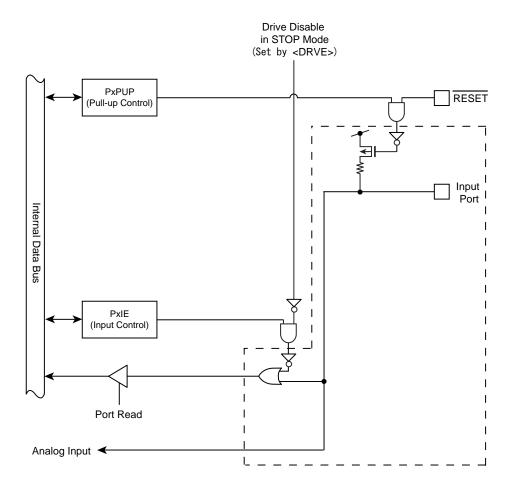

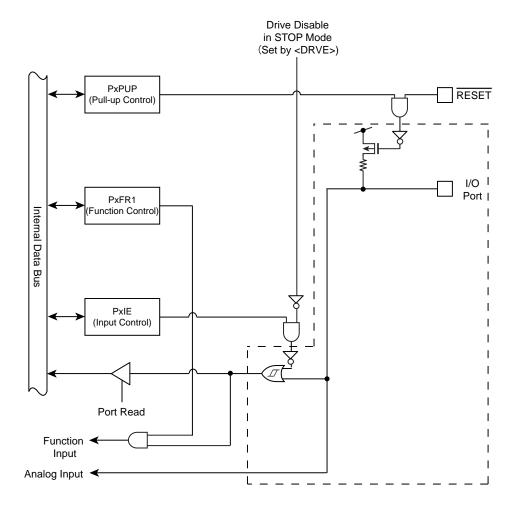

| 8.1 | Port Functions                                                                                              | 97  |

|     | 1.1 Function Lists                                                                                          |     |

|     | 1.2 Port Registers Outline                                                                                  |     |

|     | 1.3 Port States in STOP Mode                                                                                |     |

| 8.  | 1.4 Precautions for Mode Transition between STOP and SLEEP                                                  | 100 |

| 8.2 | Port functions.                                                                                             | 101 |

| 8   | 2.1 Port A (PA0 to PA3)                                                                                     |     |

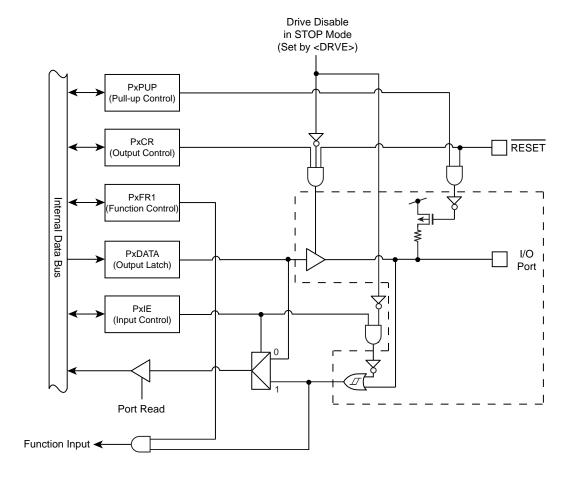

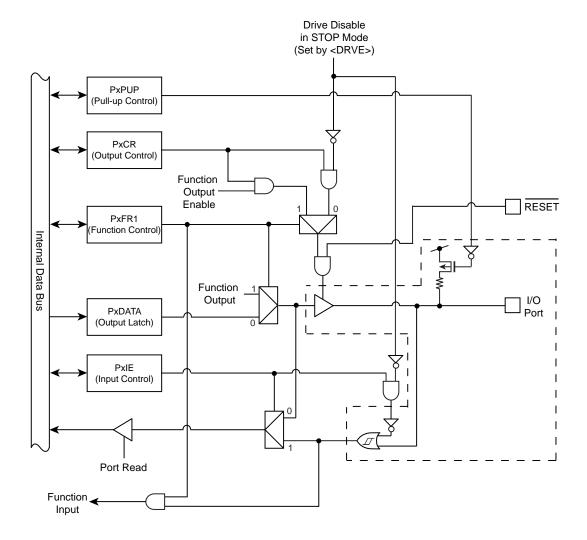

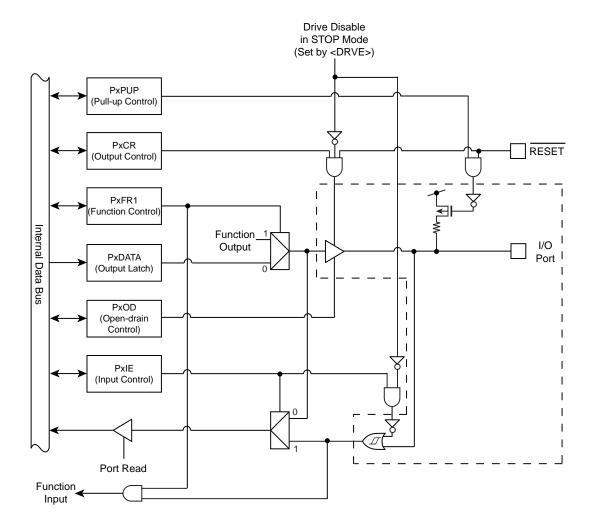

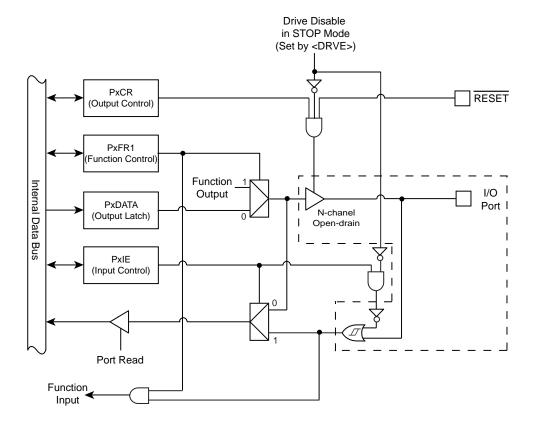

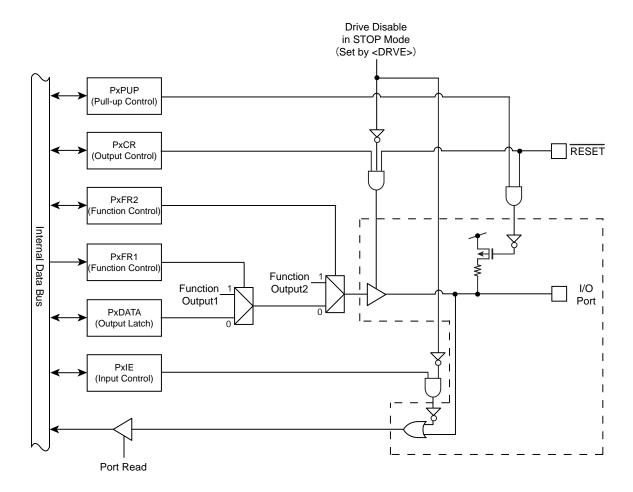

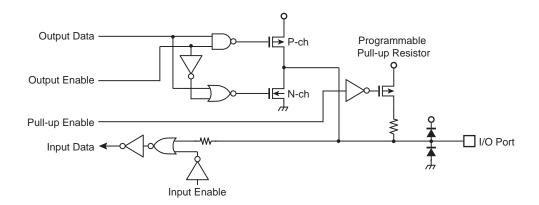

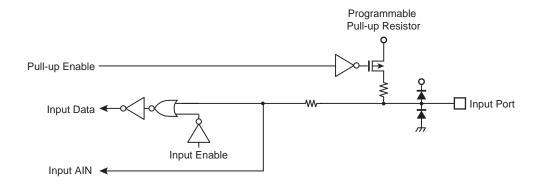

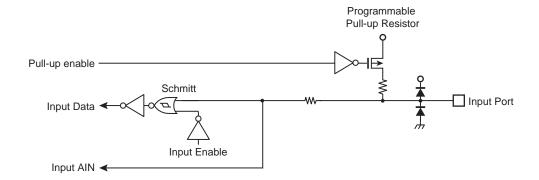

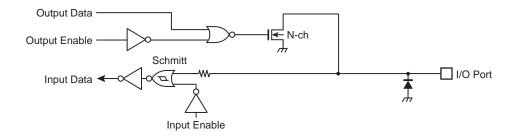

|     | 8.2.1.1 Port A Circuit Type                                                                                 |     |

|     | 8.2.1.2 Port A register                                                                                     |     |

|     | 8.2.1.3 PADATA (Port A data register) 8.2.1.4 PACR (Port A output control register)                         |     |

|     | 8.2.1.5 PAFR1 (Port A function register 1)                                                                  |     |

|     | 8.2.1.6 PAPUP (Port A pull-up control register)                                                             |     |

|     | 8.2.1.7 PAPDN (Port A pull-down control register)                                                           |     |

| 0   | 8.2.1.8 PAIE (Port A input control register) 2.2 Port B (PB0)                                               | 106 |

| ٥   | 8.2.2.1 Port B Circuit Type                                                                                 | 100 |

|     | 8.2.2.2 Port B Register                                                                                     |     |

|                      | rt Turas                                                                          | 143  |

|----------------------|-----------------------------------------------------------------------------------|------|

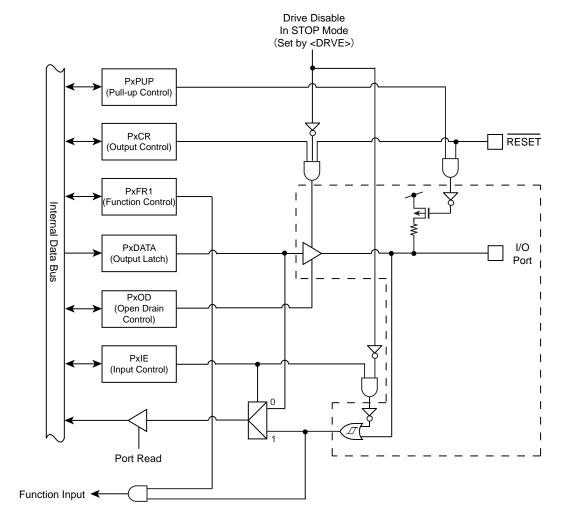

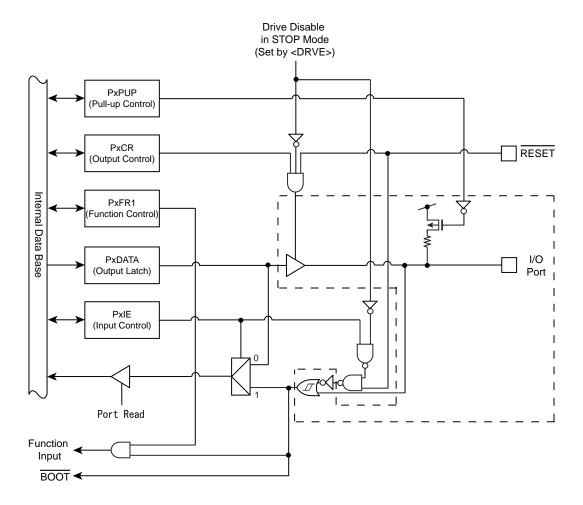

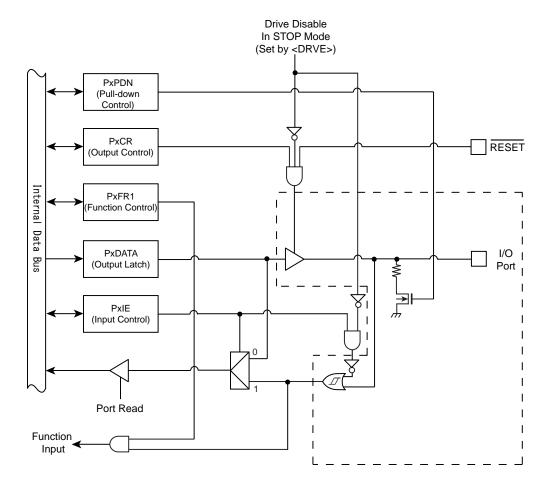

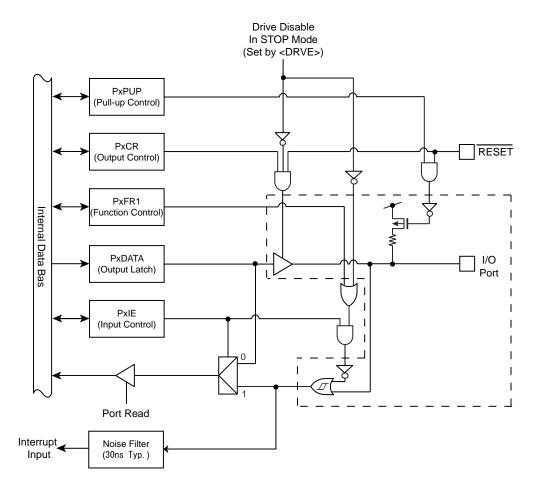

|                      | k Diagrams of Ports                                                               | 145  |

| 8.2.10.8             | PKIE (Port K input control register)                                              |      |

| 8.2.10.7             | PKPUP (Port K pull-up control register)                                           |      |

| 8.2.10.6             | PKFR2(Port K function register 2)                                                 |      |

| 8.2.10.5             | PKFR1(Port K function register 1)                                                 |      |

| 8.2.10.4             | PKCR (Port K output control register)                                             |      |

| 8.2.10.2             | PKDATA (Port K data register)                                                     |      |

| 8.2.10.1<br>8.2.10.2 | Port K Circuit Type Port K Register                                               |      |

|                      | ort K (PK0 to PK1)                                                                | 140  |

| 8.2.9.7<br>8.2.10 B  |                                                                                   | 1.40 |

| 8.2.9.6              | PJPUP (Port J pull-up control register) PJIE (Port J input control register)      |      |

| 8.2.9.5              | PJFR1(Port J function register 1)                                                 |      |

| 8.2.9.4              | PJCR (Port J output control register)                                             |      |

| 8.2.9.3              | PJDATA (Port J data register)                                                     |      |

| 8.2.9.2              | Port J Register                                                                   |      |

| 8.2.9.1              | Port J Circuit Type                                                               |      |

| 8.2.9 Po             | rt J (PJ0 to PJ4)                                                                 | 136  |

| 8.2.8.7              | PIIE (Port I input control register)                                              |      |

| 8.2.8.6              | PIPUP (Port I pull-up control register)                                           |      |

| 8.2.8.5              | PIFR1(Port I function register 1)                                                 |      |

| 8.2.8.4              | PICR (Port I output control register)                                             |      |

| 8.2.8.3              | PIDATA (Port I data register)                                                     |      |

| 8.2.8.2              | Port I Register                                                                   |      |

| 8.2.8.1              | Port I Circuit Type                                                               |      |

|                      | rt I (PI0 to PI5)                                                                 | 132  |

| 8.2.7.7              | PHIE (Port H input control register)                                              |      |

| 8.2.7.6              | PHPUP (Port H pull-up control register)                                           |      |

| 8.2.7.4<br>8.2.7.5   | PHFR1(Port H function register 1)                                                 |      |

| 8.2.7.3<br>8.2.7.4   | PHDATA (Port H data register) PHCR (Port H output control register)               |      |

| 8.2.7.2              | Port H Register                                                                   |      |

| 8.2.7.1              | Port H Circuit Type                                                               |      |

|                      | rt H (PH0 to PH3)                                                                 | 128  |

| 8.2.6.8              | PGIE (Port G input control register)                                              |      |

| 8.2.6.7              | PGPUP (Port G pull-up control register)                                           |      |

| 8.2.6.6              | PGOD (Port G open drain control register)                                         |      |

| 8.2.6.5              | PGFR1(Port G function register 1)                                                 |      |

| 8.2.6.4              | PGCR (Port G output control register)                                             |      |

| 8.2.6.3              | PGDATA (Port G data register)                                                     |      |

| 8.2.6.1<br>8.2.6.2   | Port G Circuit Type Port G Register                                               |      |

| 8.2.6 Po<br>8.2.6.1  | Prof G Circuit Type                                                               | 123  |

|                      | rt G (PG0 to PG3)                                                                 | 123  |

| 8.2.5.7<br>8.2.5.8   | PFIC (Port F input control register) PFIE (Port F input control register)         |      |

| 8.2.5.6<br>8.2.5.7   | PFOD (Port F open drain control register) PFPUP (Port F pull-up control register) |      |

|                      | PFFR1(Port F function register 1) PFOD (Port F open drain control register)       |      |

| 8.2.5.4<br>8.2.5.5   | PFCR (Port F output control register)  PEEP I (Port F function register 1)        |      |

| 8.2.5.3              | PFDATA (Port F data register)                                                     |      |

| 8.2.5.2              | Port F Register                                                                   |      |

| 8.2.5.1              | Port F Circuit Type                                                               |      |

|                      | rt F (PF4 to PF6)                                                                 | 118  |

| 8.2.4.9              | PEIE (Port E input control register)                                              |      |

| 8.2.4.8              | PEPUP (Port E pull-up control register)                                           |      |

| 8.2.4.7              | PEOD (Port E open drain control register)                                         |      |

| 8.2.4.6              | PEFR2(Port E function register 2)                                                 |      |

| 8.2.4.5              | PEFR1(Port E function register 1)                                                 |      |

| 8.2.4.4              | PECR (Port E output control register)                                             |      |

| 8.2.4.3              | PEDATA (Port E data register)                                                     |      |

| 8.2.4.1<br>8.2.4.2   | Port E Circuit Type Port E Register                                               |      |

| 8.2.4 Po<br>8.2.4.1  | rt E (PE0 to PE6)                                                                 | 113  |

| 8.2.3.6<br>8.2.4 Pa  | PDIE (Port D input control register)                                              | 112  |

| 8.2.3.5              | PDPUP (Port D pull-up control register)                                           |      |

| 8.2.3.4              | PDFR1 (Port D function register 1)                                                |      |

| 8.2.3.3              | PDDATA (Port D data register)                                                     |      |

| 8.2.3.2              | Port D Register                                                                   |      |

| 8.2.3.1              | Port D Circuit Type                                                               |      |

|                      | rt D (PD0 to PD7)                                                                 | 110  |

| 8.2.2.7              | PBIE (Port B input control register)                                              |      |

| 8.2.2.6              | PBPUP (Port B pull-up control register)                                           |      |

| 8.2.2.4<br>8.2.2.5   | PBCR (Port B output control register) PBFR1 (Port B function register 1)          |      |

| 8.2.2.3              | PBDATA (Port B data register)                                                     |      |

| 0 2 2 2              | DDD (T) (D (D) (D) (C)                                                            |      |

|                                                                                                                                                                     | Type T3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 8.3.3                                                                                                                                                               | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.4                                                                                                                                                               | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.5                                                                                                                                                               | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.6                                                                                                                                                               | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.7                                                                                                                                                               | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.8                                                                                                                                                               | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.9                                                                                                                                                               | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.10<br>8.3.11                                                                                                                                                    | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.12                                                                                                                                                              | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.13                                                                                                                                                              | 7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

| 8.3.14                                                                                                                                                              | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.15                                                                                                                                                              | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.10                                                                                                                                                              | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 8.3.17                                                                                                                                                              | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|                                                                                                                                                                     | Appendix (Port setting List)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

|                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

| 8.4.1                                                                                                                                                               | Port A Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| 8.4.2                                                                                                                                                               | <i>G</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| 8.4.3<br>8.4.4                                                                                                                                                      | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| 8.4.4                                                                                                                                                               | Port F Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| 8.4.6                                                                                                                                                               | Port G Setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

| 8.4.7                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

| 8.4.8                                                                                                                                                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| 8.4.9                                                                                                                                                               | $\varepsilon$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| 8.4.10                                                                                                                                                              | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

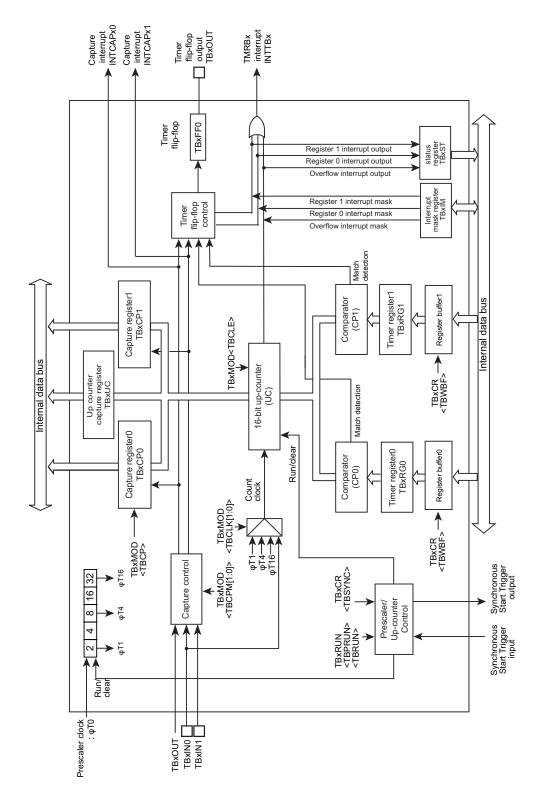

| 16-bit                                                                                                                                                              | t Timer/Event Counters(TMRB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

|                                                                                                                                                                     | (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

|                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 169               |

| 9.1                                                                                                                                                                 | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| 9.1 (<br>9.2 l                                                                                                                                                      | OutlineDifferences in the Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 170               |

| 9.1 0<br>9.2 1<br>9.3 0                                                                                                                                             | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 170<br>171        |

| 9.1 0<br>9.2 1<br>9.3 0<br>9.4 1                                                                                                                                    | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 170<br>171<br>172 |

| 9.1 (9.2 )<br>9.2 )<br>9.3 (9.4 )<br>9.4.1                                                                                                                          | Outline.  Differences in the Specifications.  Configuration.  Registers.  Register list according to channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| 9.1 (9.2 )<br>9.3 (9.4 )<br>9.4.1 (9.4.2                                                                                                                            | Outline. Differences in the Specifications. Configuration. Registers. Register list according to channel. TBxEN (Enable register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 9.1 (9.2 )<br>9.3 (9.4 )<br>9.4.1 (9.4.2 )<br>9.4.3                                                                                                                 | Outline. Differences in the Specifications. Configuration. Registers. Register list according to channel. TBxEN (Enable register). TBxRUN(RUN register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| 9.1 (9.2 ) 9.3 (9.4 ) 9.4.1 9.4.2 9.4.3 9.4.4                                                                                                                       | Outline. Differences in the Specifications. Configuration. Registers. Register list according to channel. TBxEN (Enable register). TBxRUN(RUN register). TBxCR(Control register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| 9.1 (9.2 ) 9.3 (9.4 ) 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5                                                                                                                 | Outline.  Differences in the Specifications.  Configuration.  Registers.  Register list according to channel.  TBxEN (Enable register).  TBxRUN(RUN register)  TBxCR(Control register).  TBxMOD(Mode register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

| 9.1 (9.2 l) 9.3 (9.4 l) 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6                                                                                                               | Outline.  Differences in the Specifications.  Configuration.  Registers.  Register list according to channel.  TBxEN (Enable register).  TBxRUN(RUN register)  TBxCR(Control register).  TBxMOD(Mode register).  TBxFFCR(Flip-flop control register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| 9.1 (9.2 l) 9.3 (9.4 l) 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7                                                                                                         | Outline.  Differences in the Specifications  Configuration.  Registers.  Register list according to channel.  TBxEN (Enable register).  TBxRUN(RUN register).  TBxCR(Control register).  TBxMOD(Mode register).  TBxFFCR(Flip-flop control register).  TBxST(Status register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| 9.1 (9.2 l) 9.3 (9.4 l) 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8                                                                                                   | Outline.  Differences in the Specifications  Configuration.  Registers  Register list according to channel.  TBxEN (Enable register).  TBxRUN(RUN register).  TBxCR(Control register).  TBxMOD(Mode register).  TBxFFCR(Flip-flop control register).  TBxST(Status register).  TBxIM(Interrupt mask register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| 9.1 (9.2 l) 9.3 (9.4 l) 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9                                                                                             | Outline.  Differences in the Specifications  Configuration.  Registers.  Register list according to channel.  TBxEN (Enable register).  TBxRUN(RUN register).  TBxCR(Control register).  TBxMOD(Mode register).  TBxFFCR(Flip-flop control register).  TBxST(Status register).  TBxIM(Interrupt mask register).  TBxUC(Up counter capture register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| 9.1 (9.2 l) 9.3 (9.4 l) 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10                                                                                | Outline.  Differences in the Specifications  Configuration.  Registers  Register list according to channel.  TBxEN (Enable register).  TBxRUN(RUN register).  TBxCR(Control register).  TBxMOD(Mode register).  TBxFFCR(Flip-flop control register).  TBxST(Status register).  TBxIM(Interrupt mask register).  TBxUC(Up counter capture register).  0 TBxRG0(Timer register 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 9.1 (9.2 l) 9.3 (9.4 l) 9.4.1 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11                                                                                           | Outline.  Differences in the Specifications  Configuration.  Registers.  Register list according to channel.  TBxEN (Enable register).  TBxRUN(RUN register).  TBxCR(Control register).  TBxMOD(Mode register).  TBxFFCR(Flip-flop control register).  TBxST(Status register).  TBxIM(Interrupt mask register).  TBxUC(Up counter capture register).  0 TBxRG0(Timer register 0).  1 TBxRG1(Timer register 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |