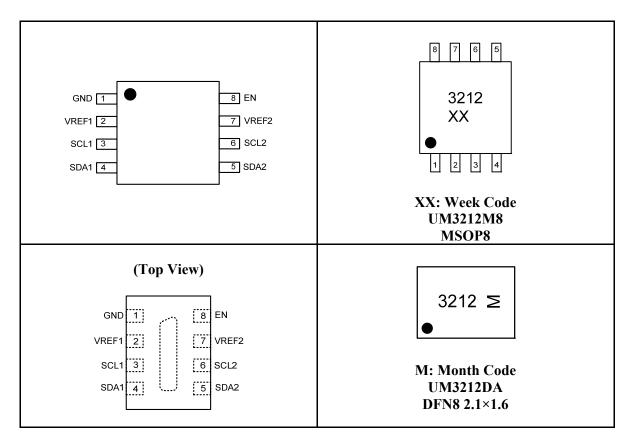

# Dual Bidirectional I<sup>2</sup>C-Bus and SMBus Voltage-Level Translator UM3212M8 MSOP8 UM3212DA DFN8 2.1×1.6 UM3212V8 VSSOP8

#### **General Description**

The UM3212 is a dual bidirectional I<sup>2</sup>C-bus and SMBus voltage-level translator with an enable (EN) input, and is operational from 1.0V to 3.6V ( $V_{ref(1)}$ ) and 1.8V to 5.5V( $V_{bias(ref)(2)}$ ).

The UM3212 allows bidirectional voltage translations between 1.0V and 5V without the use of a direction pin. The low ON-state resistance ( $R_{on}$ ) of the switch allows connections to be made with minimal propagation delay. When EN is HIGH, the translator switch is on, and the SCL1 and SDA1 I/O are connected to the SCL2 and SDA2 I/O, respectively, allowing bidirectional data flow between ports. When EN is LOW, the translator switch is off, and a high-impedance state exists between ports.

The UM3212 is not a bus buffer which provides both level translation and physically isolates the capacitance to either side of the bus when both sides are connected. The UM3212 only isolates both sides when the device is disabled and provides voltage level translation when active.

The UM3212 can also be used to run two buses, one at 400 kHz operating frequency and the other at 100 kHz operating frequency. If the two buses are operating at different frequencies, the 100 kHz bus must be isolated when the 400 kHz operation of the other bus is required. If the master is running at 400 kHz, the maximum system operating frequency may be less than 400 kHz because of the delays added by the translator.

As with the standard I<sup>2</sup>C-bus system, pull-up resistors are required to provide the logic HIGH levels on the translator's bus. The UM3212 has a standard open-collector configuration of the I<sup>2</sup>C-bus. The size of these pull-up resistors depends on the system, but each side of the translator must have a pull-up resistor. The device is designed to work with Standard-mode, Fast-mode and Fast-mode Plus I<sup>2</sup>C-bus devices in addition to SMBus devices. The maximum frequency is dependent on the RC time constant, but generally supports > 2MHz.

When the SDA1 or SDA2 port is LOW, the clamp is in the ON-state and a low resistance connection exists between the SDA1 and SDA2 ports. Assuming the higher voltage is on the SDA2 port when the SDA2 port is HIGH, the voltage on the SDA1 port is limited to the voltage set by VREF1. When the SDA1 port is HIGH, the SDA2 port is pulled to the drain pull-up supply voltage ( $V_{pu(D)}$ ) by the pull-up resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user without the need for directional control. The SCL1/SCL2 channel also functions as the SDA1/SDA2 channel.

All channels have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions, since the fabrication of the switch is symmetrical.

The translator provides excellent ESD protection to lower voltage devices, and at the same time protects less ESD-resistant devices.

#### Applications

- I<sup>2</sup>C, SMBus and SPI Level Translation

- Low-Voltage ASIC Level Translation

- Smart Card Readers

- Cell-Phone Cradles

- Portable POS Systems

- Portable Communication Devices

- Low-Cost Serial Interfaces

- Cell-Phones

- GPS

- Telecommunications Equipment

#### Features

- 2-Bit Bidirectional Translator for SDA and SCL Lines in Mixed-Mode I<sup>2</sup>C-Bus Applications

- Standard-Mode, Fast-Mode, Fast-Mode Plus and HS-Mode I<sup>2</sup>C-Bus and SMBus Compatible

- Less than 3.5ns Maximum Propagation Delay to Accommodate Standard-Mode and Fast-Mode I<sup>2</sup>C-Bus Devices and Multiple Masters

- Allows Voltage Level Translation between:

- 1) 1.0V VREF1 and 1.8V, 2.5V, 3.3V or 5V VREF2

- 2) 1.2V VREF1 and 1.8V, 2.5V, 3.3V or 5V VREF2

- 3) 1.8V VREF1 and 3.3V or 5V VREF2

- 4) 2.5V VREF1 and 5V VREF2

- 5) 3.3V VREF1 and 5V VREF2

- Open-Drain I<sup>2</sup>C-Bus I/O Ports (SCL1, SDA1, SCL2 and SDA2)

- Provides Bidirectional Voltage Translation with no Direction Pin

- Low 3.0Ω ON-State Connection between Input and Output Ports Provides Less Signal Distortion

- 5V Tolerant I<sup>2</sup>C-Bus I/O Ports to Support Mixed-Mode Signal Operation

- High-Impedance SCL1, SDA1, SCL2 and SDA2 Pins for EN=LOW

- Lock-up Free Operation

- Flow through Pinout for Ease of Printed-Circuit Board Trace Routing

- ESD Protection Exceeds 2000V HBM per JESD22-A114, 200V MM per JESD22-A115, and 1000V CDM per JESD22-C101

- Packages Offered: MSOP8, DFN8, VSSOP8

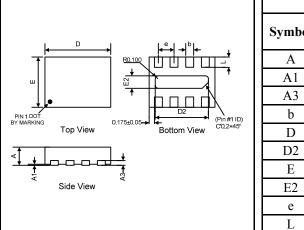

**Top View**

#### **Pin Configurations**

#### **Pin Description**

| Pin<br>Number | Symbol | Function                                                                      |

|---------------|--------|-------------------------------------------------------------------------------|

| 1             | GND    | Ground (0V).                                                                  |

| 2             | VREF1  | Low-voltage side reference supply voltage for SCL1 and SDA1.                  |

| 3             | SCL1   | Serial clock, low-voltage side; connect to VREF1 through a pull-up resistor.  |

| 4             | SDA1   | Serial data, low-voltage side; connect to VREF1 through a pull-up resistor.   |

| 5             | SDA2   | Serial data, high-voltage side; connect to VREF2 through a pull-up resistor.  |

| 6             | SCL2   | Serial clock, high-voltage side; connect to VREF2 through a pull-up resistor. |

| 7             | VREF2  | High-voltage side reference supply voltage for SCL2 and SDA2.                 |

| 8             | EN     | Switch enable input; connect to VREF2 and pull-up through a high resistor.    |

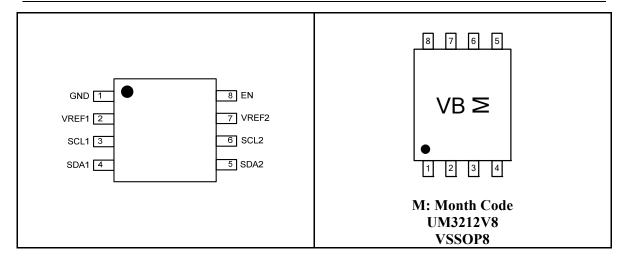

### **Ordering Information**

| Part Number | Packaging Type | Marking Code | Shipping Qty                 |

|-------------|----------------|--------------|------------------------------|

| UM3212M8    | MSOP8          | 3212         | 3000pcs/13Inch               |

|             |                |              | Tape & Reel                  |

| UM3212DA    | DFN8 2.1×1.6   | 3212         | 3000pcs/7Inch<br>Tape & Reel |

| UM3212V8    | VSSOP8         | VB           | 3000pcs/7Inch                |

| 0101321200  | 155010         |              | Tape & Reel                  |

#### Absolute Maximum Ratings (Note 1)

Over operating free-air temperature range (unless otherwise noted)

| Symbol                    | Parameter                      |                 | Value               | Unit |

|---------------------------|--------------------------------|-----------------|---------------------|------|

| V <sub>ref(1)</sub>       | Reference Voltage (1)          |                 | -0.5 to +6          | V    |

| V <sub>bias(ref)(2)</sub> | Reference Bias Voltage (2)     |                 | -0.5 to +6          | V    |

| VI                        | Input Voltage                  |                 | -0.5 (Note 2) to +6 | V    |

| V <sub>I/O</sub>          | Voltage on an Input/Output Pin |                 | -0.5 (Note 2) to +6 | V    |

| I <sub>ch</sub>           | Channel Current (DC)           |                 | +128                | mA   |

| I <sub>IK</sub>           | Input Clamp Current            | $V_{I} \leq 0V$ | -50                 | mA   |

| T <sub>stg</sub>          | Storage Temperature Range      |                 | -65 to +150         | °C   |

- Note 1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- Note 2: The input and input/output negative voltage ratings may be exceeded if the input and input/output clamp current ratings are observed.

| Symbol                                | Parameter                          | Conditions                | Min | Max | Unit |

|---------------------------------------|------------------------------------|---------------------------|-----|-----|------|

| V <sub>I/O</sub>                      | Voltage on an Input/<br>Output Pin | SCL1, SDA1,<br>SCL2, SDA2 | 0   | 5   | V    |

| V <sub>ref(1)</sub> (Note 3)          | Reference Voltage (1)              | VREF1                     | 0   | 5   | V    |

| V <sub>bias(ref)(2)</sub><br>(Note 3) | Reference Bias Voltage (2)         | VREF2                     | 0   | 5   | V    |

| V <sub>I(EN)</sub>                    | Input Voltage on Pin EN            |                           | 0   | 5   | V    |

| $I_{sw(pass)}$                        | Pass Switch Current                |                           |     | 64  | mA   |

| T <sub>amb</sub>                      | Ambient Temperature                | Operating in<br>Free-Air  | -40 | +85 | °C   |

Note 3:  $V_{ref(1)} \leq V_{bias(ref)(2)} - 1$  V for best results in level shifting applications.

#### **Electrical Characteristics**

$T_{amb}$ =-40°C to +85°C, unless otherwise specified.

| Symbol              | Parameter                             | Condi                                                           | tions                  | Min | Typ<br>(Note 4) | Max  | Unit |

|---------------------|---------------------------------------|-----------------------------------------------------------------|------------------------|-----|-----------------|------|------|

| V <sub>IK</sub>     | Input Clamping Voltage                | I <sub>I</sub> =-18mA;                                          | V <sub>I(EN)</sub> =0V |     |                 | -1.2 | V    |

| I <sub>IH</sub>     | HIGH-Level<br>Input Current           | V <sub>I</sub> =5<br>V <sub>I(EN)</sub>                         | ,                      |     |                 | 5    | μΑ   |

| C <sub>i(EN)</sub>  | Input Capacitance on<br>Pin EN        | V <sub>I</sub> =0V                                              | or 3V                  |     | 13              |      | pF   |

| Cio(off)            | Off-State Input/Output<br>Capacitance | SCLn, S<br>V <sub>0</sub> =0V or 3V                             |                        |     | 10              | 12.2 | pF   |

| C <sub>io(on)</sub> | On-State Input/Output<br>Capacitance  | SCLn, SDAn;<br>V <sub>0</sub> =0V or 3V; V <sub>I(EN)</sub> =3V |                        |     | 8               | 12   | pF   |

|                     |                                       | SCLn,                                                           | EN=4.5V                |     | 2.0             | 5.0  |      |

|                     |                                       | SDAn;                                                           | EN=3V                  |     | 2.4             | 6.0  |      |

|                     |                                       | (Note 6)<br>V <sub>I</sub> =0;                                  | EN=2.3V                |     | 3.1             | 8.0  |      |

|                     |                                       | $I_0 = 64 \text{mA}$                                            | EN=1.5V                |     | 11              | 32   |      |

| R <sub>on</sub>     | ON-State Resistance<br>(Note 5)       | SCLn,<br>SDAn;                                                  | EN=4.5V                |     | 4.6             | 7.5  | Ω    |

|                     | (1106 5)                              | V <sub>I</sub> =2.4V;<br>I <sub>0</sub> =15mA                   | EN=3V                  |     | 50              | 80   |      |

|                     |                                       | SCLn,<br>SDAn;<br>V <sub>I</sub> =1.7V;<br>I <sub>0</sub> =15mA | EN=2.3V                |     | 50              | 80   |      |

Note 4: All typical values are at  $T_{amb}=25^{\circ}C$ .

Note 5: Measured by the voltage drop between the SCL1 and SCL2, or SDA1 and SDA2 terminals at the indicated current through the switch.

ON-state resistance is determined by the lowest voltage of the two terminals.

Note 6: Guaranteed by design.

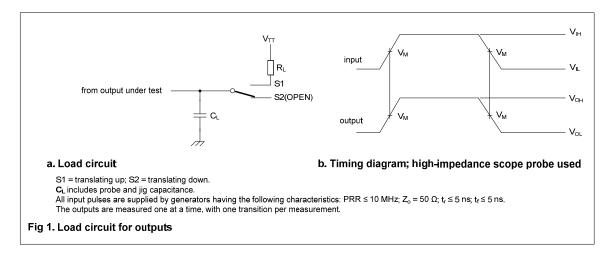

#### Switching Characteristics (Translating Down)

Over recommended operating free-air temperature range (unless otherwise noted). Values guaranteed by design.

| Symbol                  | Parameter                                                                       | Test                               | C <sub>L</sub> = | 50pF     | C <sub>L</sub> =3 | 30pF | $C_L=1$ | 15pF | Unit |

|-------------------------|---------------------------------------------------------------------------------|------------------------------------|------------------|----------|-------------------|------|---------|------|------|

| Symbol                  | rarameter                                                                       | Conditions                         | Min              | Max      | Min               | Max  | Min     | Max  | Unit |

| $V_{I(EN)} = 3.3$       | $V_{I(EN)}$ =3.3V; $V_{IH}$ =3.3V; $V_{IL}$ =0V; $V_{M}$ =1.15V (see Figure 1). |                                    |                  |          |                   |      |         |      |      |

| t <sub>PLH</sub>        | LOW to HIGH<br>Propagation<br>Delay                                             | from<br>(Input)<br>SCL2 or<br>SDA2 | 0                | 2.5      | 0                 | 1.7  | 0       | 1.2  | ns   |

| t <sub>PHL</sub>        | HIGH to LOW<br>Propagation<br>Delay                                             | to (Output)<br>SCL1 or<br>SDA1.    | 0                | 2.5      | 0                 | 2.0  | 0       | 1.3  | ns   |

| V <sub>I(EN)</sub> =2.5 | V; V <sub>IH</sub> =2.5V; V <sub>IL</sub> =                                     | =0V; V <sub>M</sub> =0.75V         | / (see Fi        | gure 1). |                   |      |         |      |      |

| t <sub>PLH</sub>        | LOW to HIGH<br>Propagation<br>Delay                                             | from<br>(Input)<br>SCL2 or<br>SDA2 | 0                | 2.5      | 0                 | 1.7  | 0       | 1.2  | ns   |

| t <sub>PHL</sub>        | HIGH to LOW<br>Propagation<br>Delay                                             | to (Output)<br>SCL1 or<br>SDA1.    | 0                | 3.0      | 0                 | 2.0  | 0       | 1.3  | ns   |

### **Switching Characteristics (Translating Up)**

Over recommended operating free-air temperature range (unless otherwise noted). Values guaranteed by design.

| Symbol            | Davamatar                                   | Test                               | $C_L = $             | 50pF                | C <sub>L</sub> =3 | 30pF     | $C_L=1$ | 15pF | Unit |

|-------------------|---------------------------------------------|------------------------------------|----------------------|---------------------|-------------------|----------|---------|------|------|

| Symbol            | Parameter                                   | Conditions                         | Min                  | Max                 | Min               | Max      | Min     | Max  | Unit |

| $V_{I(EN)} = 3.3$ | V; V <sub>IH</sub> =2.3V; V <sub>IL</sub> = | =0V; V <sub>TT</sub> =3.3V         | ; V <sub>M</sub> =1. | 15V; R <sub>L</sub> | =300Ω (           | see Figu | ire 1). |      |      |

| t <sub>PLH</sub>  | LOW to HIGH<br>Propagation<br>Delay         | from<br>(Input)<br>SCL1 or<br>SDA1 | 0                    | 2.35                | 0                 | 1.5      | 0       | 1.0  | ns   |

| t <sub>PHL</sub>  | HIGH to LOW<br>Propagation<br>Delay         | to (Output)<br>SCL2 or<br>SDA2.    | 0                    | 3.35                | 0                 | 2.25     | 0       | 1.4  | ns   |

| $V_{I(EN)} = 2.5$ | V; V <sub>IH</sub> =1.5V; V <sub>IL</sub> = | =0V; V <sub>TT</sub> =2.5V         | ; V <sub>M</sub> =0. | 75V; R <sub>L</sub> | =300Ω (           | see Figu | ire 1). |      |      |

| t <sub>PLH</sub>  | LOW to HIGH<br>Propagation<br>Delay         | from<br>(Input)<br>SCL1 or<br>SDA1 | 0                    | 2.35                | 0                 | 1.5      | 0       | 1.0  | ns   |

| t <sub>PHL</sub>  | HIGH to LOW<br>Propagation<br>Delay         | to (Output)<br>SCL2 or<br>SDA2.    | 0                    | 3.5                 | 0                 | 2.5      | 0       | 1.5  | ns   |

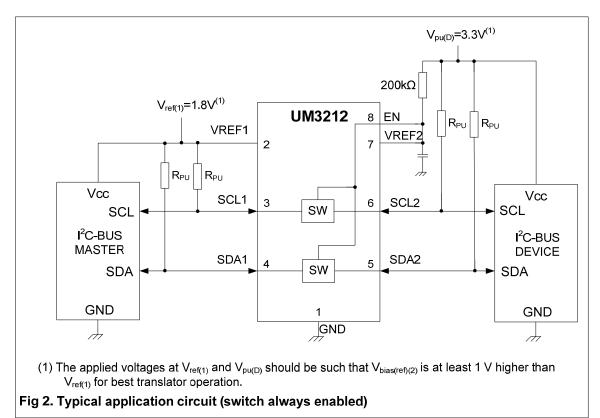

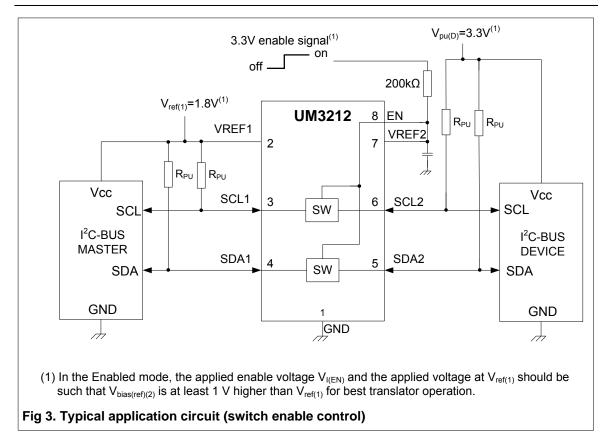

### **Typical Application Circuit**

#### **Applications Information**

#### **Bidirectional Translation**

For the bidirectional clamping configuration (higher voltage to lower voltage or lower voltage to higher voltage), the EN input must be connected to VREF2 and both pins pulled to HIGH side  $V_{pu(D)}$  through a pull-up resistor (typically 200k $\Omega$ ). This allows VREF2 to regulate the EN input. A filter capacitor on VREF2 is recommended. The I<sup>2</sup>C-bus master output can be totem pole or open-drain (pull-up resistors may be required) and the I<sup>2</sup>C-bus device output can be totem pole or open-drain (pull-up resistors are required to pull the SCL2 and SDA2 outputs to  $V_{pu(D)}$ ). However, if either output is totem pole, data must be unidirectional or the outputs must be 3-stateable and be controlled by some direction-control mechanism to prevent HIGH-to-LOW contentions in either direction. If both outputs are open-drain, no direction control is needed.

The reference supply voltage ( $V_{ref(1)}$ ) is connected to the processor core power supply voltage. When VREF2 is connected through a 200k $\Omega$  resistor to a 3.3V to 5.5V  $V_{pu(D)}$  power supply, and  $V_{ref(1)}$  is set between 1.0 V and ( $V_{pu(D)}$  –1V), the output of each SCL1 and SDA1 has a maximum output voltage equal to VREF1, and the output of each SCL2 and SDA2 has a maximum output voltage equal to  $V_{pu(D)}$ .

#### **Application Operating Conditions**

#### Refer to Figure 2

| Symbol                    | Parameter                  | Conditions               | Min                | Typ<br>(Note 7) | Max | Unit |

|---------------------------|----------------------------|--------------------------|--------------------|-----------------|-----|------|

| V <sub>bias(ref)(2)</sub> | Reference Bias Voltage (2) |                          | $V_{ref(1)} + 0.6$ | 2.1             | 5   | V    |

| V <sub>I(EN)</sub>        | Input Voltage on Pin EN    |                          | $V_{ref(1)} + 0.6$ | 2.1             | 5   | V    |

| $V_{ref(1)}$              | Reference Voltage (1)      |                          | 0                  | 1.5             | 4.4 | V    |

| I <sub>sw(pass)</sub>     | Pass Switch Current        |                          | -                  | 14              | -   | mA   |

| I <sub>ref</sub>          | Reference Current          | Transistor               | -                  | 5               | -   | μA   |

| T <sub>amb</sub>          | Ambient Temperature        | Operating<br>in Free-Air | -40                | -               | +85 | °C   |

Note 7: All typical values are at  $T_{amb}=25^{\circ}C$ .

#### **Sizing Pull-Up Resistor**

The pull-up resistor value needs to limit the current through the pass transistor when it is in the ON state to about 15mA. This ensures a pass voltage of 260 mV to 350 mV. If the current through the pass transistor is higher than 15mA, the pass voltage also is higher in the ON state. To set the current through each pass transistor at 15mA, the pull-up resistor value is calculated as:

$$R_{PU} = \frac{V_{pu(D)} - 0.35V}{0.015A}$$

The table below summarizes resistor reference voltages and currents at 15mA, 10mA, and 3mA. The resistor values shown in the +10 % column or a larger value should be used to ensure that the pass voltage of the transistor would be 350 mV or less. The external driver must be able to sink the total current from the resistors on both sides of the UM3212 device at 0.175V, although the 15mA only applies to current flowing through the UM3212 device

#### **Pull-Up Resistor Values**

Calculated for  $V_{OL}=0.35V$ ; assumes output driver  $V_{OL}=0.175V$  at stated current.

|                    |         | Pull-Up Resistor Value (Ω) |         |                  |         |                  |  |  |  |  |

|--------------------|---------|----------------------------|---------|------------------|---------|------------------|--|--|--|--|

| V                  | 15mA    |                            | 10      | mA               | 3n      | nA               |  |  |  |  |

| V <sub>pu(D)</sub> | Nominal | +10%<br>(Note 8)           | Nominal | +10%<br>(Note 8) | Nominal | +10%<br>(Note 8) |  |  |  |  |

| 5V                 | 310     | 341                        | 465     | 512              | 1550    | 1705             |  |  |  |  |

| 3.3V               | 197     | 217                        | 295     | 325              | 983     | 1082             |  |  |  |  |

| 2.5V               | 143     | 158                        | 215     | 237              | 717     | 788              |  |  |  |  |

| 1.8V               | 97      | 106                        | 145     | 160              | 483     | 532              |  |  |  |  |

| 1.5V               | 77      | 85                         | 115     | 127              | 383     | 422              |  |  |  |  |

| 1.2V               | 57      | 63                         | 85      | 94               | 283     | 312              |  |  |  |  |

Note 8:  $\pm 10\%$  to compensate for V<sub>CC</sub> range and resistor tolerance.

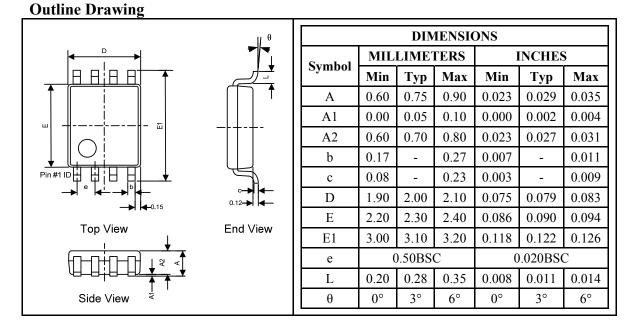

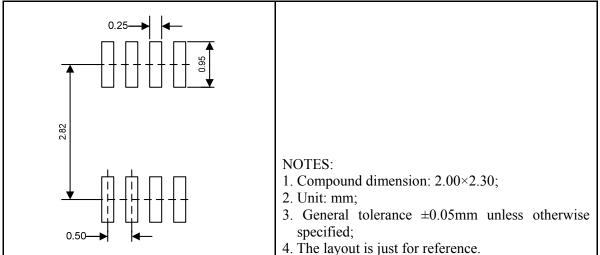

**Outline Drawing**

# **Package Information**

# UM3212M8: MSOP8

|           |               |          |      | DI     | MENSI | ONS    |         |       |

|-----------|---------------|----------|------|--------|-------|--------|---------|-------|

|           |               | Samula   | MIL  | LIME   | ΓERS  | Ι      | NCHES   |       |

| ı Dı      |               | Symbol - | Min  | Тур    | Max   | Min    | Тур     | Max   |

|           | ∘≁ ∢          | А        | -    | -      | 1.10  | -      | -       | 0.043 |

|           | <u>↓</u> Th ↓ | A1       | 0.02 | -      | 0.15  | 0.0008 | -       | 0.006 |

|           |               | A2       | 0.75 | 0.86   | 0.95  | 0.030  | 0.034   | 0.037 |

| ► 0.750   | ш 🛙           | A3       | 0.29 | 0.39   | 0.49  | 0.011  | 0.015   | 0.019 |

|           |               | b        | 0.22 | -      | 0.38  | 0.009  | -       | 0.015 |

| Pin #11D  |               | с        | 0.08 | 0.15   | 0.23  | 0.003  | 0.006   | 0.009 |

|           | θ             | D        | 2.90 | 3.00   | 3.10  | 0.114  | 0.118   | 0.122 |

| Top View  | End View      | Е        | 2.90 | 3.00   | 3.10  | 0.114  | 0.118   | 0.122 |

|           |               | E1       | 4.70 | 4.90   | 5.10  | 0.185  | 0.193   | 0.201 |

|           |               | E3       | 2.85 | 2.95   | 3.05  | 0.112  | 0.116   | 0.120 |

| Side View |               | e        | (    | ).65BS | С     | 0      | .026BSC | 1     |

|           |               | L        | 0.40 | 0.60   | 0.80  | 0.016  | 0.024   | 0.031 |

|           |               | θ        | 0°   | -      | 8°    | 0°     | -       | 8°    |

### Land Pattern

### **Tape and Reel Orientation**

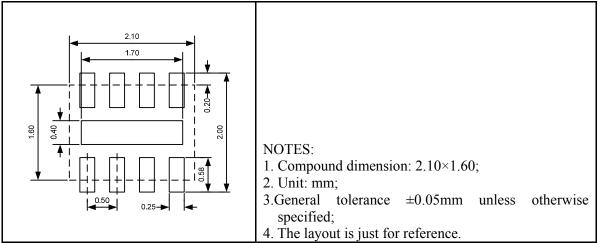

# UM3212DA: DFN8 2.1×1.6

### **Outline Drawing**

| DIMENSIONS |         |         |       |          |        |       |  |  |  |

|------------|---------|---------|-------|----------|--------|-------|--|--|--|

| Shal       | MIL     | LIMET   | ERS   | ]        | INCHES | 5     |  |  |  |

| Symbol     | Min     | Тур     | Max   | Min      | Тур    | Max   |  |  |  |

| А          | 0.50    | 0.575   | 0.605 | 0.020    | 0.023  | 0.024 |  |  |  |

| A1         | 0.00    | _       | 0.05  | 0.000    | _      | 0.002 |  |  |  |

| A3         | (       | 0.15TYF | )     | 0.006TYP |        |       |  |  |  |

| b          | 0.20    | 0.25    | 0.30  | 0.008    | 0.010  | 0.012 |  |  |  |

| D          | 2.05    | 2.10    | 2.175 | 0.081    | 0.083  | 0.086 |  |  |  |

| D2         | 1.60    | 1.70    | 1.80  | 0.063    | 0.067  | 0.071 |  |  |  |

| Е          | 1.55    | 1.60    | 1.675 | 0.061    | 0.063  | 0.066 |  |  |  |

| E2         | 0.30    | 0.40    | 0.50  | 0.012    | 0.016  | 0.020 |  |  |  |

| e          | 0.50TYP |         |       | C        | .020TY | Р     |  |  |  |

| L          | 0.275   | _       | 0.38  | 0.011    | -      | 0.015 |  |  |  |

#### Land Pattern

### Tape and Reel Orientation

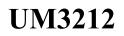

# UM3212V8: VSSOP8

#### Land Pattern

#### **Tape and Reel Orientation**

# **GREEN COMPLIANCE**

Union Semiconductor is committed to environmental excellence in all aspects of its operations including meeting or exceeding regulatory requirements with respect to the use of hazardous substances. Numerous successful programs have been implemented to reduce the use of hazardous substances and/or emissions.

All Union components are compliant with the RoHS directive, which helps to support customers in their compliance with environmental directives. For more green compliance information, please visit:

http://www.union-ic.com/index.aspx?cat\_code=RoHSDeclaration

## **IMPORTANT NOTICE**

The information in this document has been carefully reviewed and is believed to be accurate. Nonetheless, this document is subject to change without notice. Union assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the contained information, or to notify a person or organization of any update. Union reserves the right to make changes, at any time, in order to improve reliability, function or design and to attempt to supply the best product possible.

Union Semiconductor, Inc Add: Unit 606, No.570 Shengxia Road, Shanghai 201210 Tel: 021-51093966 Fax: 021-51026018 Website: www.union-ic.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Translation - Voltage Levels category:

Click to view products by Union manufacturer:

Other Similar products are found below :

NLSX4373DMR2G NLSX5012MUTAG NLSX0102FCT1G NLSX0102FCT2G PCA9306FMUTAG MC100EPT622MNG NLSX3014MUTAG NLSV4T244EMUTAG NLSX5011MUTCG NLVSX4373MUTAG NB3U23CMNTAG NLVPCA9306AMUTCG NLSX3013BFCT1G NLSX3012DMR2G NLA9306MU3TCG NVT2001GMZ P3A9606JKZ NLVSV1T244MUTBG NLSX5011AMUTAG 74AXP1T34GWH MS4553S HT7660ARZ RS0108YQ20 UM3204Q UM3204UE UM3204H UM3208UK UM3202Q RS8T245YTSS24 UM3308UK UM3212M8 UM3304QA AW39104FOR RS0101YH6 CLVC16T245MDGGREP CAVCB164245MDGGREP NTS0102DP-Q100H FXLA104UM12X FXMA2102UMX PI4ULS5V201TAEX CD40109BPWR SY89321LMG-TR SY100ELT22ZG TXS0102DCTRE4 MC10H350FNG MC10H125FNR2G MC100EPT21MNR4G MC100EP91DWG MAX13030EETE+ NLSX3018MUTAG