# ADC Prefilter with Analog Multiplexer

### **General Description**

The uS5650Q is a 4-Channel Analog prefilter and Multiplexer. This 4 channel device is intended to condition single and differential signals at bus voltages to a range appropriate for sampling with a low voltage ADC. Power supply operates from 2.8V to 3.8V.

# Ordering Information

| Order Number | Package     | Top Marking |

|--------------|-------------|-------------|

| uS5650QQKI   | WQFN4x4-32L | uS5650Q     |

#### Note:

- (1) Please check the sample/production availability with uPl representatives.

- (2) uPI products are compatible with the current IPC/JEDEC J-STD-020 requirements. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

## **Applications**

- Computers

- Power Management

- Telecom Equipment

- Battery Chargers

- Power Supplies

- Test Equipment

#### Features

- 4 Differential to Single-Ended Trans-Conductance Amplifier

- 2\*4-to-1 (1 for Bus, 1 for Shunt) Analog Multiplexer with Single Bit for MUX Select

- Single-Ended to Differential Converter with Buffered Input Reference Voltages

- Strap Selectable to Operate the Device by Itself or in a Pair

- Enable Input that Enables Active Devices and Controls an Internal FET to Ground

- Operating Shunt Voltage: 5V to 30V

- Max Bus Voltage: 30V

- Power Supply Operation: 2.8V to 3.8V

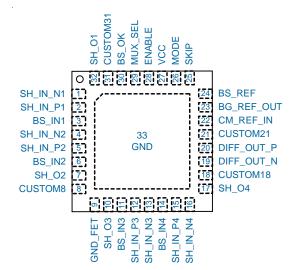

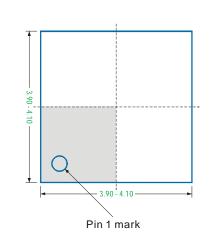

**Pin Configuration**

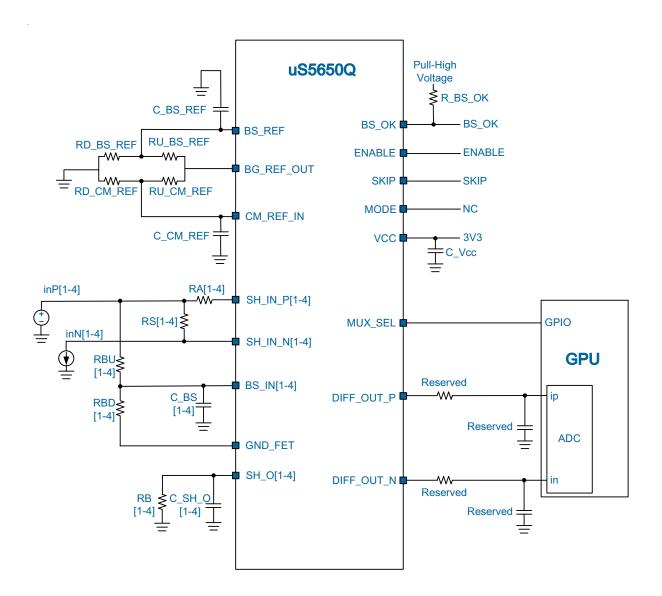

# Typical Application Circuit

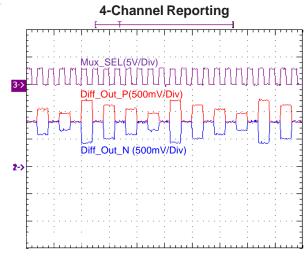

4-Channel Application Circuit (Stand-Alone Mode)

#### Note:

There are two differential output reserved resistance  $(0.86\Omega - 8.6\Omega)$  and capacitance (22pF - 82pF) which appears as a series RC with lumped equivalent.

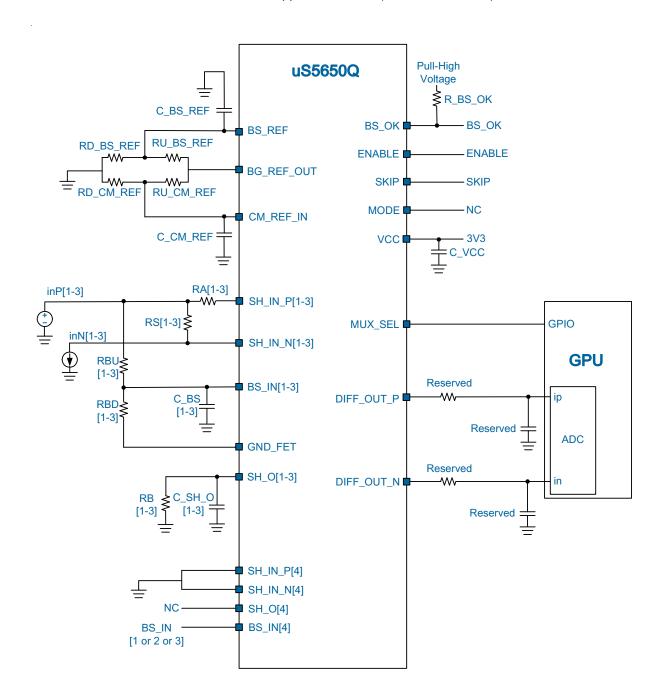

## Typical Application Circuit

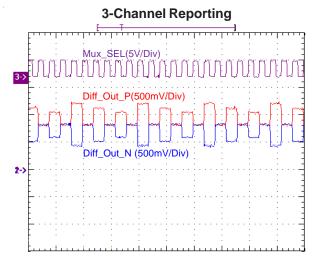

3-Channel Application Circuit (Stand-Alone Mode)

#### Note:

uS5650Q needs to incorporate at least 2 channels. Channel-reduction needs to start from channel 4. If channel reduction is used in parallel mode, both devices will operate the same number of channels.

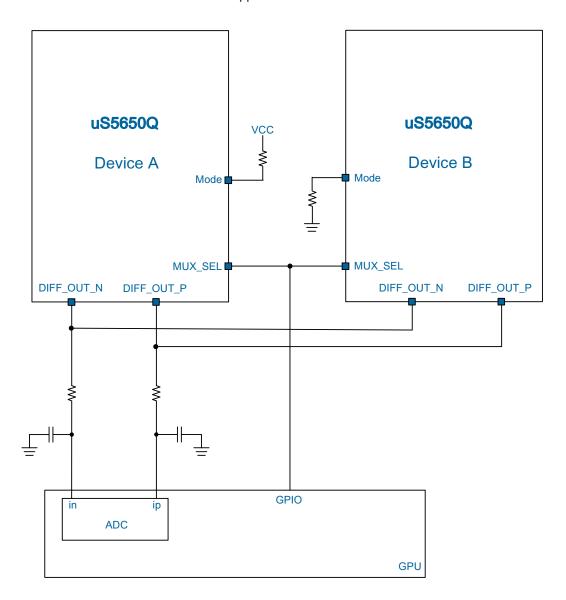

# Typical Application Circuit

### Two Device Application Circuit

EN is individual related to the GPU signal instead of Mode and VCC

| Pin No. | Pin Name   | I/O | Pin Function                                                                |

|---------|------------|-----|-----------------------------------------------------------------------------|

| 1       | SH_IN_N1   | Al  | Negative Side of Shunt Input. High impedance, high voltage, avoid floating. |

|         |            |     |                                                                             |

| 2       | SH_IN_P1   | Al  | Positive Side of Shunt Input. High impedance, high voltage, avoid floating. |

| 3       | BS_IN1     | Al  | Analog Input for Bus Voltage Multiplexer. Avoid floating.                   |

| 4       | SH_IN_N2   | Al  | Negative Side of Shunt Input. High impedance, high voltage, avoid floating. |

| 5       | SH_IN_P2   | Al  | Positive Side of Shunt Input. High impedance, high voltage, avoid floating. |

| 6       | BS_IN2     | Al  | Analog Input for Bus Voltage Multiplexer. Avoid floating.                   |

| 7       | SH_O2      | AO  | Current Source Proportional to Shunt Voltage. Low Voltage.                  |

| 8       | CUSTOM8    |     | NC. For custom functions.                                                   |

| 9       | GND_FET    | Al  | Ground to FET. It can be connected to internal FET to short to GND.         |

| 10      | SH_O3      | AO  | Current Source Proportional to Shunt Voltage. Low Voltage                   |

| 11      | BS_IN3     | Al  | Analog Input for Bus Voltage Multiplexer. Avoid Floating.                   |

| 12      | SH_IN_P3   | AI  | Positive Side of Shunt Input. High impedance, high voltage, avoid floating. |

| 13      | SH_IN_N3   | Al  | Negative Side of Shunt Input. High impedance, high voltage, avoid floating  |

| 14      | BS_IN4     | AI  | Analog Input for Bus Voltage Multiplexer. Avoid Floating.                   |

| 15      | SH_IN_P4   | AI  | Positive Side of Shunt Input. High impedance, high voltage, avoid floating  |

| 16      | SH_IN_N4   | AI  | Negative Side of Shunt Input. High impedance, high voltage, avoid floating  |

| 17      | SH_O4      | AO  | Current Source Proportional to Shunt Voltage. Low Voltage                   |

| 18      | CUSTOM18   |     | NC. For custom functions.                                                   |

| 19      | DIFF_OUT_N | AO  | Differential Output. Negative Terminal.                                     |

| 20      | DIFF_OUT_P | AO  | Differential Output. Positive Terminal.                                     |

| 21      | CUSTOM21   |     | NC. For custom functions.                                                   |

| 22      | CM_REF_IN  | Al  | Common Mode Reference.                                                      |

| 23      | BG_REF_OUT | AO  | Bandgap Analog Out.                                                         |

| 24      | BS_REF     | Al  | Reference Input for the Bus Ready Comparator.                               |

| 25      | SKIP       | Al  | Mask for BS_OK.                                                             |

| 26      | MODE       | DI  | Mode Selection for stand-alone. As device-A, or as device-B                 |

| 27      | VCC        | Al  | VCC of device.                                                              |

| 28      | ENABLE     | DI  | Enable. It takes device out of sleep and opens GNDFET.                      |

| 29      | MUX_SEL    | DI  | Multiplexer Selection.                                                      |

| 30      | BS_OK      | DO  | Open Drain Digital Output. Indicating the bus is OK.                        |

| 31      | CUSTOM31   |     | NC. For custom functions.                                                   |

| 32      | SH_O1      | AO  | Current Source Proportional to Shunt Voltage. Low Voltage.                  |

| EP      | GROUND [1] |     | Power GND of Device.                                                        |

|         |            |     |                                                                             |

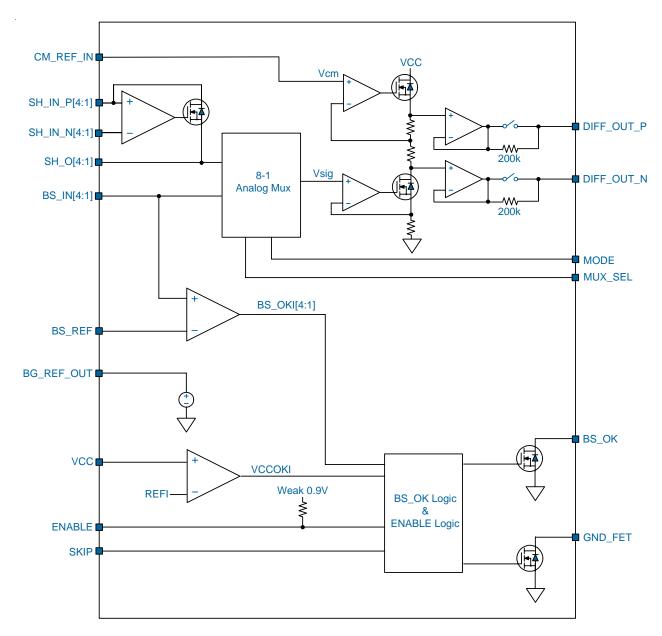

# Functional Block Diagram

Diagram of device in use with passives and GPU. Circuits drawn inside the device are representative of its function; implementation can differ. Values are provided for approximate reference only and will change based on exact application (see Inputs, Analog Multiplexer, and Differential Output) or uPI's choice in certain device parameters.

#### Inputs, Analog Multiplexer, and Differential Output

For a 4-channel device, there will be 4 shunt inputs and 4 bus inputs. The shunt input is a transconductance architecture of which SH\_IN\_P and SH\_IN\_N are positive and negative terminals respectively. SH\_O is the output of the transconductance which allows the gain to be set. This pin also internally connects to the multiplexer input. BS\_IN is a straight connection to the multiplexer input.

The chracteristics of Shunt\_IN\_P/N are as follows,

when

$$I_{LOAD} = 0$$

,  $I_{SHINP} = OPA-Offset/RA$ ;

when

$$V_{SH IN N} < V_{CC}$$

,  $I_{SH IN N} = 0$ .

The output of the multiplexer will feed a single to differential stage that drives the GPU. A common mode is provided by CM\_REF\_IN. DIFF\_OUT\_P and DIFF\_OUT\_Ndrive Vcm+4/3\*Vsig and Vcm-4/3\*Vsig respectively where Vsig is the output of the multiplexer which can be the voltage on either SH\_O or BS\_IN. It can also be different between the shunt and bus inputs. Note that since Vsig will always be positive, DIFF\_OUT\_P will always be equal or higher potential than DIFF\_OUT\_N.

The load that DIFF\_OUT needs to drive is dominated by board and GPU package traces and will have a lump equivalent fall in this range:

R:  $860 \sim 8600 \text{m}\Omega$

C: 22~82pF

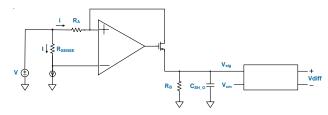

#### **Shunt Configuration**

Figure 1. Shunt Configuration

$$V_{diff} = 8/3V_{SIG}$$

$$V_{SIG} = \frac{R_B}{R_A} \times R_{SENSE} \times I$$

$(R_{_B} \, larger \, than \, 2k\Omega \, can \, be \, considered floating for channel count selection)$

$$\text{Shunt Gain} = \frac{V_{\textit{SIG}}}{R_{\textit{SENSE}} \times I} = \frac{R_{\textit{B}}}{R_{\textit{A}}}$$

If Full Range  $V_{SIG} = 0.3V$ ,  $R_{B} = 1020$ ,  $R_{A} = 340$ ,

$R_{\text{SENSE}} = 1 \text{m}\Omega$

=>Shunt Gain = 3

=> Full Range Shunt Voltage(V)

$$=V_{SENSE\_FULL} = \frac{0.3}{3} \cong 0.1(V)$$

Full Range Current(A) =

$$\frac{V_{SENSE\_FULL}}{R_{SENSE}} = \frac{0.1}{1m} \cong 100 (A)$$

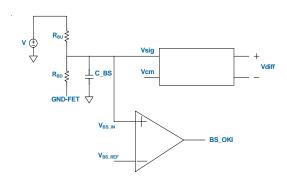

#### **Bus Configuration**

Figure 2. Bus Configuration

$$V_{diff} = 8/3V_{SIG}$$

$$V_{SIG} = \frac{R_{BD}}{R_{RU} + R_{RD}} \times V$$

$$BusGain = \frac{V_{SIG}}{V} = \frac{R_{BD}}{R_{BU} + R_{BD}}$$

$$\frac{1}{BusGain} = \frac{R_{BU} + R_{BD}}{R_{BD}}$$

If Full Range  $V_{SIG} = 0.3V$ ,  $R_{BD} = 200$ ,  $R_{BU} = 15.8k$ ,

$$=>\frac{1}{BusGain}=\frac{200+15.8k}{200}=80$$

=>Full Range Bus Voltage(V) = 80 x 0.3 = 24(V)

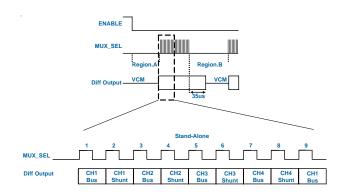

#### **Multiplexer Select Operation**

The multiplexer selection is done through a single bit digital input clocked. The device will monitor the input and cycle through the different op-amps in a fixed sequence. The sequence that the multiplexer must follow starts with the bus of the first enumerated before altering to its shunt. It then cycles likewise through the bus/shunt pairs in order of enumeration repeating itself after the shunt of the last active channel has been passed through the multiplexer. The multiplexer will repeat the cycle indefinitely until either a timeout condition is detected or a disable is asserted.

Devices can be configured to work in one three modes of operation: stand-alone, as device-A, or as device-B using

the MODE pin. In stand-alone operation, the device will cycle through op-amps all clock cycles. As device-A, the device will respond to the first set of clock cycle and go into high impedance while device-B responds to the subsequent clocks. Two devices, one configured as device-A and another as device-B will share MUX\_SEL and DIFF\_OUT lines on the PCB.

Devices can also be configured to work in reduced channel count. By floating a given SH\_O, channels of equal and higher enumeration will remain unused. Unused channels will behave as if they do not exist and be skipped over by the multiplexer. uP9026Q needs to corporate at least 2 channels. Channel-reduction needs to start from channel 4. If channel reduction is used in parallel mode, both devices will operate the same number of channels. Reducing the channel count of multiplexer will NOT impact Bus Comparator operation.

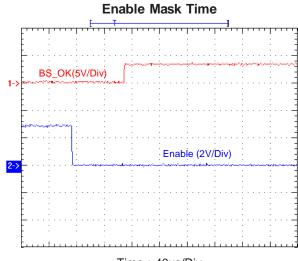

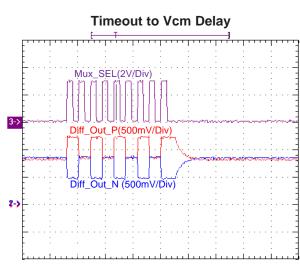

The Diff Output is VCM when ENABLE pin pulls low and MUX\_SEL not start up. Stopping MUX\_SEL over 35us will let Diff Output to VCM. Rising edge of MUX\_SEL to when DIFF\_OUT achieve 6mV error is within 250ns

Table 1. Characteristics of MODE Pin

| Mode Pin Connection                                   | Operation Mode |

|-------------------------------------------------------|----------------|

| Pull high to VCC with R < 10kΩ (Mode > 2V)            | Device-A       |

| Pull low to GND with R < $10k\Omega$ (Mode < $0.6V$ ) | Device-B       |

| Floating                                              | Stand-Alone    |

Table 2. Diff Output Reporting Sequence of 4-Channel Stand-Alone Mode

| 4-Channel Stand-Alone Mode |           |  |  |

|----------------------------|-----------|--|--|

| Clock Cycle Diff Output    |           |  |  |

| 0                          | VCM       |  |  |

| 1                          | Ch1 Bus   |  |  |

| 2                          | Ch1 Shunt |  |  |

| 3                          | Ch2 Bus   |  |  |

| 4                          | Ch2 Shunt |  |  |

| 5                          | Ch3 Bus   |  |  |

| 6                          | Ch3 Shunt |  |  |

| 7                          | Ch4 Bus   |  |  |

| 8                          | Ch4 Shunt |  |  |

| 9                          | Ch1 Bus   |  |  |

Figure 3.Diff Output Reporting Sequence of 4-Channel Stand-Alone Mode

Table 3. Diff Output Reporting Sequence of 6-Channel Parallel Mode

| 6-Channel Parallel Mode |                     |                     |  |  |

|-------------------------|---------------------|---------------------|--|--|

| Clock<br>Cycle          | Diff Output (Dev A) | Diff Output (Dev B) |  |  |

| 0                       | VCM                 | VCM                 |  |  |

| 1                       | Ch1 Bus             | VCM                 |  |  |

| 2                       | Ch1 Shunt           | VCM                 |  |  |

| 3                       | Ch2 Bus             | VCM                 |  |  |

| 4                       | Ch2 Shunt           | VCM                 |  |  |

| 5                       | Ch3 Bus             | VCM                 |  |  |

| 6                       | Ch3 Shunt           | VCM                 |  |  |

| 7                       | VCM                 | Ch1 Bus             |  |  |

| 8                       | VCM                 | Ch1 Shunt           |  |  |

| 9                       | VCM                 | Ch2 Bus             |  |  |

| 10                      | VCM                 | Ch2 Shunt           |  |  |

| 11                      | VCM                 | Ch3 Bus             |  |  |

| 12                      | VCM                 | Ch3 Shunt           |  |  |

| 13                      | Ch1 Bus             | VCM                 |  |  |

#### **Bus Comparator**

Operating independently from the multiplexer, the device will also have comparators for each bus inputs and VCC. If the BS\_IN of all active channels compare positively against a reference on BS\_REF, VCC compares positively against an internally generated reference and the SKIP pin is not

being asserted low, it will release an open drain output BS\_OK. As much as feasible, BS\_OK should remain low impedance logic low even when VCC goes below operating threshold. SKIP needs to be high voltage tolerant and can be used to power BS\_OK pull down in cases where the voltage of VCC becomes low.

#### **Bandgap Reference**

BG\_REF\_OUT provides a high accuracy bandgap reference from which BS\_REF and CM\_REF\_IN can be derived.

#### **Ground FET**

GND\_FET is a switch that connects the bus divider to ground that can be disconnected to break any leakage path between input power and ground.

#### **Enable**

Three logic levels and their behavior defined as follows. Note that enable logic levels are defined differently from expected convention.

Table 4. Configuration of ENABLE Pin

| Enable<br>State | Description                                                                                                                                                                                        |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low             | Fully Functional                                                                                                                                                                                   |

| Tri-state       | Limited Function. Only BG_REF_OUT, GND_FET, BS_OK are functional . All other biasing should be minimized. In this state, DIFF_OUT will always be high impedance and MUX_SEL logic will be ignored. |

| High            | Standby. In addition to saving features of Limited Function, GND_FET will be disconnected and additional power saving where possible.                                                              |

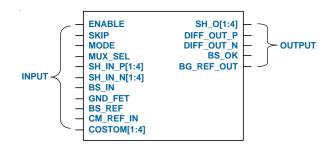

Figure 4. I/O of uS5650Q

Complete logic table of ENABLE, VCC, SKIP and BS\_IN is as follows,

Table 5. Logic Table of uS5650Q

| ENABLE | ОТР | VCC BS_IN |   | VCC BS_IN    |   | SKIP | BS_OK |

|--------|-----|-----------|---|--------------|---|------|-------|

| X      | Н   | Х         |   |              |   |      |       |

| Н      |     | Х         |   |              |   |      |       |

| T/L    | L   | L         | Х | Н            | L |      |       |

|        |     | Х         | L |              |   |      |       |

|        |     |           | Н |              | Н |      |       |

| X      |     |           | L | (open drain) |   |      |       |

### Table 6. Configuration of UVLO/OTP

| State | SH_O[1:4]           | DIFF_OUT_P/N | BS_OK       | BG_REF_OUT | T/O Counter |

|-------|---------------------|--------------|-------------|------------|-------------|

| UVLO  | Low by Ext Resistor | High Z       | See Table 5 | Low        | Reset       |

| OTP   | Low by Ext Resistor | High Z       | See Table 5 | Keep       | Reset       |

#### **VCC and GND**

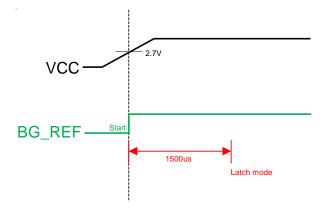

The device has a VCC pin and GND will use the thermal pad. When the device reaches its VCC voltage threshold, there can be a delay during before Full Function operation is expected and MUX\_SEL will not toggle. It is expected that MODE and channel determination will happen during this delay.

#### Customization

Those pins should be floated in production use.

|                                                                                                                                                                                                                                                                                     | _ Absolute Maximum Rating                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| (Note 1)                                                                                                                                                                                                                                                                            |                                                                                 |

| Supply Input Voltage, VCC                                                                                                                                                                                                                                                           | 2.8V to 6V                                                                      |

| Safe Voltage(SH_IN_P, SH_IN_N)                                                                                                                                                                                                                                                      |                                                                                 |

| Operating Voltage(SH_IN_P,SH_IN_N)                                                                                                                                                                                                                                                  |                                                                                 |

| Safe Voltage(BS_IN)                                                                                                                                                                                                                                                                 |                                                                                 |

| Reference Voltage for the Bus(BS_REF)                                                                                                                                                                                                                                               |                                                                                 |

| SKIP Operating Voltage                                                                                                                                                                                                                                                              |                                                                                 |

| DIFF_OUT Safety Voltage                                                                                                                                                                                                                                                             |                                                                                 |

| Safety Temperature                                                                                                                                                                                                                                                                  |                                                                                 |

| Lead Temperature (Soldering, 10 sec)                                                                                                                                                                                                                                                | 260°C                                                                           |

| ESD Rating (Note 2)                                                                                                                                                                                                                                                                 |                                                                                 |

| HBM (Human Body Mode)                                                                                                                                                                                                                                                               |                                                                                 |

| CDM (Charged Device Mode)                                                                                                                                                                                                                                                           | 1kV                                                                             |

|                                                                                                                                                                                                                                                                                     | Thermal Information                                                             |

|                                                                                                                                                                                                                                                                                     | - Triorman information                                                          |

| Package Thermal Resistance (Note 3)                                                                                                                                                                                                                                                 | 0770044                                                                         |

| WQFN4x4-32L $\theta_{JA}$                                                                                                                                                                                                                                                           | 3/°C/W                                                                          |

| WQFN4x4-32L0 <sub>JC</sub>                                                                                                                                                                                                                                                          | 20°C/VV                                                                         |

| Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C<br>WQFN4x4-32 L                                                                                                                                                                                                           | 1\\/                                                                            |

| WQFN4X4-32 L                                                                                                                                                                                                                                                                        | I VV                                                                            |

| Recomm                                                                                                                                                                                                                                                                              | ended Operation Conditions                                                      |

| (Note 4)                                                                                                                                                                                                                                                                            | •                                                                               |

| Supply Input Voltage, VCC                                                                                                                                                                                                                                                           |                                                                                 |

| Supported CM_REF_IN (Note 5)                                                                                                                                                                                                                                                        | 565mV to 885mV                                                                  |

| Safety Temperature                                                                                                                                                                                                                                                                  |                                                                                 |

| Operating Junction Temperature Range                                                                                                                                                                                                                                                |                                                                                 |

| Operating Ambient Temperature Range                                                                                                                                                                                                                                                 |                                                                                 |

| Note 1. Stresses listed as the above Absolute Maximum Ratings may can These are for stress ratings. Functional operation of the device at indicated in the operational sections of the specifications is not imrating conditions for extended periods may remain possibility to all | these or any other conditions beyond those oplied. Exposure to absolute maximum |

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- **Note 3.**  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}\text{C}$  on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- **Note 4.** The device is not guaranteed to function outside its operating conditions.

- Note 5. The typical value is 850mV.

### Electrical Characteristics

## (VCC = 3.3V, $T_A = 25$ °C, unless specified)

| Parameter                                    | Symbol | Test Conditions | Min        | Тур   | Max   | Units |

|----------------------------------------------|--------|-----------------|------------|-------|-------|-------|

| SH_IN_N Current                              |        |                 |            |       | 100   | uA    |

| Operating Voltage (SH_O)                     |        |                 |            |       | 0.3   | V     |

| Current Capability (SH_O)                    |        |                 | 1          |       |       | mA    |

| SH_O Floating Detection Resistance           |        |                 | 10k        |       |       | Ω     |

| Capacitance Load (SH_O_C)                    |        |                 | 2.2        |       | 100   | nF    |

| Comparator Offset Voltage                    |        |                 | -3         |       | 3     | mV    |

| Mux_Sel VIH                                  |        |                 | 1.4        |       |       | V     |

| Mux_Sel VIL                                  |        |                 |            |       | 0.4   | V     |

| Mux_Sel High/Low Duration                    |        |                 | 50         |       | 1     | ns    |

| Mux_Sel Timeout Reset                        |        |                 | 35         |       |       | us    |

| BS_OK Logic Low Impedance                    |        |                 |            |       | 100   | Ω     |

| Bandgap Level [1]                            |        |                 | 1.274      | 1.300 | 1.326 | V     |

| BS_OK Delay Time                             |        |                 |            | 75    |       | us    |

| Tristate Input Impedance                     |        |                 | 100k       |       |       | Ω     |

| VCC to Full Function Delay                   |        |                 |            |       | 2     | ms    |

| Standby or Limited Function to Full Function |        |                 |            |       | 40    | us    |

| GNDFET On-resistance                         |        |                 |            |       | 10    | Ω     |

| Device IDDQ Fully Functional                 |        |                 |            | 1.6   |       | mA    |

| Device IDDQ Limited Function                 |        |                 |            | 0.25  |       | mA    |

| Device IDDQ Disabled                         |        |                 |            | 0.25  | 1     | mA    |

| VCC Threshold Reference for BS_OK Input [2]  |        |                 | 2.6        |       | 2.8   | V     |

| VCC for BS_OK Low Impedance [3]              |        |                 | 1.0<br>[5] |       | 3.8   | V     |

| VCC Hysteresis for BS_OK Input               |        |                 | 100        | 150   | 200   | mV    |

| BS_OK Comparator Hysteresis                  |        |                 | 15         | 20    | 25    | mV    |

| Enable/SKIP VIH [4]                          |        |                 | 1.4        |       |       | V     |

| Enable/SKIP VIL [4]                          |        |                 |            |       | 0.4   | V     |

<sup>[1]</sup> Exact values can be defined manufacturer by should fit within a  $\pm$ -2% tolerance of some nominal

<sup>[2]</sup> VCC detection for BS\_OK must trip in this trip. Device can be either operational or not in this range

<sup>[3]</sup> VCC range where BS\_OK can maintain logic low impedance

<sup>[4]</sup> Enable driving capability should greater than 2 uA

<sup>[5]</sup> Only when SKIP voltage exceeds 2.8V, the minimum of VCC is 1.0V.

# **Typical Operation Characteristics**

Time: 40us/Div

Time: 40us/Div

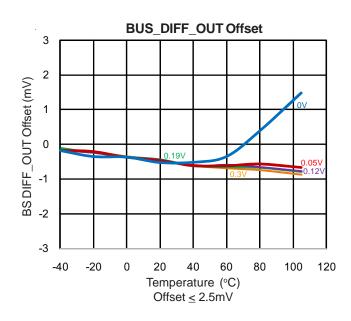

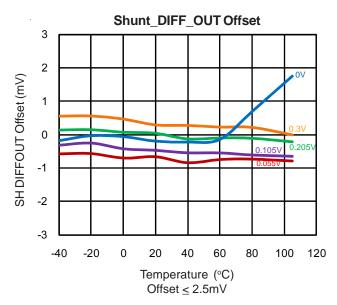

Time: 100us/Div

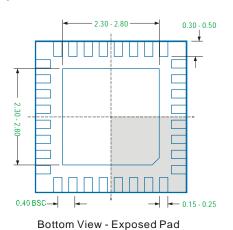

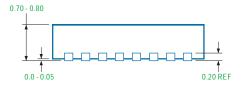

## Package Information

#### WQFN4x4 - 32L

#### Note

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

### **Important Notice**

The contents of this document are provided in connection with uPI Semiconductor Corp. ("uPI") products. uPI makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice.

No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights, is granted by this publication. Except as provided in uPI's terms and conditions of sale for such products, uPI assumes no liability whatsoever, and uPI disclaims any express or implied warranty relating to sale and/or use of uPI products, including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. uPI products are not designed, intended, authorized or warranted for use as components in systems intended for medical, life-saving, or life sustaining applications. uPI reserves the right to discontinue or make changes to its products at any time without notice.

Copyright 2019 ©, uPI Semiconductor Corp. All rights reserved.

uPI, uPI Micro Power Intellect logo, and combinations thereof, are registered trademarks of uPI Semiconductor Corp. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

®

### uPI Semiconductor Corp.

9F.,No.5, Taiyuan 1st St. Zhubei City, Hsinchu, Taiwan, R.O.C. TEL: 886.3.560.1666 FAX: 886.3.560.1888 sales@upi-semi.com