# Reference Manual

### VCM-DAS-1/2

Analog & Digital Input/Output Module for the PC/104 Bus

## VCM-DAS-1/2

Analog & Digital Input/Output Module for the PC/104 Bus

### Model VCM-DAS-1/2

Analog & Digital Input/Output Module for the PC/104 Bus

#### REFERENCE MANUAL

Doc. Rev. 4/9/2013

#### VERSALOGIC CORPORATION

WWW.VERSALOGIC.COM

12100 SW Tualatin Road Tualatin, OR 97062-7341 (503) 747-2261 Fax (971) 224-4708

Contents Copyright © 2004-2013 All Rights Reserved

#### Notice:

Although every effort has been made to ensure this document is error-free, VersaLogic makes no representations or warranties with respect to this product and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose.

VersaLogic reserves the right to revise this product and associated documentation at any time without obligation to notify anyone of such changes.

PC/104 and the PC/104-Plus logo are trademarks of the PC/104 Consortium.

## **Table of Contents**

| Other References                       | vii |

|----------------------------------------|-----|

| Overview                               | 1   |

| Using This Manual                      |     |

| Introduction                           |     |

| Features                               |     |

| General                                |     |

| Analog Input                           |     |

| Analog Output                          |     |

| Digital I/O                            |     |

| Technical Specifications               |     |

| Technical Support                      |     |

| Repair Service                         |     |

| Configuration                          |     |

| Hardware Jumper Summary                |     |

| Jumper Block Locations                 |     |

| Module Addressing                      |     |

| Analog Input Configuration             |     |

| Input Range                            |     |

| Low Pass Filter                        |     |

| Analog Output Configuration            |     |

| Output Range                           |     |

| Analog Loopback                        |     |

| 5B01 Analog Signal Conditioning Rack   |     |

| Digital Input/Output Configuration     |     |

| Rack Power Control                     |     |

| Interrupt Configuration                |     |

| IRQ Selection                          |     |

| Shared Interrupt Configuration         |     |

| About Shared Interrupts                |     |

| Regular Interrupts                     |     |

| Shared Interrupts                      |     |

| DMA Configuration.                     |     |

| Installation                           |     |

| Handling                               |     |

| Arranging the PC/104 Stack             |     |

| Signal Levels                          |     |

| External Connectors                    |     |

| Connector Functions                    |     |

| Connector Locations                    |     |

| Mating Connectors and Cable Assemblies |     |

| J1 – Digital I/O Connector             |     |

| J2 – Analog I/O Connector              |     |

| Regis | sters                                                  | 23 |

|-------|--------------------------------------------------------|----|

| •     | Introduction.                                          |    |

|       | I/O Port Mapping                                       | 23 |

|       | I/O Port Register Functions                            | 24 |

|       | Serial Port Interface (SPI) Register Functions         |    |

|       | SPI Read Data Register                                 | 26 |

|       | SPI Write Data Register                                |    |

|       | SPI Select Register                                    |    |

|       | Analog Input Registers                                 |    |

|       | ADC Periodic Trigger Rate Register                     |    |

|       | ADC Convert Register                                   |    |

|       | ADC Select Register                                    |    |

|       | Control Register                                       |    |

|       | ADC Status Register                                    |    |

|       | ADC Data High Register                                 |    |

|       | ADC Data Low Register                                  |    |

|       | Analog Input Data Representation                       |    |

|       | ADC Offset Digital Pot Register                        |    |

|       | ADC Gain Digital Pot Register                          |    |

|       | Access Example                                         |    |

|       | Analog Output Registers                                |    |

|       | Analog Output Gain Digital Pot Registers               |    |

|       | Access Example                                         |    |

|       | Analog Output Shift Register                           |    |

|       | Access Example                                         |    |

|       | Analog Output Data Representation                      |    |

|       | Digital I/O Registers                                  |    |

|       | Port Direction                                         |    |

|       | Register Functions                                     |    |

|       | Digital Output Registers                               |    |

|       | Digital Input Registers                                |    |

|       |                                                        |    |

| Oper  | ation                                                  |    |

|       | Analog Input – Polled Mode                             |    |

|       | Polled Mode Steps                                      |    |

|       | Channel selection.                                     |    |

|       | Trigger A/D conversion                                 |    |

|       | Wait until done                                        |    |

|       | Read data                                              |    |

|       | Analog Input – Interrupt Mode                          |    |

|       | Interrupt Mode Steps                                   |    |

|       | Interrupt Service Routine                              | 50 |

|       | Initialize VCM-DAS-1/2 for interrupt mode              | 50 |

|       | Initialize VCM-DAS-1/2 for Auto-trigger (if desired)   |    |

|       | Initialize interrupt controller                        |    |

|       | Initialize CPU to receive interrupts                   |    |

|       | Channel selection                                      |    |

|       | Initialize VCM-DAS-1/2 for Auto-increment (if desired) | 51 |

|       | Trigger A/D conversion                                 | 51 |

| Analog Output                                | 52 |

|----------------------------------------------|----|

| Route SPI Data to DAC Chip and Clear DACLOAD | 52 |

| Write DAC Data Frame                         |    |

| Execute DACLOAD to Update Analog Output      | 52 |

| Digital I/O                                  | 53 |

| Signal Direction                             | 53 |

| Signal Polarity                              | 53 |

| Digital Input                                | 53 |

| Digital Output                               | 53 |

| System Reset                                 | 54 |

| Calibration                                  | 55 |

| Required equipment                           | 55 |

| Preparation                                  | 55 |

| Isolate Analog Card                          | 55 |

| Jumper Configuration                         | 55 |

| Calibration Utility Program                  | 55 |

| Calibrating Analog Input                     | 56 |

| Analog Input Offset                          | 56 |

| Analog Input Gain                            | 56 |

| Calculate                                    | 56 |

| Calibrating Analog Output                    | 57 |

| Calibrate Analog Output Channel #0           | 57 |

| Calibrate Analog Output Channel #1           |    |

| Save Calibration Values to EEPROM            | 57 |

| Confirmation Of Calibration                  | 57 |

| Reload calibration parameters.               | 57 |

| Check Analog Output Channel #0               | 57 |

| Check Analog Output Channel #1               | 57 |

| Check Analog Input                           | 58 |

| Finishing Up                                 | 58 |

| Annendix A — Schematics                      | 50 |

### **Other References**

- Burr-Brown Corp., (800) 548-6132, http://www.burr-brown.com/ ADS7805 16-Bit A/D Converter

- Analog Devices Inc., (800) 262-5643, http://www.analog.com/ *AD8522 12-Bit D/A Converter AD976 16-Bit A/D Converter (alternate vendor)*

- Integrated Device Technology Inc., (800) 345-7015, http://www.idt.com 74FCT16652T Parallel Port Interface Chip

- PC/104 Consortium, (650) 903-8304, http://www.controlled.com/pc104 *PC/104 Resource Guide*

- VersaLogic Corporation, (800) 824-3163, http://www.versalogic.com Embedded PCI (PC/104-Plus) Specification. Available on web site.

This chapter introduces the VCM-DAS-1/2 Analog and Digital I/O Module, lists its features and specifications, and provides a brief overview of the installation and configuration process.

### **Using This Manual**

Each chapter in this manual corresponds to a step in the installation and operation of the module.

#### Chapter 1 - Overview

Lists basic information, specifications, and system requirements. Use this chapter to familiarize yourself with the module and it's capabilities.

#### Chapter 2 - Configuration

Describes how to jumper the module.

#### Chapter 3 - Installation

Describes how to install the VCM-DAS-1/2. Also provides information on the external connections.

#### Chapter 4 - Registers

Provides programming details and register descriptions.

#### Chapter 5 - Operation

Provides details on how to operate the Analog Input, Analog Output, Digital I/O, Digital Pots, and EEPROM circuits. Some software examples are given.

#### Chapter 6 - Calibration and Diagnostics

Describes the procedure for calibrating the module and running the included diagnostic software.

#### Appendix A - Schematics

Circuit diagrams.

#### Introduction

The VCM-DAS-1/2 module provides 16 single-ended analog input channels, featuring fast 10  $\mu$ s conversion times and  $\pm 5V$  or  $\pm 10V$  input ranges. Throughput up to 200 kHz may be realized with repeat conversions on one channel; up to 67KHz when scanning from channel to channel.

The VCM-DAS-1/2 also includes two 12-bit analog output channels. These channels may be jumpered independently for 0 to 5V or 0 to 10V output at 5 ma each. Digital data is written in a serial fashion to update the analog values.

Digital pots are used for calibrating the analog circuits. A 1K EEPROM is included to store the calibration values, and there is plenty of extra space in the EEPROM for general purpose use. The digital pots must be initialized whenever the computer system is reset.

In addition to the analog sections, the module also includes 16 digital I/O lines. These digital lines feature TTL type outputs with readback, and are compatible with optically isolated modular I/O racks.

#### **Features**

#### **GENERAL**

- +5V and ±12V supplies required

- Uses four electronic digital adjustment pots instead of manual pots

- Digital Pot settings are stored in an on-board 128 x 16 EEPROM

- Compatible with the industry standard 5B series of signal conditioners

#### **ANALOG INPUT**

- 16 channels

- 16-bit input resolution

- Single ended, high impedance inputs

- Electronic digital calibration

- Up to 200K samples/second (VCM-DAS-2), up to 100K samples/second (VCM-DAS-1)

- $\pm 5V$  and  $\pm 10V$  input ranges

- On board timer for periodic readings

- Auto retrigger mode

- Auto Channel Increment Mode

- DMA support

- Compatible with industry standard 5B01 series signal conditioners

#### **ANALOG OUTPUT**

- 2 channels

- 12-bit resolution

- Electronic digital calibration

- 0-5V and 0-10V output range

- 40 μS update time

- Short circuit proof, 5ma output current

#### **DIGITAL I/O**

- Two 8-bit ports

- ±24 ma output drive

- Programmable read-only or read/write

- Opto 22 compatible

- EEPROM storage for user data

### **Technical Specifications**

Specifications are typical at 25°C with 5.0V supply unless otherwise noted.

3.8" x 3.6" (PC/104 standard) 0.6" component height

Storage Temperature:

-40°C to 85°C

#### Free Air Operating Temperature:

0°C to +60°C

Power Requirements: (all digital outputs low [no external load], both analog outputs sourcing or sinking 5 ma ea.)

5V ±5% @ 510 ma typ. ±12V ±5% @ ±20 ma typ.

Analog Input:

Channels:

Resolution: Accuracy:

Input Mode:

Range:

16

16 bits, no missing codes

±0.003% (±3 LSBs)

Single ended

±5V or ±10V (jumper selectable, all channels the same)

10 μS (VCM-DAS-1), 5 μS (VCM-DAS-2)

5 μS (applies only when switching channels)

±35V overvoltage protection Conversion Time: Settling Time:

±35V overvoltage protection >10<sup>10</sup> $\Omega$ , 20 pF Protection:

Impedance:

Programmable 20 μS, 50 μS, 100 μS, 250 μS, 500 μS, or 1 mS Retrigger Timer:

Direct I/O

Analog Output:

Access:

Channels:

Range: 0 to 5V or 0 to 10V (jumper selectable, each channel independent)

Resolution: 12 bits Accuracy: Update Time: ±1.5 LSB <del>4</del>0 μS

Output Drive: 5 ma, 200 pF (each channel)

Bitwise serial Access:

Digital I/O:

Channels: 16 (non-inverting) Input Threshold: TTL compatible

Totem pole output with readback Architecture:

Output Drive (H): Output Drive (L): –24ma @ 2.4V +24ma @ 0.55V

Byte programmable as input or output with readback Short circuit to ground, indefinite duration Signal Direction:

Short Protection:

Access: Direct I/O

**Digital Pots:**

Organization: 4 pots used to calibrate analog section

Resolution: 256 settings

Access: Serial

**EEPROM:**

Organization: Sixty-four 16-bit words

Allocation: Two words used for digital pots, 62 words available for general purpose storage

Access: Bitwise serial

**Bus Interface:**

Occupies 16 ports on any 16-bit address boundary IRQ10, IRQ11, or IRQ12 DMA5, DMA6, or DMA7 I/O Ports:

Interrupt Channel: DMA Channel:

**External Connectors:**

Analog In/Out: Opto 22: 26-pin .1" dual-row header 34-pin .1" dual-row header

Compatibility:

Full compliance, 16-bit data bus PC/104:

Specifications are subject to change without notice.

### **Technical Support**

If you have problems that this manual can't help you solve, contact VersaLogic for technical support at **(800) 824-3163 or (503) 747-2261**. You can also reach VersaLogic by e-mail at Support@versalogic.com.

#### REPAIR SERVICE

If your product requires service, you must obtain a Returned Material Authorization (RMA) number by calling (800) 824-3163. Our standard turn-around time for repairs is five working days after we receive the product.

Please provide the following information:

- Your name, the name of your company, and your phone number

- The name of a technician or engineer who we can contact if we have questions

- Quantity of items being returned

- The model and serial number of each item (the serial number is a 5 digit bar code)

- A description of the problem

- Steps you have taken to resolve or repeat the problem

- The return shipping address

Warranty Repair All charges are covered, including UPS Ground shipping charges for

return back to your facility.

Non-warranty Repair All non-warranty repairs are subject to diagnosis and labor charges,

parts charges, and return shipping fees. We will need to know what shipping method you prefer for return back to your facility, and we will need to secure a purchase order number for invoicing the repair.

**Note!** Please mark the RMA number clearly on the outside of the box before

returning.

### Configuration

This chapter describes how to configure the on-board options for the VCM-DAS-1/2 module. Configuration involves both hardware (jumper) and software configuration. The jumpers set the base address for the module and configure the analog circuitry for various modes of operation. Software configuration completes the process by initializing the analog calibration pots every time the card is reset.

#### Warning!

The VCM-DAS-1/2 module requires +5V, +12V, and -12V for normal operation. These voltages must be supplied through the PC/104 connector. Damage to onboard components will occur if all three voltages are not present at the same time.

### **Hardware Jumper Summary**

Hardware option configuration is accomplished by installing or removing jumper plugs. In this chapter, the term "in" is used to indicate an installed jumper and "out" is used to indicate a removed jumper.

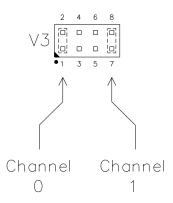

Use the following key to interpret the jumper diagrams used in this manual:

Figure 1. Jumpering Key

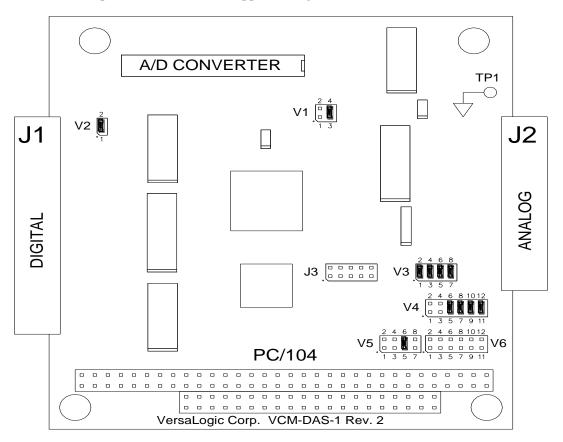

#### **JUMPER BLOCK LOCATIONS**

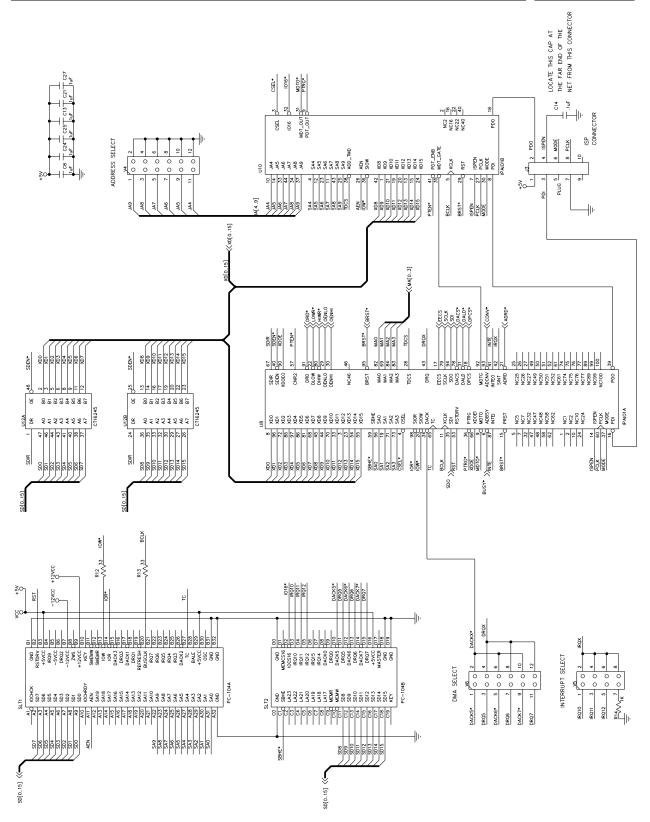

**Note** Jumpers are shown in as-shipped configuration.

Figure 2. Jumper Block Locations

Table 1: Jumper Summary

| Jumper<br>Block               | Description                                                                                                                                                                                                                                                                                                                              | As<br>Shipped | Page |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|

| V1[1-2]                       | Input Voltage Range In — ±5V Input Range Out — ±10V Input Range                                                                                                                                                                                                                                                                          | Out           | 9    |

| V1[3-4]                       | Input Low Pass Filter In — Enabled Out — Disabled                                                                                                                                                                                                                                                                                        | In            | 9    |

| V2                            | Opto 22 I/O Rack Power In — I/O rack power provided by analog board Out — I/O rack power provided externally                                                                                                                                                                                                                             | In            | 13   |

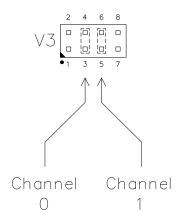

| V3[1-2]                       | Analog Loopback (Channel 0) In — Connects DAC 0 output to ADC 14 input for diagnostic loopback Out — Circuits operate independently                                                                                                                                                                                                      | In            | 11   |

| V3[3-4]                       | Analog Output 0 Voltage Range In — 0 to 10V Out — 0 to 5V                                                                                                                                                                                                                                                                                | In            | 10   |

| V3[5-6]                       | Analog Output 1 Voltage Range In — 0 to 10V Out — 0 to 5V                                                                                                                                                                                                                                                                                | In            | 10   |

| V3[7-8]                       | Analog Loopback (Channel 1) In — Connects DAC 1 output to ADC 15 input for diagnostic loopback Out — Circuits operate independently                                                                                                                                                                                                      | In            | 11   |

| V4                            | Address Select (A4 – A9)  V4[1-2] In – A9 Decoded Low Out – A9 Decoded High V4[3-4] In – A8 Decoded Low Out – A8 Decoded High V4[5-6] In – A7 Decoded Low Out – A7 Decoded High V4[7-8] In – A6 Decoded Low Out – A6 Decoded High V4[9-10] In – A5 Decoded Low Out – A5 Decoded High V4[11-12] In – A4 Decoded Low Out – A4 Decoded High | 300h          | 8    |

| V5[1-2]<br>V5[3-4]<br>V5[5-6] | Interrupt Request Select  IRQ 10  IRQ 11  IRQ 12  2 4 6  2 4 6  2 4 6                                                                                                                                                                                                                                                                    | IRQ 12        | 14   |

| V5[7-8]                       | Shared Interrupt Configuration In — Shared interrupts Out — Normal interrupts                                                                                                                                                                                                                                                            | Out           |      |

| V6                            | DMA Channel Select  DMA 5  DMA 6  DMA 7  2 4 6 8 10 12  2 4 6 8 10 12  2 4 6 8 10 12  3 5 7 9 11  0 1 3 5 7 9 11                                                                                                                                                                                                                         | None          | 16   |

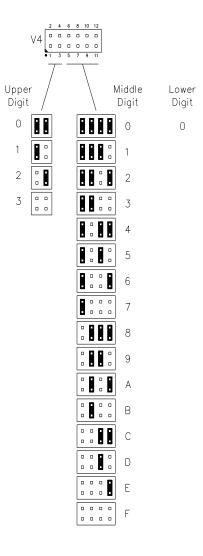

### **Module Addressing**

As shipped, the module is configured for a base address of 300h. The card occupies 16 consecutive I/O addresses (0300h to 030Fh). Ten of these addresses are mapped to control, data, and status registers. The remaining six addresses occupy positions in I/O space, but are not assigned to registers. See the Registers description section on page 23 for further register information.

The base address can range from 000h to 3F0h on any 10h address boundary. Use the table below to select the jumpering for the appropriate upper and middle hex digits of the three digit base address (i.e., "1" and "4" = 140h).

**Note** The lower digit is always "0".

Figure 3. Jumper Block Locations

### **Analog Input Configuration**

#### INPUT RANGE

The module may be operated with an input range of  $\pm 5$  volts or  $\pm 10$  volts. To achieve the maximum digital resolution and to prevent saturation, the range which most closely matches the input signal should be chosen. All channels operate with the same input range.

As shipped, the board is configured for  $\pm 5$  volt input.

**Table 2: Input Range Jumper**

| Jumper<br>Block | Description                                                     | As<br>Shipped |

|-----------------|-----------------------------------------------------------------|---------------|

| V1[1-2]         | Input Voltage Range In — ±5V Input Range Out — ±10V Input Range | Out           |

#### **Low Pass Filter**

A 1 MHz low pass filter between the instrumentation amplifier and the A/D converter can be selected to reject high frequency noise.

**Table 3: Low Pass Filter Jumper**

| Jumper<br>Block | Description                                       | As<br>Shipped |

|-----------------|---------------------------------------------------|---------------|

| V1[3-4]         | Input Low Pass Filter In — Enabled Out — Disabled | In            |

### **Analog Output Configuration**

The VCM-DAS-1/2 module features two unipolar analog output channels. Both channels are single-ended and are referenced to analog ground. The digital data format is straight binary.

#### **OUTPUT RANGE**

Each output channel can be configured independently to produce a unipolar output voltage range of 0-5 volts or 0-10 volts as shown below.

**Table 4: Output Range Jumpers**

| Jumper<br>Block | Description                                                         | As<br>Shipped |

|-----------------|---------------------------------------------------------------------|---------------|

| V3[3-4]         | Analog Output Voltage Range (Channel 0) In — 0 to 10V Out — 0 to 5V | In            |

| V3[5-6]         | Analog Output Voltage Range (Channel 1) In — 0 to 10V Out — 0 to 5V | In            |

#### **ANALOG LOOPBACK**

The two output channels can be connected (looped back) to two input channels for a direct readback of the voltage, or to provide analog output to a 5B01 signal conditioning rack. Analog loopback is also useful for diagnostic and calibration purposes.

**Table 5: Analog Loopback Jumpers**

| Jumper<br>Block | Description                                                                                                                          | As<br>Shipped |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------|

| V3[1-2]         | Analog Loopback (Channel 0)  In — Connects DAC 0 output to ADC 14 input for diagnostic loopback Out — Circuits operate independently | In            |

| V3[7-8]         | Analog Loopback (Channel 1) In — Connects DAC 1 output to ADC 15 input for diagnostic loopback Out — Circuits operate independently  | In            |

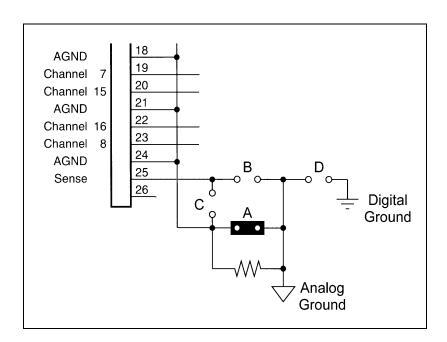

### **5B01 Analog Signal Conditioning Rack**

When using a 5B01 series analog signal conditioning rack, the input range should be set to  $\pm 5$ V. If output channels are used, the Analog Loopback jumpers must be inserted and the output range configured for  $\pm 5$ V operation.

#### Note:

It is important to configure your 5B01 signal conditioning rack so that analog ground on the rack is connected to the eight analog ground signals on the interface connector. Most racks include a jumper or cutable trace for this purpose, which must be installed (shown as "A" below).

To prevent ground loops, it is important that analog and digital grounds be connected together at only one point in the system. The VCM-DAS-1/2 brings these grounds together on the module circuitry itself, therefore any external connections between the two ground systems must be avoided. Most racks include a jumper or cutable trace that must be removed (shown as "D" below).

#### Warning!

To prevent analog output channel 0 from shorting to ground, it is very important to properly configure your 5B01 signal conditioning rack so that pin 25 is disconnected. Most racks include jumpers or cuttable traces that must be removed to leave pin 25 floating (shown as "B" and "C" below).

Figure 4. 5B01 Analog Signal Conditioning Rack

### **Digital Input/Output Configuration**

The VCM-DAS-1/2 has 16 digital I/O lines that can be programmed in groups of eight as inputs or outputs with readback. The I/O connector is compatible with 8 and 16 position modular I/O racks.

#### **RACK POWER CONTROL**

The VCM-DAS-1/2 module includes provisions for powering the external I/O rack assembly with +5 volts at 500 ma.

When jumper V2 is installed, the I/O rack power line (I/O rack pin 49) is connected directly to +5 volts on the PC/104 Bus. If the I/O rack is powered by a separate external supply, either a jumper from the I/O rack or the V2 jumper must be removed.

#### Warning!

The +5 volt power output from the VCM-DAS-1/2 card can be shorted to ground if the connector is not correctly oriented at either end of the interface cable. The use of keys in the connectors, or very clear markings on the connectors, is recommended to prevent backwards connection of the cable.

**Table 6: Opto 22 Rack Power Jumper**

| Jumper<br>Block | Description                                                                                                  | As<br>Shipped |

|-----------------|--------------------------------------------------------------------------------------------------------------|---------------|

| V2              | Opto 22 I/O Rack Power In — I/O rack power provided by analog board Out — I/O rack power provided externally | In            |

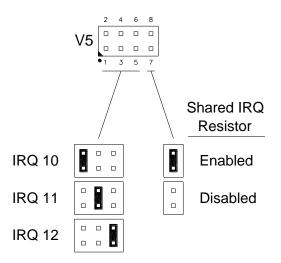

### **Interrupt Configuration**

#### **IRQ SELECTION**

Jumper V5 connects the interrupt request signal (analog input conversion complete) to one of three PC/104 Bus interrupt request lines. The choice of which jumper position to choose depends upon the capabilities of the CPU or interrupt controller used in the system.

**Table 7: Interrupt Request Jumpers**

| Jumper<br>Block    | Description                |                          |                        | As<br>Shipped |

|--------------------|----------------------------|--------------------------|------------------------|---------------|

| V5[1-2]            | Interrupt Request          | Select                   |                        | IRQ 12        |

| V5[3-4]<br>V5[5-6] | IRQ 10 2 4 6 1 0 0 0 1 3 5 | IRQ 11 2 4 6 0 0 0 1 3 5 | IRQ 12 2 4 6 0 0 0 0 0 |               |

#### **SHARED INTERRUPT CONFIGURATION**

Jumper V5[7-8] inserts a  $1K\Omega$  pull-down resistor into the IRQ circuit for applications using shared IRQs.

**Table 8: Shared Interrupt Jumper**

| Jumper<br>Block | Description                                                                   | As<br>Shipped |

|-----------------|-------------------------------------------------------------------------------|---------------|

| V5[7-8]         | Shared Interrupt Configuration In — Shared interrupts Out — Normal interrupts | Out           |

#### **ABOUT SHARED INTERRUPTS**

#### **REGULAR INTERRUPTS**

- Sources are totem-pole drivers

- Interrupt controller is set to edge trigger mode

- Interrupts are requested by driving the IRQ line from low-to-high (positive edge triggering)

- The CPU has a 4.7K pull-up resistor on each IRQ line to prevent stray interrupts on unused inputs. Unused IRQ lines assume a high state.

- Only one interrupt source per IRQ line

- The IRQ line can be left in a high or low state when not requesting interrupts. It is common practice, however, to leave the line in the low state.

- A new interrupt is requested by lowering the IRQ line and raising it again

#### SHARED INTERRUPTS

- Sources are tri-statable, totem-pole drivers with the input tied high

- Interrupt controller is set to level trigger mode

- The CPU has a 4.7K pull-up resistor on each IRQ line to prevent stray interrupts on unused inputs. Unused IRQ lines assume a high state.

- Each source has a 1K pull-down resistor tied to the IRQ line through a series jumper. Only one shared device per IRQ line should have the jumper installed. The pull-down resistor fights against the 4.7K pull-up resistor on the CPU, but the 1K wins, causing the IRQ line to assume a low state.

- Interrupts are requested by enabling the tri-state driver. This drives the IRQ line from low-to-high.

- The source must work against the pull-down resistor

- Multiple sources are allowed per IRQ line. Software must distinguish which device made the interrupt request by polling the hardware within the Interrupt Service Routine.

- When not requesting an interrupt, the tri-statable driver must be disabled. This leaves the IRQ line in a low state, allowing other sources on the same IRQ line to make requests of their own.

### **DMA Configuration**

The VCM-DAS-1/2 can be setup to generate a DMA transfer request upon analog input conversion complete. These requests can be routed to DMA channel 5, 6, or 7 depending upon the configuration of jumper V6.

**Table 9: DMA Channel Selection Jumpers**

| Jumper<br>Block | Description                                |                                                        |                                                        | As<br>Shipped |

|-----------------|--------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------|

| V6              | DMA Channel Sel                            | ect                                                    |                                                        | None          |

|                 | DMA 5                                      | DMA 6                                                  | DMA 7                                                  |               |

|                 | 2 4 6 8 10 12<br>1 0 0 0 0<br>1 3 5 7 9 11 | 2 4 6 8 10 12<br>0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 2 4 6 8 10 12<br>0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |               |

### Handling

After removing the module from its protective wrapper, place the module on a grounded, staticfree surface, component side up. Use an anti-static foam pad if available. Do not slide the board over any surface.

The module should also be protected during shipment or storage with anti-static foam and conductive bubble wrap.

#### Warning!

The VCM-DAS-1/2 is designed for reliability, however, electrostatic discharge (ESD) can damage on-board components. When handling the module, standard ESD procedures should be observed. If an ESD station is not available, you can provide some ESD protection by wearing a grounded antistatic wrist strap.

### **Arranging the PC/104 Stack**

- 1. Turn the system power off. Installing or removing modules from the PC/104 stack while the power is on may damage the system.

- 2. The VCM-DAS-1/2 module can occupy any stack position, however, if the stack contains PC/104-Plus modules, the VCM-DAS-1/2 module should be plugged on top of these cards.

- 3. Additional stack-through modules can be stacked on top of the VCM-DAS-1/2. Up to six PC/104 modules can be added. If a non-stack-through module is used, it must be topmost module on the stack.

### Signal Levels

Connector J1 is the digital input/output connector. Each circuit is a tri-statable totem-poll TTL driver with a 10K ohm pull up resistor to +5V. Input gates are attached to each output signal for read-back. Signal direction is determined by the DIRHI and DIRLO bits in the CONTROL register. External equipment attached to connector J1 must be able to sink 500 µA @ 5V per channel. The maximum non-destructive input voltage applied to any channel is +5V.

Connector J2 is the analog input and output connector. All analog input signals are single ended analog level signals measured with respect to analog ground. The maximum non-destructive input voltage applied to any of the inputs is ±16.5V. Each analog channel presents a minimum input impedance of 16K ohms.

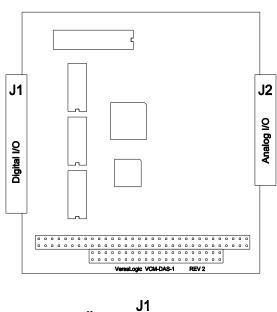

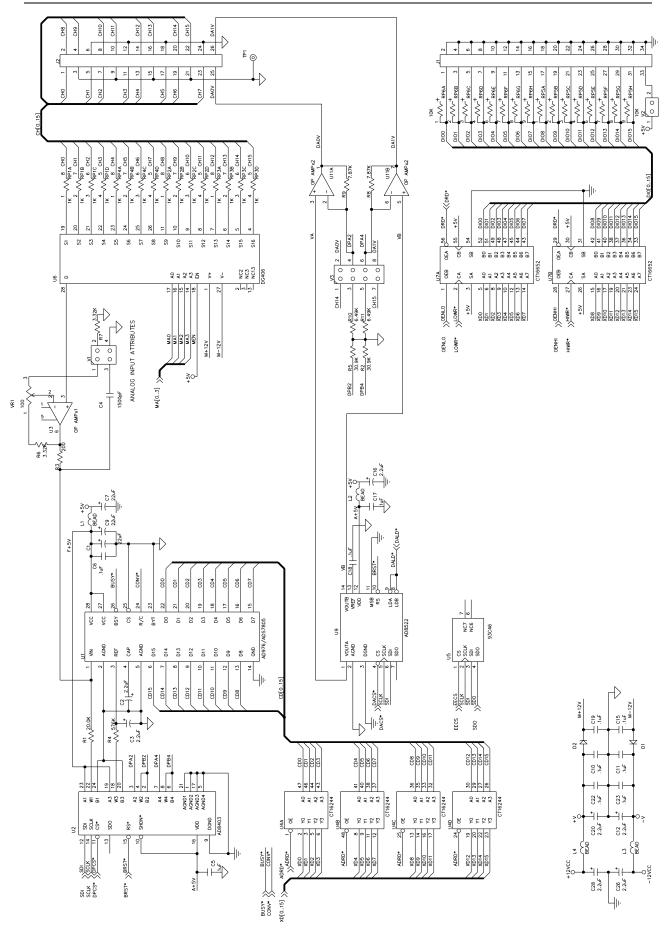

### **External Connectors**

#### **CONNECTOR FUNCTIONS**

**Table 10: Connector Functions**

| Connector | Function              |

|-----------|-----------------------|

| J1        | Digital I/O Connector |

| J2        | Analog I/O Connector  |

#### **CONNECTOR LOCATIONS**

Figure 5. Connector Locations

#### MATING CONNECTORS AND CABLE ASSEMBLIES

Connections to the VCM-DAS-1/2 can be made using 0.05" pitch flat ribbon cable with 0.1" mass-terminated mating connectors. One cable for J2 is available from VersaLogic for development work, however, you will probably want to make your own custom cable to more closely match the requirements of your embedded computer project.

**Table 11: Mating Connectors and Cable Assemblies**

| Connector           | Mating<br>Connector                                              |

|---------------------|------------------------------------------------------------------|

| J1<br>(Digital I/O) | Std. 34-pin 0.1 in. IDC<br>header, 3M 3414-6634 or<br>equivalent |

| J2<br>(Analog I/O)  | Std. 26-pin 0.1 in. IDC<br>header, 3M 3399-6626 or<br>equivalent |

#### J1 - DIGITAL I/O CONNECTOR

**Table 12: Digital I/O Connector Pinout**

| 14       | 0:                      | 0( - 00                  |

|----------|-------------------------|--------------------------|

| J1       | Signal                  | Opto 22                  |

| Pin      | Name                    | Function                 |

| 1        | DIO0                    | MOD15*                   |

| 2        | Digital Ground          | Digital Ground           |

| 3        | DIO1                    | MOD14*                   |

| 4        | Digital Ground          | Digital Ground           |

| 5        | DIO2                    | MOD13*                   |

| 6        | Digital Ground          | Digital Ground           |

| 7        | DIO3                    | MOD12*                   |

| 8        | Digital Ground          | Digital Ground           |

| 9        | DIO4                    | MOD11*                   |

| 10<br>11 | Digital Ground<br>DIO5  | Digital Ground<br>MOD10* |

| 12       | Digital Ground          | Digital Ground           |

| 13       | Digital Ground<br>DIO6  | MOD9*                    |

| 14       | Digital Ground          | Digital Ground           |

| 15       | DIO7                    | MOD8*                    |

| 16       | Digital Ground          | Digital Ground           |

| 17       | DIO8                    | MOD7*                    |

| 18       | Digital Ground          | Digital Ground           |

| 19       | DIO9                    | MOD6*                    |

| 20       | Digital Ground          | Digital Ground           |

| 21       | DIO10                   | MOD5*                    |

| 22       | Digital Ground          | Digital Ground           |

| 23<br>24 | DIO11                   | MOD4*                    |

| 24<br>25 | Digital Ground<br>DIO12 | Digital Ground<br>MOD3*  |

| 26       | Digital Ground          | Digital Ground           |

| 27       | DIO13                   | MOD2*                    |

| 28       | Digital Ground          | Digital Ground           |

| 29       | DIO14                   | MOD1*                    |

| 30       | Digital Ground          | Digital Ground           |

| 31       | DIO15                   | MOD0*                    |

| 32       | Digital Ground          | Digital Ground           |

| 33       | Power                   | Power                    |

| 34       | Digital Ground          | Digital Ground           |

**MOD0\* – MOD15\*.** Opto 22 bi-directional interface signals. Each signal consists of a tristatable totem-poll TTL driver with a  $10K\Omega$  pull up resistor to +5V. Input gates are attached to each output signal for read-back. Signal direction is determined by the DIRHI and DIRLO bits in the CONTROL register.

**Power.** +5V power output. When jumper V5 is installed, up to 500 mA can be drawn from this +5V output to power the Opto 22 interface rack or other external equipment. If the I/O rack is powered by a separate external supply, the power jumper on the I/O rack or the V2 jumper must be removed. See page 13 for further information.

**Digital Ground.** All signals on connector J1 are referenced to these digital ground connections. The use of all ground connections is recommended to maintain a high degree of signal integrity.

#### J2 - ANALOG I/O CONNECTOR

Table 13: Analog I/O Connector Pinout

| J2  | Signal     |                  |

|-----|------------|------------------|

| Pin | Name       | Function         |

| 1   | CH0        |                  |

| 2   | CH8        | Channel 0 Input  |

| 3   | AGND       | Channel 8 Input  |

| 4   | CH9        | Analog Ground    |

| 5   | CH9<br>CH1 | Channel 9 Input  |

| 6   |            | Channel 1 Input  |

|     | AGND       | Analog Ground    |

| 7   | CH2        | Channel 2 Input  |

| 8   | CH10       | Channel 10 Input |

| 9   | AGND       | Analog Ground    |

| 10  | CH11       | Channel 11 Input |

| 11  | CH3        | Channel 3 Input  |

| 12  | AGND       | Analog Ground    |

| 13  | CH4        | Channel 4 Input  |

| 14  | CH12       | Channel 12 Input |

| 15  | AGND       | Analog Ground    |

| 16  | CH13       | Channel 13 Input |

| 17  | CH5        | Channel 5 Input  |

| 18  | AGND       | Analog Ground    |

| 19  | CH6        | Channel 6 Input  |

| 20  | CH14       | Channel 14 Input |

| 21  | AGND       | Analog Ground    |

| 22  | CH15       | Channel 15 Input |

| 23  | CH7        | Channel 7 Input  |

| 24  | AGND       | Analog Ground    |

| 25  | DA0V       | Channel 0 Output |

| 26  | DA1V       | Channel 1 Output |

**Channel 0 to 15 Input.** Analog voltages are applied to these inputs for A/D conversion. All inputs are single-ended, and are referenced to Analog Ground.

**Analog Ground.** This signal is the on-board analog ground. All signals on J2 are referenced to this signal. The use of multiple Analog Ground signals is recommended to maintain a high degree of signal integrity.

**Channel 0 & 1 Output.** Analog voltage outputs referenced to analog ground. Each signal can source or sink up to 5 mA.

### Introduction

This section includes information about registers, control and status bits, and data formats. It focuses primarily on the individual registers, the bits contained within them, and their functional descriptions. The VCM-DAS-1/2 contains two different sets of registers, those that occupy standard I/O ports, and those that are part of an on-board Serial Peripheral Interface (SPI) bus. Devices on the SPI bus include both analog output channels, the EEPROM, and four digital calibration pots.

### I/O Port Mapping

The VCM-DAS-1/2 occupies 16 ports in the I/O map. Ten I/O ports are mapped to functional registers, the remaining six I/O ports are decoded by the board, and cannot be used by other PC/104 Modules.

Write I/O Port As Shipped Read Register Register **Address Address** Board Address + 15 030Fh Board Address + 14 030Eh Board Address + 13 030Dh Board Address + 12 030Ch Board Address + 11 030Bh Board Address + 10 030Ah **SPIWDAT** Board Address + 9 0309h **SPIRDAT SPISEL** Board Address + 8 0308h **PARWHI PARRHI** Board Address + 7 0307h **PARWLO PARRLO** Board Address + 6 0306h **ADCHI** Board Address + 5 0305h **ADCLO** Board Address + 4 0304h **ADCPTR** Board Address + 3 0303h **ADCCVT** Board Address + 2 0302h

Board Address + 1

Board Address + 0

0301h

0300h

Table 14: I/O Port Addresses

**ADCSEL**

CONTROL

**ADCSTAT**

#### I/O PORT REGISTER FUNCTIONS

The following table lists the functions assigned to each read and write I/O port register.

**Table 15: Register Functions**

| Write    |                                                                                     |      |

|----------|-------------------------------------------------------------------------------------|------|

| Register | Description                                                                         | Page |

| SPIWDAT  | Write Data to Analog Output Channels, Digital Pots, and EEPROM                      | 27   |

| SPISEL   | Serial Peripheral Interface (SPI) Chip Select<br>Register and DAC Load              | 28   |

| PARWHI   | Parallel Port Data High (Opto 22 Modules 0-7)                                       | 47   |

| PARWLO   | Parallel Port Data Low (Opto 22 Modules 8-15)                                       | 47   |

| ADCPTR   | Analog Input Periodic Trigger Rate                                                  | 30   |

| ADCCVT   | Triggers Analog Input Conversion, Clears Done<br>Bit                                | 31   |

| ADCSEL   | Analog Input Channel Select, Scan Range Limit                                       | 32   |

| CONTROL  | Analog Input Interrupt, DMA, Trigger Modes, Auto Increment, Parallel Port Direction | 34   |

| Read<br>Register | Description                                   | Page |

|------------------|-----------------------------------------------|------|

| SPIRDAT          | Read Data from EEPROM                         | _    |

| PARWHI           | Parallel Port Data High (Opto 22 Modules 0-7) | 47   |

| PARWLO           | Parallel Port Data Low (Opto 22 Modules 8-15) | 47   |

| ADCHI            | Analog Input High Data Byte                   | 37   |

| ADCLO            | Analog Input Low Data Byte                    | 38   |

| ADCSTAT          | A/D Busy, A/D Done                            | 36   |

### **Serial Port Interface (SPI) Register Functions**

The following table lists the functions assigned to each register accessible through the Serial Port Interface (SPI). These registers are accessed in a serial fashion by manipulating the SPIWDAT, SPISEL, and SPIRDAT registers.

**Table 16: Register Functions**

| Write    |                                                            |               |

|----------|------------------------------------------------------------|---------------|

| Register | Description                                                |               |

| ADOFSET  | Analog Input Offset Digital Pot                            | (DPOT#1)      |

| DA0GAIN  | Analog Output Channel 0 Gain Digital Pot                   | (DPOT#2)      |

| ADGAIN   | Analog Input Gain Digital Pot                              | (DPOT#3)      |

| DA1GAIN  | Analog Output Channel 1 Gain Digital Pot                   | (DPOT#4)      |

| DA0DATA  | Analog Output Channel 0 Data Register                      |               |

| DA1DATA  | Analog Output Channel 1 Data Register                      |               |

| WDATA    | Data to be stored in EEPROM                                |               |

| ADDRESS  | EEPROM address                                             |               |

| OPCODE   | Operation code used to specify EEPROM reactions functions. | d, write, and |

| Read<br>Register | Description           |

|------------------|-----------------------|

| RDATA            | Data read from EEPROM |

#### **SPI READ DATA REGISTER**

#### SPIRDAT (READ) 0309h

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

|----|----|----|----|----|----|----|-------|

| _  | _  | _  | _  | _  | -  | -  | RDATA |

This register is used to read data from the serial EEPROM. Operational details regarding the serial EEPROM chip exceed the scope of this manual. The user is encouraged to use the C/C++ software functions provided with the VCM-DAS-1/2 to access EEPROM contents.

**Table 17: SPIRDAT Bit Assignments**

| Bit   | Mnemonic | Description                                                                                                                                                                            |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-D1 | _        | Unused — These bits have no function.                                                                                                                                                  |

| D0    | RDATA    | Read Data — Serial read data from the SPI. Data read from this bit returns stored information from the EEPROM. In certain modes, this bit is also used to indicate EEPROM busy status. |

#### **SPI W**RITE DATA REGISTER

#### SPIWDAT (WRITE) 0309h

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

|----|----|----|----|----|----|----|-------|

| _  | _  | _  | _  | _  | -  | _  | WDATA |

This register is used to write data to the various devices on the serial peripheral interface. Each device contains a shift register which receives data written to the WDATA bit. You must first select which chip is to receive the data by writing to the SPISEL register.

**Table 18: SPIWDAT Bit Assignments**

| Bit   | Mnemonic | Description                                                                                                                        |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| D7-D1 | _        | Unused — These bits have no function.                                                                                              |

| D0    | WDATA    | Write Data — Serial write data to the SPI. Data written to this bit is clocked into the shift register of the selected SPI device. |

#### **SPI SELECT REGISTER**

#### SPISEL (WRITE) 0308H

| D7 | D6 | D5 | D4 | D3      | D2    | D1      | D0     |

|----|----|----|----|---------|-------|---------|--------|

| _  | _  | _  | _  | DACLOAD | EESEL | DPOTSEL | DACSEL |

This register is used to select which device on the serial peripheral interface (SPI) bus should receive data written to the SPIWDAT register. Bit D3 (DACLOAD) is used to transfer the contents of the analog output shift register(s) to the A/D converter(s), causing an output voltage update.

**Table 19: SPISEL Bit Assignments**

| Bit   | Mnemonic | Description                                                                                                                                                                                        |                                                                                                                                                                                                                       |  |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D7-D4 | _        | Unused — These bits have no function.                                                                                                                                                              |                                                                                                                                                                                                                       |  |

| D3    | DACLOAD  | Analog Output Data Load — This control bit is used to transfer the analog output data from the DAC shift register to the D/A converters. Data is transferred on the 0 to 1 transition of this bit. |                                                                                                                                                                                                                       |  |

|       |          | DACLOAD = 0 Both analog output channels remain stable.                                                                                                                                             |                                                                                                                                                                                                                       |  |

|       |          | DACLOAD = 1                                                                                                                                                                                        | The Analog Output Data stored in the Analog Output Shift Register (DACSR) is transferred to the appropriate D/A converter(s) as determined by the A and B bits in DACSR. Output voltage change(s) occurs immediately. |  |

|       |          | <b>NOTE:</b> The update occurs when DACLOAD changes from 0 to 1. DACLOAD should be reset to "0" prior to loading new data into the DACSR register.                                                 |                                                                                                                                                                                                                       |  |

| D2    | EESEL    | <b>EEPROM Chip Select</b> — This control bit selects the EEPROM chip for serial data transfer.                                                                                                     |                                                                                                                                                                                                                       |  |

|       |          | EESEL = 0 EEPROM chip ignores the serial data interface.                                                                                                                                           |                                                                                                                                                                                                                       |  |

|       |          | EESEL = 1                                                                                                                                                                                          | EEPROM chip responds to serial data interface reads and writes.                                                                                                                                                       |  |

| D1    | DPOTSEL  | <b>Digital Pot Chip Select</b> — This control bit selects the digital pot chi for serial data transfer.                                                                                            |                                                                                                                                                                                                                       |  |

|       |          | DPOTSEL = 0                                                                                                                                                                                        | Digital pot chip ignores the serial data interface.                                                                                                                                                                   |  |

|       |          | DPOTSEL = 1                                                                                                                                                                                        | Digital pot chip responds to serial data interface reads and writes.                                                                                                                                                  |  |

| D0    | DACSEL   | Analog Output Chip Select — This control bit selects the analog output chip for serial data transfer.                                                                                              |                                                                                                                                                                                                                       |  |

|       |          | DACSEL = 0                                                                                                                                                                                         | Analog output chip ignores the serial data interface                                                                                                                                                                  |  |

|       |          | DACSEL = 1                                                                                                                                                                                         | Analog output chip responds to serial data interface writes.                                                                                                                                                          |  |

### **Analog Input Registers**

The following table lists the functions assigned to each analog input read and write register.

**Table 20: Register Functions**

| Write<br>Register | Description                                                                         | Page |

|-------------------|-------------------------------------------------------------------------------------|------|

| ADCPTR            | Analog Input Periodic Trigger Rate                                                  | 30   |

| ADCCVT            | Triggers Analog Input Conversion, Clears Done Bit                                   | 31   |

| ADCSEL            | Analog Input Channel Select, Scan Range Limit                                       | 32   |

| CONTROL           | Analog Input Interrupt, DMA, Trigger Modes, Auto Increment, Parallel Port Direction | 34   |

| Read<br>Register | Description           | Page |

|------------------|-----------------------|------|

| ADCHI            | Analog High Data Byte | 37   |

| ADCLO            | Analog Low Data Byte  | 38   |

| ADCSTAT          | A/D Busy, A/D Done    | 36   |

#### **ADC PERIODIC TRIGGER RATE REGISTER**

## ADCPTR (WRITE) 0303H

| D7 | D6 | D5 | D4 | D3 | D2  | D1  | D0  |

|----|----|----|----|----|-----|-----|-----|

| _  | _  | _  | _  | _  | TR2 | TR1 | TR0 |

This register specifies the periodic trigger rate for applications which need analog input conversions at predetermined intervals.

**Table 21: ADCPTR Bit Assignments**

| Bit   | Mnemonic | Descr  | iption                                | l        |                 |                                                                         |  |  |

|-------|----------|--------|---------------------------------------|----------|-----------------|-------------------------------------------------------------------------|--|--|

| D7-D3 | _        | Unuse  | Unused — These bits have no function. |          |                 |                                                                         |  |  |

| D2-D0 | TR2-TR0  | Trigge | er Rat                                | e — Th   | ese bits set th | ne periodic trigger rate.                                               |  |  |

|       |          | TR2    | TR1                                   | TR0      | Counts          | Triggering Rate                                                         |  |  |

|       |          | 0      | 0                                     | 0        | 128             | 15.3 Microseconds                                                       |  |  |

|       |          | 0      | 0                                     | 1        | 256             | 30.4 Microseconds                                                       |  |  |

|       |          | 0      | 1                                     | 0        | 512             | 60.9 Microseconds                                                       |  |  |

|       |          | 0      | 1                                     | 1        | 1024            | 122.2 Microseconds                                                      |  |  |

|       |          | 1      | 0                                     | 0        | 2048            | 244.5 Microseconds                                                      |  |  |

|       |          | 1      | 0                                     | 1        | 4096            | 491.5 Microseconds                                                      |  |  |

|       |          | 1      | 1                                     | 0        | 8192            | 982.9 Microseconds                                                      |  |  |

|       |          |        | (whic                                 | h are su |                 | ermined by counting PC/104 bus<br>CPU). The times given above are<br>k. |  |  |

#### **ADC CONVERT REGISTER**

#### ADCCVT (WRITE) 0302H

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

|----|----|----|----|----|----|----|-----|

| _  | _  | _  | _  | _  | _  | _  | CMD |

The ADCCVT register is a write register which is used to trigger an A/D conversion under software control.

Note:

A word-wide output instruction to the ADCSEL register (out dx,ax) also writes into the ADCCVT register causing channel addressing and triggering with one CPU instruction.

**Table 22: ADCCVT Bit Assignments**

| Bit   | Mnemonic | Description                                   |                                                                                                                                                                                                                                                                                                                        |  |  |

|-------|----------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D7-D1 | _        | Unused — Th                                   | ese bits have no function.                                                                                                                                                                                                                                                                                             |  |  |

| D0    | CMD      | Command — This control bit has two functions. |                                                                                                                                                                                                                                                                                                                        |  |  |

|       |          | CMD = 0                                       | Clears the BUSY bit in the ADCSTAT register and cancels the interrupt request signal. Normally this is a seldom used function because reading data from the ADCHI register performs these actions. The most common use of this command is to remove the interrupt request signal when operating the board in DMA mode. |  |  |

|       |          | CMD = 1                                       | Triggers (starts) an A/D conversion. Writing a 1 to this bit causes an A/D conversion to start. It is not necessary to write a 0 before triggering the next conversion.                                                                                                                                                |  |  |

|       |          | Note:                                         | Proper operation dictates that A/D conversions should only be triggered when the A/D converter is idle (i.e., the BUSY bit in the ADCSTAT register = 0). Retriggering a conversion while one is underway is not recommended.                                                                                           |  |  |

#### **ADC SELECT REGISTER**

## ADCSEL (WRITE) 0301H

| D7 | D6 | D5  | D4  | D3   | D2   | D1   | D0   |

|----|----|-----|-----|------|------|------|------|

| _  | _  | SL1 | SL0 | SEL3 | SEL2 | SEL1 | SEL0 |

This register is used to select the analog channel to use for A/D conversion. It is also used to limit the number of scanned channels in auto-increment mode.

**Table 23: ADCSEL Bit Assignments**

| Bit   | Mnemonic | Descr                                                                                                                                                                                                                                                                                                                           | Description        |                                                                                                                                                                           |  |  |  |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D7-D6 | _        | Unuse                                                                                                                                                                                                                                                                                                                           | ed — T             | hese bits have no function.                                                                                                                                               |  |  |  |

| D5-D4 | SL1-SL0  | Scan Range Limit — These two bits define and restrict the number of channels scanned in auto-increment mode. This allows for faster throughput when fewer than 16 analog inputs are used. A board reset selects (00) so that applications which do not use auto-increment mode are not restricted to a limited set of channels. |                    |                                                                                                                                                                           |  |  |  |

|       |          | SL1                                                                                                                                                                                                                                                                                                                             | SL1 SL0 Scan Range |                                                                                                                                                                           |  |  |  |

|       |          | 0                                                                                                                                                                                                                                                                                                                               | 0                  | <b>Channels 0 to 15</b> – This selection does not restrict the number of channels accessed in auto-increment mode. Allows access to all channels.                         |  |  |  |

|       |          | 0                                                                                                                                                                                                                                                                                                                               | 1                  | Channels 0 to 3 – This selection causes the first four channels to be accessed in auto-increment mode. Channels 0 through 3 are accessed in sequence, and then repeated.  |  |  |  |

|       |          | 1                                                                                                                                                                                                                                                                                                                               | 0                  | Channels 0 to 7 – This selection causes the first eight channels to be accessed in auto-increment mode. Channels 0 through 7 are accessed in sequence, and then repeated. |  |  |  |

|       |          | 1                                                                                                                                                                                                                                                                                                                               | 1                  | Unused – This combination is invalid.                                                                                                                                     |  |  |  |

Table 23: ADCSEL Bit Assignments (cont.)

| Description |                                                                                                 |                                                                                                                  |                                                                                                                                                                                                           |

|-------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| conversion. | ln auto-ii                                                                                      | ncrement                                                                                                         | s select the analog channel to use for A/D mode, the channel address changes all other cases the channel remains                                                                                          |

| SEL3 SEL    | 2 SEL1                                                                                          | SEL0                                                                                                             | Selected Channel                                                                                                                                                                                          |

| number stor | ed in this                                                                                      | s register.                                                                                                      | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 t bits in the Control register affect the A settling delay of approximately 5 never this register changes.                                                          |

|             | Channel Se conversion. I after each A static.  SEL3 SEL3  0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 | conversion. In auto-in after each A/D conversions static.  SEL3 SEL2 SEL1  0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | Channel Select — These bits conversion. In auto-increment after each A/D conversion. In static.  SEL3 SEL2 SEL1 SEL0  0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 1 1 |

#### **CONTROL REGISTER**

## CONTROL (WRITE) 0300H

| D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DIRHI | DIRLO | DMAEN | AINCR | ATRIG | PTRIG | SHARE | INTEN |

This register is used to set various operating modes of the VCM-DAS-1/2. A board reset sets this register to 00h.

**Table 24: CONTROL Bit Assignments**

| Bit | Mnemonic | Description           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | DIRHI    |                       | <b>Direction</b> — This bit controls the direction of the upper IIel I/O port (DIO8–DIO15).                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |          | DIRHI = 0             | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |          | DIRHI = 1             | Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D6  | DIRLO    |                       | <b>Direction</b> — This bit controls the direction of the lower llel I/O port (DIO0–DIO7).                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          | DIRLO = 0             | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |          | DIRLO = 1             | Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D5  | DMAEN    | Direct Memory<br>DMA. | / Access Enable — Enables or disables analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                |