# **DCM™ DC-DC Converter**

# DCM2322x72S26A0y6z

# Isolated, Regulated DC Converter

## **Features & Benefits**

- · Isolated, regulated DC-DC converter

- Up to 100 W, 4.20 A continuous

- 90.0% peak efficiency

- 443 W/in<sup>3</sup> Power density

- Wide input range 14 72 Vdc

- Safety Extra Low Voltage (SELV) 24.0 V Nominal Output

- 3000 Vdc isolation

- ZVS high frequency switching

- Enables low-profile, high-density filtering

- Dual modes of operation:

- Array mode

- Up to 8 units 800 W

- No power derating needed

- Sharing strategy permits dissimilar line voltages across an array

- Enhanced V<sub>OUT</sub> regulation mode

- Standalone: 100 W

- Fully operational current limit

- · OV, OC, UV, short circuit and thermal protection

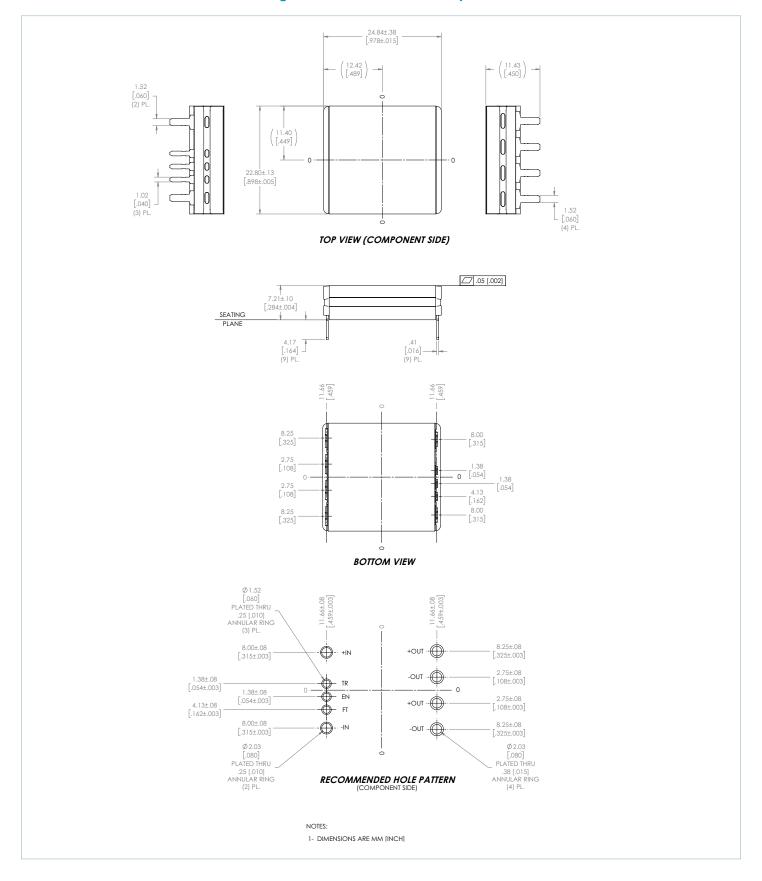

- 2322 through-hole ChiP™ package

- 0.978" x 0.898" x 0.284" (24.84 mm x 22.8 mm x 7.21 mm)

## **Typical Applications**

- Rail Transportation

- Defense / Aerospace

- Industrial

- Process Control

| Product Ratings                                      |                           |  |  |  |  |  |

|------------------------------------------------------|---------------------------|--|--|--|--|--|

| $V_{IN} = 14 \text{ V to } 72 \text{ V}$             | P <sub>OUT</sub> = 100 W  |  |  |  |  |  |

| V <sub>OUT</sub> = 24.0 V<br>(14.4 V to 26.4 V Trim) | I <sub>OUT</sub> = 4.20 A |  |  |  |  |  |

## **Product Description**

The DCM2322 is a lower power, isolated and regulated DC-DC converter that operates from an unregulated, wide-range input to generate an isolated 24.0 Vdc output. With its high-frequency zero-voltage switching (ZVS) topology, the DCM2322 converter consistently delivers high efficiency across the input line range. Modular DCM converters and downstream DC-DC products support efficient power distribution, providing superior power system performance and connectivity from a variety of unregulated power sources to the point-of-load.

Leveraging the thermal and density benefits of Vicor's ChiP packaging technology, the DCM2322 offers flexible thermal management options with very low top and bottom side thermal impedances. Thermally adept ChiP based power components enable customers to quickly and predictably achieve cost effective power system solutions.

## **Part Ordering Information**

| Product<br>Function         |    | kage<br>ze | Package<br>Type              | Max<br>Input<br>Voltage | Range<br>Ratio | Max<br>Output<br>Voltage | Max<br>Output<br>Power | Temperature<br>Grade                     | Option                                                                                               |

|-----------------------------|----|------------|------------------------------|-------------------------|----------------|--------------------------|------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------|

| DCM                         | 23 | 22         | х                            | 72                      | S              | 26                       | Α0                     | У                                        | 6z                                                                                                   |

| DCM =<br>DC-DC<br>Converter | m  | nm         | T =<br>Through hole<br>ChiPs |                         | Internal I     | Reference                |                        | T = -40°C to 125°C<br>M = -55°C to 125°C | 60 = Array and<br>Enhanced V <sub>OUT</sub> Regultion<br>Modes / Analog Control<br>Interface Version |

## **Typical Applications**

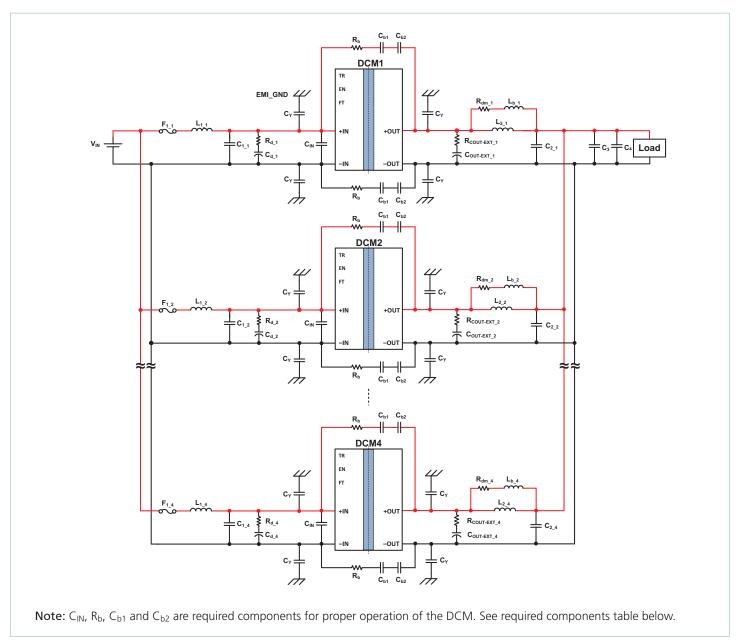

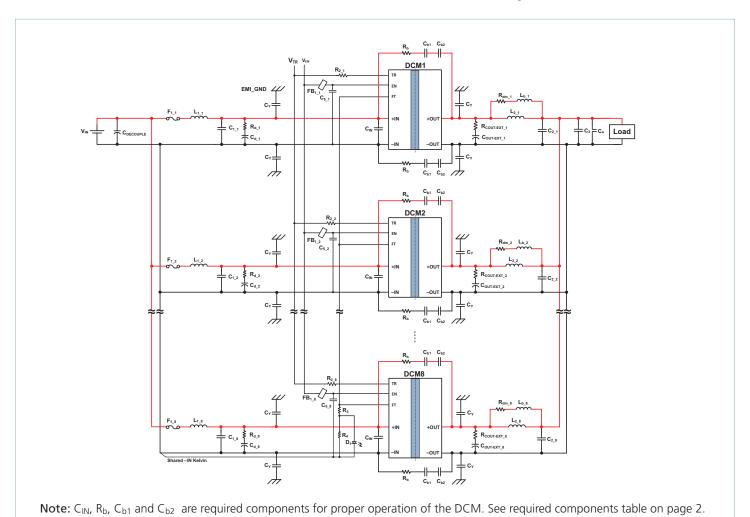

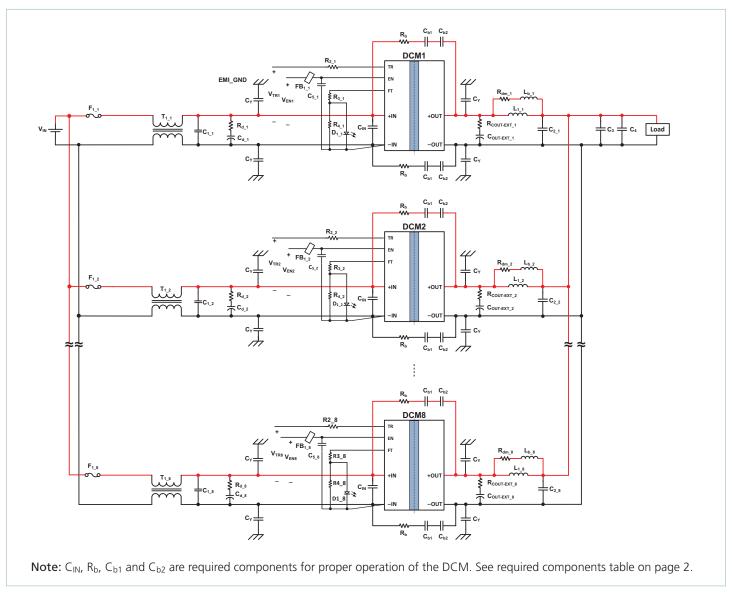

DCM2322x72S26A0y6z in an array of four units; applicable when DCM is operating in Array Mode

| Required Components               |                                                  |  |  |  |  |

|-----------------------------------|--------------------------------------------------|--|--|--|--|

| C <sub>IN</sub>                   | <b>TDK</b> C5750X7T2E225M250KA, 2.2 μF, 250 V    |  |  |  |  |

| R <sub>b</sub>                    | Generic 1 Ω, 1/4 W                               |  |  |  |  |

| C <sub>b1</sub> , C <sub>b2</sub> | <b>KEMET</b> C1812C103KGRACTU, 10,000 pF, 2000 V |  |  |  |  |

## **Typical Applications (Cont.)**

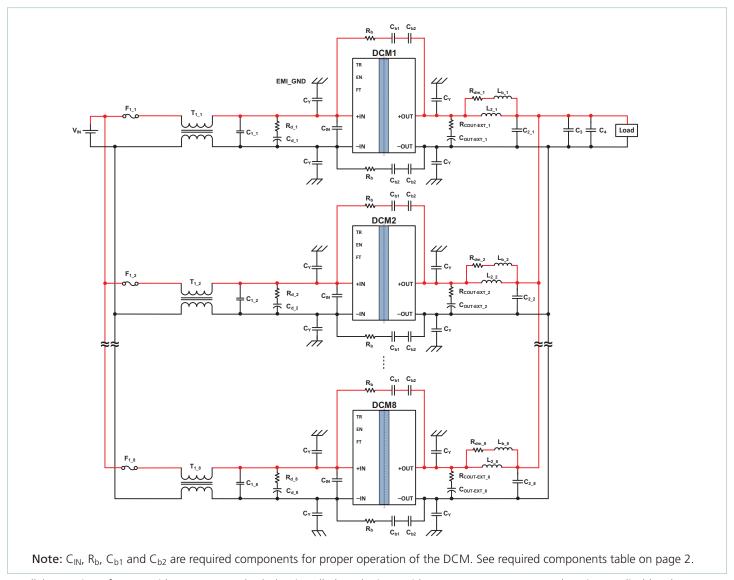

Parallel operation of DCMs with common mode chokes installed on the input side to suppress common mode noise; applicable when DCM is operating in Array Mode

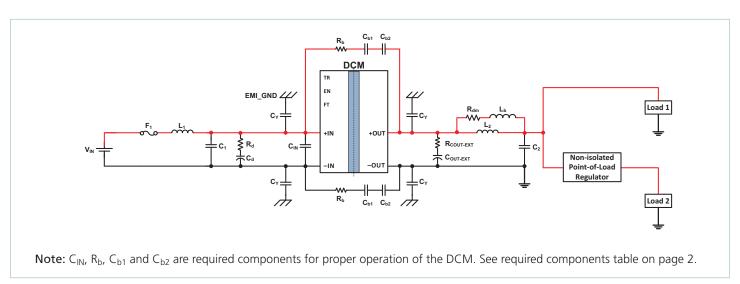

Single DCM2322x72S26A0y6z, to a non-isolated regulator, and direct to load

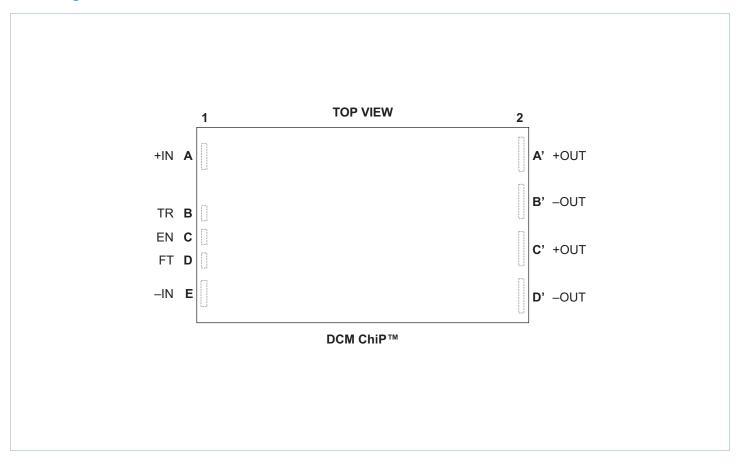

# **Pin Configuration**

# **Pin Descriptions**

| Pin<br>Number | Signal Name | Туре                   | Function                                                                                                                   |

|---------------|-------------|------------------------|----------------------------------------------------------------------------------------------------------------------------|

| A1            | +IN         | INPUT POWER            | Positive input power terminal                                                                                              |

| B1            | TR          | INPUT                  | Enables and disables trim functionality. Adjusts output voltage when trim active.                                          |

| C1            | EN          | INPUT                  | Dual function:  1. Enables either Array or Enhanced V <sub>OUT</sub> Regulation mode  2. Enables and disables power supply |

| D1            | FT          | OUTPUT                 | Fault monitoring                                                                                                           |

| E1            | -IN         | INPUT POWER<br>RETURN  | Negative input power terminal                                                                                              |

| A'2, C'2      | +OUT        | OUTPUT POWER           | Positive output power terminal                                                                                             |

| B'2, D'2      | -OUT        | OUTPUT POWER<br>RETURN | Negative output power terminal                                                                                             |

## **Absolute Maximum Ratings**

The absolute maximum ratings below are stress ratings only. Operation at or beyond these maximum ratings can cause permanent damage to the device. Electrical specifications do not apply when operating beyond rated operating conditions.

| Parameter                              | Comments         | Min  | Max  | Unit |

|----------------------------------------|------------------|------|------|------|

| Input Voltage (+IN to -IN)             |                  | -0.5 | 87.5 | V    |

| Input Voltage Slew Rate                |                  | -1   | 1    | V/µs |

| TR to –IN                              |                  | -0.3 | 3.5  | V    |

| EN to -IN                              |                  | -0.3 | 3.5  | V    |

| FT to -IN                              |                  | -0.3 | 3.5  | V    |

| ri to -iiv                             |                  |      | 5    | mA   |

| Output Voltage (+OUT to –OUT)          |                  | -0.5 | 31.7 | V    |

| Dielectric withstand (input to output) | Basic insulation | 3000 |      | Vdc  |

| Internal Operating Temperature         | T-Grade          | -40  | 125  | °C   |

| internal Operating Temperature         | M-Grade          | -55  | 125  | °C   |

| Storage Temperature                    | T-Grade          | -40  | 125  | °C   |

| Storage remperature                    | M-Grade          | -65  | 125  | °C   |

| Average Output Current                 |                  |      | 7.5  | А    |

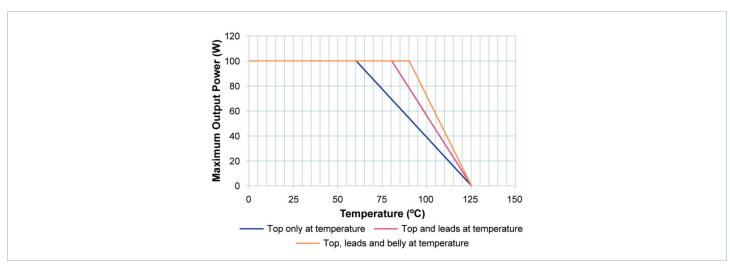

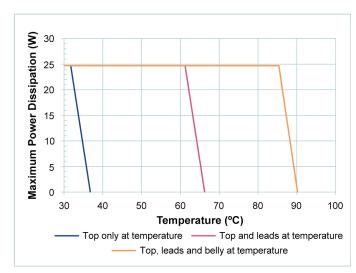

Figure 1 — Thermal Specified Operating Area: Max Output Power vs. Case Temp, Single unit at minimum full load efficiency

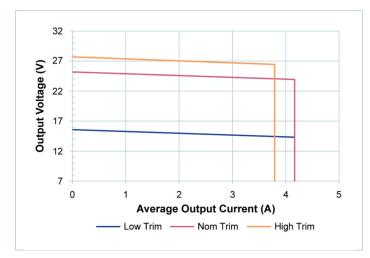

Figure 2 — Electrical Specified Operating Area: Array Mode

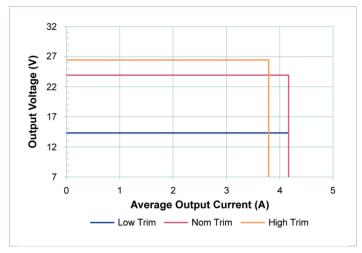

**Figure 3** — Electrical Specified Operating Area: Enhanced  $V_{OUT}$  Regulation Mode

## **Common Electrical Specifications: Array and Enhanced Vout Regulation Modes**

Specifications apply over all line, trim and load conditions, internal temperature  $T_{INT} = 25^{\circ}\text{C}$ , unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C for T-Grade and -55°C <  $T_{INT}$  < 125°C for M-grade.

| Attribute                          | Attribute Symbol Conditions         |                                                                                                                                                                                            | Min   | Тур      | Max   | Unit |

|------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-------|------|

|                                    |                                     |                                                                                                                                                                                            |       |          |       |      |

|                                    | I                                   | Power Input Specification                                                                                                                                                                  |       |          |       |      |

| Input voltage range                | V <sub>IN</sub>                     | Continuous operation                                                                                                                                                                       | 14    | 43       | 72    | V    |

| Inrush current (peak)              | I <sub>INRP</sub>                   | With maximum C <sub>OUT-EXT</sub> , full resistive load                                                                                                                                    |       |          | 8.0   | Α    |

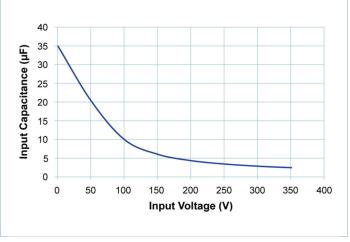

| Input capacitance (internal)       | C <sub>IN-INT</sub>                 | Effective value at nominal input voltage                                                                                                                                                   |       | 37.6     |       | μF   |

| Input capacitance (internal) ESR   | R <sub>CIN-INT</sub>                | At 1 MHz                                                                                                                                                                                   |       | 0.41     |       | mΩ   |

| Input inductance (external)        | L <sub>IN</sub>                     | Differential mode, with no further line bypassing                                                                                                                                          |       |          | 1     | μΗ   |

|                                    |                                     | No Load Specification                                                                                                                                                                      |       |          |       |      |

| Input power – disabled             | $P_{Q}$                             | Nominal line, see Fig. 4                                                                                                                                                                   |       | 0.6      | 0.8   | W    |

| iliput power – disabled            | rQ                                  | Worst case line, see Fig. 4                                                                                                                                                                |       |          | 1.2   | W    |

| lance and the second second        | D                                   | Nominal line, see Fig. 5                                                                                                                                                                   |       | 2.5      | 3.5   | W    |

| Input power – enabled with no load | P <sub>NL</sub>                     | Worst case line, see Fig. 5                                                                                                                                                                |       |          | 4.0   | W    |

|                                    |                                     | Power Output Specification                                                                                                                                                                 |       | <u>'</u> |       |      |

| Output voltage set point           | V <sub>OUT-NOM</sub>                | V <sub>IN</sub> = 43 V, nominal trim, at 100% Load, T <sub>INT</sub> = 25°C                                                                                                                | 23.88 | 24.0     | 24.12 | V    |

| Rated output voltage trim range    | Vouttrimming                        | Specifies the Low, Nominal and High Trim conditions.  Array Mode: trim range over temp at full load  Enhanced V <sub>OUT</sub> Regultion Mode: trim range over temp, with > 10% rated load | 14.4  | 24.0     | 26.4  | V    |

| Rated output power                 | P <sub>OUT</sub>                    | Continuous, V <sub>OUT</sub> ≥ 24.0 V                                                                                                                                                      | 100   |          |       | W    |

| Rated output current               | I <sub>OUT</sub>                    | Continuous, V <sub>OUT</sub> ≤ 24.0 V                                                                                                                                                      | 4.20  |          |       | А    |

| Output current limit               | I <sub>OUT-LM</sub>                 | Of rated I <sub>OUT</sub> max. Fully operational current limit, for nominal trim and below                                                                                                 | 100   | 120      | 140   | %    |

| Current limit delay                | t <sub>IOUT-LIM</sub>               | The module will power limit in a fast transient event                                                                                                                                      |       | 1        |       | ms   |

|                                    |                                     | Full load, nominal line, nominal trim                                                                                                                                                      | 89.0  | 90.0     |       | %    |

| Efficiency                         | η                                   | Full load, over line and temperature, nominal trim                                                                                                                                         | 80.0  |          |       | %    |

|                                    |                                     | 50% load, over rated line, temperature and trim                                                                                                                                            | 75.0  |          |       | %    |

| Output voltage ripple              | V <sub>OUT-PP</sub>                 | 20 MHz bandwidth. At nominal trim, minimum C <sub>OUTEXT</sub> and at least 10 % rated load                                                                                                |       | 257      |       | mV   |

| Output capacitance (internal)      | C <sub>OUT-INT</sub>                | Effective value at nominal output voltage                                                                                                                                                  |       | 80       |       | μF   |

| Output capacitance (internal) ESR  | R <sub>COUT-INT</sub>               | At 1 MHz                                                                                                                                                                                   |       | 0.228    |       | mΩ   |

| Output capacitance (external)      | C <sub>OUT-EXT</sub>                | Excludes component temperature coefficient For load transients that remain > 10% rated load                                                                                                | 470   |          | 5000  | μF   |

| Output capacitance (external)      | C <sub>OUT-EXT-TRANS</sub>          | Excludes component temperature coefficient For load transients down to I <sub>TRAN_MIN</sub> rated load, with static trim                                                                  | 500   |          | 5000  | μF   |

| Output capacitance (external)      | C <sub>OUT-EXT-</sub><br>TRANS-TRIM | Excludes component temperature coefficient For load transients down to I <sub>TRAN_MIN</sub> rated load, with dynamic trimming                                                             | 500   |          | 5000  | μF   |

| Minimum Transient Load             | I <sub>TRAN_MIN</sub>               | Minimum required load for proper operation of DCM during load transient conditions                                                                                                         | 0     |          |       | %    |

| Output capacitance, ESR (ext.)     | R <sub>COUT-EXT</sub>               | At 10 kHz, excludes component tolerances                                                                                                                                                   | 10    |          |       | mΩ   |

## Common Electrical Specifications (Cont.): Array and Enhanced V<sub>OUT</sub> Regulation Modes

Specifications apply over all line, trim and load conditions, internal temperature  $T_{INT} = 25^{\circ}\text{C}$ , unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C for T-Grade and -55°C <  $T_{INT}$  < 125°C for M-grade.

| Attribute                                                        | Symbol                     | Conditions / Notes                                                                                                                                                           | Min   | Тур | Max   | Unit |

|------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

|                                                                  |                            | Power Output Specifications (Cont.)                                                                                                                                          |       |     |       |      |

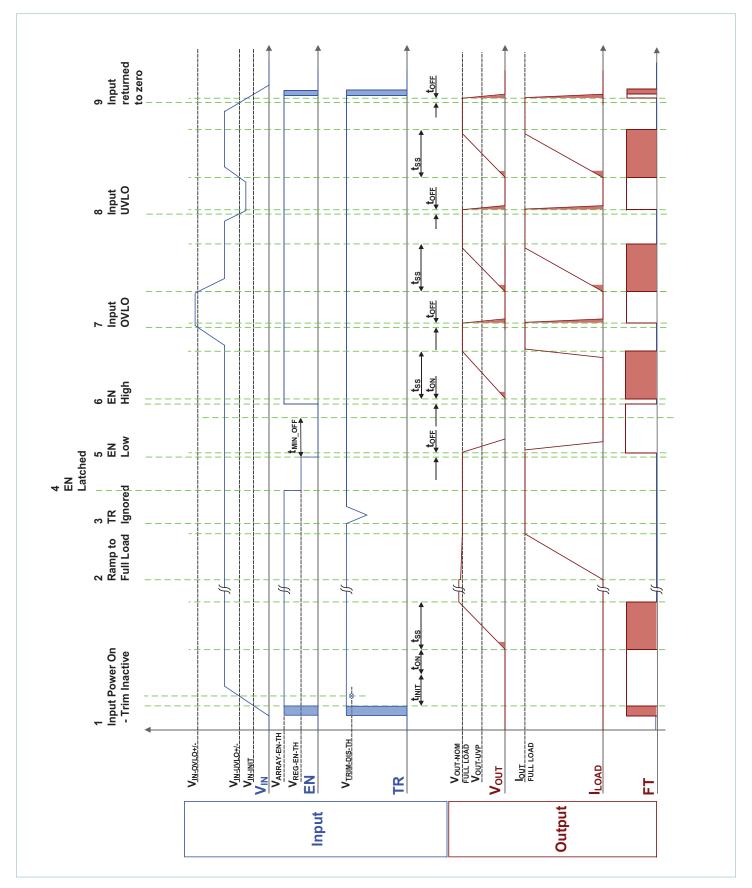

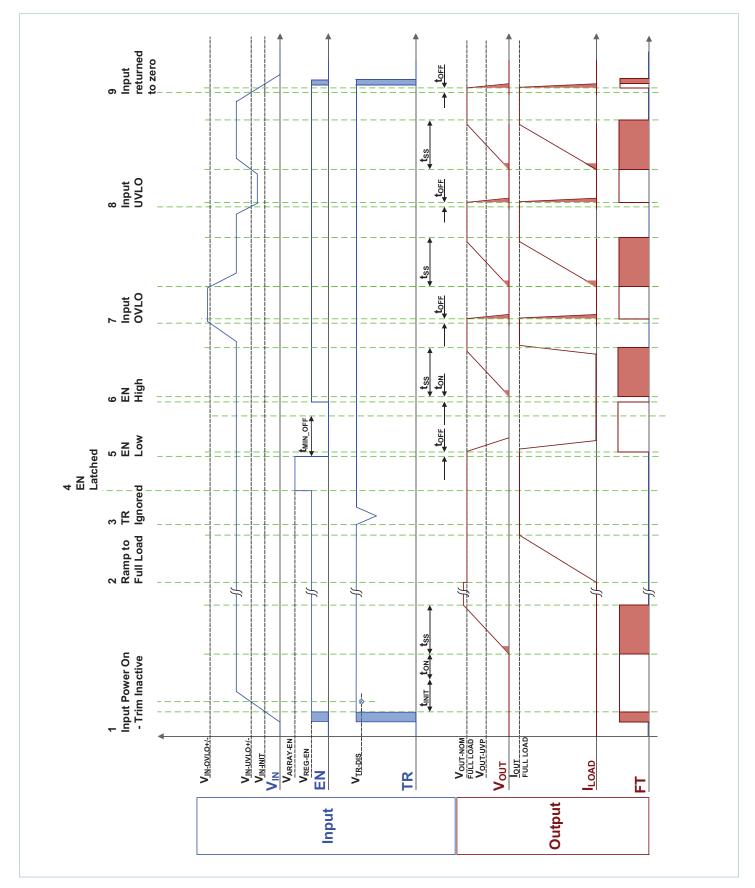

| Initialization delay                                             | t                          | See state diagram                                                                                                                                                            |       | 25  | 40    | ms   |

| <u> </u>                                                         | t <sub>INIT</sub>          | From rising edge EN, with V <sub>IN</sub> pre-applied.                                                                                                                       |       | 23  | 40    | 1115 |

| Output turn-on delay                                             | t <sub>ON</sub>            | See timing diagram                                                                                                                                                           |       | 200 |       | μs   |

| Output turn-off delay                                            | t <sub>OFF</sub>           | From falling edge EN. See timing diagram                                                                                                                                     |       |     | 600   | μs   |

| Soft start ramp time                                             | t <sub>SS</sub>            | At full rated resistive load. Typ spec is 1-up with min $C_{OUT-EXT}$ . Max spec is for arrays with max $C_{OUT-EXT}$                                                        |       | 300 | 500   | ms   |

| V <sub>OUT</sub> threshold for max<br>rated load current         | V <sub>OUT-FL-THRESH</sub> | During startup, $V_{\text{OUT}}$ must achieve this threshold before output can support full rated current                                                                    |       |     | 12.0  | V    |

| I <sub>OUT</sub> at startup                                      | I <sub>OUT-START</sub>     | Max load current at startup while $V_{OUT}$ is below $V_{OUTFL\_THRESH}$                                                                                                     | 0.42  |     |       | А    |

| Monotonic soft-start threshold voltage                           | V <sub>OUT-MONOTONIC</sub> | Output voltage rise becomes monotonic with 10% of preload once it crosses V <sub>OUT-MONOTONIC</sub>                                                                         |       |     | 12.0  | V    |

| Minimum required disabled duration                               | t <sub>OFF-MIN</sub>       | This refers to the minimum time a module needs to be in the disabled state before it will attempt to start via EN                                                            |       |     | 2     | ms   |

| Minimum required disabled duration for predictable restart       | toff-monotonic             | This refers to the minimum time a module needs to be in<br>the disabled state before it is guaranteed to exhibit<br>monotonic soft-start and have predictable startup timing |       |     | 100   | ms   |

| Voltage deviation (transient)                                    | %V <sub>OUT-TRANS</sub>    | Minimum C <sub>OUT EXT</sub> (10 ↔ 90% load step),                                                                                                                           |       | <10 |       | %    |

| Settling time                                                    | t <sub>SETTLE</sub>        | excluding load line.                                                                                                                                                         |       | 4.0 |       | ms   |

|                                                                  |                            | Powertrain Protections                                                                                                                                                       |       |     |       |      |

| Input Voltage Initialization threshold                           | V <sub>IN-INIT</sub>       | Threshold to start t <sub>INIT</sub> delay                                                                                                                                   |       |     | 6     | V    |

| Input Voltage Reset threshold                                    | V <sub>IN-RESET</sub>      | Latching faults will clear once V <sub>IN</sub> falls below V <sub>IN-RESET</sub>                                                                                            | 3     |     |       | V    |

| Input undervoltage lockout threshold                             | V <sub>IN-UVLO-</sub>      |                                                                                                                                                                              | 8.40  |     | 13.30 | V    |

| Input undervoltage recovery threshold                            | V <sub>IN-UVLO+</sub>      | See Timing diagram                                                                                                                                                           |       |     | 14.00 | V    |

| Input overvoltage lockout threshold                              | V <sub>IN-OVLO+</sub>      |                                                                                                                                                                              |       |     | 80    | V    |

| Input overvoltage recovery threshold                             | V <sub>IN-OVLO-</sub>      | See Timing diagram                                                                                                                                                           | 72    |     |       | V    |

| Output overvoltage threshold                                     | V <sub>OUT-OVP</sub>       | From 25% to 100% load. Latched shutdown                                                                                                                                      | 30.36 |     |       | V    |

| Output overvoltage threshold                                     | V <sub>OUT-OVP-LL</sub>    | From 0% to 25% load. Latched shutdown                                                                                                                                        | 31.68 |     |       | V    |

| Minimum current limited V <sub>OUT</sub>                         | V <sub>OUT-UVP</sub>       | Over all operating steady-state line and trim conditions                                                                                                                     |       |     | 10.80 | V    |

| Overtemperature threshold (internal)                             | T <sub>INT-OTP</sub>       |                                                                                                                                                                              | 125   |     |       | °C   |

| Power limit                                                      | P <sub>LIM</sub>           |                                                                                                                                                                              |       |     | 200   | W    |

| V <sub>IN</sub> overvoltage to cessation of powertrain switching | t <sub>OVLO-SW</sub>       | Independent of fault logic                                                                                                                                                   |       | 4.5 |       | μs   |

| V <sub>IN</sub> overvoltage response time                        | t <sub>ovlo</sub>          | For fault logic only                                                                                                                                                         |       |     | 200   | μs   |

| V <sub>IN</sub> undervoltage response time                       | t <sub>UVLO</sub>          |                                                                                                                                                                              |       |     | 100   | ms   |

| Short circuit response time                                      | t <sub>sc</sub>            | Powertrain on, operational state                                                                                                                                             |       |     | 200   | μs   |

| Short circuit, or temperature fault recovery time                | t <sub>FAULT</sub>         | See Timing diagram                                                                                                                                                           |       | 1   |       | S    |

## **Electrical Specifications: Array Mode Only**

Specifications apply over all line, trim and load conditions, internal temperature  $T_{INT} = 25$ °C, unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C for T-Grade and -55°C <  $T_{INT}$  < 125°C for M-grade.

| Attribute                              | Symbol                      | Conditions / Notes                                                                                                                                                       | Min    | Тур    | Max    | Unit  |  |  |  |  |

|----------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-------|--|--|--|--|

|                                        |                             |                                                                                                                                                                          |        |        |        |       |  |  |  |  |

| Power Output Specification             |                             |                                                                                                                                                                          |        |        |        |       |  |  |  |  |

| Output voltage load regulation         | ΔV <sub>OUT-LOAD</sub>      | Linear load line. Output voltage increase from full rated<br>load current to no load (Does not include light load<br>regulation). See Fig. 17 and Sec. Design Guidelines | 1.1309 | 1.2631 | 1.3968 | V     |  |  |  |  |

| Output voltage light load regulation   | $\Delta V_{	ext{OUT-LL}}$   | 0% to 10% load, additional $V_{\text{OUT}}$ relative to calculated load-line point; see Sec. Design Guidelines                                                           | -0.36  |        | 2.53   | V     |  |  |  |  |

| Output voltage temperature coefficient | $\Delta V_{	ext{OUT-TEMP}}$ | Nominal, linear temperature coefficient, relative to $T_{\text{INT}} = 25^{\circ}\text{C}$ . See Fig. 18 and Design Guidelines Section                                   |        | -3.20  |        | mV/°C |  |  |  |  |

| Output voltage accuracy                | %V <sub>OUT-ACCURACY</sub>  | The total output voltage setpoint accuracy from the calculated ideal $V_{OUT}$ based on load, temp and trim. Excludes $\Delta V_{OUT-LL}$                                | -3.0   |        | 3.0    | %     |  |  |  |  |

## **Electrical Specifications: Enhanced V<sub>OUT</sub> Regulation Mode Only**

Specifications apply over all line, trim and load conditions, internal temperature  $T_{INT} = 25^{\circ}C$ , unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C for T-Grade and -55°C <  $T_{INT}$  < 125°C for M-grade.

| Attribute                            | Symbol                     | Conditions / Notes                                                                                                                                                    | Min   | Тур | Max  | Unit |

|--------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

|                                      |                            |                                                                                                                                                                       |       |     |      |      |

|                                      |                            | <b>Power Output Specifications</b>                                                                                                                                    |       |     |      |      |

| Output voltage regulation            |                            | At nominal line, nominal trim, full load and ambient temperature                                                                                                      | -0.5  |     | 0.5  |      |

|                                      | %V <sub>OUT</sub> -        | At nominal line, nominal trim and:  • Load >20% of full load and ambient temperature  • Full load and over temperature                                                | -1.0  |     | 1.0  | %    |

|                                      |                            | All other conditions (does not include light load regulation)                                                                                                         | -1.5  |     | 1.5  |      |

| Output voltage accuracy              | %V <sub>OUT-ACCURACY</sub> | The total output voltage set-point accuracy from the calculated $V_{OUT}$ based on load, temp and trim.<br>Excludes:  • $\Delta V_{OUT-LL}$ • $\% V_{OUT-REGULATION}$ | -2.0  |     | 2.0  | %    |

| Output voltage light load regulation | ΔV <sub>OUT-LL</sub>       | 0% to 10% load, additional V <sub>OUT</sub> relative to V <sub>OUT</sub> accuracy; see Design Guidelines section                                                      | -0.36 |     | 2.53 | V    |

## **Signal Specifications**

Specifications apply over all line, trim and load conditions, internal temperature  $T_{INT} = 25$ °C, unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C for T-Grade and -55°C <  $T_{INT}$  < 125°C for M-grade.

#### Trim: TR

- ullet The TR pin enables and disables trim functionality when  $V_{IN}$  is initially applied to the DCM converter. When Vin first crosses  $V_{IN-UVLO+}$ , the voltage on TR determines whether or not trim is active.

- If TR is not floating at power up and has a voltage less than TR trim enable threshold, trim is active.

- If trim is active, the TR pin provides dynamic trim control with at least 30Hz of -3dB control bandwidth over the output voltage of the DCM converter.

- The TR pin has an internal pull-up to V<sub>CC</sub> and is referenced to the -IN pin of the converter.

| SIGNAL TYPE     | STATE                     | ATTRIBUTE                                         | SYMBOL                                                 | CONDITIONS / NOTES                                    | MIN  | NOM  | MAX  | UNIT |

|-----------------|---------------------------|---------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|------|------|------|------|

| DIGITAL         | TR trim disable threshold | $V_{TRIM\text{-}DIS\text{-}TH}$                   | Trim disabled when TR above this threshold at power up |                                                       |      | 3.20 | V    |      |

| INPUT           | INPUT Startup             | TR trim enable threshold                          | V <sub>TRIM-EN-TH</sub>                                | Trim enabled when TR below this threshold at power up | 3.15 |      |      | V    |

|                 |                           | Internally generated V <sub>CC</sub>              | $V_{CC}$                                               |                                                       | 3.21 | 3.30 | 3.39 | V    |

|                 | Operational               | TR pin functional range                           | $V_{TRIM-EN}$                                          |                                                       | 0.00 | 2.44 | 3.16 | V    |

| ANALOG<br>INPUT | NLOG with Trim            | V <sub>OUT</sub> referred TR<br>pin resolution    | $V_{\text{OUT-RES}}$                                   | With $V_{CC} = 3.3 \text{ V}$                         |      | 31   |      | mV   |

|                 |                           | TR internal pull up resistance to V <sub>CC</sub> | R <sub>TRIIM-INT</sub>                                 |                                                       | 9.9  | 10.0 | 10.1 | kΩ   |

#### **Enable: EN**

- Dual Function:

- The EN pin enables either the Array mode or Enhanced V<sub>OUT</sub> Regulation mode based on the voltage level on EN pin during start up.

- The EN pin enables and disables the DCM converter; when held low the unit will be disabled.

- The EN pin has an internal pull-up to VCC and is referenced to the -IN pin of the converter.

| SIGNAL TYPE      | STATE               | ATTRIBUTE                                                  | SYMBOL                     | CONDITIONS / NOTES | MIN  | NOM  | MAX  | UNIT |

|------------------|---------------------|------------------------------------------------------------|----------------------------|--------------------|------|------|------|------|

|                  | EN enable threshold | $V_{\text{ENABLE-EN-TH}}$                                  |                            |                    |      | 2.31 | V    |      |

|                  |                     | EN disable threshold                                       | $V_{\text{ENABLE-DIS-TH}}$ |                    | 0.99 |      |      | V    |

|                  |                     | Internally generated V <sub>CC</sub>                       | $V_{CC}$                   |                    | 3.21 | 3.30 | 3.39 | V    |

| DIGITAL<br>INPUT | Any                 | EN internal pull up resistance to V <sub>CC</sub>          | R <sub>ENABLE-INT</sub>    |                    | 9.9  | 10.0 | 10.1 | kΩ   |

|                  |                     | Array mode enable threshold                                | V <sub>ARRAY-EN-TH</sub>   |                    | 2.97 |      |      | V    |

|                  |                     | Enhanced V <sub>OUT</sub> Regulation mode enable threshold | V <sub>REG-EN-TH</sub>     |                    |      |      | 2.63 | V    |

## Fault: FT

- The FT pin is a Fault flag pin.

- When the module is enabled and no fault is present, the FT pin does not have current drive capability.

- Whenever the powertrain stops (due to a fault protection or disabling the module by pulling EN low), the FT pin output Vcc and provides current to drive an external ciruit.

- When module starts up, the FT pin is pulled high to V<sub>CC</sub> during microcontroller initialization and will remain high until soft start process starts.

| SIGNAL TYPE | STATE      | ATTRIBUTE                                         | SYMBOL                            | CONDITIONS / NOTES                                                    | MIN | NOM | MAX | UNIT |

|-------------|------------|---------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| Any         | Any        | FT internal pull up resistance to V <sub>CC</sub> | R <sub>FAULT-INT</sub>            |                                                                       | 494 | 499 | 504 | kΩ   |

|             | FT voltage | $V_{\text{FAULT-ACTIVE}}$                         | At rated current drive capability | 3.0                                                                   |     |     | V   |      |

| OUTPUT      |            | FT current drive capability                       | I <sub>FAULT-ACTIVE</sub>         | Over-load beyond the ABSOLUTE MAXIMUM ratings may cause module damage | 4   |     |     | mA   |

|             |            | FT response time                                  | t <sub>FT-ACTIVE</sub>            | Delay from cessation of switching to FT Pin Active                    |     |     | 200 | μs   |

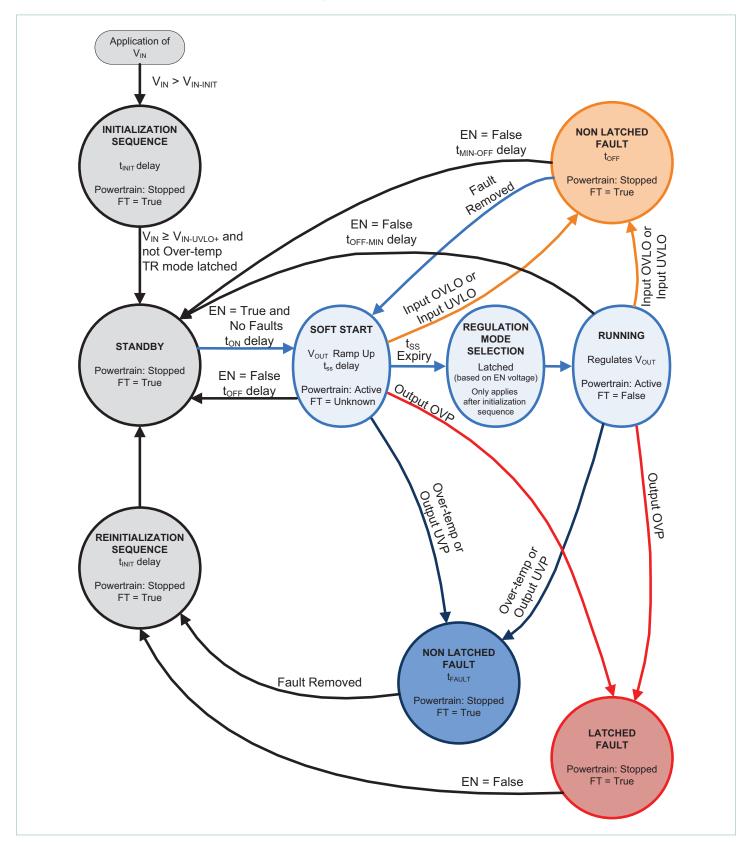

## **High Level Functional State Diagram**

Conditions that cause state transitions are shown along arrows. Sub-sequence activities listed inside the state bubbles.

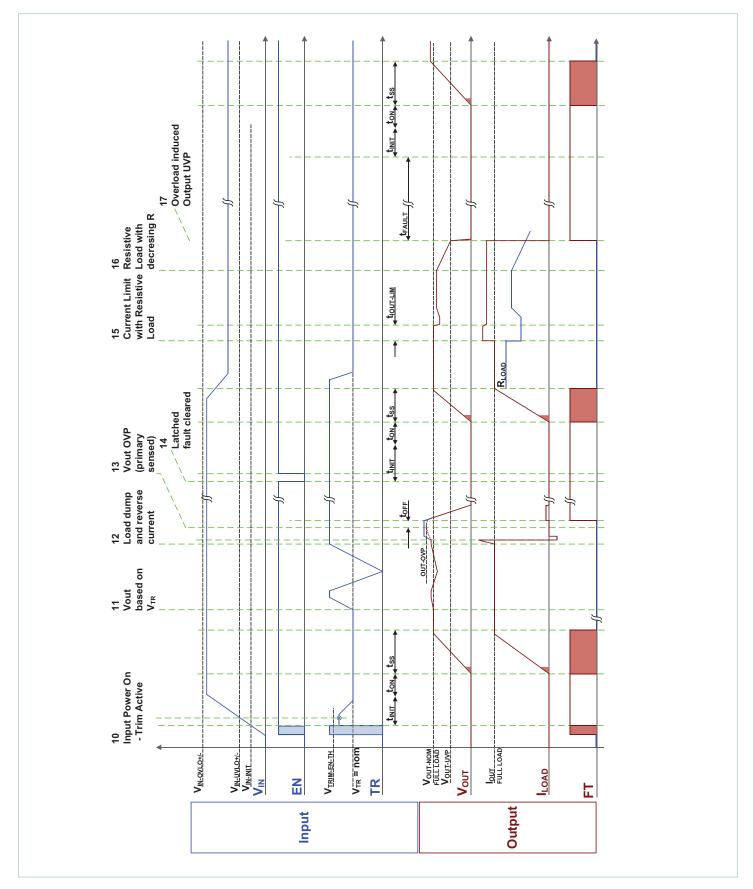

## **Timing Diagrams – Array Mode**

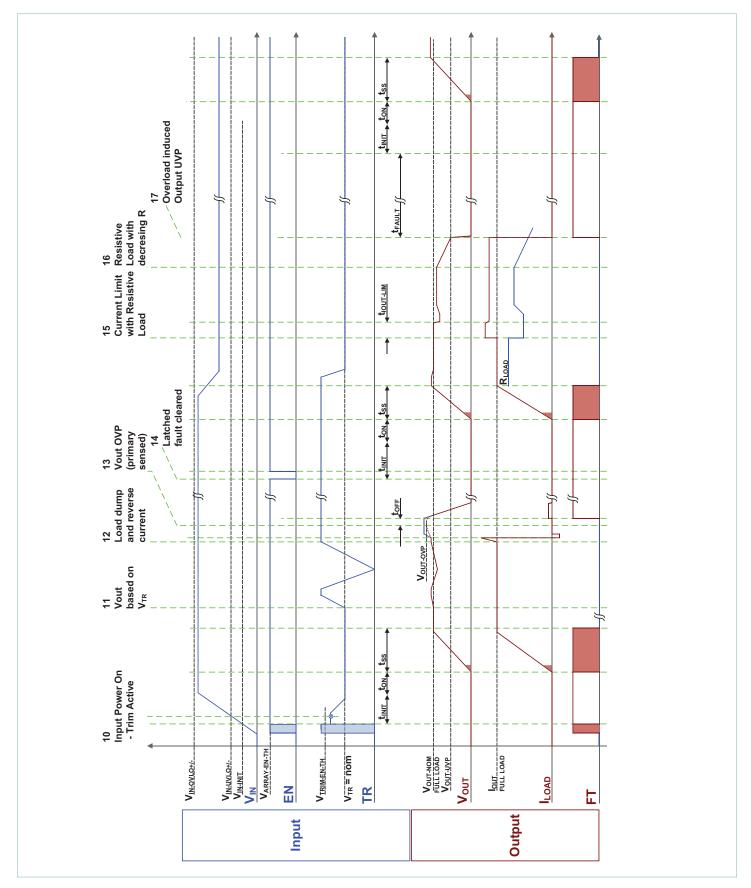

## **Timing Diagrams – Array Mode (Cont.)**

# **Timing Diagrams – Enhanced V<sub>OUT</sub> Regulation Mode**

# **Timing Diagrams – Enhanced V**<sub>OUT</sub> **Regulation Mode (Cont.)**

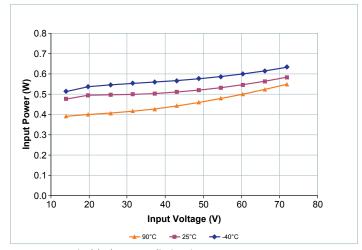

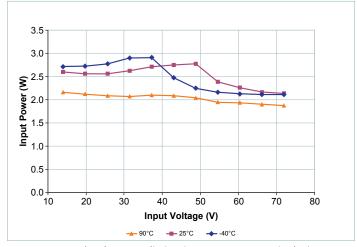

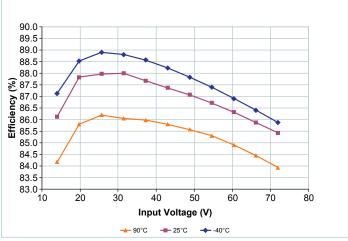

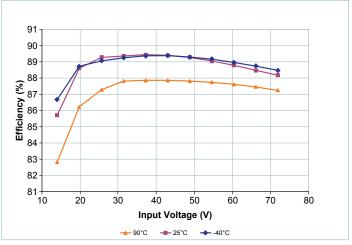

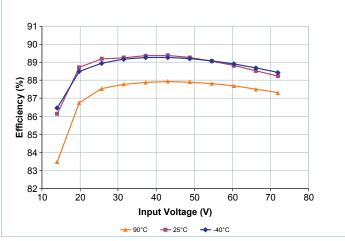

## Common Typical Performance Characteristics: Array and Enhanced V<sub>OUT</sub> Regulation Modes

The following figures present typical performance at  $T_C = 25$ °C, unless otherwise noted. See associated figures for general trend data. Unless otherwise specified, figures are applicable for both modes of operation

**Figure 4** — Disabled power dissipation vs.  $V_{IN}$

**Figure 5** — No load power dissipation vs.  $V_{IN}$ , at nominal trim

**Figure 6** — Full Load Efficiency vs.  $V_{IN}$ , at low trim

**Figure 7** — Full Load Efficiency vs.  $V_{IN}$ , at nominal trim

Figure 8 — Full Load Efficiency vs. V<sub>IN</sub>, at high trim

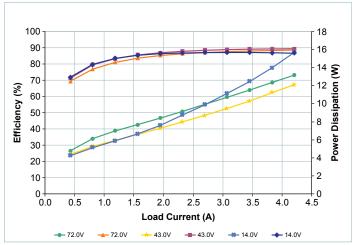

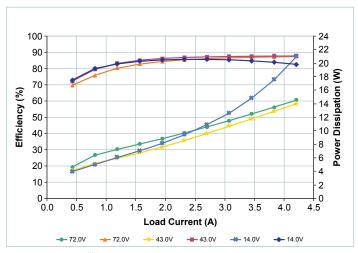

## Common Typical Performance Characteristics (Cont.): Array and Enhanced Vout Regulation Modes

The following figures present typical performance at  $T_C = 25$ °C, unless otherwise noted. See associated figures for general trend data. Unless otherwise specified, figures are applicable for both modes of operation

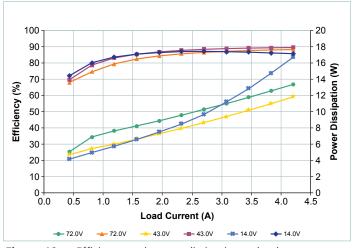

**Figure 9** — Efficiency and power dissipation vs.load at  $T_{CASF} = -40^{\circ}\text{C}$ , nominal trim

**Figure 11** — Efficiency and power dissipation vs.load at  $T_{CASE} = 90^{\circ}\text{C}$ , nominal trim

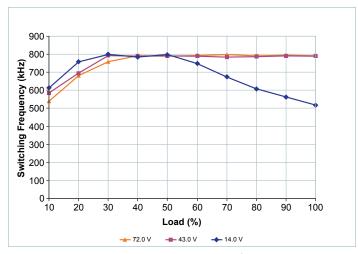

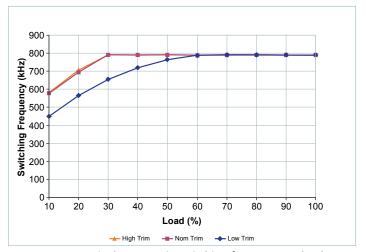

**Figure 13** — Nominal powertrain switching frequency vs. load, at nominal trim

**Figure 10** — Efficiency and power dissipation vs.load at  $T_{CASE} = 25^{\circ}\text{C}$ , nominal trim

Figure 12 — Effective internal input capacitance vs. applied voltage

**Figure 14** — Nominal powertrain switching frequency vs. load, at nominal  $V_{\rm IN}$

## Common Typical Performance Characteristics (Cont.): Array and Enhanced V<sub>OUT</sub> Regulation Modes

The following figures present typical performance at  $T_C = 25$ °C, unless otherwise noted. See associated figures for general trend data. Unless otherwise specified, figures are applicable for both modes of operation

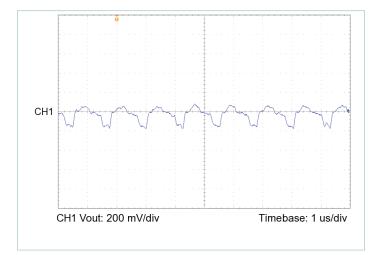

**Figure 15** — Output voltage ripple,  $V_{IN}$  = 43 V,  $V_{OUT}$  = 24.0 V,  $C_{OUT\_EXT}$  = 470  $\mu$ F,  $R_{LOAD}$  = 5.714  $\Omega$

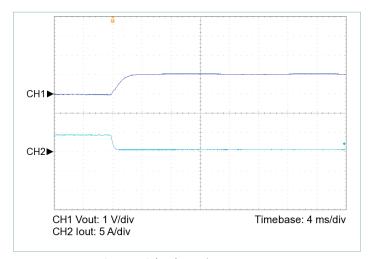

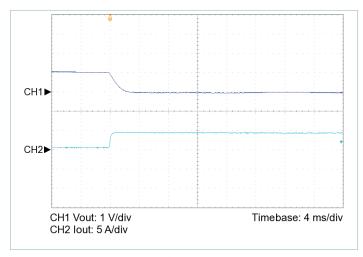

**Figure 16** —Startup from EN,  $V_{IN}$  = 43 V,  $C_{OUT\_EXT}$  = 5000  $\mu$ F,  $R_{LOAD}$  = 5.714  $\Omega$

## **Typical Performance Characteristics: Array Mode Only**

The following figures present typical performance at  $T_C = 25$ °C, unless otherwise noted. See associated figures for general trend data.

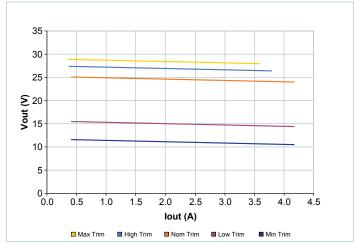

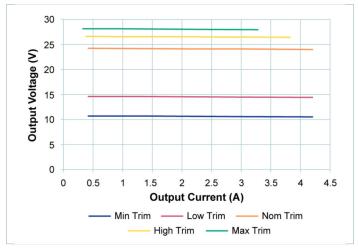

Figure 17 — Ideal V<sub>OUT</sub> vs. load current, at 25°C case

**Figure 19** — 100% to 10% load transient response,  $V_{IN}$  = 43 V, nominal trim,  $C_{OUT\_EXT}$  = 470  $\mu F$

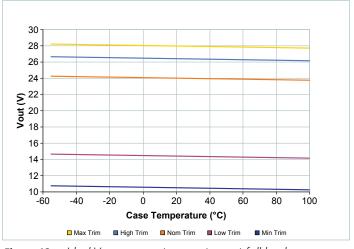

**Figure 18** — Ideal  $V_{OUT}$  vs. case temperature, at full load

**Figure 20** — 10% to 100% load transient response,  $V_{IN}$  = 43 V, nominal trim,  $C_{OUT\_EXT}$  = 470  $\mu$ F

## Typical Performance Characteristics: Enhanced V<sub>OUT</sub> Regulation Mode Only

The following figures present typical performance at  $T_C = 25$ °C, unless otherwise noted. See associated figures for general trend data.

**Figure 21** — Ideal  $V_{OUT}$  vs. load current, at 25°C case, operating in Enhanced  $V_{OUT}$  Regulation Mode

## **General Characteristics**

Specifications apply over all line, trim and load conditions, internal temperature  $T_{INT} = 25^{\circ}\text{C}$ , unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C for T-Grade and -55°C <  $T_{INT}$  < 125°C for M-grade.

| Attribute                      | Symbol                    | Conditions / Notes                                                                            | Min           | Тур           | Max           | Unit      |  |

|--------------------------------|---------------------------|-----------------------------------------------------------------------------------------------|---------------|---------------|---------------|-----------|--|

|                                |                           |                                                                                               |               |               |               |           |  |

| Mechanical                     |                           |                                                                                               |               |               |               |           |  |

| Length                         | L                         |                                                                                               | 24.46/[0.963] | 24.84/[0.978] | 25.22/[0.993] | mm/[in]   |  |

| Width                          | W                         |                                                                                               | 22.67/[0.893] | 22.8/[0.898]  | 22.93/[0.903] | mm/[in]   |  |

| Height                         | Н                         |                                                                                               | 7.11/[0.28]   | 7.21/[0.284]  | 7.31/[0.288]  | mm/[in]   |  |

| Volume                         | Vol                       | No heat sink                                                                                  |               | 4.08/[0.25]   |               | cm³/[in³] |  |

| Weight                         | W                         |                                                                                               |               | 15.0/[0.53]   |               | g/[oz]    |  |

| Lead finish                    |                           | Nickel                                                                                        | 0.51          |               | 2.03          | μm        |  |

|                                |                           | Palladium                                                                                     | 0.02          |               | 0.15          |           |  |

|                                |                           | Gold                                                                                          | 0.003         |               | 0.051         |           |  |

| Thermal                        |                           |                                                                                               |               |               |               |           |  |

|                                |                           | T-Grade                                                                                       | -40           |               | 125           | - °C      |  |

| Operating internal temperature | T <sub>INT</sub>          | M-Grade                                                                                       | -55           |               | 125           |           |  |

| Thermal resistance top side    | $\theta_{	ext{INT-TOP}}$  | Estimated thermal resistance to maximum temperature internal component from isothermal top    |               | 3.50          |               | °C/W      |  |

| Thermal resistance leads       | $	heta_{	ext{INT-LEADS}}$ | Estimated thermal resistance to maximum temperature internal component from isothermal leads  |               | 8.40          |               | °C/W      |  |

| Thermal resistance bottom side | <b>Ө</b> ІNТ-ВОТТОМ       | Estimated thermal resistance to maximum temperature internal component from isothermal bottom |               | 3.90          |               | °C/W      |  |

| Thermal capacity               |                           |                                                                                               |               | 10.3          |               | Ws/°C     |  |

|                                |                           | Assembly                                                                                      |               |               |               |           |  |

| <b>5</b>                       | _                         | T-Grade                                                                                       | -40           |               | 125           | °C        |  |

| Storage temperature            | T <sub>ST</sub>           | M-Grade                                                                                       | -65           |               | 125           |           |  |

| ESD rating                     | НВМ                       | Method per Human Body Model Test<br>ESDA/JEDEC JDS-001-2012                                   | CLASS 1C      |               |               | V         |  |

|                                | CDM                       | Charged Device Model JESD22-C101E                                                             | CLASS 2       |               |               |           |  |

| Soldering [1]                  |                           |                                                                                               |               |               |               |           |  |

| Peak temperature top case      |                           | For further information, please contact factory applications                                  |               |               | 135           | °C        |  |

<sup>&</sup>lt;sup>[1]</sup> Product is not intended for reflow solder attach.

## **General Characteristics (Cont.)**

Specifications apply over all line, trim and load conditions, internal temperature  $T_{INT} = 25^{\circ}\text{C}$ , unless otherwise noted. **Boldface** specifications apply over the temperature range of -40°C <  $T_{INT}$  < 125°C for T-Grade and -55°C <  $T_{INT}$  < 125°C for M-grade.

| Attribute                  | Symbol                                                                       | Conditions / Notes                                                                    | Min  | Тур  | Max | Unit |  |  |

|----------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|------|-----|------|--|--|

|                            |                                                                              |                                                                                       |      |      |     |      |  |  |

| Safety                     |                                                                              |                                                                                       |      |      |     |      |  |  |

| Dielectric Withstand Test  | V <sub>HIPOT</sub>                                                           | IN to OUT                                                                             | 3000 |      |     | Vdc  |  |  |

|                            |                                                                              | IN to CASE                                                                            | 1500 |      |     | Vdc  |  |  |

|                            |                                                                              | OUT to CASE                                                                           | 1500 |      |     | Vdc  |  |  |

| Reliability                |                                                                              |                                                                                       |      |      |     |      |  |  |

| MTBF                       |                                                                              | MIL-HDBK-217 FN2 Parts Count 25°C<br>Ground Benign, Stationary, Indoors /<br>Computer |      | 3.84 |     | MHrs |  |  |

|                            |                                                                              | Telcordia Issue 2, Method I Case 3, 25°C, 100% D.C., GB, GC                           |      | 8.95 |     | MHrs |  |  |

| Agency Approvals           |                                                                              |                                                                                       |      |      |     |      |  |  |

| Agency approvals/standards |                                                                              |                                                                                       |      |      |     |      |  |  |

|                            | CE Marked for Low Voltage Directive and RoHS Recast Directive, as applicable |                                                                                       |      |      |     |      |  |  |

| Previous Part Number       |                                                                              |                                                                                       |      |      |     |      |  |  |

|                            |                                                                              | NOT APPLIED                                                                           |      |      |     |      |  |  |

#### **Pin Functions**

#### +IN, -IN

Input power pins. -IN is the reference for all control pins, and therefore a Kelvin connection for the control signals is recommended as close as possible to the pin on the package, to reduce effects of voltage drop due to -IN currents.

#### +OUT, -OUT

Output power pins.

#### EN (Enable)

The EN pin provides two functionalities:

- Enables and disables the DCM converter.

- Selects Array mode or Enhanced V<sub>OUT</sub> Regulation mode.

The EN pin is referenced to the –IN pin of the converter. It has an internal pull up to  $V_{CC}$  through a  $10k\Omega$  resistor.

EN is an input only, it does not pull low in the event of a fault.

#### Enable/Disable Control

- Output disable: when EN is pulled down externally below the disable threshold (V<sub>ENABLE-DIS-TH</sub>), the DCM converter will be disabled.

- Output enable: when EN is allowed to pull up above the enable threshold (V<sub>ENABLE-EN-TH</sub>) through the internal pull up to V<sub>CC</sub>, the DCM converter will be enabled.

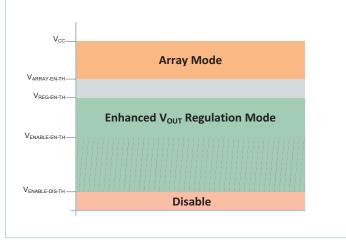

Figure 22 — EN pin voltage thresholds

Selecting Array Mode or Enhanced  $V_{OUT}$  Regulation Mode The EN pin can also be used to select Array mode operation or Enhanced  $V_{OUT}$  Regulation mode operation. The DCM mode of operation is dependent on the voltage seen by the DCM at its EN pin at first start up following application of  $V_{IN}$ . The DCM will latch in selected mode of operation at the end of soft start, and persist in that same mode until loss of input voltage.

At the first start up after application of V<sub>IN</sub>, if EN is allowed to float to:

- A value above V<sub>ENABLE-EN-TH</sub>, but below V<sub>REG-EN-TH</sub>, the DCM will implement Enhanced V<sub>OUT</sub> Regulation mode.

- $\blacksquare$  A value above  $V_{ARRAY-EN-TH}$  and up to  $V_{CC}$  , the DCM will implement array mode operation.

Note that the selected mode of operation is not changed when a DCM recovers from any fault condition, or after a disable event through EN. The operation mode is reset only with cycling of input power.

### TR (Trim)

The TR pin is used to select the trim mode and to trim the output voltage of the DCM converter. The TR pin has an internal pull-up to  $V_{CC}$  through a 10.0  $k\Omega$  resistor.

The DCM will latch trim behavior at application of  $V_{\rm IN}$  (once  $V_{\rm IN}$  exceeds  $V_{\rm IN-UVLO+}$ ), and persist in that same behavior until loss of input voltage.

- At application of  $V_{IN}$ , if the voltage on TR is sampled at above  $V_{TRIM-DIS-TH}$ , the module will latch in a non-trim mode, and will ignore the TR input for as long as  $V_{IN}$  is present.

- At application of  $V_{\rm IN}$ , if the voltage on TR is sampled at below  $V_{\rm TRIM-EN-TH}$ , the TR will serve as an input to control the real time output voltage, relative to full load, 25°C. It will persist in this behavior until  $V_{\rm IN}$  is no longer present.

If trim is active when the DCM is operating, the TR pin provides dynamic trim control at a typical 30 Hz of -3dB bandwidth over the output voltage. TR also decreases the current limit threshold when trimming above  $V_{\rm OUT-NOM}$ .

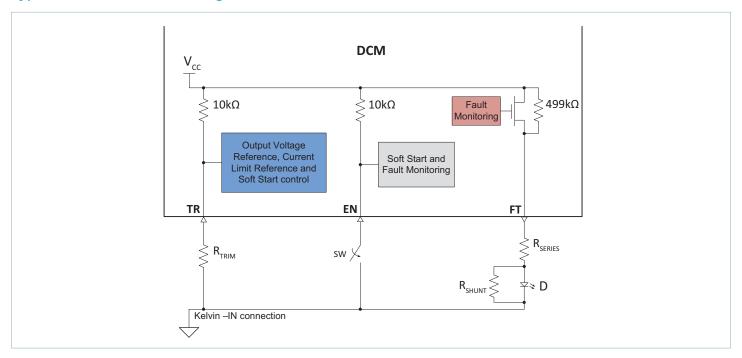

### FT (Fault)

The FT pin provides a Fault signal.

Anytime the module is enabled and has not recognized a fault, the FT pin is inactive. FT has an internal 499 k $\Omega$  pull-up to V<sub>CC</sub>, therefore a shunt resistor, R<sub>SHUNT</sub>, of approximately 50 k $\Omega$  can be used to ensure the LED is completly off when there is no fault, per the diagram below.

Whenever the powertrain stops (due to a fault protection or disabling the module by pulling EN low), the FT pin becomes active and provides current to drive an external circuit.

When active, FT pin drives to  $V_{CC}$ , with up to 4 mA of external loading. Module may be damaged from an over-current FT drive, thus a resistor in series for current limiting is recommended.

The FT pin becomes active momentarily when the module starts up.

## Typical External Circuits for Signal Pins (TR, EN, FT)

## **Design Guidelines**

#### **Building Blocks and System Design**

The DCM™ converter input accepts the full 14 to 72 V range, and it generates an isolated trimmable 24.0 Vdc output. Multiple DCMs may be paralleled in array mode of operation for higher power capacity via wireless load sharing, even when they are operating off of different input voltage supplies.

The DCM converter provides a regulated output voltage around defined nominal load line and temperature coefficients. The load line and temperature coefficients enable configuration of an array of DCM converters which manage the output load with no share bus among modules. Downstream regulators may be used to provide tighter voltage regulation, if required.

The DCM2322x72S26A0y6z may be used in standalone applications where the output power requirements are up to 100 W or applicaions requires tighter voltage regultion. However, it is easily deployed as arrays of modules to increase power handling capacity. Arrays of up to eight units have been qualified for 800 W capacity. Application of DCM converters in an array requires no derating of the maximum available power versus what is specified for a single module.

Note: For more information on operation of single DCM, refer to "Single DCM as an Isolated, Regulated DC-DC Converter" application note AN:029.

#### **Soft Start**

When the DCM starts, it will go through a soft start. The soft start routine ramps the output voltage by modulating the internal error amplifier reference. This causes the output voltage to approximate a piecewise linear ramp. The output ramp finishes when the voltage reaches either the nominal output voltage, or the trimmed output voltage in cases where trim mode is active.

During soft-start, the maximum load current capability is reduced. Until Vout achieves at least  $V_{OUT\text{-}FL\text{-}THRESH}$ , the output current must be less than  $I_{OUT\text{-}START}$  in order to guarantee startup. Note that this is current available to the load, above that which is required to charge the output capacitor.

#### **Nominal Output Voltage Load Line**

#### DCM in Array Mode

Throughout this document, the programmed output voltage, (either the specified nominal output voltage if trim is inactive or the trimmed output voltage if trim is active), is specified at full load, and at room temperature. The actual output voltage of the DCM is given by the programmed trimmed output voltage, with modification based on load and temperature. The nominal output voltage is 24.0 V, and the actual output voltage will match this at full load and room temperature with trim inactive.

The largest modification to the actual output voltage compared to the programmed output is due to the 5.263%  $V_{OUT\text{-}NOM}$  load line, which for this model corresponds to  $\Delta V_{OUT\text{-}LOAD}$  of 1.2631V. As the load is reduced, the internal error amplifier reference, and by extension the output voltage, rises in response. This load line is the primary enabler of the wireless current sharing amongst an array of DCMs.

The load line impact on the output voltage is absolute, and does not scale with programmed trim voltage.

For a given programmed output voltage, the actual output voltage versus load current at <u>for nominal trim and room temperature</u> is given by the following equation:

$$V_{OUT}$$

@  $25^{\circ} = 24.0 + 1.2631 \cdot (1 - I_{OUT} / 4.20)$  (1) Use 0 V for  $\Delta V_{OUT-LL}$  when load is above 10% of rated load. See section on light load boosting operation for light load effects on output voltage.

#### DCM in Enhanced V<sub>OUT</sub> Regulation Mode

In Enhanced  $V_{\text{OUT}}$  Regulation mode, output voltage is not a function of load line.

#### **Nominal Output Voltage Temperature Coefficient**

#### DCM in Array Mode

A second additive term to the programmed output voltage is based on the temperature of the module. This term permits improved thermal balancing among modules in an array, especially when the factory nominal trim point is utilized (trim mode inactive). This term is much smaller than the load line described above, representing only a -3.20 mV/°C change. Regulation coefficient is relative to 25°C.

For nominal trim and full load, the output voltage relates to the temperature according to the following equation:

$$V_{OUT\text{-}FL} = 24.0 - 3.200 \cdot 0.001 \cdot (T_{INT} - 25)$$

(2)

where  $T_{\text{INT}}$  is in °C.

The impact of temperature coefficient on the output voltage is absolute, and does not scale with trim or load.

#### DCM in Array Mode

In Enhanced  $V_{\text{OUT}}$  Regulation mode, output voltage is not a function of temperature coefficient.

# Trim Mode and Output Trim Control: DCM in Array and Enhanced V<sub>OUT</sub> Regulation Modes

When the input voltage is initially applied to a DCM, and after  $t_{\rm INIT}$  elapses, the trim pin voltage  $V_{TR}$  is sampled. The TR pin has an internal pull up resistor to  $V_{CC}$ , so unless external circuitry pulls the pin voltage lower, it will pull up to  $V_{CC}$ . If the initially sampled trim pin voltage is higher than  $V_{TRIM\text{-DIS}}$ , then the DCM will disable trimming as long as the  $V_{IN}$  remains applied. In this case, for all subsequent operation the output voltage will be programmed to the nominal. This minimizes the support components required for applications that only require the nominal rated Vout, and also provides the best output setpoint accuracy, as there are no additional errors from external trim components

If at initial application of  $V_{\rm IN}$ , the TR pin voltage is prevented from exceeding  $V_{\rm TRIM-EN}$ , then the DCM will activate trim mode, and it will remain active for as long as  $V_{\rm IN}$  is applied.

$V_{\text{OUT}}$  set point under full load and room temperature can be calculated using the equation below:

$$V_{OUT\text{-}FL} @ 25^{\circ}C = 10.50 + (18.235 \cdot V_{TR}/V_{CC})$$

(3)

Note that the trim mode is not changed when a DCM recovers from any fault condition or being disabled.

Module performance is guaranteed through output voltage trim range  $V_{\text{OUT-TRIMMING}}$ . If  $V_{\text{OUT}}$  is trimmed above this range, then certain combinations of line and load transient conditions may trigger the output OVP.

#### **Overall Output Voltage Transfer Function**

#### DCM in Array Mode

Taking load line (equation 1), temperature coefficient (equation 2) and trim (equation 3) into account, the general equation relating the DC  $V_{OUT}$  to programmed trim (when active), load, and temperature is given by:

$$V_{OUT} = 10.50 + (18.235 \cdot V_{TR}/V_{CC}) + 1.2631 \cdot (1 - I_{OUT} / 4.20) -3.200 \cdot 0.001 \cdot (T_{INT} - 25) + \Delta V_{OUT-LL}$$

(4)

### DCM in Enhanced V<sub>OUT</sub> Regulation Mode

In Enhanced  $V_{OUT}$  Regulation Mode, only trim (Equation 3) is applicable. The general equation relating the DC  $V_{OUT}$  to programmed trim is given by:

$$V_{OUT} = 10.50 + (18.235 \cdot V_{TR}/V_{CC}) + \Delta V_{OUT-LL}$$

(5)

Finally, note that when the load current is below 10% of the rated capacity, there is an additional  $\Delta V$  which may add to the output voltage, depending on the line voltage which is related to light load boosting. Please see the section on light load boosting below for details.

Use 0 V for  $\Delta V_{OUT-LL}$  when load is above 10% of rated load. See section on light load boosting operation for light load effects on output voltage.

#### **Output Current Limit**

The DCM features a fully operational current limit which effectively keeps the module operating inside the Safe Operating Area (SOA) for all valid trim and load profiles. The current limit approximates a "brick wall" limit, where the output current is prevented from exceeding the current limit threshold by reducing the output voltage via the internal error amplifier reference. The current limit threshold at nominal trim and below is typically 120% of rated output current, but it can vary between 100% to 140%. In order to preserve the SOA, when the converter is trimmed above the nominal output voltage, the current limit threshold is automatically reduced to limit the available output power.

When the output current exceeds the current limit threshold, current limit action is held off by 1ms, which permits the DCM to momentarily deliver higher peak output currents to the load. Peak output power during this time is still constrained by the internal Power Limit of the module. The fast Power Limit and relatively slow Current Limit work together to keep the module inside the SOA. Delaying entry into current limit also permits the DCM to minimize droop voltage for load steps.

Sustained operation in current limit is permitted, and no derating of output power is required, even in an array configuration.

Some applications may benefit from well matched current distribution, in which case fine tuning sharing via the trim pins permits control over sharing. The DCM does not require this for proper operation, due to the power limit and current limit behaviors described here.

Current limit can reduce the output voltage to as little as the UVP threshold ( $V_{OUT-UVP}$ ). Below this minimum output voltage compliance level, further loading will cause the module to shut down due to the output undervoltage fault protection.

## Line Impedance, Input Slew rate and Input Stability Requirements

Connect a high-quality, low-noise power supply to the +IN and -IN terminals. Additional capacitance may have to be added between +IN and -IN to make up for impedances in the interconnect cables as well as deficiencies in the source.

Excessive source impedance can bring about system stability issues for a regulated DC-DC converter, and must either be avoided or compensated by filtering components. A 1000  $\mu F$  input capacitor is the minimum recommended in case the source impedance is insufficient to satisfy stability requirements.

Additional information can be found in the filter design application note:

www.vicorpower.com/documents/application\_notes/vichip\_appnote23.pdf

Please refer to this input filter design tool to ensure input stability: <a href="http://app2.vicorpower.com/filterDesign/intiFilter.do">http://app2.vicorpower.com/filterDesign/intiFilter.do</a>.

Ensure that the input voltage slew rate is less than 1V/us, otherwise a pre-charge circuit is required for the DCM input to control the input voltage slew rate and prevent overstress to input stage components.

#### **Input Fuse Selection**

The DCM is not internally fused in order to provide flexibility in configuring power systems. Input line fusing is recommended at the system level, in order to provide thermal protection in case of catastrophic failure. The fuse shall be selected by closely matching system requirements with the following characteristics:

- Current rating (usually greater than the DCM converter's maximum current)

- Maximum voltage rating (usually greater than the maximum possible input voltage)

- Ambient temperature

- Breaking capacity per application requirements

- Nominal melting I<sup>2</sup>t

- Recommended fuse: See Agency Approvals for Recommended Fuse <a href="http://www.vicorpower.com/dc-dc/isolated-regulated/dcm#Documentation">http://www.vicorpower.com/dc-dc/isolated-regulated/dcm#Documentation</a>

## **Fault Handling**

#### Input Undervoltage Fault Protection (UVLO)

The converter's input voltage is monitored to detect an input under voltage condition. If the converter is not already running, then it will ignore enable commands until the input voltage is greater than  $V_{\text{IN-UVLO-}}$ . If the converter is running and the input voltage falls below  $V_{\text{IN-UVLO-}}$ , the converter recognizes a fault condition, the powertrain stops switching, and the output voltage of the unit falls.

Input voltage transients which fall below UVLO for less than  $t_{\rm UVLO}$  may not be detected by the fault proection logic, in which case the converter will continue regular operation. No protection is required in this case.

Once the UVLO fault is detected by the fault protection logic, the converter shuts down and waits for the input voltage to rise above  $V_{\rm IN-UVLO+}$ . Provided the converter is still enabled, it will then restart.

## Input Overvoltage Fault Protection (OVLO)

The converter's input voltage is monitored to detect an input over voltage condition. When the input voltage is more than the  $V_{\text{IN-OVLO+}}$ , a fault is detected, the powertrain stops switching, and the output voltage of the converter falls.

After an OVLO fault occurs, the converter will wait for the input voltage to fall below  $V_{\text{IN-OVLO}}$ . Provided the converter is still enabled, the powertrain will restart.

The powertrain controller itself also monitors the input voltage. Transient OVLO events which have not yet been detected by the fault sequence logic may first be detected by the controller if the input slew rate is sufficiently large. In this case, powertrain switching will immediately stop. If the input voltage falls back in range before the fault sequence logic detects the out of range condition, the powertrain will resume switching and the fault logic will not interrupt operation Regardless of whether the powertrain is running at the time or not, if the input voltage does not recover from OVLO before  $t_{\rm OVLO}$ , the converter fault logic will detect the fault.

### Output Undervoltage Fault Protection (UVP)

The converter determines that an output overload or short circuit condition exists by measuring its primary sensed output voltage and the output of the internal error amplifier. In general, whenever the powertrain is switching and the primary-sensed output voltage falls below  $V_{\text{OUT-UVP}}$  threshold, a short circuit fault will be registered. Once an output undervoltage condition is detected, the powertrain immediately stops switching, and the output voltage of the converter falls. The converter remains disabled for a time  $t_{\text{FAULT}}$ . Once recovered and provided the converter is still enabled, the powertrain will again enter the soft start sequence after  $t_{\text{INIT}}$  and  $t_{\text{ON}}$ .

#### Temperature Fault Protections (OTP)

The fault logic monitors the internal temperature of the converter. If the measured temperature exceeds  $T_{\text{INT-OTP}}$ , a temperature fault is registered. As with the under voltage fault protection, once a temperature fault is registered, the powertrain immediately stops switching, the output voltage of the converter falls, and the converter remains disabled for at least time  $t_{\text{FAULT}}$ . Then, the converter waits for the internal temperature to return to below  $T_{\text{INT-OTP}}$  before recovering. Provided the converter is still enabled, the DCM will restart after  $t_{\text{INIT}}$  and  $t_{\text{CN}}$ .

#### Output Overvoltage Fault Protection (OVP)

The converter monitors the output voltage during each switching cycle by a corresponding voltage reflected to the primary side control circuitry. If the primary sensed output voltage exceeds V<sub>OUT-OVP</sub>, the OVP fault protection is triggered. The control logic disables the powertrain, and the output voltage of the converter falls.

This type of fault is latched, and the converter will not start again until the latch is cleared. Clearing the fault latch is achieved by either disabling the converter via the EN pin, or else by removing the input power such that the input voltage falls below  $V_{\text{IN-INIT}}$ .

#### External Output Capacitance

The DCM converter internal compensation requires a minimum external output capacitor. An external capacitor in the range of 470 to 5000  $\mu F$  with ESR of 10 m $\Omega$  is required, per DCM for control loop compensation purposes.

However some DCM models require an increase to the minimum external output capacitor value in certain loading and trim condition. In applications where the load can go below 10% of rated load but the output trim is held constant, the range of output capacitor required is given by  $C_{\text{OUT-EXT-TRANS}}$  in the Electrical Specifications table. If the load can go below 10% of rated load and the DCM output trim is also dynamically varied, the range of output capacitor required is given by  $C_{\text{OUT-EXT-TRANS-TRIM}}$  in the Electrical Specifications table.

## Light Load Boosting

Under light load conditions, the DCM converter may operate in light load boosting depending on the line voltage. Light load boosting occurs whenever the internal power consumption of the converter combined with the external output load is less than the minimum power transfer per switching cycle. In order to maintain regulation, the error amplifier will switch the powertrain off and on repeatedly, to effectively lower the average switching frequency, and permit operation with no external load. During the time when the power train is off, the module internal consumption is significantly reduced, and so there is a notable reduction in no-load input power in light load boosting. When the load is less than 10% of rated Iout, the output voltage may rise by a maximum of 2.53 V, above the output voltage calculated from trim, temperature, and load line conditions.

#### Thermal Design

Based on the safe thermal operating area shown in page 5, the full rated power of the DCM2322x72S26A0y6z can be processed provided that the top, bottom, and leads are all held below 90°C. These curves highlight the benefits of dual sided thermal management, but also demonstrate the flexibility of the Vicor ChiP platform for customers who are limited to cooling only the top or the bottom surface.

The OTP sensor is located on the top side of the internal PCB structure. Therefore in order to ensure effective over-temperature fault protection, the case bottom temperature must be constrained by the thermal solution such that it does not exceed the temperature of the case top.

The ChiP package provides a high degree of flexibility in that it presents three pathways to remove heat from internal power dissipating components. Heat may be removed from the top surface, the bottom surface and the leads. The extent to which these three surfaces are cooled is a key component for determining the maximum power that is available from a ChiP, as can be seen from Figure 23.

Since the ChiP has a maximum internal temperature rating, it is necessary to estimate this internal temperature based on a real thermal solution. Given that there are three pathways to remove heat from the ChiP, it is helpful to simplify the thermal solution into a roughly equivalent circuit where power dissipation is modeled as a current source, isothermal surface temperatures are represented as voltage sources and the thermal resistances are represented as resistors. Figure 23 shows the "thermal circuit" for a 2322 ChiP DCM, in an application where both case top and case bottom, and leads are cooled. In this case, the DCM power dissipation is PD<sub>TOTAL</sub> and the three surface temperatures are represented as T<sub>CASE\_TOP</sub>, T<sub>CASE\_BOTTOM</sub>, and T<sub>LEADS</sub>. This thermal system can now be very easily analyzed with simple resistors, voltage sources, and a current source.

This analysis provides an estimate of heat flow through the various pathways as well as internal temperature.

Figure 23 — Double side cooling and leads thermal model

Alternatively, equations can be written around this circuit and analyzed algebraically:

$$T_{INT} - PD_1 \cdot \theta_{INT-TOP} = T_{CASE\_TOP}$$

$T_{INT} - PD_2 \cdot \theta_{INT-BOTTOM} = T_{CASE\_BOTTOM}$

$T_{INT} - PD_3 \cdot \theta_{INT-LEADS} = T_{LEADS}$

$PD_{TOTAL} = PD_1 + PD_2 + PD_3$

Where  $T_{INT}$  represents the internal temperature and  $PD_1$ ,  $PD_2$ , and  $PD_3$  represent the heat flow through the top side, bottom side, and leads respectively.

Figure 24 — One side cooling and leads thermal model

Figure 24 shows a scenario where there is no bottom side cooling. In this case, the heat flow path to the bottom is left open and the equations now simplify to:

$$T_{INT} - PD_1 \bullet \theta_{INT-TOP} = T_{CASE\_TOP}$$

$T_{INT} - PD_3 \bullet \theta_{INT-LEADS} = T_{LEADS}$

$PD_{TOTAL} = PD_1 + PD_3$

Figure 25 — One side cooling thermal model