# PRM® Regulator PRM48BH480T200B00

# High Efficiency Remote Sense PRM Converter

# **FEATURES**

- 45 V (38 to 55  $V_{\text{IN}}),$  non-isolated ZVS buck-boost regulator

- 5 to 55 V adjustable output range

- Building block for high efficiency DC-DC systems

- 200 W Output Power in 0.57 in<sup>2</sup> footprint

- 97% typical efficiency, at full load

- 1,300 W/in<sup>3</sup> (81 W/cm<sup>3</sup>) Power Density

- Enables a 48 V to 1.5 V, 130 A isolated, regulated solution with total footprint of 1.7 in<sup>2</sup> (11 cm<sup>2</sup>)

- Flexible "Remote Sense" architecture optimizes regulation / feedback loop design to fit application requirements

- Current Feedback signal allows dynamic adjustment of current limit setpoint

- 4.93 MHrs MTBF (MIL-HDBK-217Plus Parts Count)

# **TYPICAL APPLICATIONS**

- High Efficiency Server Processor and Memory Power

- High Density ATE system DC-DC power

- Telecom NPU and ASIC core power

- LED drivers

- High Density Power Supply DC-DC rail outputs

- Non-isolated power converters

# DESCRIPTION

The VI Chip<sup>®</sup> PRM<sup>®</sup> Regulator is a high efficiency converter, operating from a 38 to 55 Vdc input to generate a regulated 5 to 55 Vdc output. The ZVS Buck – Boost topology enables high switching frequency (~1 MHz) operation with high conversion efficiency. High switching frequency reduces the size of reactive components enabling power density up to 1,300 W/in<sup>3</sup>.

The half VI Chip package is compatible with standard pickand-place and surface mount assembly processes with a planar thermal interface area and superior thermal conductivity.

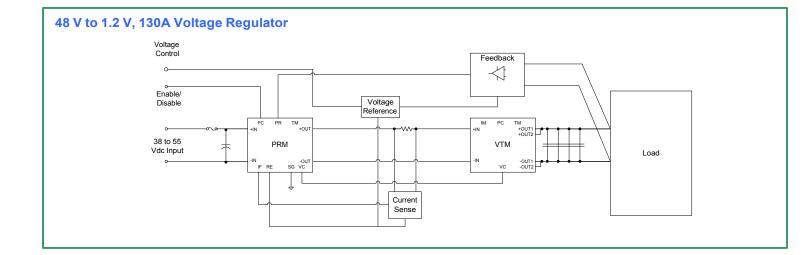

In a Factorized Power Architecture <sup>™</sup> system, the PRM48BH480T200B00 and downstream VTM<sup>®</sup> transformer minimize distribution and conversion losses in a high power solution.

An external control loop and current sensor maintain regulation and enable flexibility both in the design of voltage and current compensation loops to control of output voltages and currents.

# 1.0 ABSOLUTE MAXIMUM RATINGS

The ABSOLUTE MAXIMUM ratings below are stress ratings only. Operation at or beyond these maximum ratings can cause permanent damage to device. Electrical specifications do not apply when operating beyond rated operating conditions. All voltages are specified relative to SG unless otherwise noted. Positive pin current represents current flowing out of the pin.

|                                          | Min  | Max  | Unit |

|------------------------------------------|------|------|------|

| PR                                       | -0.3 | 10.5 | V    |

| PR                                       |      | ±10  | mA   |

| PC                                       | -0.3 | 5.7  | V    |

|                                          |      | ±10  | mA   |

| ™                                        | -0.3 | 5.7  | V    |

| 1111                                     |      | ±1   | mA   |

| +IN to –IN                               | -1   | 62   | V    |

| VS                                       | -0.5 | 10.5 | V    |

| VS                                       |      | ±100 | mA   |

| SG                                       |      | ±100 | mA   |

| F                                        | -0.5 | 5.7  | V    |

| RE                                       | -0.3 | 5    | V    |

| VC to -OUT                               | -0.5 | 18   | V    |

|                                          |      | ±1.8 | Α    |

| +OUT to -OUT                             | -1   | 62   | V    |

| Output Current                           |      | ±5.5 | А    |

| Operating Analog IC Junction Temperature | -40  | 125  | °C   |

| Storage Temperature                      | -40  | 125  | °C   |

#### 2.0 ELECTRICAL CHARACTERISTICS

Specifications apply over all line and load conditions,  $T_J = 25$  °C and output voltage from 20 V to 55 V, unless otherwise noted. Boldface specifications apply over the temperature range of -40 °C <  $T_J$  < 125 °C (T-grade).

| Attribute                             | Symbol                             | Conditions / Notes                                                                                                           | Min   | Тур   | Max          | Unit |

|---------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------------|------|

| POWER INPUT SPECIFICATION             |                                    |                                                                                                                              |       |       |              |      |

| Input Voltage range                   | V <sub>IN</sub>                    |                                                                                                                              | 38    | 45    | 55           | V    |

| V <sub>IN</sub> Slew Rate             | dV <sub>IN</sub> /dt               | 0 < V <sub>IN</sub> < 18 V                                                                                                   | 0.001 |       | 1000         | V/ms |

| No Load Power Dissipation             | P <sub>NL</sub>                    | PC High, V <sub>IN</sub> = 45 V                                                                                              |       | 2.6   | 4            | W    |

| Input Quiescent current               | l <sub>oc</sub>                    | PC Low, V <sub>IN</sub> = 45 V                                                                                               |       | 4.5   | 8.5          | mA   |

| Input Current                         | IIN_DC                             | I <sub>OUT</sub> = 4.17 A, V <sub>IN</sub> = 38 V, V <sub>OUT</sub> = 48 V                                                   |       | 5.5   | 5.7          | Α    |

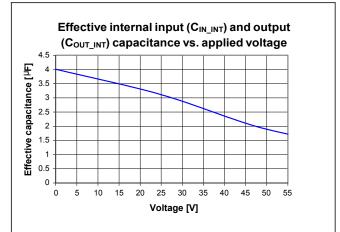

| Input Capacitance (Internal)          |                                    | Effective value, V <sub>IN</sub> = 45 V (see Fig. 20)                                                                        |       | 2     |              | μF   |

| Input Capacitance (Internal) ESR      | R <sub>Cin</sub>                   |                                                                                                                              |       | 3     |              | mΩ   |

| POWER OUTPUT SPECIFICATION            |                                    |                                                                                                                              |       |       |              |      |

| Output Voltage range                  | V <sub>OUT</sub>                   |                                                                                                                              | 5     | 48    | 55           | V    |

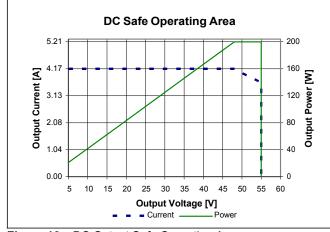

| Output Current                        | I <sub>OUT</sub>                   | See Fig.16, SOA                                                                                                              |       |       | 4.17         | Α    |

| Output Power                          | Pout                               | See Fig.16, SOA                                                                                                              |       |       | 200          | W    |

| Output Tum-ON Delay                   | T <sub>ON</sub>                    | From PC pin release to V <sub>OUT</sub> , V <sub>IN</sub> pre-applied and T <sub>OFF</sub> already expired                   |       | 20    |              | μs   |

| Output Tull-ON Delay                  | T <sub>OFF</sub> + T <sub>ON</sub> | From V <sub>IN</sub> applied to V <sub>OUT</sub> , PC floating                                                               |       | 18.02 |              | ms   |

|                                       |                                    | Equal input, output and PR voltage at full load; V <sub>IN</sub> = 45 V, V <sub>OUT</sub> = 48 V, exclusive of current limit |       |       | ±10          | %    |

| Current Sharing accuracy              | I <sub>OUT_PS</sub>                | Equal input, output and PR voltage at full load;                                                                             |       |       | See sec 10.6 | %    |

|                                       |                                    | Over line, trim, and temperature; exclusive of current limit                                                                 |       |       | See sec 10.0 | 70   |

|                                       |                                    | Nominal line, full load, V <sub>OUT</sub> = 48V                                                                              | 95.7  | 96.9  |              | %    |

| Efficiency                            | η                                  | 50% load and V <sub>OUT</sub> = 48 V; over temperature                                                                       | 94.5  |       |              | %    |

|                                       |                                    | 50% load; over temperature                                                                                                   | 88.5  |       |              | %    |

| Output Discharge current              | I <sub>OD</sub>                    | Section 4.0                                                                                                                  |       | 0.5   |              | mA   |

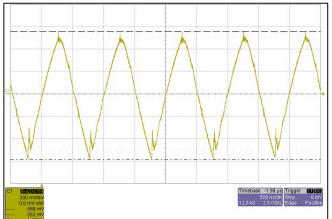

| Output Voltage Ripple                 | V <sub>OUT_PP</sub>                | C <sub>OUT_EXT</sub> = 0 F, I <sub>OUT</sub> = 4.17 A, V <sub>IN</sub> = 45 V, V <sub>OUT</sub> = 48 V, 20 MHz BW            |       | 1020  | 1500         | mV   |

| Output Inductance (Parasitic)         | L <sub>OUT_PAR</sub>               | Frequency @ 1 MHz, Simulated J-Lead model                                                                                    |       | 2.5   |              | nH   |

| Output Capacitance (Internal)         | C <sub>OUT_INT</sub>               | Effective value, V <sub>OUT</sub> = 48 V (see Fig. 20)                                                                       |       | 2     |              | μF   |

| Output Capacitance (Internal) ESR     | R <sub>Cout</sub>                  |                                                                                                                              |       | 3     |              | mΩ   |

| POWERTRAIN PROTECTIONS                |                                    |                                                                                                                              |       |       |              |      |

| Input Undervoltage Turn-ON            | VIN UVLO+                          | Instantanous powertrain shutdown, latched after T <sub>BLANK</sub>                                                           |       | 35.75 | 37.13        | V    |

| Input Undervoltage Turn-OFF           | VIN UVLO-                          |                                                                                                                              | 31.97 | 33.56 |              | V    |

| Input Overvoltage Turn-ON             | VIN OVLO+                          | Instantanous powertrain shutdown, latched after T <sub>BLANK</sub>                                                           | 55.91 | 57.24 |              | V    |

| Input Overvoltage Turn-OFF            | VIN OVLO-                          |                                                                                                                              |       | 58.44 | 59.91        | V    |

| Overcurrent (IF) and Input            | -<br>-                             |                                                                                                                              | 50    | 400   | 450          | μs   |

| Over/Undervoltage Blanking Time       | TBLANK                             |                                                                                                                              | 50    | 120   | 150          | PS   |

| Output Overvoltage Threshold          | V <sub>OUT_OVLO+</sub>             | Instantaneous, latched shutdown                                                                                              | 55.25 | 56.57 | 59.04        | V    |

| Thermal Shutdown Setpoint             | T <sub>J_OTP</sub>                 | Instantaneous, latched shutdown; guaranteed by design, not production tested; $V_{TM}$ = 4.03V                               | 130   |       |              | °C   |

| Overtemperature, Output Overvoltage   | -                                  |                                                                                                                              |       | 2     |              | μs   |

| and PC Shutdown Response Time         | T <sub>PROT</sub>                  |                                                                                                                              |       | 2     |              | P3   |

| Short Circuit Vout Threshold          | V <sub>sc_vout</sub>               |                                                                                                                              |       | 3.0   |              | V    |

| Short Circuit Vout Recovery Threshold | V <sub>SC_VOUTR</sub>              |                                                                                                                              |       | 4.0   |              | V    |

| Short Circuit Vpr Threshold           | V <sub>SC_VPR</sub>                |                                                                                                                              |       | 7.2   |              | V    |

| Short Circuit Vpr Recovery Threshold  | V <sub>SC_VPRR</sub>               |                                                                                                                              |       | 7.1   |              | V    |

| Short Circuit Timeout                 | T <sub>sc</sub>                    | Short Circuit fault latched after V <sub>SC_VOUT</sub> and V <sub>SC_VPR</sub> thresholds persist for this time              |       | 20    |              | ms   |

| Short Circuit Fault Recovery Time     | T <sub>SCR</sub>                   |                                                                                                                              |       | 0.1   |              | ms   |

| Output Power Limit                    | P <sub>PROT</sub>                  |                                                                                                                              | 200   |       |              | w    |

#### 3.0 SIGNAL CHARACTERISTICS

Specifications apply over all line and load conditions,  $T_J = 25$  °C and Output Voltage from 20 V to 55 V, unless otherwise noted. Boldface specifications apply over the temperature range of -40 °C <  $T_J$  < 125 °C (T-grade).

| Primary Control                                            | PC               |                                    |                     |                                                   |      |      |      |      |

|------------------------------------------------------------|------------------|------------------------------------|---------------------|---------------------------------------------------|------|------|------|------|

| . The PC pin enables and disables the                      | PRM              | •                                  |                     |                                                   |      |      |      |      |

| · In PRM array configurations, PC pins                     | should be conne  | ected in order to synchronize sta  | rtup.               |                                                   |      |      |      |      |

| <ul> <li>It is a weak pull-down during any faul</li> </ul> | t mode excluding | short circuit. PC is a strong pull | -down to SG if      | a Short Circuit fault is latched.                 |      |      |      |      |

| Signal Type                                                | State            | Attribute                          | Symbol              | Conditions / Notes                                | Min  | Тур  | Max  | Unit |

| Analog Output                                              | Regular          | PC Voltage                         | V <sub>PC</sub>     |                                                   | 4.7  |      | 5.3  | V    |

|                                                            | Operation        | PC Available Current               | I <sub>PC_OP</sub>  |                                                   | 1.8  |      |      | mA   |

|                                                            | Startup          | PC Source Current                  | I <sub>PC_EN</sub>  | After T <sub>OFF</sub>                            |      | 90   |      | ۲A   |

|                                                            |                  | Minimum Time to Start              | T <sub>OFF</sub>    | Section 5.0                                       | 10.0 | 18.0 | 30.0 | ms   |

|                                                            | Startup          | PC Enable Threshold                | V <sub>PC_EN</sub>  |                                                   |      | 2.50 | 3.20 | V    |

| Digital Input / Output                                     | Standby          | PC Disable Threshold               | V <sub>PC_DIS</sub> |                                                   | 1.75 | 2.40 |      | V    |

|                                                            | Otandby          | PC Resistance to disable           | R <sub>PC_EXT</sub> | Max Resistance to SG required to disable the PRM  |      |      | 300  | Ω    |

| Digital Output [Short Circuit Fault]                       | Fault            | PC Sink Current to SG              | I <sub>PC_SC</sub>  | Short circuit, PC Voltage 1 V or above            |      | 25   |      | mA   |

| Digital Output [All other Faults]                          | Fault            | PC Sink Current to ~1V             | IPC_FAULT           | Temperature, Over- and Under-Voltage, Overcurrent |      | 10   |      | μA   |

| Voltage Source                                                   | VS         | ]                         |                     |                                                                                             |      |      |      |      |  |  |

|------------------------------------------------------------------|------------|---------------------------|---------------------|---------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| Intended to power feedback components and/or auxiliary circuits. |            |                           |                     |                                                                                             |      |      |      |      |  |  |

| Signal Type                                                      | State      | Attribute                 | Symbol              | Conditions / Notes                                                                          | Min  | Тур  | Max  | Unit |  |  |

|                                                                  |            | VS Voltage                | V <sub>vs</sub>     |                                                                                             | 8.55 | 9.00 | 9.45 | V    |  |  |

|                                                                  | Regular    | VS Available Current      | Ivs                 |                                                                                             | 5    |      |      | mA   |  |  |

| Analog Output                                                    | Operation  | VS Voltage Ripple         |                     | lout = 0A, Cvs_ext=0. Maximum specification<br>includes powertrain operation in burst mode. |      | 100  | 400  | mV   |  |  |

|                                                                  | Transition | VS Capacitance (External) | C <sub>VS_EXT</sub> |                                                                                             |      |      | 0.04 | μF   |  |  |

|                                                                  | Transition | VS Fault Response Time    | T <sub>FR_VS</sub>  | From fault recognition to VS = 1.5 V                                                        |      | 30   |      | μs   |  |  |

| Reference Enable                                      | RE                  |                                     |                     |                                                                |     |      |     |      |

|-------------------------------------------------------|---------------------|-------------------------------------|---------------------|----------------------------------------------------------------|-----|------|-----|------|

| RE signals successful startup and                     |                     | •                                   |                     |                                                                |     |      |     |      |

| <ul> <li>Regulated, delayed voltage source</li> </ul> | e intended to power | the reedback circuit voltage refere | nce and curre       | nt monitor                                                     |     |      |     |      |

| Signal Type                                           | State               | Attribute                           | Symbol              | Conditions / Notes                                             | Min | Тур  | Max | Unit |

|                                                       | Regular             | RE Voltage                          | V <sub>RE</sub>     |                                                                | 3.0 | 3.3  | 3.6 | v    |

|                                                       |                     | RE Available Current                | I <sub>RE</sub>     |                                                                | 8.0 |      |     | mA   |

|                                                       | Operation           | RE Regulation                       | % <sub>RE</sub>     | across load and temperature                                    |     | ±2.5 |     | %    |

| Analog Output                                         |                     | RE Voltage Ripple                   | V <sub>RE_PP</sub>  | includes powertrain in burst mode                              |     | 100  |     | mV   |

|                                                       |                     | PC to RE Delay                      | T <sub>PC_RE</sub>  | Fault detected                                                 |     | 100  |     | μs   |

|                                                       | Transition          | RE Capacitance (External)           | C <sub>RE_EXT</sub> |                                                                |     |      | 0.1 | μF   |

|                                                       |                     | VS to RE Delay                      | T <sub>VS_RE</sub>  | VS = 8.1 V to RE high, V <sub>IN</sub> > V <sub>IN_UVLO-</sub> |     | 1    |     | ms   |

| Control Node                                             | PR                   |                                |                 |                         |      |      |      |      |

|----------------------------------------------------------|----------------------|--------------------------------|-----------------|-------------------------|------|------|------|------|

| <ul> <li>Modulator control node input</li> </ul>         |                      |                                |                 |                         |      |      |      |      |

| <ul> <li>Sinks constant current when external</li> </ul> | lly driven           |                                |                 |                         |      |      |      |      |

| <ul> <li>Sources current when pulled below a</li> </ul>  | ctive range          |                                |                 |                         |      |      |      |      |

| Signal Type                                              | State                | Attribute                      | Symbol          | Conditions / Notes      | Min  | Тур  | Max  | Unit |

|                                                          | Regular<br>Operation | PR Voltage Active Range        | V <sub>PR</sub> |                         | 0.79 |      | 7.40 | V    |

| Analog Input                                             |                      | PR Source Current              | I <sub>PR</sub> | V <sub>PR</sub> ≤ 0.79V |      |      | 2    | mA   |

| Analog input                                             |                      | PR Sink Current                | IPR_Low         | V <sub>PR</sub> > 0.79V | 250  | 500  | 750  | ۲A   |

|                                                          |                      | PR Resistance to SG (Internal) | R <sub>PR</sub> |                         |      | 93.3 |      | kΩ   |

Current Feedback • A voltage proportional to the PRM output current must be supplied externally to the IF pin in order for the device to properly protect overcurrent events and to enable output current limit (clamp) Overcurrent protection trip will cause instantaneous powertrain disable, latched after T<sub>BLAN</sub> Signal Type State Attribute Symbol Conditions / Notes Min Тур Мах Unit Current Limit (clamp) Threshold VIF\_IL V<sub>IN</sub> = 45 V; T<sub>J</sub> = 25 °C 1.90 2.00 2.10 v Not Production Tested; Guaranteed by Design; Regular Overcurrent Protection Threshold VIF OC 2.58 2.69 2.80 Analog Input T<sub>J</sub> = 25 °C Operation IF Input Impedance  $\mathbf{R}_{\mathsf{IF}}$ 2.11 2.13 2.15 kΩ Current Limit Bandwidth BWIL kHz 2

| Temperature Monitor                                                          | ТМ                   |                      |                     |                                                                    |      |      |      |            |

|------------------------------------------------------------------------------|----------------------|----------------------|---------------------|--------------------------------------------------------------------|------|------|------|------------|

| The TM pin monitors the internal to     "Power Good" flag to verify that the |                      |                      |                     |                                                                    |      |      |      |            |

| Signal Type                                                                  | State                | Attribute            | Symbol              | Conditions / Notes                                                 | Min  | Тур  | Max  | Unit       |

|                                                                              |                      | TM Voltage           | V <sub>TM</sub>     | Full temperature range                                             | 2.12 |      | 4.04 | V          |

|                                                                              |                      | TM Voltage reference | V <sub>TM_AMB</sub> | T <sub>J</sub> = 27 °C                                             | 2.94 | 3.00 | 3.06 | V          |

| Analog Output                                                                | Regular<br>Operation | TM Voltage Ripple    | V <sub>VS_PP</sub>  | powertrain in burst mode                                           |      | 350  |      | mV         |

|                                                                              | Operation            | TM Available Current | ITM                 |                                                                    | 100  |      |      | μ <b>A</b> |

|                                                                              |                      | TM Gain              | A <sub>TM</sub>     |                                                                    |      | 10   |      | mV/°C      |

| Digital Output [Fault Flag]                                                  | Fault or<br>Standby  | TM Disabled Current  | TM DIS              | DC state with TM Voltage +/- 0.5V. This is a high impedance state. |      | 0.0  |      | mA         |

| Signal Ground                                                                | SG    |                           |                 |                    |      |     |     |      |  |

|------------------------------------------------------------------------------|-------|---------------------------|-----------------|--------------------|------|-----|-----|------|--|

| All control signals must be referenced to this pin, with the exception of VC |       |                           |                 |                    |      |     |     |      |  |

| SG is internally connected to -IN and -OUT                                   |       |                           |                 |                    |      |     |     |      |  |

| Signal Type                                                                  | State | Attribute                 | Symbol          | Conditions / Notes | Min  | Тур | Max | Unit |  |

| Analog Input / Output                                                        | Any   | Maximum Allowable Current | I <sub>SG</sub> |                    | -100 |     | 100 | mA   |  |

| VTM Control                                                                                                                            | VC      |                  |        |                                               |     |     |     |      |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|--------|-----------------------------------------------|-----|-----|-----|------|--|--|

| Pulsed voltage source used to power and synchronize start up of downstream VTM     If not used, must be resistively terminated to -OUT |         |                  |        |                                               |     |     |     |      |  |  |

| Signal Type                                                                                                                            | State   | Attribute        | Symbol | Conditions / Notes                            | Min | Тур | Max | Unit |  |  |

|                                                                                                                                        |         | VC Voltage       | Vvc    | $R_{VC} = 68\Omega$                           | 13  |     |     | v    |  |  |

| Analog Output                                                                                                                          | Startup | VC Current Limit | Ivc    | V <sub>C</sub> = 14 V, V <sub>IN</sub> > 20 V | 200 | 500 |     | mA   |  |  |

|                                                                                                                                        | Stattup | VC duration      | Tvc    |                                               | 7   | 10  | 16  | ms   |  |  |

|                                                                                                                                        |         | VC Slew Rate     | dVC/dt | $R_{VC} = 1k^{\Omega}$                        |     | 20  |     | V/µs |  |  |

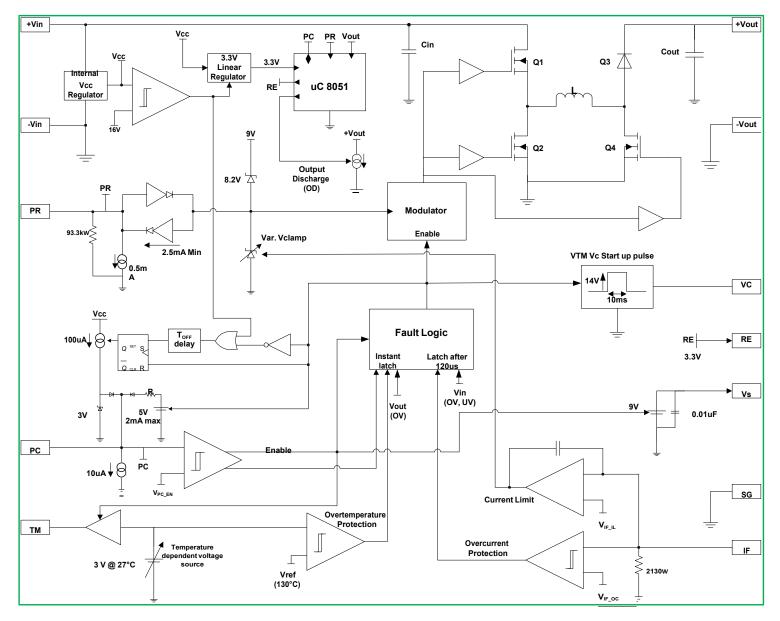

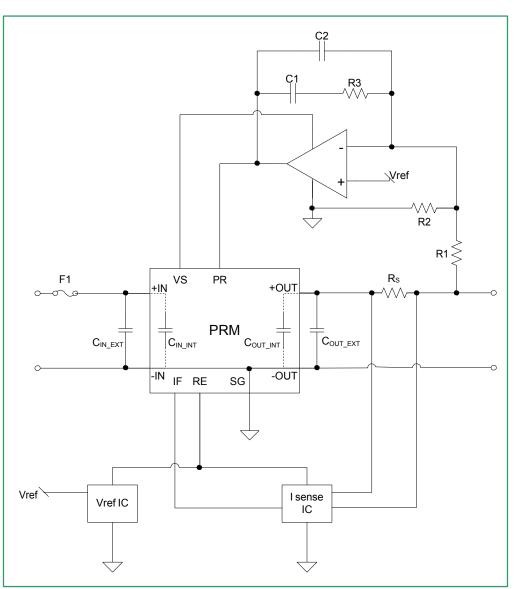

# 4.0 FUNCTIONAL BLOCK DIAGRAM

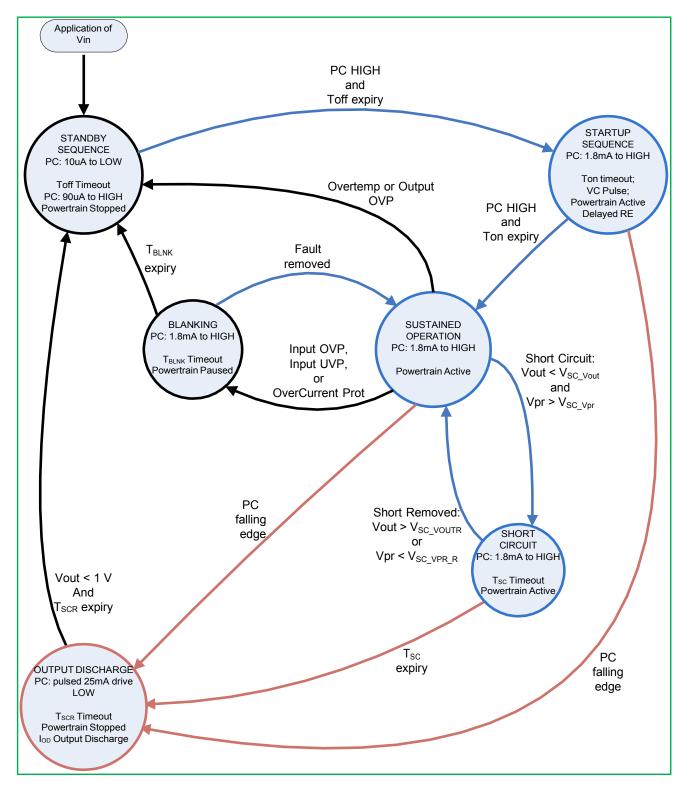

## 5.0 HIGH LEVEL FUNCTIONAL STATE DIAGRAM

Conditions that cause state transitions are shown along arrows. Sub-sequence activities listed inside the state bubbles.

Rev 1.1 7/2015

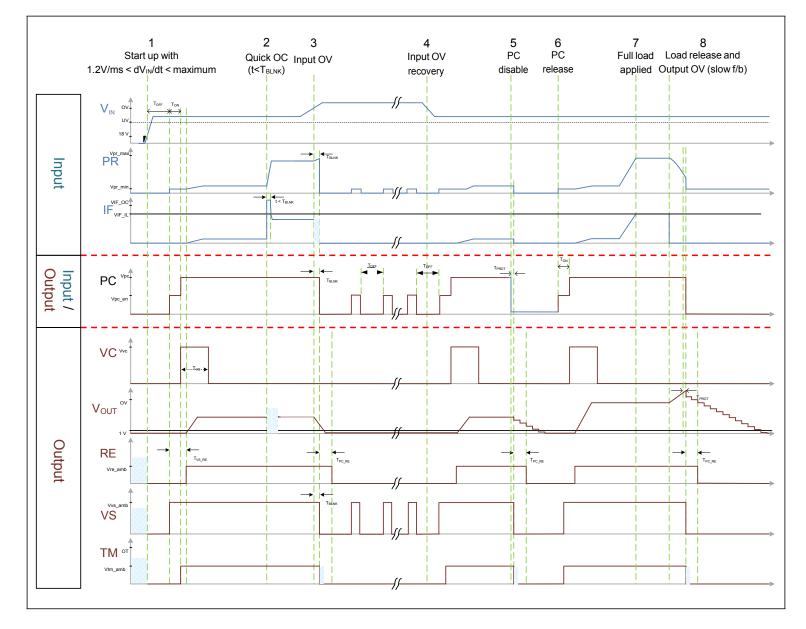

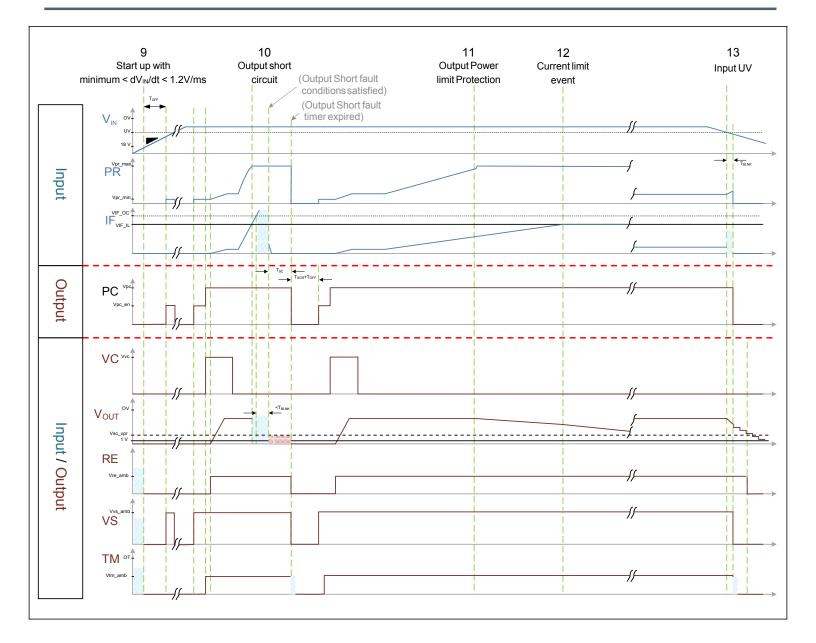

## 6.0 TIMING DIAGRAMS

Module Inputs are shown in blue; Module Outputs are shown in brown; Timing diagrams assumes the following:

- >> Single PRM (no array)

- >> VS powers error amplifier

- >> RE powers voltage reference and output current transducer

- >> I<sub>OUT</sub> is sensed, scaled, and fed back to IF pin such that IF = 2.00 V at full load

### 7.0 APPLICATIONS CHARACTERISTICS

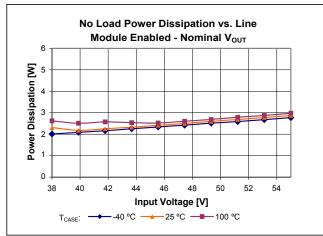

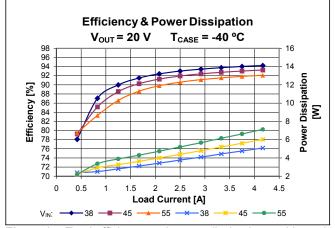

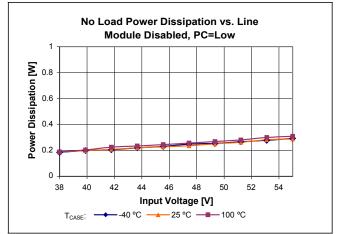

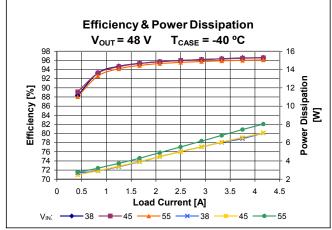

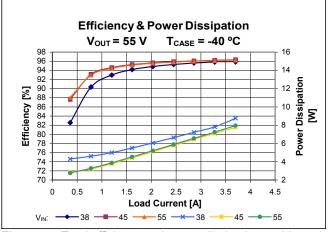

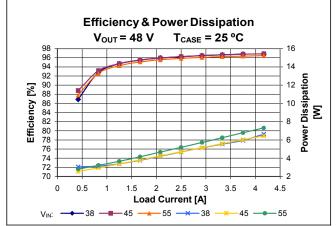

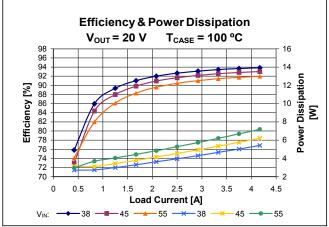

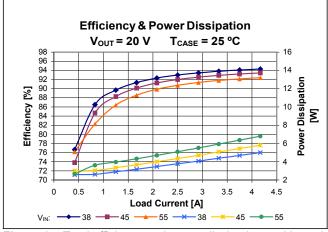

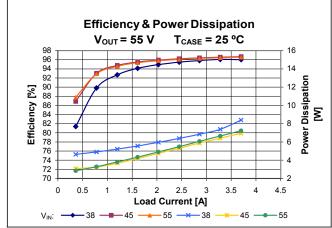

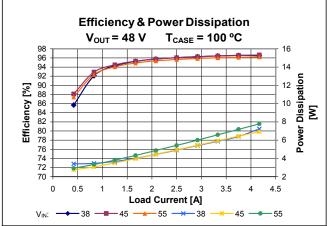

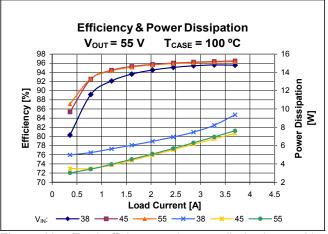

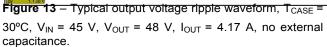

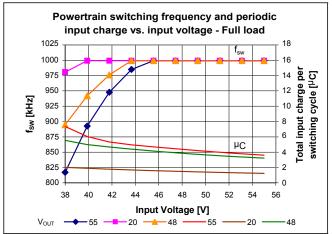

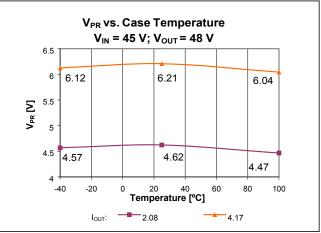

The following figures present typical performance at  $T_c = 25^{\circ}$  C, unless otherwise noted. See associated figures for general trend data.

Figure 1 - No load power dissipation vs.  $V_{\text{IN}},$  module enabled

Figure 3 – Total efficiency and power dissipation vs.  $V_{IN}$  and  $I_{OUT}$ ,  $V_{OUT}$  = 20 V,  $T_{CASE}$  = -40°C

Figure 2 - No load power dissipation vs.  $V_{\text{IN}},$  module disabled

**Figure 4** – Total efficiency and power dissipation vs.  $V_{IN}$  and  $I_{OUT}$ ,  $V_{OUT}$  = 48 V,  $T_{CASE}$  = -40°C

Figure 5 – Total efficiency and power dissipation vs.  $V_{\text{IN}}$  and  $I_{\text{OUT}},\,V_{\text{OUT}}$  = 55 V,  $T_{\text{CASE}}$  = -40°C

Figure 7 – Total efficiency and power dissipation vs.  $V_{\text{IN}}$  and  $I_{\text{OUT}}, V_{\text{OUT}}$  = 48 V,  $T_{\text{CASE}}$  = 25°C

Figure 9 – Total efficiency and power dissipation vs.  $V_{IN}$  and  $I_{OUT},\,V_{OUT}$  = 20 V,  $T_{CASE}$  = 100°C

Figure 6 – Total efficiency and power dissipation vs.  $V_{IN}$  and  $I_{OUT},\,V_{OUT}$  = 20 V,  $T_{CASE}$  = 25°C

Figure 8 – Total efficiency and power dissipation vs.  $V_{\text{IN}}$  and  $I_{\text{OUT}}, V_{\text{OUT}}$  = 55 V,  $T_{\text{CASE}}$  = 25°C

Figure 10 – Total efficiency and power dissipation vs.  $V_{IN}$  and  $I_{OUT}$ ,  $V_{OUT}$  = 48 V,  $T_{CASE}$  = 100°C

Figure 11 – Total efficiency and power dissipation vs.  $V_{\text{IN}}$  and  $I_{\text{OUT}},\,V_{\text{OUT}}$  = 55 V,  $T_{\text{CASE}}$  = 100°C

**Figure 15** – Powertrain switching frequency and periodic input charge vs.  $V_{IN}$ ,  $V_{OUT}$ ;  $I_{OUT}$  = 4.17 A

**Figure 12** – Typical control node voltage vs.  $T_{CASE}$ ,  $I_{OUT}$ ;  $V_{IN}$  = 45 V,  $V_{OUT}$  = 48 V

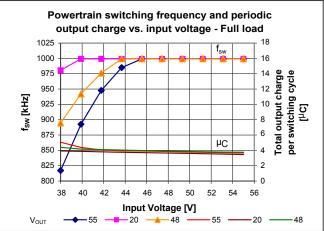

Figure 14 – Powertrain switching frequency and periodic output charge vs.  $V_{IN}$ ,  $V_{OUT}$ ;  $I_{OUT}$  = 4.17 A

Figure 16 – DC Output Safe Operating Area

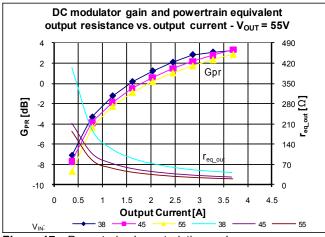

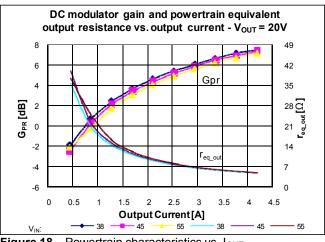

Figure 17 – Powertrain characteristics vs.  $I_{OUT;}$  Resistive load,  $V_{OUT}$  = 55 V, various  $V_{IN}$

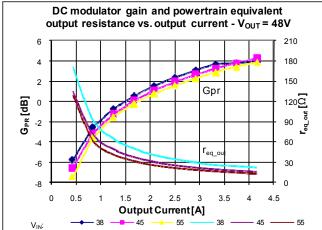

**Figure 19** – Powertrain characteristics vs.  $I_{OUT;}$ Resistive load,  $V_{OUT}$  = 48 V, various  $V_{IN}$

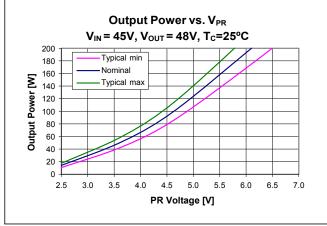

Figure 21 – Output Power vs.  $V_{PR}$ ;  $V_{IN}$  = 45 V,  $V_{OUT}$  = 48 V,  $T_{CASE}$  = 25°C

Figure 18 – Powertrain characteristics vs.  $I_{OUT}$ ; Resistive load,  $V_{OUT}$  = 20 V, various  $V_{IN}$

**Figure 20** – Effective internal input and output capacitance vs. voltage – ceramic type

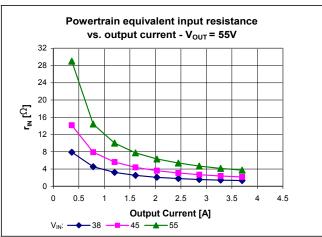

**Figure 22** – Magnitude of powertrain dynamic input impedance vs.  $V_{IN}$ ,  $I_{OUT}$ ;  $V_{OUT}$  = 55 V

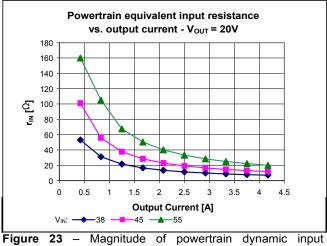

**Figure 23** – Magnitude of powertrain dynamic inpitimpedance vs.  $V_{IN}$ ,  $I_{OUT}$ ;  $V_{OUT}$  = 20 V

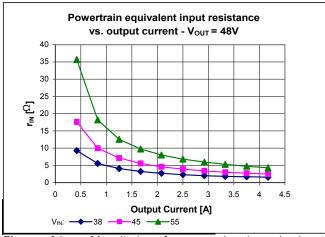

**Figure 24** – Magnitude of powertrain dynamic input impedance vs.  $V_{IN}$ ,  $I_{OUT}$ ;  $V_{OUT}$  = 48 V

# 8.0 GENERAL CHARACTERISTICS

Specifications apply over all line and load conditions,  $T_J = 25$  °C and Output Voltage from 20 V to 55 V, unless otherwise noted. Boldface specifications apply over the temperature range of -40 °C <  $T_J$  < 125 °C (T-grade).

| Attribute                                          | Symbol             | Conditions / Notes                                                                       | Min           | Тур            | Max           | Unit                                |

|----------------------------------------------------|--------------------|------------------------------------------------------------------------------------------|---------------|----------------|---------------|-------------------------------------|

| MECHANICAL                                         |                    |                                                                                          |               |                |               |                                     |

| Length                                             | L                  |                                                                                          | 21.8 / [0.86] | 22.0 / [0.87]  | 22.3 / [0.88] | mm / [in]                           |

| Width                                              | W                  |                                                                                          | 16.3 / [0.64] | 16.5 / [0.65]  | 16.8 / [0.66] | mm / [in]                           |

| Height                                             | Н                  |                                                                                          |               | 6.73 / [0.265] |               |                                     |

| Volume                                             | Vol                | No Heatsink                                                                              |               | 2.44 / [0.15]  |               | cm <sup>3</sup> /[in <sup>3</sup> ] |

| Weight                                             | W                  |                                                                                          |               | 7              |               | q                                   |

|                                                    |                    | Nickel                                                                                   | 0.51          |                | 2.03          |                                     |

| Lead Finish                                        |                    | Palladium                                                                                | 0.02          |                | 0.15          | μm                                  |

|                                                    |                    | Gold                                                                                     | 0.003         |                | 0.050         |                                     |

|                                                    |                    |                                                                                          |               |                |               |                                     |

| THERMAL                                            |                    |                                                                                          |               |                |               |                                     |

| Operating and Storage Junction<br>Temperature      | TJ                 |                                                                                          | -40           |                | 125           | °C                                  |

| Operating Case Temperature                         | Tc                 | Any operating condition                                                                  | -40           |                | 100           | °C                                  |

| Thermal Capacity                                   |                    |                                                                                          |               | 5              |               | Ws/ºC                               |

|                                                    |                    |                                                                                          |               |                |               |                                     |

| ASSEMBLY                                           |                    |                                                                                          |               |                |               |                                     |

| Peak Compressive Force Applied to<br>Case (Z-axis) |                    | Supported by J-Lead only                                                                 |               |                | 3<br>5.33     | lbs<br>lbs/in <sup>2</sup>          |

| Storage Temperature                                | T <sub>ST</sub>    |                                                                                          | -40           |                | 125           | °C                                  |

|                                                    |                    |                                                                                          |               |                |               |                                     |

|                                                    | ESD <sub>HBM</sub> | Human Body Model, "JEDEC JESD 22-A114C.01"                                               | 1000          |                |               |                                     |

| ESD Rating                                         | ESDCDM             | Charged Device Model, "JEDEC JESD 22-C101D"                                              | 400           |                |               | V                                   |

|                                                    | 0.00               |                                                                                          |               |                | I             |                                     |

| SOLDERING                                          |                    |                                                                                          |               |                |               |                                     |

| Peak Temperature During Reflow                     |                    | MSL 4 (Datecode 1528 and later)                                                          |               |                | 245           | °C                                  |

| Maximum Time Above [217] °C                        |                    |                                                                                          | -             |                | 150           | s                                   |

| Peak Heating Rate During Reflow                    |                    |                                                                                          |               | 1.5            | 2             | °C/s                                |

| Peak Cooling Rate Post Reflow                      |                    |                                                                                          |               | 2.5            | 3             | °C/s                                |

| · · · · · · · · · · · · · · · · · · ·              |                    |                                                                                          |               |                |               |                                     |

| SAFETY and RELIABILITY                             |                    |                                                                                          |               |                |               |                                     |

| MTBF                                               |                    | Telcordia Issue 2 - Method I Case 1; Ground Benign, Controlled                           |               | 2.51           |               | MHrs                                |

| WIDF                                               |                    | MIL-HDBK-217Plus Parts Count - 25C Ground Benign, Stationary, Indoors / Computer Profile |               | 4.93           |               | MHrs                                |

|                                                    |                    | <sub>c</sub> TUV <sub>us</sub>                                                           |               |                |               | <u> </u>                            |

| Agency Approvals / Standards                       |                    | CE Mark                                                                                  |               |                |               |                                     |

|                                                    |                    | ROHS 6 of 6                                                                              |               |                |               |                                     |

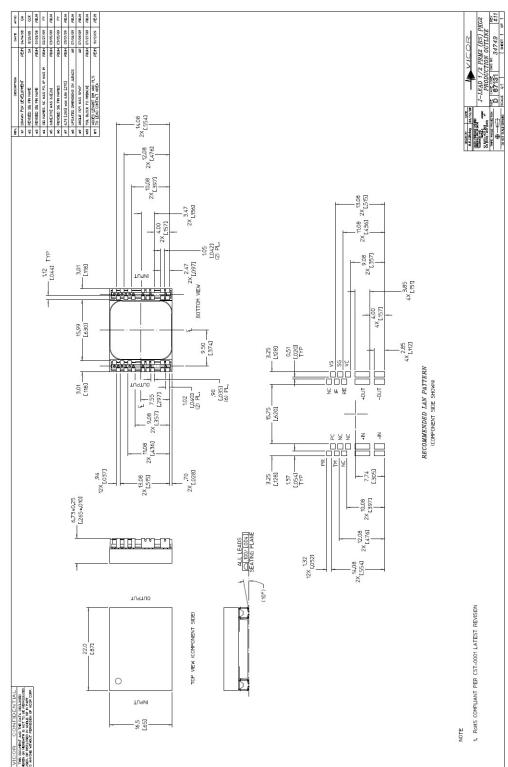

# 9.0 PRODUCT OUTLINE DRAWING AND RECOMMENDED PCB FOOTPRINT

#### 10.1 PRODUCT DETAILS AND DESIGN GUIDELINES

# 10.2 Control pins description and characteristics

**Control node (PR)** is the input to the control node which determines the powertrain timing and ultimately the module output power (Figure 21). An internal 0.5mA current sink is always active. The bi-directional buffer between PR and the control node has two states. In normal operation, PR will be above the 0.79 V switching threshold, and will drive the control node through the buffer. An internal 7.4 V clamp determines the maximum output power that can be requested of the modulator.

When PR falls below 0.79 V, the converter will stop switching. An internal circuit clamps the modulator input control node to 0.79 V, and a buffer will source up to 2.5 mA out of the pin at that clamp level. For this reason, the output impedance of the amplifier driving PR must be taken into account. A rail-to-rail operational amplifier with low output impedance is always recommended.

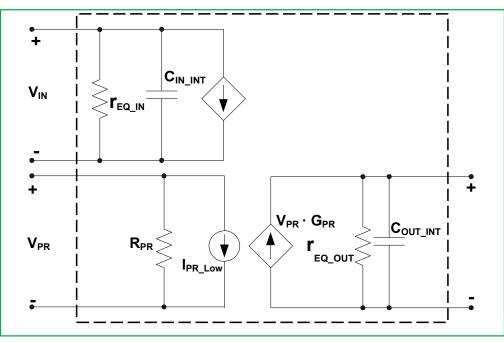

The powertrain small signal (plant) response consists of a single pole determined by the load resistance, the powertrain equivalent output resistance, and the total output capacitance (internal and external to the module). Both the modulator gain and the equivalent output resistance vary as a function of line, load and output voltage, as shown in Figures 17, 18 and 19. As the load increases, the powertrain pole moves to higher frequency. As a result, the closed loop crossover frequency will be the

highest at full load and lowest at minimum load. Figure 25 shows a reference AC small-signal model.

**Current feedback (IF)** is the input for the module output overcurrent protection and current limit features (see functional block diagram in section 4.0). A voltage proportional to the powertrain output current must be applied to IF in order for overcurrent protection to operate properly.

If the IF voltage exceeds the IF pin's overcurrent protection threshold, the powertrain will stop switching. If the IF voltage falls below the overcurrent protection threshold within  $T_{BLANK}$  time, then the powertrain will immediately resumes switching. Otherwise a fault is latched.

The current limit threshold for the IF pin is set lower than the protection threshold. When the IF pin average voltage exceeds the current limit threshold, an internal integrator will activate a clamp amplifier which overrides the modulator input maximum level. This causes the powertrain to maintain a constant output current.

The bandwidth of this current limit integrator is significantly slower than that of the PR control node input. Therefore this current limit can not be used in lieu of properly compensating the (external) PR control loop to avoid exceeding maximum current or power ratings for the device.

If the IF pin is not driven, it must be resistively terminated to SG. A 1 k $\Omega$  resistor to SG is recommended in this case.

Figure 25 – PRM48BH480T200B00 AC small signal model

**VTM Control (VC)** pin supplies an initial  $V_{CC}$  voltage to downstream VTMs, enabling them and synchronizing their startup with the PRM. The  $V_{CC}$  voltage is a pulse, typically 10 ms duration at 14 V.

If VC is not loaded by a VTM, it must be terminated with a 1 k $\Omega$  resistor to –V<sub>OUT</sub>.

**Primary Control (PC)** is both an input and an output. It can provide the following features:

• Delayed start: upon application of voltage (>UVLO) to the module power input and after  $T_{\text{OFF}}$ , the PC pin will source a constant 90  $\mu\text{A}$  current.

• Output disable: PC may be pulled down externally in order to disable the module. Pull down resistance should be less than 300  $\Omega$  to SG.

• Fault detection flag: The PC 5 V voltage source is internally turned off when a fault condition is latched. Note that aside from the Short Circuit fault condition, PC does not have significant current sinking capability. Therefore in the case of an array of PRMs with interconnected PC pins, PC does not in general reflect the fault state of all PRMs. The common PC line will not disable neighboring modules when a fault is detected except for a latched Output Short Circuit fault. Conversely any unit in the array latching a Short Circuit fault will disable the array for T<sub>SCR</sub>.

**Temperature Monitor (TM)** pin outputs a voltage proportional to the absolute temperature of the converter analog control IC. It can be used to accomplish the following functions:

• Monitor the control IC temperature: The gain and setpoint of TM are such that the temperature, in Kelvin, of the PRM controller IC is equal to the voltage on the TM pin scaled by 100. (i.e. 3.0 V = 300 K = 27 °C).

• Closed loop thermal management at the system level (e.g. variable speed fans or coolant flow)

• Fault detection flag: The TM voltage source is turned off as soon as a fault is detected. For system monitoring purposes (microcontroller interface) faults are detected on falling edges of TM.

**Reference Enable (RE)** pin outputs a regulated 3.3 V, 8 mA voltage source. It is enabled only after successful startup of the PRM powertrain (see chapters 5.0 and 6.0.) RE is intended to power the output current transducer and also the voltage reference for the control loop. Powering the reference generator with RE helps provide a controlled startup, since the output voltage of the system is able to track the reference level as it comes up.

**Voltage Source (VS)** pin outputs a gated (e.g. mirrors PC status), non-isolated, regulated 9 V, 5 mA voltage source. It can be used to power external control circuitry; it always leads RE.

**Signal Ground (SG)** pin provides a Kelvin connection to the PRM's internal signal ground. It should be used as the reference for PR, TM, IF, and should return all PC, VS and RE pin currents. In array configurations with common ground control circuits, a series resistor (~1  $\Omega$ ) is recommended in order to decouple power and signal current returns.

10.2 Control circuit requirements and design procedure

The PRM48BH480T200B00 is an intelligent powertrain module designed to fully exploit external output voltage feedback and current sensing sub-circuits. These two external circuits are illustrated in Figure 26, which shows an example of the PRM in a standalone application with local voltage feedback and high side current sensing.

In general, these circuits include a precision voltage reference, an operational amplifier which provides closed loop feedback compensation, and a high side current sense circuit which includes a shunt and current sense IC.

The following design procedures refer to the circuit shown in Figure 26.

10.2.1 Setting the output voltage level

The output voltage setpoint is a function of the voltage reference and the output voltage sense ratio. With reference to Fig. 26, R1 and R2 form the output voltage sensing divider which provides the scaled output voltage to the negative input of the error amplifier; a dedicated reference IC provides the reference voltage to the positive input of the error amplifier. Under normal operation, the error amplifier will keep the voltages at the inverting and non-inverting inputs equal, and therefore the output voltage is defined by:

$$V_{OUT} = V_{ref} \cdot \frac{R1 + R2}{R2}$$

Note that the component R1 will also factor into the compensation as described in a later section.

It is important to apply proper slew rate to the reference voltage rise when the control loop is initially enabled. The recommended range for reference rise time is 1 ms to 9 ms. The lower rise time limit will ensure optimized modulator timing performance during startup, and to allow the current limit feature (through IF pin) to fully protect the device during power-up. The upper rise time limit is needed to guarantee a sufficient factorized bus voltage is provided to any downstream VTM input before the end of the VC pulse. 10.2.2 Setting the output current limit and overcurrent protection level

The current limit and overcurrent protection set points are linked, and scale together against the current sense shunt, and the gain of the current sense amplifier. The output of the current sense IC provides the IF voltage which has  $V_{IF IL}$  and  $V_{IF OC}$  thresholds for the two functions respectively. The set points are therefore defined by:

$$I_{IL} = \frac{V_{IF_{-}IL}}{R_{S} \cdot G_{CS}}$$

and

$$I_{OC} = \frac{V_{IF_OC}}{R_s \cdot G_{CS}}$$

where G<sub>CS</sub> is the gain of the current sense amplifier.

### 10.2.3 Control loop compensation requirements

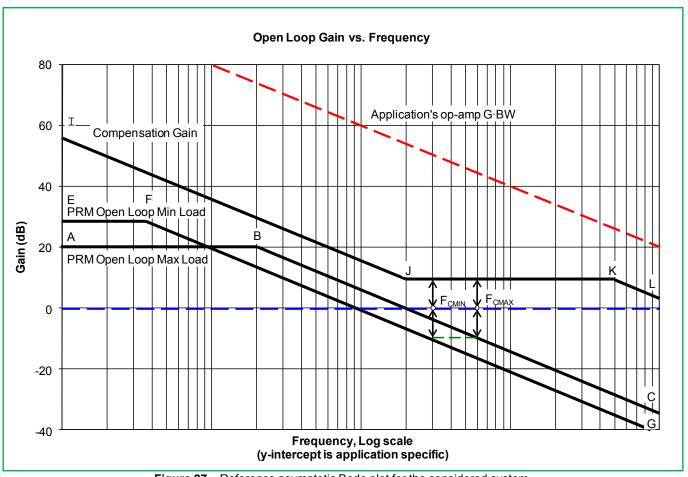

In order to properly compensate the control loop, all components which contribute to the closed loop frequency response should be identified and understood. Figure 25 shows the AC small signal model for the module. Modulator DC transconductance gain (GPR) and powertrain equivalent resistance (r<sub>EQ OUT</sub>) are shown. These modeling parameters will support a design cut-off frequency up to 50 kHz.

Standard Bode analysis should be used for calculating the error amplifier compensation and analyzing the closed loop stability. The recommended stability criteria are as follows:

1) Phase Margin >  $45^{\circ}$ : for the closed loop response, the phase should be greater than 45° where the gain crosses 0dB. 2) Gain Margin > 10dB : The closed loop gain should be

lower than -10dB where the phase crosses 0°.

3) Gain Slope = -20dB / decade : The closed loop gain should have a slope of -20dB / decade at the crossover frequency.

The compensation characteristics must be selected to meet these stability criteria. Refer to Figure 27 for a local sense, voltage-mode control example based on the configuration in Figure 26. In this example, it is assumed that the maximum crossover frequency (F<sub>CMAX</sub>) has been selected to occur between B and C. Type-2 compensation (Curve IJKL) is sufficient in this case.

The following data must be gathered in order to proceed:

- ▶ Modulator Gain G<sub>PR</sub>: See Figures 17, 18, 19

- >> Powertrain equivalent resistance r<sub>EQ</sub>: See Figures 17, 18, 19

>> Internal output capacitance: see Figure 20

>> External output capacitance value

In the case of ceramic capacitors, the ESR can be considered low enough to push the associated zero well above the frequency of interest. Applications with high ESR capacitor may require a different type of compensation, or cascade control.

The system poles and zeros of the closed loop can then be defined as follows:

>> Powertrain pole, assuming the external capacitor ESR can be neglected:

$$R_{C_{OUT\_EXT}} \ll \frac{r_{EQ\_OUT} \cdot R_{LOAD}}{r_{EQ\_OUT} + R_{LOAD}}$$

>> Main pole frequency:

$$F_{p} \approx \frac{1}{2\pi \cdot \frac{r_{EQ_OUT} \cdot R_{LOAD}}{r_{EQ_OUT} + R_{LOAD}} \cdot \left(C_{OUT} + C_{OUT} + C_{OUT}\right)}$$

>> Compensation Mid-Band Gain:

$$G_{\rm MB} = 20 \log \frac{R}{R_1}$$

[1]

>> Compensation Zero:

$$\mathbf{F}_{Z1} = \frac{\mathbf{I}}{2\pi \cdot \mathbf{R}_3 \cdot \mathbf{C}_1}$$

[2]

>> Compensation Pole:

$$F_{P2} = \frac{1}{2\pi \cdot \underline{R_3 \cdot C_1 \cdot C_2}}$$

$$C_1 + C_2$$

vicorpower.com

800 927, 9474

and for  $F_{P2} >> F_{Z1} (C_1 + C_2 \approx C_1)$ :

$$\mathbf{F}_{P2} \approx \frac{1}{2\boldsymbol{\Pi} \cdot \boldsymbol{R}_3 \cdot \boldsymbol{C}_2}$$

[3]

# 10.2.4 Midband Gain Design (R1,R3):

With reference to Figure 27: curve ABC is the:

- >> minimum output voltage in the application

- >> maximum input voltage expected in the application

- >> maximum load

PRM open loop response, and is where the maximum crossover frequency occurs. In order for the maximum crossover frequency to occur at the design choice  $F_{CMAX}$ , the compensation gain must be equal and opposite of the powertrain gain at this frequency. For stability purposes, the compensation should be in the Mid-band (J-K) at the crossover. Using Equation [1], the mid-band gain can be selected appropriately.

10.2.5 Compensation Zero Design (C1):

With reference to Figure 27: curve EFG is the:

- >> maximum output voltage in the application

- >> minimum input voltage expected in the application

- >> minimum load in the application

PRM open loop response, and is where the minimum crossover frequency  $F_{CMIN}$  occurs. Based on stability criteria, the compensation must be in the mid-band at the minimum crossover frequency, therefore  $F_{CMIN}$  will occur where EFG is equal and opposite of  $G_{MB}$ . C1 can be selected using Equation [2] so that  $F_{Z1}$  occurs prior to  $F_{CMIN}$ .

Figure 26 - Control circuit example

Figure 27 – Reference asymptotic Bode plot for the considered system

10.2.6 High Frequency Pole Design (C2):

Using Equation [3], C2 should be selected so that  $F_{P2}$  is at least one decade above  $F_{CMAX}$  and prior to the gain bandwidth product of the operational amplifier (10 MHz for this example). For applications with a higher desired crossover frequency the use of a high gain bandwidth product amplifier may be necessary to ensure that the real pole can be set at least one decade above the maximum crossoverfrequency.

10.2.7 Verifying Stability:

The preferred method for verifying stability is to use a network analyzer, measuring the closed loop response across various lines and load conditions.

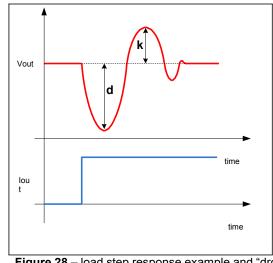

In the absence of a network analyzer, a load step transient response can be used in order to estimate stability.

Figure 28 illustrates an example of a load step response. Equation [4] can be used to predict the phase margin

based on the ratio of the "kick" to "droop" (as defined in Fig. 28).

Figure 28 – load step response example and "droop" vs. "kick" definition

$$\Phi_m \approx 100 \sqrt{\frac{\ln \frac{k^2}{\ln \frac{d}{d}}}{\ln \frac{k^2}{d}}} + \pi^2}$$

[4]

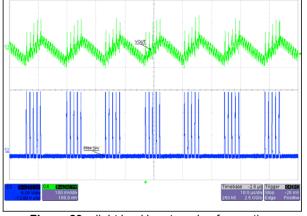

10.3 Burst Mode Operation:

At light loads, the PRM will operate in a burst mode due to minimum timing constraints. An example burst operation waveform is illustrated in Figure 29.

For very light loads, and also for higher input voltages, the minimum time power switching cycle from the powertrain will exceed the power required by the load. In this case the external error amplifier will periodically drive PR below the switching threshold in order to maintain regulation. Switching will cease momentarily until the error amplifier once again drives PR voltage above the threshold.

Figure 29 – light load burst mode of operation

Note that during the bursts of switching, the powertrain frequency is constant, but the number of pulses as well as the time between bursts is variable. The variability depends on many factors including input voltage, output voltages, load impedance, and external error amplifier output impedance.

In burst mode, the gain of the PR input to the plant which is modeled in the previous sections is time varying. Therefore the small signal analysis can not be directly applied to burst mode operation.

# 10.4 Input and Output filter design

Figures 14 and 15 provide the total input and output charge per cycle, as well as switching frequency, of the PRM at full load under various input and output voltages conditions.

Figure 20 provides the effective internal capacitance of the module. A conservative estimate of input and output peakpeak voltage ripple at nominal line and trim is provided by equation [5]:

$$\Delta V = \frac{Q_{TOT} - \frac{I \cdot 0.4}{f_{SW}}}{C_{INT} + C_{EXT}}$$

[5]

$Q_{TOT}$  is the total input (Fig. 15) or output (Fig. 14) charge per switching cycle at full load, while  $C_{INT}$  is the module internal effective capacitance at the considered voltage (Fig. 20) and  $C_{EXT}$  is the external effective capacitance at the considered voltage.

# 10.5 Input filter stability

The PRM can provide very high dynamic transients. It is therefore very important to verify that the voltage supply source as well as the interconnecting line are stable and do not oscillate. For this purpose, the converter dynamic input impedance magnitude  $|r_{EQ\_IN}|$  is provided in Figures 22, 23, 24. It is recommended to provide adequate design margin with respect to the stability conditions illustrated in 10.5.1 and 10.5.2.

10.5.1 Inductive source and local, external input decoupling capacitance with negligible ESR (i.e.: ceramic type)

The voltage source impedance can be modeled as a series  $R_{\text{line}}L_{\text{line}}$  circuit. The high performance ceramic decoupling capacitors will not significantly damp the network because of their low ESR; therefore in order to guarantee stability the following conditions must be verified:

$$R_{line} > \frac{L_{line}}{(C_{IN} + C_{IN}) \cdot |r_{EQ}|}$$

[6]

$$R_{line} << |r_{EQ_{IN}}|$$

<sup>[7]</sup>

It is critical that the line source impedance be at least an octave lower than the converter's dynamic input resistance, [7]. However, R<sub>line</sub> cannot be made arbitrarily low otherwise equation [6] is violated and the system will show instability, due to under-damped RLC input network.

10.5.2 Inductive source and local, external input decoupling capacitance with significant  $R_{CIN\_EXT}$  ESR (i.e.: electrolytic type)

In order to simplify the analysis in this case, the voltage source impedance can be modeled as a simple inductor  $L_{\text{line}}$ . Notice that, the high performance ceramic capacitors  $C_{\text{IN\_INT}}$  within the PRM should be included in the external electrolytic capacitance value for this purpose. The stability criteria will be

$$\left| r_{EQ\_IN} \right| > R_{C_{IN\_EXT}}$$

[8]

$$\frac{L_{line}}{C_{IN\_EXT} \cdot R_{C_{IN\_EXT}}} < |r_{EQ\_IN}|$$

[9]

Equation [9] shows that if the aggregate ESR is too small – for example by using very high quality input capacitors  $(C_{IN\_EXT})$  – the system will be under-damped and may even become destabilized. Again, an octave of design margin in satisfying [8] should be considered the minimum.

## 10.6 Arrays

Up to ten PRMs of the same type may be placed in parallel to expand the power capacity of the system. The following high-level guidelines must be followed in order for the resultant system to start up and operate properly, and to avoid overstress or exceeding any absolute maximum ratings.

- IN pins of all PRMs must be connected together. Both inductance and resistance from the common power source to each PRM should be minimized, and matched.

- Input voltage to all PRMs must be the same. Independent fuses for each PRM are recommended.

- PC pins must be connected together for synchronization and proper fault response.

- Reference supply to the control loop voltage reference and current sense circuitry must be enabled when all modules' RE pins have reached their operational voltage levels.

- >> There must be one single external voltage control loop. The control loop must drive each PR pin relative to each module's SG pin, and the local PR voltage must be the same across all modules.

- >> Each PRM must have its own local current shunt and current sense circuitry to drive its IF pin.

- The number of PRMs required to achieve a given array capacity must consider all sources of mismatch to avoid overstress of any PRM in the array. Imbalances in sharing are not only due to current sharing accuracy specifications, but also

temperature differences among PRMs, Vin variations, and error terms in the buffering of the error amplifier output to the PR pins.

Control loop compensation procedures above will hold for an array, in general, although many parameters must be scaled against the number of PRMs in the system.

Please contact Vicor Applications for assistance.

10.7 Input Fuse Recommendations

A fuse should be incorporated at the input to each PRM, in series with the +IN pin. A 10 A or smaller input fuse (Littelfuse<sup>®</sup> NANO<sup>2®</sup> 451/453 Series, or equivalent) is required to safety agency conditions of acceptability. Always ascertain and observe the safety, regulatory, or other agency specifications that apply to your specific application.

# 10.8 Layout considerations

Application Note AN:005 details board layout using VI Chip components. Additional consideration must be given to the external control circuit components.

The current sense shunt signal voltage is highly sensitive to noise. As such, current sensing circuitry should be located close to the shunt to minimize the length of the sense signals. A Kelvined connection at the shunt is recommended for best results.

The control signal from a remote voltage sense circuit to the PRM should be shielded. Avoid routing this, or other control signals directly underneath the PRM, if possible. Components that tie directly to the PRM should be located close to their respective pins. It is also critical that all control components be referenced to SG, and that SG not be tied to any other ground in the system, including –IN or –OUT of the PRM.

# Warranty

Vicor products are guaranteed for two years from date of shipment against defects in material or workmanship when in normal use and service. This warranty does not extend to products subjected to misuse, accident, or improper application or maintenance. Vicor shall not be liable for collateral or consequential damage. This warranty is extended to the original purchaser only.

EXCEPT FOR THE FOREGOING EXPRESS WARRANTY, VICOR MAKES NO WARRANTY, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

Vicor will repair or replace defective products in accordance with its own best judgment. For service under this warranty, the buyer must contact Vicor to obtain a Return Material Authorization (RMA) number and shipping instructions. Products returned without prior authorization will be returned to the buyer. The buyer will pay all charges incurred in returning the product to the factory. Vicor will pay all reshipment charges if the product was defective within the terms of this warranty.

Information published by Vicor has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. Vicor reserves the right to make changes to any products without further notice to improve reliability, function, or design. Vicor does not assume any liability arising out of the application or use of any product or circuit; neither does it convey any license under its patent rights nor the rights of others. Vicor general policy does not recommend the use of its components in life support applications wherein a failure or malfunction may directly threaten life or injury. Per Vicor Terms and Conditions of Sale, the user of Vicor components in life support applications assumes all risks of such use and indemnifies Vicor against all damages.

# Vicor's comprehensive line of power solutions includes high density AC-DC and DC-DC modules and accessory components, fully configurable AC-DC and DC-DC power supplies, and complete custom power systems.

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor components are not designed to be used in applications, such as life support systems, wherein a failure or malfunction could result in injury or death. All sales are subject to Vicor's Terms and Conditions of Sale, which are available upon request.

# Specifications are subject to change without notice.

# **Intellectual Property Notice**

Vicor and its subsidiaries own Intellectual Property (including issued U.S. and Foreign Patents and pending patent applications) relating to the products described in this data sheet. Interested parties should contact Vicor's Intellectual Property Department.

The products described on this data sheet are protected by the following U.S. Patents Numbers: 5,945,130; 6,403,009; 6,710,257; 6,911,848; 6,930,893; 6,934,166; 6,940,013; 6,969,909; 7,038,917; 7,145,186; 7,166,898; 7,187,263; 7,202,646; 7,361,844; D496,906; D505,114; D506,438; D509,472; and for use under 6,975,098 and 6,984,965.

Vicor Corporation 25 Frontage Road Andover, MA, USA 01810 Tel: 800-735-6200 Fax: 978-475-6715

email Customer Service: custserv@vicorpower.com Technical Support: apps@vicorpower.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management IC Development Tools category:

Click to view products by Vicor manufacturer:

Other Similar products are found below :

EVAL-ADM1168LQEBZ EVB-EP5348UI MIC23451-AAAYFLEV MIC5281YMMEEV DA9063-EVAL ADP122-3.3-EVALZ ADP130-0.8-EVALZ ADP130-1.2-EVALZ ADP130-1.5-EVALZ ADP130-1.8-EVALZ ADP1714-3.3-EVALZ ADP1716-2.5-EVALZ ADP1740-1.5-EVALZ ADP1752-1.5-EVALZ ADP1828LC-EVALZ ADP1870-0.3-EVALZ ADP1871-0.6-EVALZ ADP1873-0.6-EVALZ ADP1874-0.3-EVALZ ADP1882-1.0-EVALZ ADP199CB-EVALZ ADP2102-1.25-EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2-EVALZ ADP1882-1.0-EVALZ ADP199CB-EVALZ ADP2106-1.8-EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2-EVALZ ADP2102-3-EVALZ ADP2102-4-EVALZ ADP2106-1.8-EVALZ ADP2147CB-110EVALZ AS3606-DB BQ24010EVM BQ24075TEVM BQ24155EVM BQ24157EVM-697 BQ24160EVM-742 BQ24296MEVM-655 BQ25010EVM BQ3055EVM NCV891330PD50GEVB ISLUSBI2CKIT1Z LM2744EVAL LM2854EVAL LM3658SD-AEV/NOPB LM3658SDEV/NOPB LM3691TL-1.8EV/NOPB LM4510SDEV/NOPB LM5033SD-EVAL LP38512TS-1.8EV EVAL-ADM1186-1MBZ EVAL-ADM1186-2MBZ