# 16-Channel Wideband Video Multiplexers

## **DESCRIPTION**

The DG535/536 are 16-channel multiplexers designed for routing one of 16 wideband analog or digital input signals to a single output. They feature low input and output capacitance, low on-resistance, and n-channel DMOS "T" switches, resulting in wide bandwidth, low crosstalk and high "off" isolation. In the on state, the switches pass signals in either direction, allowing them to be used as multiplexers or as demultiplexers.

On-chip address latches and decode logic simplify microprocessor interface. Chip Select and Enable inputs simplify addressing in large matrices. Single-supply operation and a low 75  $\mu$ W power consumption vastly reduces power supply requirements.

Theses devices are built on a proprietary D/CMOS process which creates low-capacitance DMOS FETs and high-speed, low-power CMOS logic on the same substrate.

For more information please refer to Vishay Siliconix Application Note AN501 (FaxBack document number 70608).

#### **FEATURES**

- Crosstalk: 100 dB at 5 MHz

- 300 MHz Bandwidth

- · Low Input and Output Capacitance

- Low Power: 75 μW

- Low  $r_{DS(on)}$ : 50  $\Omega$

- On-Board Address Latches

- Disable Output

## **BENEFITS**

- High Video Quality

- Reduced Insertion Loss

- Reduced Input Buffer Requirements

- Minimizes Power Consumption

- · Simplifies Bus Interface

## **APPLICATIONS**

- Video Switching/Routing

- · High Speed Data Routing

- RF Signal Multiplexing

- · Precision Data Acquisition

- Crosspoint Arrays

- FLIR Systems

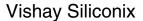

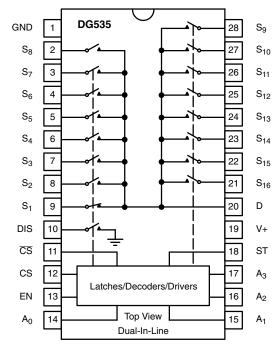

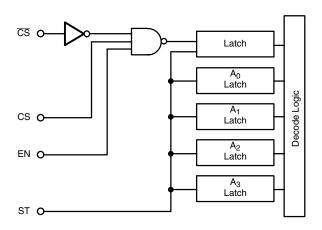

## **FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION**

<sup>\*</sup> Pb containing terminations are not RoHS compliant, exemptions may apply

Pb-free Available

RoHS<sup>3</sup>

| ORDERING INFORMATION |                    |                       |  |  |  |  |  |

|----------------------|--------------------|-----------------------|--|--|--|--|--|

| Temperature Range    | Package            | Part Number           |  |  |  |  |  |

| - 40 to 85 °C        | 28-Pin Plastic DIP | DG535DJ<br>DG535DJ-E3 |  |  |  |  |  |

|                      | 44-Pin PLCC        | DG536DN<br>DG536DN-E3 |  |  |  |  |  |

| TRUT | RUTH TABLE |    |                 |                |                |                                                |                                                               |                                     |                      |  |

|------|------------|----|-----------------|----------------|----------------|------------------------------------------------|---------------------------------------------------------------|-------------------------------------|----------------------|--|

| EN   | cs         | CS | ST <sup>a</sup> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> A <sub>0</sub> Channel Selected | A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> Channel Selected | Channel Selected                    | Disable <sup>b</sup> |  |

| 0    | Х          | Х  |                 |                |                |                                                |                                                               |                                     |                      |  |

| Х    | 0          | Х  | 1               | Х              | Х              | Х                                              | Х                                                             | None                                | High Z               |  |

| Х    | Х          | 1  |                 |                |                |                                                |                                                               |                                     |                      |  |

|      |            |    |                 | 0              | 0              | 0                                              | 0                                                             | S <sub>1</sub>                      |                      |  |

|      |            |    |                 | 0              | 0              | 0                                              | 1                                                             | S <sub>2</sub>                      |                      |  |

|      |            |    |                 | 0              | 0              | 1                                              | 0                                                             | S <sub>3</sub>                      |                      |  |

|      |            |    |                 | 0              | 0              | 1                                              | 1                                                             | S <sub>4</sub>                      |                      |  |

|      |            |    |                 | 0              | 1              | 0                                              | 0                                                             | S <sub>5</sub>                      |                      |  |

|      |            |    | 1               |                | 0              | 1                                              | 0                                                             | 1                                   | S <sub>6</sub>       |  |

|      |            |    |                 | 0              | 1              | 1                                              | 0                                                             | S <sub>7</sub>                      |                      |  |

| 1    | 1          | 0  |                 | 0              | 1              | 1                                              | 1                                                             | S <sub>8</sub>                      | Low Z                |  |

| '    | '          | 0  | '               | 1              | 0              | 0                                              | 0                                                             | S <sub>9</sub>                      | LOW Z                |  |

|      |            |    |                 | 1              | 0              | 0                                              | 1                                                             | S <sub>10</sub>                     |                      |  |

|      |            |    |                 | 1              | 0              | 1                                              | 0                                                             | S <sub>11</sub>                     |                      |  |

|      |            |    |                 | 1              | 0              | 1                                              | 1                                                             | S <sub>12</sub>                     |                      |  |

|      |            |    |                 | 1              | 1              | 0                                              | 0                                                             | S <sub>13</sub>                     |                      |  |

|      |            |    |                 | 1              | 1              | 0                                              | 1                                                             | S <sub>14</sub>                     |                      |  |

|      |            |    |                 | 1              | 1              | 1                                              | 0                                                             | S <sub>15</sub>                     |                      |  |

|      |            |    |                 | 1              | 1              | 1                                              | 1                                                             | S <sub>16</sub>                     |                      |  |

| Х    | Х          | Х  | 0               | Х              | Х              | Х                                              | Х                                                             | Maintains previous switch condition | High Z or Low Z      |  |

Logic "0" =  $V_{AL} \le 4.5 \text{ V}$ Logic "1" =  $V_{AH} \ge 10.5 \text{ V}$ X = Do not Care

## Notes:

a. Strobe input (ST) is level triggered.

b. Low Z, High Z = impedance of Disable Output to GND. Disable output sinks current when any channel is selected.

| Parameter                                |                                 | Limit                                                       | Unit |  |  |  |  |

|------------------------------------------|---------------------------------|-------------------------------------------------------------|------|--|--|--|--|

| V+ to GND                                |                                 | - 0.3 to + 18                                               | ٧    |  |  |  |  |

| Digital Inputs                           |                                 | (GND - 0.3) to (V+) + 2<br>or 20 mA, whichever occurs first |      |  |  |  |  |

| $V_S, V_D$                               |                                 | (GND - 0.3) to (V+) + 2<br>or 20 mA, whichever occurs first |      |  |  |  |  |

| Current (any terminal) Continuou         | S                               | 20                                                          | mA   |  |  |  |  |

| Current (S or D) Pulsed 1 ms 10          | % duty cycle                    | 40                                                          |      |  |  |  |  |

| Storage Temperature                      | (A Suffix)                      | - 65 to 150                                                 | °C   |  |  |  |  |

| Storage remperature                      | (D Suffix)                      | - 65 to 125                                                 |      |  |  |  |  |

|                                          | 28-Pin Plastic DIP <sup>b</sup> | 625                                                         |      |  |  |  |  |

| Power Dissipation (Package) <sup>a</sup> | 28-Pin Sidebraze <sup>c</sup>   | 1200                                                        | mW   |  |  |  |  |

|                                          | 44-Pin PLCC <sup>d</sup>        | 450                                                         |      |  |  |  |  |

|                                          | 44-Pin Cerquad <sup>e</sup>     | 825                                                         |      |  |  |  |  |

## Notes:

- a. All leads soldered or welded to PC board.

- b. Derate 8.6 mW/°C above 75 °C.

- c. Derate 16 mW/°C above 75 °C.

- d. Derate 6 mW/°C above 75 °C.

- e. Derate 11 mW/°C above 75 °C.

# DG535/536 Vishay Siliconix

|                                              | Test Conditions Unless Otherwise Specified V+ = 15 V, ST, CS = 10.5 V |                                                          |         |                   | <b>A Suffix</b><br>- 55 to 125 °C |                  | D Suffix<br>- 40 to 85 °C |                  |                  |      |

|----------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------|---------|-------------------|-----------------------------------|------------------|---------------------------|------------------|------------------|------|

| Parameter                                    | Symbol                                                                | $\overline{CS} = 4.5 \text{ V}, V_A = 4.5 \text{ or } 1$ |         | Temp <sup>b</sup> | Тур <sup>с</sup>                  | Min <sup>c</sup> | Max <sup>c</sup>          | Min <sup>c</sup> | Max <sup>c</sup> | Unit |

| Analog Switch                                | Зуппоп                                                                | 00 = 1.0 t, t <sub>A</sub> = 1.0 ti                      |         | Tellip            | ТУР                               | IVIIII           | IVIAX                     | IVIIII           | IVIAX            | Oili |

| Analog Signal Range <sup>e</sup>             | V <sub>ANALOG</sub>                                                   |                                                          |         | Full              |                                   | 0                | 10                        | 0                | 10               | V    |

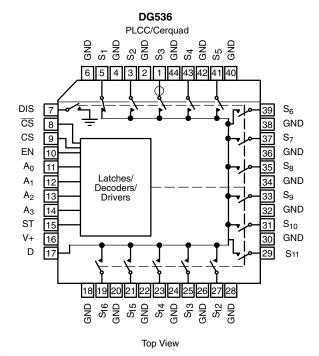

| Drain-Source                                 | ANALOG                                                                |                                                          |         | Room              | 55                                | •                | 90                        |                  | 90               | •    |

| On-Resistance                                | r <sub>DS(on)</sub>                                                   | $I_S = -1 \text{ mA}, V_D = 3 \text{ V, EN}$             |         | Full              |                                   |                  | 120                       |                  | 120              | Ω    |

| Resistance Match                             | $\Delta r_{DS(on)}$                                                   | Sequence Each Switch                                     | n On    | Room              |                                   |                  | 9                         |                  | 9                | İ    |

| Source Off Leakage Current                   | I <sub>S(off)</sub>                                                   | $V_S = 3 \text{ V}, V_D = 0 \text{ V}, EN =$             | 4.5 V   | Room<br>Full      |                                   | - 10<br>- 100    | 10<br>100                 | - 10<br>- 100    | 10<br>100        | ^    |

| Drain On Leakage Current                     | I <sub>D(on)</sub>                                                    | $V_S = V_D = 3 \text{ V, EN} = 10$                       | ).5 V   | Room<br>Full      |                                   | - 10<br>- 1000   | 10<br>1000                | - 10<br>- 100    | - 10<br>- 100    | nA   |

| Disable Output                               | R <sub>DISABLE</sub>                                                  | I <sub>DISABLE</sub> = 1 mA, EN = 1                      | 10.5 V  | Room<br>Full      | 100                               |                  | 200<br>250                |                  | 200<br>250       | Ω    |

| Digital Control                              |                                                                       |                                                          |         |                   |                                   |                  |                           |                  |                  |      |

| Input Voltage High                           | $V_{AIH}$                                                             |                                                          |         | Full              |                                   | 10.5             |                           | 10.5             |                  | ٧    |

| Input Voltage Low                            | $V_{AIL}$                                                             |                                                          |         | Full              |                                   |                  | 4.5                       |                  | 4.5              | · ·  |

| Address Input Current                        | I <sub>AI</sub>                                                       | V <sub>A</sub> = GND or V+                               |         | Room<br>Full      | < 0.01                            | - 1<br>- 100     | 1<br>100                  | - 1<br>- 100     | 1<br>100         | μΑ   |

| Address Input Capacitance                    | C <sub>A</sub>                                                        |                                                          |         | Full              | 5                                 |                  |                           |                  |                  | pF   |

| Dynamic Characteristics                      |                                                                       |                                                          |         |                   |                                   |                  |                           |                  |                  |      |

|                                              |                                                                       |                                                          | PLCC    | Room              | 32                                |                  | 45                        |                  | 45               |      |

| On State Input Capacitance <sup>e</sup>      | C <sub>S(on)</sub>                                                    | $V_{D} = V_{S} = 3 \text{ V}$                            | Cerquad | Room              | 35                                |                  |                           |                  |                  |      |

|                                              |                                                                       |                                                          | DIP     | Room              | 40                                |                  | 55                        |                  | 55               |      |

| Off State Input Capacitance <sup>e</sup>     |                                                                       |                                                          | PLCC    | Room              | 2                                 |                  | 8                         |                  | 8                |      |

|                                              | C <sub>S(off)</sub>                                                   | V <sub>S</sub> = 3 V                                     | Cerquad | Room              | 5                                 |                  |                           |                  |                  | pF   |

|                                              |                                                                       |                                                          | DIP     | Room              | 3                                 |                  |                           |                  |                  |      |

| Off State Output                             | •                                                                     |                                                          | PLCC    | Room              | 8                                 |                  | 20                        |                  | 20               |      |

| Capacitance                                  | $C_{D(off)}$                                                          | $V_D = 3 V$                                              | Cerquad | Room              | 12                                |                  |                           |                  |                  | 1    |

|                                              |                                                                       |                                                          | DIP     | Room              | 9                                 |                  | 000                       |                  | 000              |      |

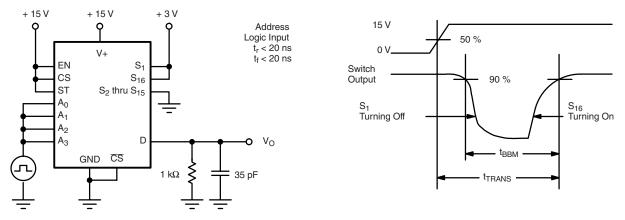

| Multiplexer Switching Time                   | t <sub>TRANS</sub>                                                    | See Figure 4                                             |         | Full              |                                   | 0.5              | 300                       | 0.5              | 300              |      |

| Break-Before-Make Interval                   | t <sub>OPEN</sub>                                                     |                                                          |         | Full              |                                   | 25               |                           | 25               |                  | ns   |

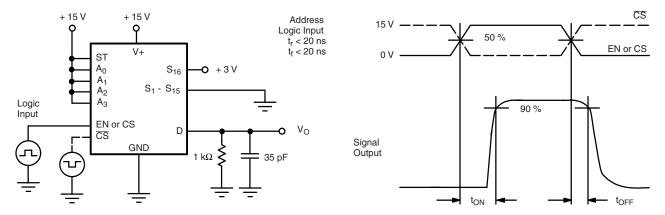

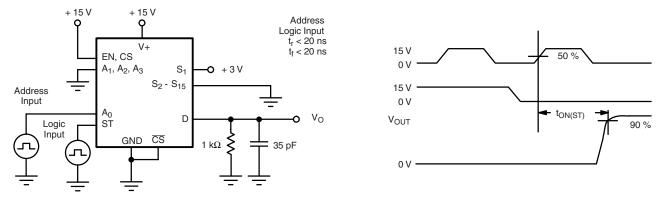

| EN, CS, <del>CS</del> , ST, t <sub>ON</sub>  | t <sub>ON</sub>                                                       | See Figure 2 and 3                                       | 3       | Full              |                                   |                  | 300                       |                  | 300              |      |

| EN, CS, <del>CS</del> , ST, t <sub>OFF</sub> | t <sub>OFF</sub>                                                      | See Figure 2                                             |         | Full              |                                   |                  | 150                       |                  | 150              |      |

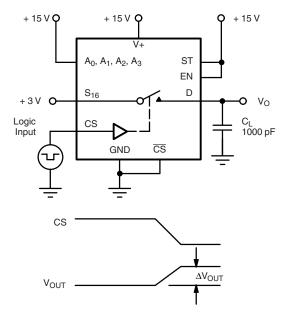

| Charge Injection                             | Q                                                                     | See Figure 5                                             |         | Room              | - 35                              |                  |                           |                  |                  | рС   |

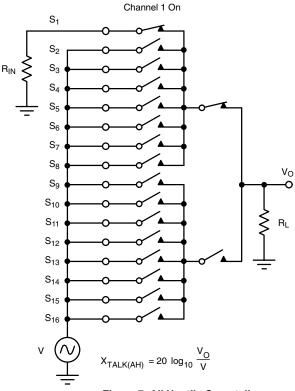

|                                              |                                                                       | $R_{IN} = 75 \Omega$ , $R_L = 75 \Omega$                 | PLCC    | Room              | - 100                             |                  |                           |                  |                  |      |

| Single-Channel Crosstalk                     | X <sub>TALK(SC)</sub>                                                 | f = 5 MHz                                                | Cerquad | Room              | - 93                              |                  |                           |                  |                  |      |

|                                              |                                                                       | See Figure 9                                             | DIP     | Room              | - 60                              |                  |                           |                  |                  |      |

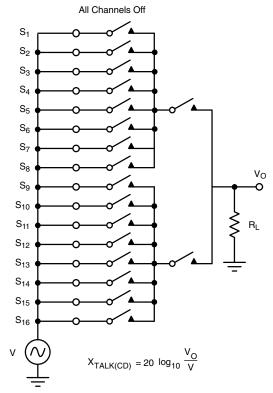

| Chip Disabled Crosstalk                      |                                                                       | $R_{IN} = R_L = 75 \Omega$ , $f = 5 MHz$                 | PLCC    | Room              | - 85                              |                  |                           |                  |                  |      |

|                                              | X <sub>TALK(CD)</sub>                                                 | EN = 4.5 V                                               | Cerquad | Room              | - 84                              |                  |                           |                  |                  |      |

|                                              |                                                                       | See Figure 8                                             | DIP     | Room              | - 60                              |                  |                           |                  |                  | dB   |

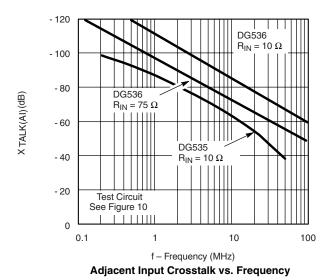

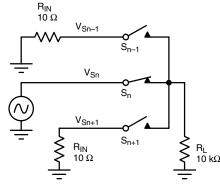

| A.II                                         | V                                                                     | $R_{IN} = 10 \Omega$ , $R_L = 10 k\Omega$                | PLCC    | Room              | - 92                              |                  |                           |                  |                  |      |

| Adjacent Input Crosstalk                     | X <sub>TALK(AI)</sub>                                                 | f = 5 MHz                                                | Cerquad | Room              | - 87                              |                  |                           |                  |                  |      |

|                                              |                                                                       | See Figure 10                                            | DIP     | Room              | - 72                              |                  |                           |                  |                  |      |

|                                              | V                                                                     | $R_{IN} = 10 \Omega$ , $R_L = 10 k\Omega$                | PLCC    | Room              | - 74                              | - 60             |                           | - 60             |                  |      |

| All Hostile Crosstalk <sup>e</sup>           | X <sub>TALK(AH)</sub>                                                 | f = 5 MHz<br>See Figure 7                                | Cerquad | Room              | - 74                              |                  |                           |                  |                  |      |

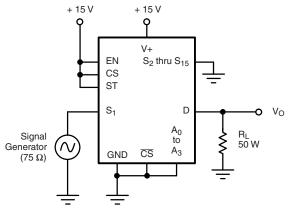

|                                              | BW                                                                    | See Figure 7 $R_L = 50 \Omega, \text{ See Figure}$       | DIP     | Room              | - 60<br>500                       |                  |                           |                  |                  | MH:  |

| SPECIFICATIONS <sup>a</sup>                                                                                                | 1               |                                                                                                                    |                   |                  |                  |                  |                  |                  |      |

|----------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|------------------|------------------|------------------|------|

|                                                                                                                            |                 | Test Conditions Unless Otherwise Specified                                                                         |                   |                  |                  | uffix<br>125 °C  |                  | uffix<br>85 °C   |      |

| Parameter                                                                                                                  | Symbol          | V+ = 15  V, ST, CS = 10.5  V<br>$\overline{\text{CS}} = 4.5 \text{ V, V}_{A} = 4.5 \text{ or } 10.5 \text{ V}^{f}$ | Temp <sup>b</sup> | Тур <sup>с</sup> | Min <sup>c</sup> | Max <sup>c</sup> | Min <sup>c</sup> | Max <sup>c</sup> | Unit |

| Power Supplies                                                                                                             |                 |                                                                                                                    |                   |                  |                  |                  |                  |                  |      |

| Positive Supply Current                                                                                                    | I+              | Any One Channge I Selected with All                                                                                | Room<br>Full      | 5                |                  | 50<br>100        |                  | 50<br>100        | μΑ   |

| Supply Voltage Range                                                                                                       | V+              | Logic Inputs at GND or V+                                                                                          | Full              |                  | 10               | 16.5             | 10               | 16.5             | V    |

| Minimum Input Timing Re                                                                                                    | quirements      |                                                                                                                    |                   |                  | •                |                  |                  |                  |      |

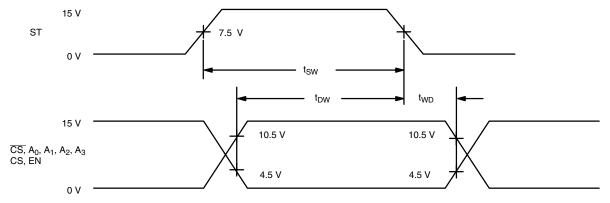

| Strobe Pulse Width                                                                                                         | t <sub>SW</sub> |                                                                                                                    | Full              |                  | 200              |                  | 200              |                  |      |

| A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub> CS, $\overline{\text{CS}}$ , EN Data Valid to Strobe     | t <sub>DW</sub> | See Figure 1                                                                                                       | Full              |                  | 100              |                  | 100              |                  | ns   |

| A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub> CS, $\overline{\text{CS}}$ , EN  Data Valid after Strobe | t <sub>WD</sub> |                                                                                                                    | Full              |                  | 50               |                  | 50               |                  |      |

#### Notes:

- a. Refer to PROCESS OPTION FLOWCHART.

- b. Room = 25  $^{\circ}$ C, Full = as determined by the operating temperature suffix.

- c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- d. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

- e. Guaranteed by design, not subject to production test.

- f.  $V_A$  = input voltage to perform proper function.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

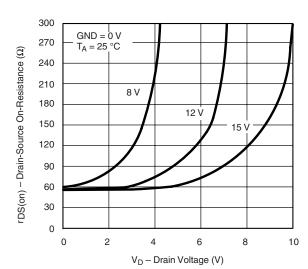

$r_{DS(on)}$  vs.  $V_D$  and Temperature

$r_{DS(on)}$  vs.  $V_D$  and Power Supply Voltage

# TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

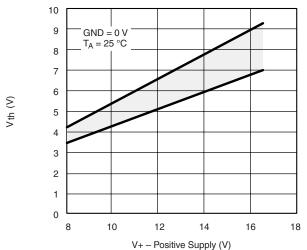

Logic Input Switching Threshold vs. Supply Voltage (V+)

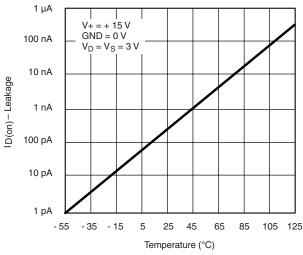

I<sub>D(on)</sub> vs. Temperature

14 GND = 0 V 12 10 125 °C 8 25 °C (hd) + 6 4 55 °C 2 0 10 11 12 13 14 15 16 17 18

Supply Current vs.

Supply Voltage and Temperature

V+ - Positive Supply (V)

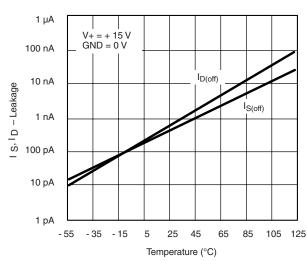

Leakage Current vs. Temperature

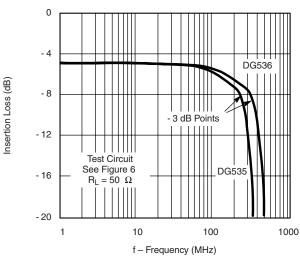

- 3 dB Bandwidth Insertion Loss vs. Frequency

# VISHAY.

# TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

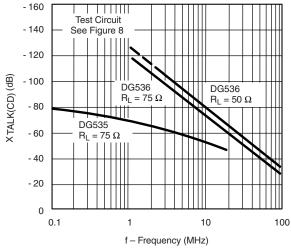

Chip Disable Crosstalk vs. Frequency

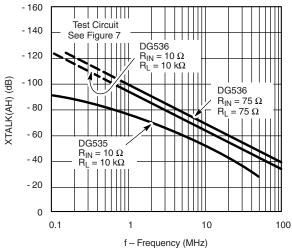

All Hostile Crosstalk vs. Frequency

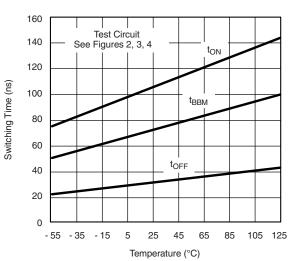

$t_{\mbox{\scriptsize ON}},\,t_{\mbox{\scriptsize OFF}}$  and Break-Before-Make vs. Temperature

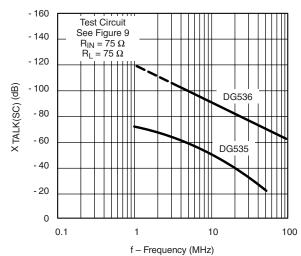

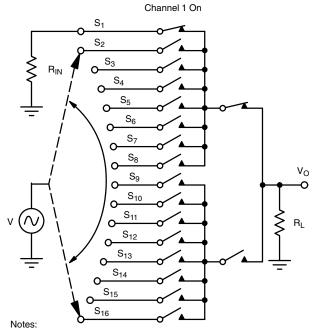

Single Channel Crosstalk vs. Frequency

# **INPUT TIMING REQUIREMENTS**

Figure 1.

## **TEST CIRCUITS**

Figure 2. EN, CS, CS, Turn On/Off Time

Figure 3. Strobe ST Turn On Time

Figure 4. Transition Time and Break-Before-Make Interval

# VISHAY.

## **TEST CIRCUITS**

$\Delta V_{OUT}$  is the measured voltage error due to charge injection. The charge injection in Coulombs is Q = C<sub>L</sub> x  $\Delta V_{OUT}$

Figure 5. Charge Injection

Figure 6. Bandwidth

Figure 7. All Hostile Crosstalk

Figure 8. Chip Disabled Crosstalk

# **TEST CIRCUITS**

1. Any individual channel between  $\ensuremath{S_2}$  and  $\ensuremath{S_{16}}$  can be selected

2.

$$X_{TALK(SC)} = 20 \log_{10} \frac{V_O}{V}$$

is scanned sequentially from  $S_2$  to  $S_{16}$

Figure 9. Single Channel Crosstalk

$$X_{TALK(AI)} = 20 \log_{10} \frac{V_{Sn-1}}{V_{Sn}} \text{ or } 20 \log_{10} \frac{V_{Sn+1}}{V_{Sn}}$$

Figure 10. Adjacent Input Crosstalk

| PIN DESCRIPTION                     |                                                                                                                                |  |  |  |  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                              | Description                                                                                                                    |  |  |  |  |  |

| S <sub>1</sub> thru S <sub>16</sub> | Analog inputs/outputs                                                                                                          |  |  |  |  |  |

| D                                   | Multiplexer output/demultiplexer input                                                                                         |  |  |  |  |  |

| DIS                                 | Open drain low impedance to analog ground when any channel is selected                                                         |  |  |  |  |  |

| CS, CS, EN                          | Logic inputs to selected desired multiplexer(s) when using several multiplexers in a system                                    |  |  |  |  |  |

| A <sub>0</sub> thru A <sub>3</sub>  | Binary address inputs to determine which channel is selected                                                                   |  |  |  |  |  |

| ST                                  | Strobe input that latches A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub> , $\overline{\text{CS}}$ , CS, EN  |  |  |  |  |  |

| V+                                  | Positive supply voltage input                                                                                                  |  |  |  |  |  |

| GND                                 | Analog signal ground and most negative potential  All ground pins should be connected externally to ensure dynamic performance |  |  |  |  |  |

#### **DETAILED DESCRIPTION**

The DG535/536 are 16-channel single-ended multiplexers with on-chip address logic and control latches.

The multiplexer connects one of sixteen inputs  $(S_1, S_2)$  through  $S_{16}$  to a common output (D) under the control of a 4-bit binary address  $(A_0 \text{ to } A_3)$ . The specific input channel selected for each address is given in the Truth Table.

All four address inputs have on-chip data latches which are controlled by the Strobe (ST) input. These latches are transparent when Strobe is high but they maintain the chosen address when Strobe goes low. To facilitate easy microprocessor control in large matrices a choice of three independent logic inputs (EN, CS and  $\overline{\text{CS}}$ ) are provided on chip. These inputs are gated together (see Figure 11) and only when EN = CS = 1 and  $\overline{\text{CS}}$  = 0 can an output switch be selected. This necessary logic condition is then latched-in when Strobe (ST) goes low.

Figure 11. CS, CS, EN, ST Control Logic

Break-before-make switching prevents momentary shorting when changing from one input to another.

The devices feature a two-level switch arrangement whereby two banks of eight switches (first level) are connected via two series switches (second level) to a common DRAIN output.

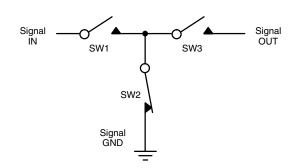

In order to improve crosstalk all sixteen first level switches are configured as "T" switches (see Figure 12).

With this method  $SW_2$  operates out of phase with  $SW_1$  and  $SW_3$ . In the on condition  $SW_1$  and  $SW_3$  are closed with  $SW_2$  open whereas in the off condition  $SW_1$  and  $SW_3$  are open and  $SW_2$  closed. In the off condition the input to  $SW_3$  is effectively the isolation leakage of  $SW_1$  working into the on-resistance of  $SW_2$  (typically 200  $\Omega$ ).

Figure 12. "T" Switch Arrangement

The two second level series switches further improve crosstalk and help to minimize output capacitance.

The DIS output can be used to signal external circuitry. DIS is a high impedance to GND when no channel is selected and a low impedance to GND when any one channel is selected.

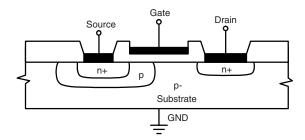

The DG535/536 have extensive applications where any high frequency video or digital signals are switched or routed. Exceptional crosstalk and bandwidth performance is achieved by using n-channel DMOS FETs for the "T" and series switches.

Figure 13. Cross-Section of a Single DMOS Switch

It can clearly be seen from Figure 13 that there exists a PN junction between the substrate and the drain/source terminals.

Should a signal which is negative with respect to the substrate (GND pin) be connected to a source or drain terminal, then the PN junction will become forward biased and current will flow between the signal source and GND. This effective shorting of the signal source to GND will not necessarily cause any damage to the device, provided that the total current flowing is less than the maximum rating, (i.e., 20 mA).

#### **DETAILED DESCRIPTION**

Since no PN junctions exist between the signal path and V+, positive overvoltages are not a problem, unless the breakdown voltage of the DMOS drain terminal (see Figure 13) (+ 18 V) is exceeded. Positive overvoltage conditions must not exceed + 18 V with respect to the GND pin. If this condition is possible (e.g. transients in the signal), then a diode or Zener clamp may be used to prevent breakdown.

The overvoltage conditions described may exist if the supplies are collapsed while a signal is present on the inputs. If this condition is unavoidable, then the necessary steps outlined above should be taken to protect the device

#### **DC** Biasing

To avoid negative overvoltage conditions and subsequent distortion of ac analog signals, dc biasing may be necessary. Biasing is not required, however, in applications where signals are always positive with respect to the GND or substrate connection, or in applications involving multiplexing of low level (up to  $\pm$  200 mV) signals, where forward biasing of the PN substrate-source/drain terminals would not occur.

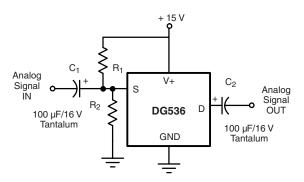

Biasing can be accomplished in a number of ways, the simplest of which is a resistive potential divider and a few dc blocking capacitors as shown in Figure 14.

Figure 14. Simple Bias Circuit

$\rm R_1$  and  $\rm R_2$  are chosen to suit the appropriate biasing requirements. For video applications, approximately 3 V of bias is required for optimal differential gain and phase performance. Capacitor  $\rm C_1$  blocks the dc bias voltage from being coupled back to the analog signal source and  $\rm C_2$  blocks the dc bias from the output signal. Both  $\rm C_1$  and  $\rm C_2$  should be tantalum or ceramic disc type capacitors in order to operate efficiently at high frequencies. Active bias circuits are recommended if rapid switching time between channels is required.

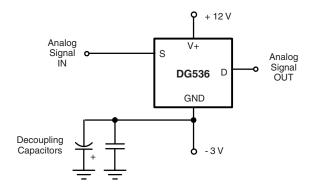

An alternative method is to offset the supply voltages (see Figure 15).

Decoupling would have to be applied to the negative supply to ensure that the substrate is well referenced to signal ground. Again the capacitors should be of a type offering good high frequency characteristics.

Level shifting of the logic signals may be necessary using this offset supply arrangement.

Figure 15. DG536 with Offset Supply

TTL to CMOS level shifting is easily obtained by using a MC14504B.

#### **Circuit Layout**

Good circuit board layout and extensive shielding is essential for optimizing the high frequency performance of the DG536. Stray capacitances on the PC board and/or connecting leads will considerably degrade the ac performance. Hence, signal paths must be kept as short as practically possible, with extensive ground planes separating signal tracks.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?70070">http://www.vishay.com/ppg?70070</a>.

Vishay

# **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Document Number: 91000 Revision: 18-Jul-08

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Multiplexer Switch ICs category:

Click to view products by Vishay manufacturer:

Other Similar products are found below:

NLV74HC4066ADR2G HEF4051BP MC74HC4067ADTG DG508AAK/883B NLV14051BDG 016400E PI3V512QE 7705201EC

PI2SSD3212NCE NLAS3257CMX2TCG PI5A3157BC6EX PI3DBS12412AZLEX PI3V512QEX PI3DBS16213ZLEX PI3DBS16415ZHEX

PS509LEX MUX36S16IRSNR TC7W53FK,LF CD4053BM96 MC74HC4053ADWR2G SN74LV4051APWR HEF4053BT.653

PI3L720ZHEX ADG1404YRUZ-REEL7 ADG1208YRZ-REEL7 MAX4704EUB+T ADG1406BRUZ-REEL7 CD4053BPWRG4

74HC4053D.653 74LVC2G53DP.125 74HC4052DB.112 74HC4052PW.112 74HC4053DB.112 74HC4067DB.112 74HC4351DB.112

74HCT4052D.112 74HCT4052DB.112 74HCT4067D.112 74HCT4351D.112 74LV4051PW.112 FSA1256L8X\_F113 PI5V330QE

PI5V331QE 5962-8771601EA 5962-87716022A ADG5249FBRUZ ADG1439BRUZ ADG1438BRUZ AD7506JNZ AD7506KNZ