#### Rev. 1.2, 16-Nov-2023

For technical questions, contact: <a href="mailto:sensorstechsupport@vishay.com">sensorstechsupport@vishay.com</a> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

**Vishay Semiconductors**

# A Small Package Proximity Sensor With a VCSEL, Low Idle Current, I<sup>2</sup>C Interface, and Smart Dual Slave Address

- Package type: surface-mount

- Dimensions (L x W x H in mm): 2.0 x 1.0 x 0.5

- Integrated modules: vertical-cavity surfaceemitting laser (VCSEL), photodiode, and application-specific integrated circuit (ASIC)

- 1.8 V rated power supply and I<sup>2</sup>C bus

- Low power consumption with 5 µA idle current

- A small package allows a design with a small window size

- Smart dual I<sup>2</sup>C slave address in one package

- Immunity to red glow (940 nm VCSEL)

- Programmable I<sub>VCSEL</sub> sink current

- Intelligent cancellation to reduce cross talk phenomenon

- Smart persistence scheme to reduce measurement response time

- Interrupt functionality

- Material categorization: for definitions of compliance please see www.vishay.com/doc?99912

### APPLICATIONS

- · Smartphones and true wireless stereo (TWS) earbuds

- VR / AR headsets and smart glasses

- Smartwatches

- Touchless button / dispensing

| PRODUCT SUMMARY |                            |                                   |                         |    |                                      |                                                |  |  |  |  |

|-----------------|----------------------------|-----------------------------------|-------------------------|----|--------------------------------------|------------------------------------------------|--|--|--|--|

| PART<br>NUMBER  | OPERATING<br>RANGE<br>(mm) | OPERATING<br>VOLTAGE RANGE<br>(V) | AGE RANGE VOLTAGE RANGE |    | OUTPUT<br>CODE                       | ADC RESOLUTION<br>PROXIMITY /<br>AMBIENT LIGHT |  |  |  |  |

| VCNL36828P      | 200                        | 1.65 to 2.00                      | 1.2 to 3.6              | 20 | 12 bit /<br>16 bit, l <sup>2</sup> C | 16 bit / -                                     |  |  |  |  |

| ORDERING INFORMATION |               |                              |                          |  |  |  |  |  |  |

|----------------------|---------------|------------------------------|--------------------------|--|--|--|--|--|--|

| ORDERING CODE        | PACKAGING     | VOLUME <sup>(1)</sup>        | REMARKS                  |  |  |  |  |  |  |

| VCNL36828P           | Tape and reel | MOQ: 5000 pcs, 5000 pcs/reel | 2.0 mm x 1.0 mm x 0.5 mm |  |  |  |  |  |  |

### Note

<sup>(1)</sup> MOQ: minimum order quantity

### LINKS TO ADDITIONAL RESOURCES

### DESCRIPTION

The VCNL36828P is a fully integrated proximity sensor. It combines a vertical-cavity surface-emitting laser (VCSEL), photodiode, and application-specific integrated circuit (ASIC) within a single package. The VCNL36828P has been developed for proximity detection applications that require a dual slave address, low power consumption, small package size, small window size, and short range operation. In addition, given the typical rated supply voltage of 1.8 V to reduce power consumption, the sensor is intended for battery-powered applications.

VCNL36828P

RoHS COMPLIANT

HALOGEN

FREE GREEN

(5-2008)

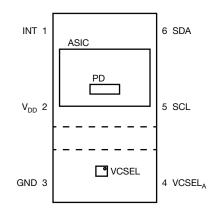

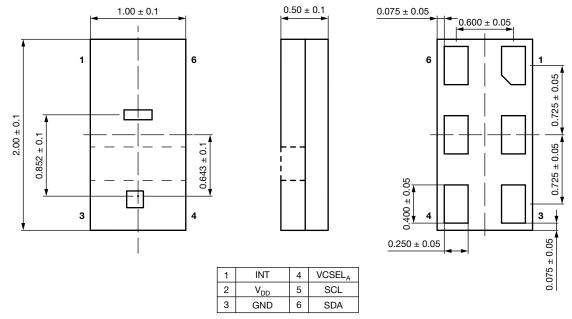

### **PIN DEFINITION**

| PIN DESCRIPTION | PIN DESCRIPTION    |                    |                               |  |  |  |  |  |  |  |  |

|-----------------|--------------------|--------------------|-------------------------------|--|--|--|--|--|--|--|--|

| PIN NUMBER      | PIN NAME           | TYPE               | DESCRIPTION                   |  |  |  |  |  |  |  |  |

| 1               | INT                | O (open drain)     | Interrupt                     |  |  |  |  |  |  |  |  |

| 2               | V <sub>DD</sub>    | I                  | Supply voltage                |  |  |  |  |  |  |  |  |

| 3               | GND                | I                  | Ground                        |  |  |  |  |  |  |  |  |

| 4               | VCSELA             | I                  | VCSEL anode                   |  |  |  |  |  |  |  |  |

| 5               | SCL (1)            | I / O (open drain) | I <sup>2</sup> C serial clock |  |  |  |  |  |  |  |  |

| 6               | SDA <sup>(1)</sup> | I / O (open drain) | I <sup>2</sup> C serial data  |  |  |  |  |  |  |  |  |

### Note

<sup>(1)</sup> Pin 5 (SCL) and pin 6 (SDA) can be swapped to change the slave address from 0x60 to 0x51; please refer to Table 1

| ABSOLUTE MAXIMUM RATINGS (T <sub>amb</sub> = 25 °C, unless otherwise specified) |                |                  |      |      |      |  |  |  |  |  |

|---------------------------------------------------------------------------------|----------------|------------------|------|------|------|--|--|--|--|--|

| PARAMETER                                                                       | TEST CONDITION | SYMBOL           | MIN. | MAX. | UNIT |  |  |  |  |  |

| Supply voltage                                                                  |                | V <sub>DD</sub>  | 0    | 2    | V    |  |  |  |  |  |

| Ambient temperature range                                                       |                | T <sub>amb</sub> | -40  | +85  | °C   |  |  |  |  |  |

| Storage temperature range                                                       |                | T <sub>stg</sub> | -40  | +100 | °C   |  |  |  |  |  |

# VCNL36828P

# Vishay Semiconductors

| BASIC CHARACTERISTICS                      | <b>BASIC CHARACTERISTICS</b> (T <sub>amb</sub> = 25 °C, unless otherwise specified) |                      |      |                                                                                                                                                                                   |      |      |  |  |  |  |  |  |

|--------------------------------------------|-------------------------------------------------------------------------------------|----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--|--|--|--|--|--|

| PARAMETER                                  | TEST CONDITION                                                                      | SYMBOL               | MIN. | TYP.                                                                                                                                                                              | MAX. | UNIT |  |  |  |  |  |  |

| ASIC                                       |                                                                                     |                      |      | •                                                                                                                                                                                 |      | •    |  |  |  |  |  |  |

| Supply voltage                             |                                                                                     | V <sub>DD</sub>      | 1.65 | 1.80                                                                                                                                                                              | 2.00 | V    |  |  |  |  |  |  |

|                                            | Shutdown state; light condition = dark;<br>$V_{DD} = 1.8 V$                         |                      | -    | 1                                                                                                                                                                                 | -    |      |  |  |  |  |  |  |

| Supply current <sup>(1)</sup>              | Idle state <sup>(2)</sup> ; $V_{DD} = 1.8 V$                                        | I <sub>DD</sub>      | -    | 5                                                                                                                                                                                 | -    | μA   |  |  |  |  |  |  |

| Γ                                          | Active state <sup>(2)</sup> ; V <sub>DD</sub> = 1.8 V                               |                      | -    | 5       1.80       2.0         1       -         5       -         330       -         2       -         1.8       3.6         -       0.5         2       -         1.92       - | -    |      |  |  |  |  |  |  |

| I <sup>2</sup> C supply voltage            |                                                                                     | V <sub>PULL UP</sub> | 1.2  | 1.8                                                                                                                                                                               | 3.6  | V    |  |  |  |  |  |  |

| I <sup>2</sup> C signal input, logic high  | V <sub>DD</sub> = 1.8 V                                                             | V <sub>IH</sub>      | 1    | -                                                                                                                                                                                 | -    | V    |  |  |  |  |  |  |

| I <sup>2</sup> C signal input, logic low   | V <sub>DD</sub> = 1.8 V                                                             | VIL                  | -    | -                                                                                                                                                                                 | 0.5  | V    |  |  |  |  |  |  |

| VCSEL                                      |                                                                                     |                      |      |                                                                                                                                                                                   |      |      |  |  |  |  |  |  |

| Supply voltage of the VCSEL <sup>(3)</sup> |                                                                                     | V <sub>VCSEL</sub>   | 2.62 | -                                                                                                                                                                                 | 3.60 | V    |  |  |  |  |  |  |

| Forward voltage                            | I <sub>F</sub> = 9 mA                                                               | V <sub>F</sub>       | -    | 1.92                                                                                                                                                                              | -    | V    |  |  |  |  |  |  |

| Forward current                            |                                                                                     | I <sub>F</sub>       | 7    | -                                                                                                                                                                                 | 20   | mA   |  |  |  |  |  |  |

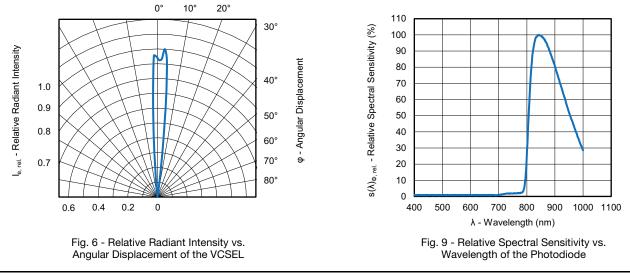

| Angle of half intensity                    |                                                                                     | φ                    | -    | ± 4.5                                                                                                                                                                             | -    | 0    |  |  |  |  |  |  |

| Peak wavelength                            | I <sub>F</sub> = 9 mA                                                               | λρ                   | -    | 940                                                                                                                                                                               | -    | nm   |  |  |  |  |  |  |

| Spectral bandwidth                         | I <sub>F</sub> = 9 mA                                                               | Δλ                   | -    | 3                                                                                                                                                                                 | -    | nm   |  |  |  |  |  |  |

| PHOTODIODE                                 |                                                                                     |                      |      | •                                                                                                                                                                                 |      | •    |  |  |  |  |  |  |

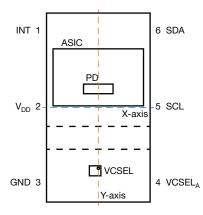

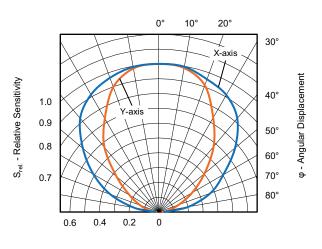

| Angle of holf consistivity                 | X-axis <sup>(4)</sup>                                                               |                      | -    | ± 60                                                                                                                                                                              | -    | 0    |  |  |  |  |  |  |

| Angle of half sensitivity                  | Y-axis <sup>(4)</sup>                                                               | φ -                  |      | ± 45                                                                                                                                                                              | -    |      |  |  |  |  |  |  |

| Peak sensitivity wavelength                |                                                                                     | λρ                   | -    | 850                                                                                                                                                                               | -    | nm   |  |  |  |  |  |  |

Notes

<sup>(1)</sup> Actual current consumption depends on the register settings. Please refer to the application note on the current consumption

(2) Excluding VCSEL driving current

<sup>(3)</sup> V<sub>VCSEL</sub> should at least match the minimum required supply voltage for the VCSEL V<sub>VCSEL, min</sub>. Please refer to the V<sub>VCSEL, min</sub> table

<sup>(4)</sup> Cross section of the package

| V <sub>VCSEL</sub> , MIN.    | -      |        |        |        |        |        |       |        |  |  |  |  |

|------------------------------|--------|--------|--------|--------|--------|--------|-------|--------|--|--|--|--|

| PS_CURRENT (I <sub>F</sub> ) | 7 mA   | 9 mA   | 11 mA  | 12 mA  | 15 mA  | 17 mA  | 19 mA | 20 mA  |  |  |  |  |

| V <sub>VCSEL, min.</sub>     | 2.62 V | 2.74 V | 2.86 V | 2.91 V | 3.08 V | 3.19 V | 3.3 V | 3.36 V |  |  |  |  |

| V <sub>VCSEL, max.</sub>     |        | 3.6 V  |        |        |        |        |       |        |  |  |  |  |

### LASER CLASS

### Note

• Product specification with IEC / EN 60825-1:2014 compliance and above label

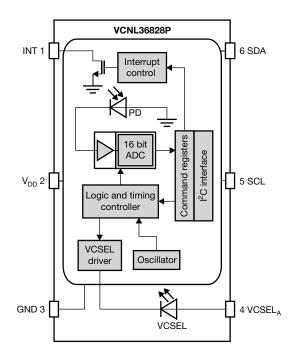

### **BLOCK DIAGRAM**

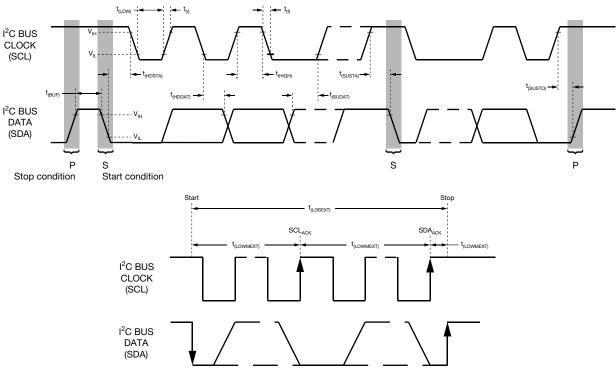

| DADAMETED                                                                                      | SYMBOL                | STANDA | RD MODE | FAST |      |      |

|------------------------------------------------------------------------------------------------|-----------------------|--------|---------|------|------|------|

| PARAMETER                                                                                      | STMBUL                | MIN.   | MAX.    | MIN. | MAX. | UNIT |

| Clock frequency                                                                                | f <sub>(I2CCLK)</sub> | 10     | 100     | 10   | 400  | kHz  |

| Bus free time between start and stop condition                                                 | t <sub>(BUF)</sub>    | 4.7    | -       | 1.3  | -    | μs   |

| Hold time after (repeated) start condition;<br>after this period, the first clock is generated | t <sub>(HDSTA)</sub>  | 4.0    | -       | 0.6  | -    | μs   |

| Repeated start condition setup time                                                            | t <sub>(SUSTA)</sub>  | 4.7    | -       | 0.6  | -    | μs   |

| Stop condition setup time                                                                      | t <sub>(SUSTO)</sub>  | 4.0    | -       | 0.6  | -    | μs   |

| Data hold time                                                                                 | t <sub>(HDDAT)</sub>  | 0      | 3450    | 0    | 900  | ns   |

| Data setup time                                                                                | t <sub>(SUDAT)</sub>  | 250    | -       | 100  | -    | ns   |

| I <sup>2</sup> C clock (SCL) low period                                                        | t <sub>(LOW)</sub>    | 4.7    | -       | 1.3  | -    | μs   |

| I <sup>2</sup> C clock (SCL) high period                                                       | t <sub>(HIGH)</sub>   | 4.0    | -       | 0.6  | -    | μs   |

| Clock / data fall time                                                                         | t <sub>(f)</sub>      | -      | 300     | -    | 300  | ns   |

| Clock / data rise time                                                                         | t <sub>(r)</sub>      | -      | 1000    | -    | 300  | ns   |

#### Note

• Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

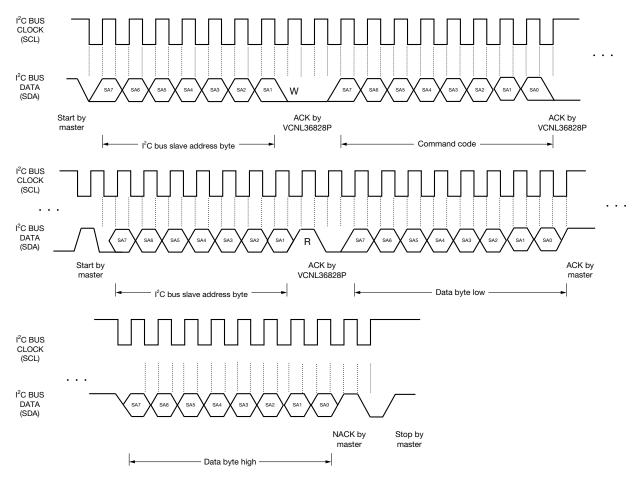

Fig. 1 - I<sup>2</sup>C Bus Timing Diagram

www.vishay.com

**Vishay Semiconductors**

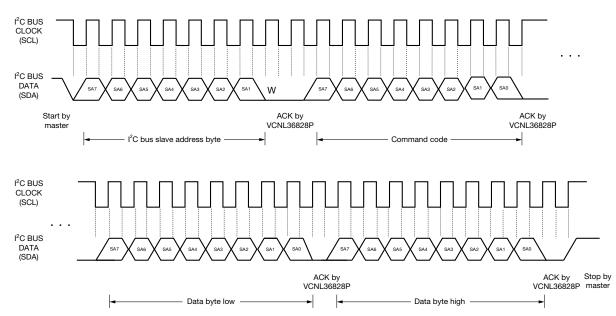

### PARAMETER TIMING INFORMATION

Fig. 2 - I<sup>2</sup>C Bus Timing for Sending Word Command Format

Fig. 3 - I<sup>2</sup>C Bus Timing for Receiving Word Command Format

For technical questions, contact: <u>sensorstechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

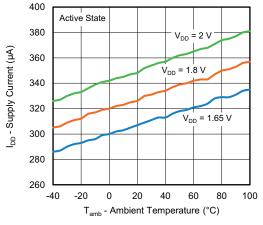

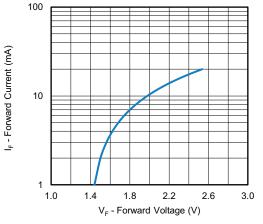

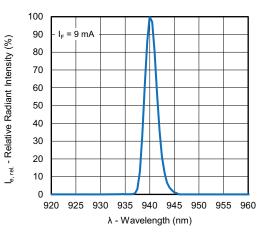

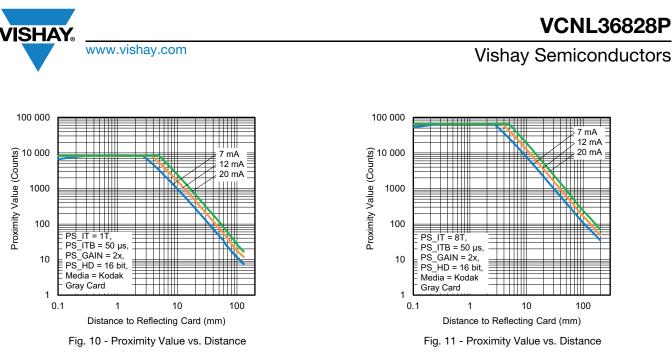

### **TYPICAL PERFORMANCE CHARACTERISTICS** ( $T_{amb} = 25 \text{ °C}$ , unless otherwise specified)

Fig. 4 - Supply Current vs. Ambient Temperature

Fig. 5 - Forward Current vs. Forward Voltage of the VCSEL

Fig. 7 - Relative Radiant Intensity vs. Wavelength of the VCSEL

Fig. 8 - Relative Sensitivity vs. Angular Displacement of the Photodiode

Rev. 1.2, 16-Nov-2023

7

Document Number: 80306

For technical questions, contact: <u>sensorstechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

### **APPLICATION INFORMATION**

### **Slave Address Selection**

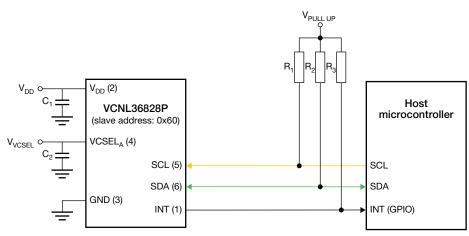

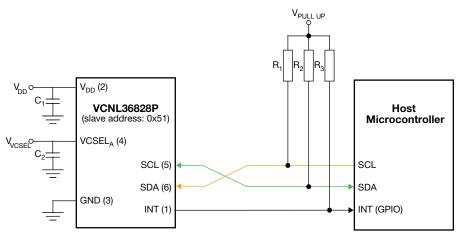

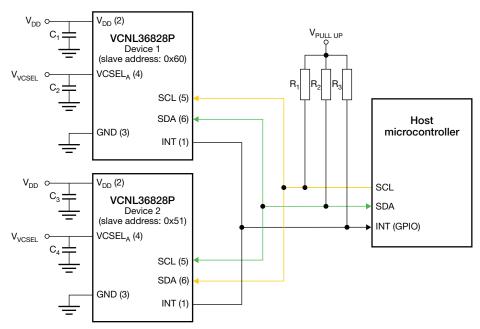

The VCNL36828P supports a smart dual slave address where the designer can change the slave address by swapping the SCL and SDA pins, as shown in Table 1.

| TABLE 1 | TABLE 1 - SLAVE ADDRESS TABLE |                     |                             |                            |  |  |  |  |  |  |  |

|---------|-------------------------------|---------------------|-----------------------------|----------------------------|--|--|--|--|--|--|--|

| PIN 5   | PIN 6                         | 7 BIT SLAVE ADDRESS | 8 BIT SLAVE ADDRESS (WRITE) | 8 BIT SLAVE ADDRESS (READ) |  |  |  |  |  |  |  |

| SCL     | SDA                           | 0x60                | 0xC0                        | 0xC1                       |  |  |  |  |  |  |  |

| SDA     | SCL                           | 0x51                | 0xA2                        | 0xA3                       |  |  |  |  |  |  |  |

A smart dual slave address provides the flexibility for the designer to connect two devices from two different slave addresses on the same I<sup>2</sup>C bus. Besides that, the two slave address options allow designers to select a different slave address if one is used by the other slave devices on the same  $I^2C$  bus in a single device application.

#### Application Circuit With a Single Device - Slave Address 0x60

Fig. 12 shows an application circuit example with a single device. As described in Table 1, when pins 5 and 6 are connected to the clock and data signal from the microcontroller, as shown in Fig. 12, they will then be configured as an SCL pin and SDA pin, respectively. The 7 bit slave address option of 0x60 will be automatically selected.

Fig. 12 - Application Circuit Example for a Single VCNL36828P - Slave Address 0x60

### Application Circuit With a Single Device - Slave Address 0x51

On the other hand, when pins 5 and 6 are connected to the data and clock signal from the microcontroller, as shown in Fig. 13, they will then be configured as an SDA pin and SCL pin, respectively. The 7 bit slave address option of 0x51 will be automatically selected.

Fig. 13 - Application Circuit Example for a Single VCNL36828P - Slave Address 0x51

Table 2 shows the required values and the explanation for the individual application circuit parameters.

| TABLE 2 - A                     | PPLICATION C                    | CIRCUIT PARAMETERS                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CIRCUIT<br>PARAMETER            | VALUE                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>DD</sub>                 | 1.65 V to 2.00 V                | A stable power supply such as a low dropout regulator or a switching regulator is required; the power supply isolation can be further improved with a decoupling capacitor $C_1$                                                                                                                                                                                                                                           |

| V <sub>VCSEL</sub>              | 2.62 V to 3.60 V                | A stable power supply such as a low dropout regulator or a switching regulator that can supply an adequate amount of power (max. VCSEL pulse driving current of 20 mA) is required; the power supply isolation can be further improved with a decoupling capacitor C <sub>2</sub> ; the minimum voltage depends on the selected driving current of the VCSEL; please refer to Table V <sub>VCSEL, min.</sub> for reference |

| V <sub>PULL UP</sub>            | 1.2 V to 3.6 V                  | A stable power supply such as a low dropout regulator or a switching regulator is required; a voltage level shifter is required if the I <sup>2</sup> C bus voltage from the microcontroller is higher than 3.6 V                                                                                                                                                                                                          |

| C <sub>1</sub> - C <sub>4</sub> | 100 nF to 1 µF                  | Decoupling capacitors are recommended to reduce the noise in the supply voltage                                                                                                                                                                                                                                                                                                                                            |

| R <sub>1</sub> - R <sub>2</sub> | 2.2 kΩ to 4.7 kΩ                | Pull-up resistors within the range of 2.2 k $\Omega$ to 4.7 k $\Omega$ are recommended; any increase in bus capacitance or resistance will increase the logic high transition time                                                                                                                                                                                                                                         |

| R <sub>3</sub>                  | 4.7 k $\Omega$ to 22 k $\Omega$ | Pull-up resistor within the range of 4.7 k $\Omega$ to 22 k $\Omega$ is recommended                                                                                                                                                                                                                                                                                                                                        |

### **Application Circuit With a Smart Dual Slave Address**

Fig. 14 shows an application circuit example with a smart dual slave address. By swapping the SCL and SDA pins of the second device, as shown in Table 1, the designer can change the 7 bit slave address of the VCNL36828P. This provides the flexibility for the designer to connect two devices from two different slave addresses on the same I<sup>2</sup>C bus.

Fig. 14 - Application Circuit Example for Two VCNL36828Ps - Smart Dual Slave Address

### I<sup>2</sup>C Write and Read Protocol

The communication with the VCNL36828P can be performed via I<sup>2</sup>C. The I<sup>2</sup>C write and read protocol when communicating with the proximity sensor is shown in Fig. 15.

| Sen        | d byte $\rightarrow$ write comr                                     | nand   | to \ | /CNL36828P                         |   |   |               |   |                |   |                |     |   |   |                |   |   |

|------------|---------------------------------------------------------------------|--------|------|------------------------------------|---|---|---------------|---|----------------|---|----------------|-----|---|---|----------------|---|---|

| 1          | 7                                                                   | 1      | 1    | 8                                  | 1 |   | 8             | 1 |                |   | 8              | 1   | 1 |   |                |   |   |

| S          | Slave address                                                       | Wr     | А    | Command code                       | А |   | Data byte low | А | Data byte high |   | Data byte high |     | Ρ |   |                |   |   |

| Rec        | eive byte $ ightarrow$ read da                                      | ta fro | m V  | CNL36828P                          |   |   |               |   |                |   |                |     |   |   |                |   |   |

| 1          | 7                                                                   | 1      | 1    | 8                                  | 1 | 1 | 7             |   | 1              | 1 | 8              |     |   | 1 | 8              | 1 | 1 |

| S          | Slave address                                                       | Wr     | А    | Command code                       | А | S | Slave address |   | Rd             | А | Data byte      | low |   | А | Data byte high | Ν | Р |

| P =<br>A = | start condition<br>stop condition<br>acknowledge<br>not acknowledge |        |      | Host action<br>VCNL36828P response |   |   |               |   |                |   |                |     |   |   |                |   |   |

|            |                                                                     |        |      |                                    |   |   |               |   |                |   |                |     |   |   |                |   |   |

Fig. 15 - I<sup>2</sup>C Write and Read Protocol

It is imperative that only the restart condition for the I<sup>2</sup>C read is implemented instead of the stop and restart condition.

# VCNL36828P

**Vishay Semiconductors**

### **Function Description**

| COMMAND<br>CODE | DATA BYTE<br>LOW / HIGH | REGISTER<br>NAME | DEFAULT<br>VALUE                                 | FUNCTION                                                                      | ACCESS    |  |  |  |  |

|-----------------|-------------------------|------------------|--------------------------------------------------|-------------------------------------------------------------------------------|-----------|--|--|--|--|

|                 | 1                       | PS CONF1 L       | 0x00                                             | Internal calibration setting                                                  |           |  |  |  |  |

|                 | L                       | PS_CONFI_L       | UXUU                                             | Switch the sensor on / off                                                    |           |  |  |  |  |

| 0x00            |                         |                  |                                                  | High dynamic range setting                                                    |           |  |  |  |  |

|                 | н                       | PS_CONF1_H       | 0x00                                             | Persistence setting                                                           | ]         |  |  |  |  |

|                 |                         |                  |                                                  | Interrupt setting                                                             |           |  |  |  |  |

|                 | L                       |                  |                                                  | Measurement period setting                                                    |           |  |  |  |  |

|                 |                         | PS_CONF2_L       | 0x00                                             | Signal strength setting (Integration time and multi-pulse)                    |           |  |  |  |  |

| 0x01            |                         |                  |                                                  | High gain setting                                                             |           |  |  |  |  |

| 0.01            |                         |                  |                                                  | Sensitivity of the ADC setting                                                |           |  |  |  |  |

|                 | н                       | H PS_CONF2_H     |                                                  | Internal crosstalk cancellation setting                                       | Write     |  |  |  |  |

|                 |                         |                  | VCSEL driving current setting                    |                                                                               |           |  |  |  |  |

|                 | L                       |                  | PS CONF3 L 0x00 Sensor mode setting              |                                                                               | and read  |  |  |  |  |

| 0x02            | L                       | F3_CONF3_L       | Active force mode trigger setting                |                                                                               |           |  |  |  |  |

| 0702            | н                       |                  | PS CONF3 H 0x00 Short measurement period setting |                                                                               |           |  |  |  |  |

|                 | 11                      | 1.9_00101.9_11   | Sunlight cancellation setting                    |                                                                               |           |  |  |  |  |

| 0x03            | L                       | PS_THDL_L 0x00   |                                                  | Low threshold interrupt value setting (low byte)                              |           |  |  |  |  |

| 0703            | Н                       | PS_THDL_H        | 0x00                                             | Low threshold interrupt value setting (high byte)                             |           |  |  |  |  |

| 0x04            | L                       | PS_THDH_L        | 0x00                                             | High threshold interrupt value setting (low byte)                             |           |  |  |  |  |

| 0,04            | Н                       | PS_THDH_H        | 0x00                                             | High threshold interrupt value setting (high byte)                            |           |  |  |  |  |

| 0x05            | L                       | PS_CANC_L        | 0x00                                             | Offset count cancellation value setting (low byte)                            |           |  |  |  |  |

| 0,000           | Н                       | PS_CANC_H        | 0x00                                             | Offset count cancellation value setting (high byte)                           |           |  |  |  |  |

| 0xF8            | L                       | PS_DATA_L        | 0x00                                             | Proximity output data (low byte)                                              |           |  |  |  |  |

|                 | Н                       | PS_DATA_H        | 0x00                                             | Proximity output data (high byte)                                             |           |  |  |  |  |

| 0xF9            | L                       | Reserved         | 0x00 - 0xFF                                      | Reserved                                                                      |           |  |  |  |  |

| 071.9           | Н                       | INT_FLAG         | 0x00                                             | Interrupt flag                                                                | Read only |  |  |  |  |

| 0xFA            | L                       | VCNL36828P_ID_L  | 0x28 / 0x29                                      | Device ID<br>Slave address: 0x60; ID = 0x28<br>Slave address: 0x51; ID = 0x29 |           |  |  |  |  |

|                 | Н                       | VCNL36828P_ID_H  | 0x01                                             | Device ID                                                                     | 1         |  |  |  |  |

### Notes

• All of the reserved registers are used for internal test. These values must be kept constant

(1) The default ID depends on the connection of the SCL and SDA pins on the VCNL36828P with the SCL and SDA pins on the host MCU. If pins 5 and 6 on the VCNL36828P are connected to the SCL and SDA pins on the host, the default value will be 0x28. On the other hand, if pins 5 and 6 on the VCNL36828P are connected to the SDA and SCL pins on the host, the default value will be 0x29. Please refer to Fig. 13

### **Command Register Format**

| TABLE 4   | TABLE 4 - REGISTER NAME: PS_CONF1_L |                               |                                   |     |           |                    |                                          |  |  |  |  |  |

|-----------|-------------------------------------|-------------------------------|-----------------------------------|-----|-----------|--------------------|------------------------------------------|--|--|--|--|--|

| Bit 7     | Bit 6                               | Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 |                                   |     |           |                    |                                          |  |  |  |  |  |

| PS_CAL    | Reserved PS_ON                      |                               |                                   |     |           |                    |                                          |  |  |  |  |  |

| COMMAND C | COMMAND CODE 0x00                   |                               |                                   |     |           |                    |                                          |  |  |  |  |  |

| Bit N     | lame                                | Fund                          | ction                             | Bit | Value     | ription            |                                          |  |  |  |  |  |

| PS CAL    |                                     | Enable / disable the          | internal calibration              | 7   | 0x0 (0b0) | Disable (default)  |                                          |  |  |  |  |  |

| F3_       | CAL                                 |                               | internal calibration              | 7   | 0x1 (0b1) | Enable             |                                          |  |  |  |  |  |

| Rese      | erved                               | Rese                          | Reserved 6 : 1 0x00<br>(0b000000) |     |           |                    | Should be kept default                   |  |  |  |  |  |

| PS ON     |                                     | Switch the sensor on / off    |                                   | 0   | 0x0 (0b0) |                    | urn off the sensor<br>hutdown) (default) |  |  |  |  |  |

|           |                                     |                               |                                   |     | 0x1 (0b1) | Turn on the sensor |                                          |  |  |  |  |  |

| TABLE 5    | - REGISTER | R NAME: PS_CON             | NF1_H                       |           |                   |                   |                            |

|------------|------------|----------------------------|-----------------------------|-----------|-------------------|-------------------|----------------------------|

| Bit 15     | Bit 14     | Bit 13                     | Bit 12                      | Bit 11    | Bit 10            | Bit 9             | Bit 8                      |

| Reserved   | PS_HD      | PS_SP_INT                  | PS_SMART_PERS               | PS_I      | PERS              | PS_               | INT                        |

| COMMAND (  | CODE       |                            |                             |           |                   | 0x00              |                            |

| Bit N      | lame       | Fund                       | ction                       | Bit       | Value             | Desci             | ription                    |

| Rese       | erved      | Rese                       | erved                       | 15        | 0x0 (0b0)         | Should be         | kept default               |

| De         | HD         | Enable / disable high c    | lynamic range (12 bit /     | 14        | 0x0 (0b0)         | Disable (12       | bit) (default)             |

| гэ <u></u> | _חח        | 16 bit) ADC output setting |                             | 14        | 0x1 (0b1)         | Enable            | (16 bit)                   |

|            | P INT      | Enable / disable the       | 13                          | 0x0 (0b0) | Disable (default) |                   |                            |

| P5_5       | P_INT      | mode inter                 | 13                          | 0x1 (0b1) | Ena               | able              |                            |

|            |            | Enable / disable the       | e smart persistence         | 12        | 0x0 (0b0)         | Disable (default) |                            |

| F3_SIVIAI  | RT_PERS    | setting when the inter     | 12                          | 0x1 (0b1) | Enable            |                   |                            |

|            |            |                            |                             | 11 10     | 0x0 (0b00)        | 1 time (default)  |                            |

|            | PERS       |                            | onsecutive threshold        |           | 0x1 (0b01)        | 2 times           |                            |

| F3_F       | ENO        | inter                      | ecessary to trigger<br>rupt | 11 : 10   | 0x2 (0b10)        | 3 times           |                            |

|            |            |                            | ·                           |           | 0x3 (0b11)        | 4 times           |                            |

|            |            |                            |                             |           | 0x0 (0b00)        | Interrupt dis     | able (default)             |

| PS         | INT        | Set the interrup           | ot mode setting             | 9:8       | 0x1 (0b01)        | Logic high        | / low mode                 |

| 10_        |            |                            | st mode betting             | 0.0       | 0x3 (0b11)        |                   | ich high / low<br>ld event |

VCNL36828P

www.vishay.com

Vishay Semiconductors

| TABLE 6 -  | REGISTER N | IAME: PS_CO                                                                                      | NF2_L              |       |            |                                                |                                    |

|------------|------------|--------------------------------------------------------------------------------------------------|--------------------|-------|------------|------------------------------------------------|------------------------------------|

| Bit 7      | Bit 6      | Bit 5                                                                                            | Bit 4              | Bit 3 | Bit 2      | Bit 1                                          | Bit 0                              |

| PS_PI      | ERIOD      | PS                                                                                               | _IT                | PS_   | MPS        | PS_ITB                                         | PS_GAIN                            |

| COMMAND CO | DDE        |                                                                                                  |                    |       |            | 0x01                                           |                                    |

| Bit N      | Bit Name   |                                                                                                  | ction              | Bit   | Value      | Descr                                          | iption                             |

|            |            |                                                                                                  |                    |       | 0x0 (0b00) | ,                                              | translates into<br>ent/s (default) |

|            | ERIOD      | Set the measu                                                                                    | romant pariod      | 7:6   | 0x1 (0b01) |                                                | translates into<br>rements/s       |

| F3_FI      |            | Set the measu                                                                                    | irement penoa      | 7.0   | 0x2 (0b10) | 200 ms, which translates into 5 measurements/s |                                    |

|            |            |                                                                                                  |                    |       | 0x3 (0b11) |                                                | translates into<br>rements/s       |

|            |            | Set the integration time for one<br>measurement; the pulse length<br>"T" is determined by PS_ITB |                    | 5:4   | 0x0 (0b00) | 1 T (d                                         | efault)                            |

| De         | IT         |                                                                                                  |                    |       | 0x1 (0b01) | 2 T                                            |                                    |

| FG         |            |                                                                                                  |                    |       | 0x2 (0b10) | 4 T                                            |                                    |

|            |            |                                                                                                  |                    |       | 0x3 (0b11) | 8 T                                            |                                    |

|            |            |                                                                                                  |                    |       | 0x0 (0b00) | 1 pulse                                        | (default)                          |

| PS         | MPS        | Set the number                                                                                   | of infrared signal | 3:2   | 0x1 (0b01) | 2 pulses                                       |                                    |

| F3_        | WF 3       | pulses per m                                                                                     | neasurement        | 5.2   | 0x2 (0b10) | 4 pu                                           | llses                              |

|            |            |                                                                                                  |                    |       | 0x3 (0b11) | 8 pi                                           | llses                              |

| De         | ITB        | Sot the pulse lon                                                                                | gth "T" for PS_IT  | 1     | 0x0 (0b0)  | T = 25 με                                      | s (default)                        |

| P3_        |            | Set the pulse left                                                                               | 901 I 101 F3_11    | I     | 0x1 (0b1)  | T = 5                                          | 50 µs                              |

|            | GAIN       | Sat the gain                                                                                     | of the ADC         | 0     | 0x0 (0b0)  | x 1 gain                                       | (default)                          |

| P3_0       |            | Set the gain                                                                                     |                    | U     | 0x1 (0b1)  | x 2                                            | gain                               |

| TABLE 7 - | REGISTER | NAME: PS_C                                           | ONF2_H             |          |             |                   |                  |

|-----------|----------|------------------------------------------------------|--------------------|----------|-------------|-------------------|------------------|

| Bit 15    | Bit 14   | Bit 13                                               | Bit 12             | Bit 11   | Bit 10      | Bit 9             | Bit 8            |

| Res       | erved    | PS_SENS                                              | PS_OFFSET          | Reserved |             | PS_CURRENT        |                  |

| COMMAND C | ODE      |                                                      |                    |          |             | 0x01              |                  |

| Bit M     | Name     | Fu                                                   | inction            | Bit      | Value       | Descr             | ription          |

| Res       | erved    | Re                                                   | eserved            | 15 : 14  | 0x0 (0b00)  | Should be l       | kept default     |

|           | SENG     | Sat the same                                         | itivity of the ADC | 13       | 0x0 (0b0)   | Normal sensi      | tivity (default) |

| F3_       | SENS     | Set the sensitivity of the ADC                       |                    | 13       | 0x1 (0b1)   | High sensitivity  |                  |

|           | FFSET    | Enable / disable the internal crosstalk cancellation |                    | 12       | 0x0 (0b0)   | Disable (default) |                  |

| F3_0      | IT SET   |                                                      |                    | 12       | 0x1 (0b1)   | Enable            |                  |

| Res       | erved    | Re                                                   | eserved            | 11       | 0x0 (0b0)   | Should be l       | kept default     |

|           |          |                                                      |                    |          | 0x0 (0b000) | 7 mA (default)    |                  |

|           |          |                                                      |                    |          | 0x1 (0b001) | 9 mA              |                  |

|           |          |                                                      |                    |          | 0x2 (0b010) | 11 mA             |                  |

|           | JRRENT   | Sat the VCS                                          | EL driving current | 10:8     | 0x3 (0b011) | 12 mA             |                  |

| F3_00     |          | Set the VCS                                          |                    | 10.0     | 0x4 (0b100) | 15                | mA               |

|           |          |                                                      |                    |          | 0x5 (0b101) | 17                | mA               |

|           |          |                                                      |                    |          | 0x6 (0b110) | 19 mA             |                  |

|           |          |                                                      |                    |          | 0x7 (0b111) | 20 mA             |                  |

Rev. 1.2, 16-Nov-2023

14

# Vishay Semiconductors

**VCNL36828P**

Document Number: 80306

| TABLE 8 - MAX                    | KIMUM BIT RESO        | LUTION AND DI        | GITAL OUTPUT C         | OUNTS                  |                        |  |  |  |

|----------------------------------|-----------------------|----------------------|------------------------|------------------------|------------------------|--|--|--|

| BIT N                            | NAME                  | PS_IT = 1T           | PS_IT = 2T             | $PS_IT = 4T$           | PS_IT = 8T             |  |  |  |

| PS HD = 0 (12  bit)              | PS_GAIN = 0 (x1 gain) | 12 bit / 4095 counts |                        |                        |                        |  |  |  |

| PS_HD = 0 (12 bit)               | PS_GAIN = 1 (x2 gain) |                      |                        |                        |                        |  |  |  |

| $D_{2}^{2} = 1 (16 \text{ bit})$ | PS_GAIN = 0 (x1 gain) | 12 bit / 4095 counts | 13 bit / 8191 counts   | 14 bit / 16 383 counts | 15 bit / 32 767 counts |  |  |  |

| PS_HD = 1 (16 bit)               | PS_GAIN = 1 (x2 gain) | 13 bit / 8191 counts | 14 bit / 16 383 counts | 15 bit / 32 767 counts | 16 bit / 65 535 counts |  |  |  |

| TABLE 9 - REGISTER NAME: PS_CONF3_L |                  |                                                                         |               |       |              |                        |         |  |  |  |  |

|-------------------------------------|------------------|-------------------------------------------------------------------------|---------------|-------|--------------|------------------------|---------|--|--|--|--|

| Bit 7                               | Bit 6            | Bit 5                                                                   | Bit 4         | Bit 3 | Bit 2        | Bit 1                  | Bit 0   |  |  |  |  |

| Res                                 | erved            | PS_TRIG                                                                 | PS_MODE       |       | Rese         | erved                  |         |  |  |  |  |

| COMMAND C                           | OMMAND CODE 0x02 |                                                                         |               |       |              |                        |         |  |  |  |  |

| Bit I                               | Name             | Fu                                                                      | nction        | Bit   | Value        | Desci                  | ription |  |  |  |  |

| Res                                 | erved            | Re                                                                      | served        | 7:6   | 0x0 (0b00)   | Should be kept default |         |  |  |  |  |

| PS TRIG                             |                  | Set the active force mode trigger;<br>This bit will be reset to 0 after |               | 5     | 0x0 (0b0)    | Off (d                 | efault) |  |  |  |  |

| F3_                                 |                  | the measurement cycle                                                   |               | 5     | 0x1 (0b1)    | Trigger                |         |  |  |  |  |

|                                     | MODE             | Set the mea                                                             | surement mode | 4     | 0x0 (0b0)    | Auto mode (default)    |         |  |  |  |  |

| PS_MODE                             |                  | of th                                                                   | e sensor      | 4     | 0x1 (0b1)    | Active force mode      |         |  |  |  |  |

| Res                                 | erved            | Re                                                                      | served        | 3:0   | 0x0 (0b0000) | Should be kept default |         |  |  |  |  |

| TABLE 10  | - REGISTER | NAME: PS_  | CONF3_H                          |               |                                         |                                                   |                                |

|-----------|------------|------------|----------------------------------|---------------|-----------------------------------------|---------------------------------------------------|--------------------------------|

| Bit 15    | Bit 14     | Bit 13     | Bit 12                           | Bit 11        | Bit 10                                  | Bit 9                                             | Bit 8                          |

| PS_SP     | PERIOD     | Reserved   |                                  | PS_SC         |                                         | Rese                                              | erved                          |

| COMMAND C | ODE        |            |                                  |               |                                         | 0x02                                              |                                |

| Bit N     | lame       | Fu         | Inction                          | Bit           | Value                                   | Desci                                             | ription                        |

|           |            | 0x0 (0b00) |                                  | (follow PS_PE | short period<br>ERIOD setting)<br>ault) |                                                   |                                |

| PS_SP     | PS_SPERIOD |            | Set the short measurement period |               | 0x1 (0b01)                              | 6.25 ms, which translates in 160 measurements/s   |                                |

|           |            |            |                                  |               | 0x2 (0b10)                              |                                                   | n translates into<br>rements/s |

|           |            |            |                                  |               | 0x3 (0b11)                              | 25 ms, which translates into<br>40 measurements/s |                                |

| Rese      | erved      | Re         | eserved                          | 13            | 0x0 (0b0)                               | Should be                                         | kept default                   |

|           | 20         | Enabl      | e / disable                      | 10, 10        | 0x0 (0b000)                             | )) Disable (default)                              |                                |

|           | _SC        |            | ht cancellation                  | 12 : 10       | 0x7 (0b111)                             | Ena                                               | able                           |

| Rese      | erved      | Re         | eserved                          | 9:8           | 0x0 (0b00)                              | Should be                                         | kept default                   |

VCNL36828P

www.vishay.com

# Vishay Semiconductors

| TABLE 11  | TABLE 11 - REGISTER NAME: PS_THDL |                                       |                       |        |             |           |         |  |  |  |  |

|-----------|-----------------------------------|---------------------------------------|-----------------------|--------|-------------|-----------|---------|--|--|--|--|

| Bit 7     | Bit 6                             | Bit 5                                 | Bit 4                 | Bit 3  | Bit 2       | Bit 1     | Bit 0   |  |  |  |  |

| PS_THDL_L |                                   |                                       |                       |        |             |           |         |  |  |  |  |

| Bit 15    | Bit 14                            | Bit 13                                | Bit 12                | Bit 11 | Bit 10      | Bit 9     | Bit 8   |  |  |  |  |

|           | PS_THDL_H                         |                                       |                       |        |             |           |         |  |  |  |  |

| COMMAND C | ODE                               |                                       |                       |        |             | 0x03      |         |  |  |  |  |

| Bit N     | Bit Name Function                 |                                       |                       | Bit    | Value       | Desci     | ription |  |  |  |  |

| PS_T      | PS_THDL_L                         |                                       | shold interrupt value | 7:0    | 0 to 65 535 |           | byte    |  |  |  |  |

| PS_THDL_H |                                   | Set the low threshold interrupt value |                       | 15 : 8 | 0 10 05 555 | High byte |         |  |  |  |  |

| TABLE 12                                                                                                      | TABLE 12 - REGISTER NAME: PS_THDH |                  |                        |             |             |           |         |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|------------------------|-------------|-------------|-----------|---------|--|--|--|--|

| Bit 7                                                                                                         | Bit 6                             | Bit 5            | Bit 4                  | Bit 3       | Bit 2       | Bit 1     | Bit 0   |  |  |  |  |

| PS_THDH_L                                                                                                     |                                   |                  |                        |             |             |           |         |  |  |  |  |

| Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8 |                                   |                  |                        |             |             |           |         |  |  |  |  |

|                                                                                                               | PS_THDH_H                         |                  |                        |             |             |           |         |  |  |  |  |

| COMMAND C                                                                                                     | ODE                               |                  |                        |             |             | 0x04      |         |  |  |  |  |

| Bit N                                                                                                         | lame                              | Fu               | Inction                | Bit         | Value       | Desc      | ription |  |  |  |  |

| PS_THDH_L Set the high threshold                                                                              |                                   | 7:0              |                        | 0 to 65 535 | Low byte    |           |         |  |  |  |  |

| PS_THDH_H                                                                                                     |                                   | Set the high the | eshold interrupt value | 15 : 8      | 0 10 05 555 | High byte |         |  |  |  |  |

| TABLE 13  | - REGISTER                         | NAME: PS_ | CANC            |         |              |           |              |  |  |  |

|-----------|------------------------------------|-----------|-----------------|---------|--------------|-----------|--------------|--|--|--|

| Bit 7     | Bit 6                              | Bit 5     | Bit 4           | Bit 3   | Bit 2        | Bit 1     | Bit 0        |  |  |  |

| PS_CANC_L |                                    |           |                 |         |              |           |              |  |  |  |

| Bit 15    | Bit 14                             | Bit 13    | Bit 12          | Bit 11  | Bit 10       | Bit 9     | Bit 8        |  |  |  |

|           | Reserved PS_CANC_H                 |           |                 |         |              |           |              |  |  |  |

| COMMAND C | ODE                                |           |                 |         |              | 0x05      |              |  |  |  |

| Bit I     | Name                               | Fu        | inction         | Bit     | Value        | Desci     | ription      |  |  |  |

| PS_C      | PS_CANC_L Set the offset           |           |                 | 7:0     | 0 to 4095    | Low byte  |              |  |  |  |

| PS_C      | PS_CANC_H count cancellation value |           | cellation value | 11:8    | 0 10 4095    | High byte |              |  |  |  |

| Res       | Reserved Reserved                  |           |                 | 15 : 12 | 0x0 (0b0000) | Should be | kept default |  |  |  |

| TABLE 14                                                                                                      | TABLE 14 - REGISTER NAME: PS_DATA |              |                    |        |             |           |        |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------|--------------------|--------|-------------|-----------|--------|--|--|--|--|

| Bit 7                                                                                                         | Bit 6                             | Bit 5        | Bit 4              | Bit 3  | Bit 2       | Bit 1     | Bit 0  |  |  |  |  |

| PS_DATA_L                                                                                                     |                                   |              |                    |        |             |           |        |  |  |  |  |

| Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8 |                                   |              |                    |        |             |           |        |  |  |  |  |

|                                                                                                               | PS_DATA_H                         |              |                    |        |             |           |        |  |  |  |  |

| COMMAND C                                                                                                     | ODE                               |              |                    |        |             | 0xF8      |        |  |  |  |  |

| Bit N                                                                                                         | Bit Name Function                 |              |                    | Bit    | Value       | Descr     | iption |  |  |  |  |

| PS_DATA_L Read the proximity output data                                                                      |                                   | 7:0          | 0 to 65 535        |        | byte        |           |        |  |  |  |  |

| PS_DATA_H                                                                                                     |                                   | nead the pro | xinity output data | 15 : 8 | 0 10 05 555 | High byte |        |  |  |  |  |

Rev. 1.2, 16-Nov-2023

Document Number: 80306

# **VCNL36828P**

Vishay Semiconductors

| TABLE 15     | - REGISTER | R NAME: INT                       | FLAG                             |         |                                            |                                                  |                             |

|--------------|------------|-----------------------------------|----------------------------------|---------|--------------------------------------------|--------------------------------------------------|-----------------------------|

| Bit 7        | Bit 6      | Bit 5                             | Bit 4                            | Bit 3   | Bit 2                                      | Bit 1                                            | Bit 0                       |

|              |            | •                                 | Reserv                           | ed      | •                                          | •                                                |                             |

| Bit 15       | Bit 14     | Bit 13                            | Bit 12                           | Bit 11  | Bit 10                                     | Bit 9                                            | Bit 8                       |

|              | Reserved   |                                   | PS_SPFLAG                        | Res     | erved                                      | PS_IF_CLOSE                                      | PS_IF_AWAY                  |

| COMMAND CODE |            |                                   |                                  |         |                                            | 0xF9                                             |                             |

| Bit I        | Name       | Fu                                | Inction                          | Bit     | Value                                      | Desci                                            | ription                     |

| Res          | erved      | Re                                | eserved                          | 7:0     | 0x00 - 0xFF<br>(0b00000000 -<br>0b1111111) | Should be                                        | kept default                |

| Res          | erved      | Re                                | Reserved                         |         | 0x0 (0b000)                                | Should be l                                      | kept default                |

| PS SPFLAG    |            | Read the sunlight protection mode |                                  | 12      | 0x0 (0b0)                                  |                                                  | otection mode<br>event flag |

| 10_0         |            | interrupt event flag              |                                  |         | 0x1 (0b1)                                  | Sunlight protection mode<br>interrupt event flag |                             |

| Res          | erved      | Re                                | eserved                          | 11 : 10 | 0x0 (0b00)                                 | Should be                                        | kept default                |

|              |            | Read the high                     | Read the high threshold crossing |         | 0x0 (0b0)                                  |                                                  | hold crossing<br>event flag |

| PS_IF_CLOSE  |            | interrupt event flag              |                                  | 9       | 0x1 (0b1)                                  | High threshold crossing interruevent flag        |                             |

|              | PS_IF_AWAY |                                   | threshold crossing               | 8       | 0x0 (0b0)                                  | No low thres<br>interrupt                        | hold crossing<br>event flag |

| F3_IF        |            |                                   | ot event flag                    | o       | 0x1 (0b1)                                  | Low threshold crossing interre<br>event flag     |                             |

| TABLE 16 - REGISTER NAME: VCNL36828P_ID |                 |                    |           |        |                      |                       |                       |  |  |  |  |

|-----------------------------------------|-----------------|--------------------|-----------|--------|----------------------|-----------------------|-----------------------|--|--|--|--|

| Bit 7                                   | Bit 6           | Bit 5              | Bit 4     | Bit 3  | Bit 2                | Bit 1                 | Bit 0                 |  |  |  |  |

|                                         |                 |                    | VCNL36828 | P_ID_L |                      |                       |                       |  |  |  |  |

| Bit 15                                  | Bit 14          | Bit 13             | Bit 12    | Bit 11 | Bit 10 Bit 9 Bit 8   |                       |                       |  |  |  |  |

|                                         | VCNL36828P_ID_H |                    |           |        |                      |                       |                       |  |  |  |  |

| COMMAND CODE 0xFA                       |                 |                    |           |        |                      |                       |                       |  |  |  |  |

| Bit Name Function                       |                 |                    |           | Bit    | Value                | Description           |                       |  |  |  |  |

|                                         |                 |                    |           |        | 0x28<br>(0b00101000) |                       | with a<br>ess of 0x60 |  |  |  |  |

| VCNL36828P_ID_L<br>VCNL36828P_ID_H      |                 | Read the device ID |           | 7:0    | 0x29<br>(0b00101001) | Device<br>slave addre | with a<br>ess of 0x51 |  |  |  |  |

|                                         |                 |                    |           | 15 : 8 | 0x01<br>(0b0000001)  | Should be l           | kept default          |  |  |  |  |

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

### **PACKAGE INFORMATION** in millimeters

Fig. 16 - VCNL36828P Package Dimensions

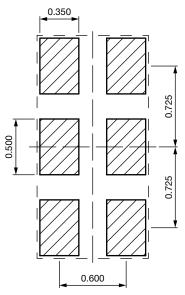

### **RECOMMENDED LAYOUT PAD INFORMATION** in millimeters

Fig. 17 - VCNL36828P PCB Layout Footprint

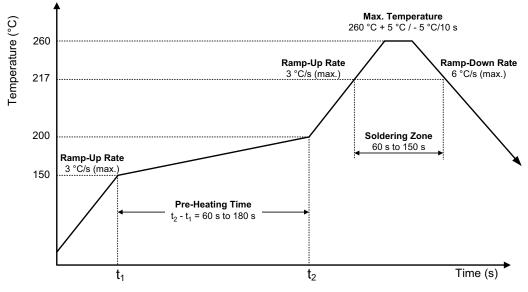

### **RECOMMENDED INFRARED REFLOW**

Soldering conditions which are based on J-STD-020C

| IR REFLOW PROFILE CONDITION                |            |                                       |               |

|--------------------------------------------|------------|---------------------------------------|---------------|

| PARAMETER                                  | CONDITIONS | TEMPERATURE                           | TIME          |

| Peak temperature                           |            | 260 °C + 5 °C / - 5 °C (max.: 265 °C) | 10 s          |

| Preheat temperature range and timing       |            | 150 °C to 200 °C                      | 60 s to 180 s |

| Timing within 5 °C to peak temperature     |            | -                                     | 10 s to 30 s  |

| Timing maintained above temperature / time |            | 217 °C                                | 60 s to 150 s |

| Timing from 25 °C to peak temperature      |            | -                                     | 8 min (max.)  |

| Ramp-up rate                               |            | 3 °C/s (max.)                         | -             |

| Ramp-down rate                             |            | 6 °C/s (max.)                         | -             |

Recommend Normal Solder Reflow is 235 °C to 265 °C

Fig. 18 - VCNL36828P Solder Reflow Profile Chart

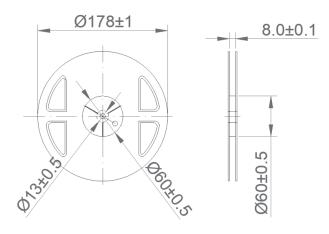

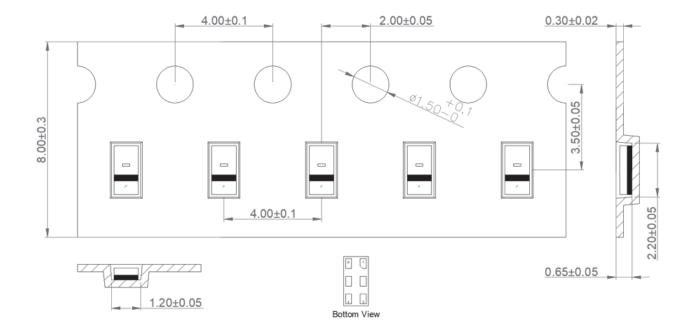

### TAPE PACKAGING INFORMATION in millimeters

Vishay

# Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Vishay products are not designed for use in life-saving or life-sustaining applications or any application in which the failure of the Vishay product could result in personal injury or death unless specifically qualified in writing by Vishay. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

© 2024 VISHAY INTERTECHNOLOGY, INC. ALL RIGHTS RESERVED

Revision: 01-Jul-2024

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Proximity Sensors category:

Click to view products by Vishay manufacturer:

Other Similar products are found below :

70.340.1028.0

70.360.2428.0

8027AL20NL2CPXX

9221350022

922AA2W-A9P-L

GL-12F-C2.5X10(LOT3)

972AB3XM-A3P-L

PS3251

980659-1

E2E2-X5M41-M4

E2E-X14MD1-G

E2E-X2D1-G

E2E-X4MD1-G

E2E-X5E1-5M-N

E2E-X5Y2-N

EH-302

EI3010TBOP

MS605AU

EP175-32000

IC08ANC15PO-K

IFRM04P1513/S35L

IFRM06P1703/S35L

IFRM08P1501/S35L

IFRM12N17G3/L

IFRM12P3502/L

IFRM12P37G1/S14L

ILFK12E9189/I02

ILFK12E9193/I02

IMM2582C

OISN-013

25.332.0653.1

25.352.0653.0

25.352.0753.0

25.523.3253.0

9151710023

922AA1HI-A4P-L

922AA2XM-B9P-L

922FS0.8-H4P-G-020

922FS1.5C-A4P-Z774

SC606ABV0S30

SM851A1200FP

F3S-A162-U

GL-12F-C2X10(LOT10)

GL-8HIBX10

QT-08L