## HS512K16 8Mb Radiation-Hardened Synchronous Dual-Port SRAM

HS512K16 is a high performance synchronous Dual-Port SRAM organized as 524,288 words with 16-bit word. It can be configured as Master or Slave device. Master device can initiate autonomous scrub and demand scrub cycles on Slave device.

- True dual-port synchronous SRAM, 8Mb memory

- Selectable between Pipeline and Flow-Through modes

- Built-in EDAC (Error Detection and Correction) to mitigate soft errors

- Built-in Scrub Engine for autonomous correction

- Built-in Address counter for sequential memory access with repeat feature

- Dual chip enable allows depth and width expansion without additional logic

- Asynchronous Output Enable for each port

- Support various clock modes and stress test modes

- Direct read mode from data bits or parity bits for quick memory testing

- Cycle Time <20ns flow through mode, <15ns pipeline mode</li>

- Access time <17ns flow through mode, <12ns pipeline mode

- Manufactured by TI at DMOS5 wafer fab

- 130nm CMOS generation with commercial layout rules

- 5 levels metal, with Cu , Al layers

- 8T DP SRAM cell

- CMOS compatible input and output level, three state bidirectional data bus

- 3.3 +/- 0.3V I/O, 1.5 +/- 0.15V CORE

- Radiation performance

- Manufactured by TI with SST 130nm RH process and selective circuit design hardening

- TID immunity > 300Krads (Si)

- SER < 1e-10 errors/bit-day @ geosynchronous orbit & solar minimum (with ECC/Scrub)

- Latch up immunity > LET = 110 MeV (T=125°C)

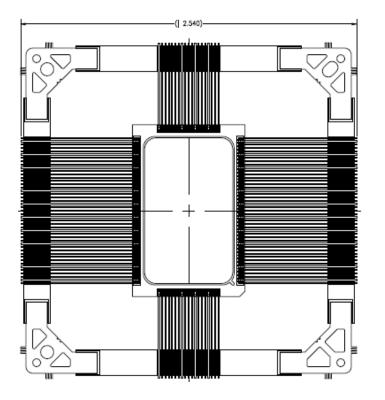

- Packaging options: 128pin CQFP, Die

- Temperature options: -55°C to 125°C and -55°C to 200°C

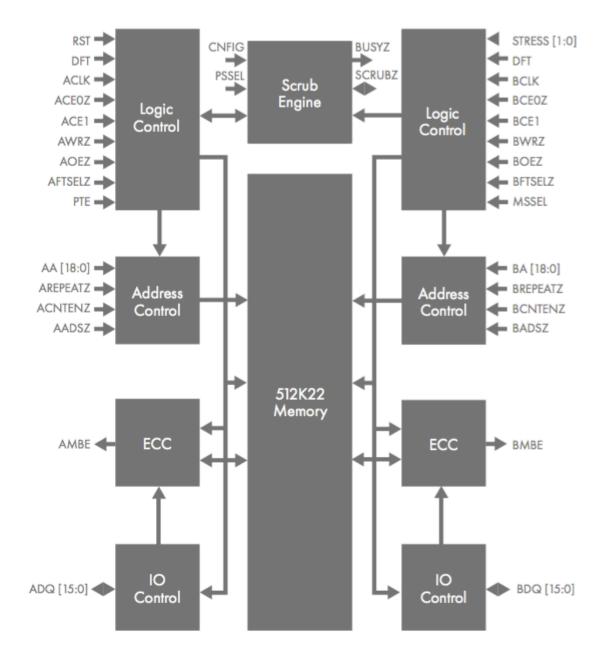

# Figure 1: Block Diagram

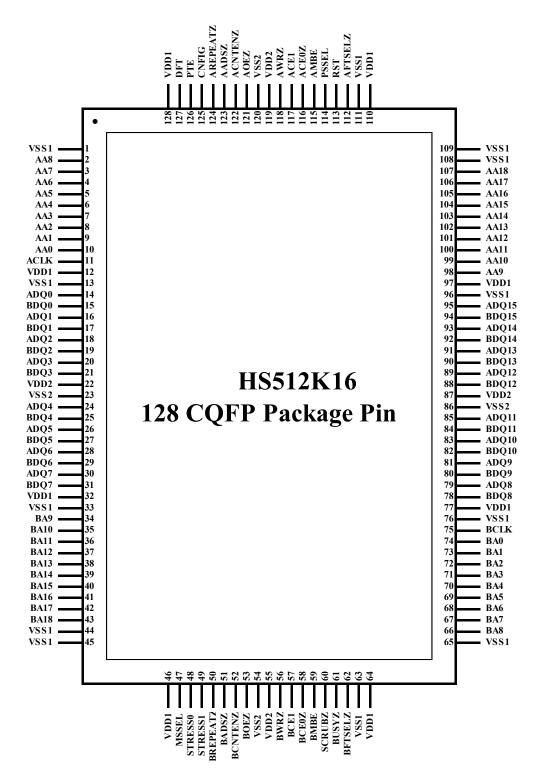

## Figure 2: Pin-out

0

# Table 1: SRAM Device Pin Description

| Port-A    | Port-B    | Туре | Active | Description                                                                                                                                                                                         |

|-----------|-----------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACLK      | BCLK      | -    |        | Clock signal                                                                                                                                                                                        |

| ACE0Z     | BCEOZ     | I    | Low    | Chip Enable-1                                                                                                                                                                                       |

| ACE1      | BCE1      | I    | High   | Chip Enable-2                                                                                                                                                                                       |

| AWRZ      | BWRZ      | I    | Low    | Write/Read Enable - Low for Write and High for Read                                                                                                                                                 |

| AA[18:0]  | BA[18:0]  | I    |        | Address bus                                                                                                                                                                                         |

| ADQ[15:0] | BDQ[15:0] | I/O  |        | Data bus                                                                                                                                                                                            |

| AOEZ      | BOEZ      | I    | Low    | Asynchronous Output Enable – Low for Read and High for Write                                                                                                                                        |

| AFTSELZ   | BFTSELZ   | Ι    | Low    | Asynchronous Pipeline/Flow-Through select – High for<br>Pipeline and Low for Flow-Through                                                                                                           |

| ACNTENZ   | BCNTENZ   | I    | Low    | Port Counter Enable                                                                                                                                                                                 |

| AADSZ     | BADSZ     | I    | Low    | Port Counter Address Load Strobe                                                                                                                                                                    |

| AREPEATZ  | BREPEATZ  | -    | Low    | Port Counter Repeat – Resets the address counter to initial address stored in Mirror Register                                                                                                       |

| AMBE      | BMBE      | 0    | High   | Multiple Bit Error Indicator                                                                                                                                                                        |

| CN        | FIG       | Ι    | High   | High for Configuration/Test Mode Enable – Low for<br>Write/Read normal/Scrub mode (asynchronous)                                                                                                    |

| BUS       | SYZ       | 0    | Low    | Busy Warning; active low to indicate the scrub cycle is coming                                                                                                                                      |

| SCR       | UBZ       | I/O  | Low    | Scrub Cycle; device is not accessible when SCRUBZ is low                                                                                                                                            |

| D         | FT        | I    | High   | DFT enable; active high for portion testing (asynchronous)                                                                                                                                          |

| PSS       | SEL       | I    |        | Port selection for SCRUB operation; Low for Port-A and<br>High for Port-B (asynchronous)                                                                                                            |

| MS        | SEL       | I    | High   | Master/Slave device selection. Low for Master and High for Slave (asynchronous). Should be treated as DC signal.                                                                                    |

| PT        | Ē         | I    | High   | Parity Test Enable; Low for reading data and High for reading parity bits (asynchronous).                                                                                                           |

| STRES     | S[1:0]    | I    |        | Margin Test setting: Should be treated as DC signal.<br>+ 01: normal mode; 00: screen mode<br>+ 10: slow mode; 11: very slow mode                                                                   |

| RS        | ST        | I    | High   | Reset Control Register to default values, prohibited the<br>other operations. All registers defined in Table 3 are set to<br>default values. All internal address counter of scrub is reset<br>to 1 |

| VD        | D2        | Ι    |        | Supply voltage for IO                                                                                                                                                                               |

| VD        | D1        | I    |        | Supply voltage for CORE                                                                                                                                                                             |

| VS        | \$2       | Ι    |        | Ground for IO                                                                                                                                                                                       |

| VS        | \$1       | Ι    |        | Ground for CORE                                                                                                                                                                                     |

C035HS512K16 provides a true synchronous Dual-Port Static SRAM interface. Each port has its Clock (xCLK); four control inputs named Chip Enable-1 (xCE0Z), Chip Enable-2 (xCE1), Write Enable (xWRZ) and Output Enable (xOEZ); 19 address inputs xA(18:0) and 16 bidirectional data bus xDQ(15:0). xWRZ controls read and write operations. During read operation, xOEZ must be asserted low to enable the outputs and xOEZ must be asserted to high to enable the inputs during write.

It is imperative to configure the Control Register after power up. In this operation, EDAC enable/disable, Scrub enable/disable, Scrub Rate, Delay between BUSYZ and SCRUBZ, Double Bit Error/Single Bit Error indicator, read-timing margin used in memory and external clock mode are configured. It can be re-configured whenever it is needed. Entire address bus of Port-A is used to configure the Control Register. Whenever the Control Register is configured or reset to default values, Scrub will restart to clean memory at address '0'.

## Table 2: SRAM Device Control Operation for Configuration Mode

| ACLK | CNFIG | AA[8] | AA[9] | AA[10] | Mode                   |

|------|-------|-------|-------|--------|------------------------|

| /    | Н     | L     | L     | L      | Write Control Register |

| /    | Н     | Н     | L     | L      | Read Control Register  |

# Table 3: Control Register Function

| Address Bits | Register | Name                                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|----------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AA[3:0]      | SRR[3:0] | Scrub Rate Register                                   | SRR sets typical scrub frequency $(1/t_{BLBL})$ @25°C& Vdd nominal) as follows:0 = 1.28 MHz1 = 1.28 MHz7 = 98.5 KHz12 = 3.1 KHz2 = 1.28 MHz8 = 49.3 KHz13 = 1.54 KHz3 = 1.28 MHz9 = 24.6 KHz14 = 770 Hz4 = 788 KHz10 = 12.3 KHz5 = 394 KHzSRR values of 0 - 3 are not recommended as they will                                                                                                                                                                                                                  |

|              |          |                                                       | result in memory unavailable to the system ~100% of the time. Default value of SRR is '7'.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AA[7:4]      | SDR[3:0] | Scrub Delay Register                                  | SDR sets the typical interval $t_{BLSL}$ between falling<br>edges of BUSYZ and SCRUBZ (@25°C & Vdd<br>nominal) as follows:<br>0 = 60 ns 6 = 570 ns 11 = 995 ns<br>1 = 145 ns 7 = 655 ns 12 = 1.08 µs<br>2 = 230 ns 8 = 740 ns 13 = 1.16 µs<br>3 = 315 ns 9 = 825 ns 14 = 1.25 µs<br>4 = 400 ns 10 = 910 ns 15 = 1.33 µs<br>5 = 485 ns<br>Minimum delay must be >25ns to insure SRAM access<br>completed before scrub cycle starts in case of minimum<br>delay is programmed. Default value of SDR is '0'.       |

| AA[11]       | BER      | Bypass EDAC<br>Register                               | 0 : Enable EDAC (default value)<br>1 : Disable EDAC including Scrub                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AA[12]       | BSR      | Bypass Scrub Register                                 | 0 : Enable Scrub (default value)<br>1 : Disable Scrub                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AA[13]       | ETR      | Error Type Register                                   | 0 : xMBE indicate double bit error (default<br>value)<br>1 : xMBE indicate singe bit error                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AA[17:14]    | PDR[3:0] | Pull Down Control<br>Register<br>(Valid when DFT = 1) | <ul> <li>16 values of PDR configure the read-timing margin:</li> <li>0: 1 pull down cells 8: 17 pull down cells</li> <li>1: 3 pull down cells 9: 19 pull down cells</li> <li>2: 5 pull down cells 10: 21 pull down cells</li> <li>3: 7 pull down cells 11: 23 pull down cells</li> <li>4: 9 pull down cells 12: 25 pull down cells</li> <li>5: 11 pull down cells 13: 27 pull down cells</li> <li>6: 13 pull down cells 14: 29 pull down cells</li> <li>7: 15 pull down cells 15: 31 pull down cells</li> </ul> |

| AA[18]       | CKR      | Clock Mode Register<br>(Valid when DFT =1)            | 0 : Self-time Mode (default value)<br>1 : Clock Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

- > Each port can be accessed independently with its Clock.

- When the EDAC is enabled, 16 data bits will be encoded to 6 parity bits and these 22 bits will be written to the memory in write operation. In read operation, 22 data bits from memory will be read, decoded, corrected (if single bit error) to 16 data bits. If double bit error occurs, xMBE will be asserted to high.

- When the EDAC is disabled, neither encoding nor decoding is executed. Only 16 data bits will be written directly into memory in write operation and 16 data bits will be read out at IO port in read operation.

- Each port can be configured to Pipeline or Flow-Through mode via xFTSELZ pin. xFTSELZ is an asynchronous signal. It should be treated as DC signal, i.e. steady state during operation.

- Flow-Through mode is configured by putting xFTSELZ to low. In this mode, write, read operation is executed fully in one clock cycle. It requires a large cycle time (low frequency).

- Pipeline mode is configured by putting xFTSELZ to high. In this mode, write operation completes in one clock cycle but read operation requires two continuous clock cycles. So, this mode can be used at higher frequency.

| xCLK | xCE0Z | xCE | xWRZ | xOEZ | ΙΟ       | Memory Mode                |

|------|-------|-----|------|------|----------|----------------------------|

|      |       | 1   |      |      | Mode     |                            |

| /    | Н     | Х   | Х    | Х    | Hi-Z     | Standby (see Note 4*)      |

| /    | L     | L   | Х    | Х    | Hi-Z     | Standby with enabled scrub |

|      |       |     |      |      |          | operation                  |

| /    | L     | Н   | L    | Н    | Data in  | Word Write                 |

| /    | L     | Н   | Н    | L    | Data out | Word Read                  |

| /    | L     | Н   | Н    | Н    | Hi-Z     | Output Deselected          |

## Table 4: SRAM Device Control Operation for Write/Read

#### Notes:

1. / : Rising edge, L: Low logic, H : High logic, X : Don't care

ADSZ, CNTENZ, REPEATZ are set to appropriate values for address access; refer to Table

5.

- 3. DFT is set to low for normal mode and high for SRAM test mode.

- 4. If ACEOZ = BCEOZ = H, chip will be standby WITHOUT SCRUB.

Each port of the memory contains an Address Counter. It allows the host access a portion of the memory sequentially. The Address Counter contains two registers: Counter Register and Mirror Register.

• Mirror Register is used to specify the initial point of the memory that the Address Counter begins accessing. Its value is not set at power-up. A known location should be loaded into this register via xADSZ during initialization if desired. Any subsequent xADSZ access during operation will update this value.

• Counter Register contains the address used to access a memory array beginning at the address specified by Mirror Register. This counter advances at the rising edge of xCLK while xCNTENZ is asserted. Whenever xREPEATZ is asserted, this counter is reset to the initial value stored in Mirror Register.

• The operation of the Address Counter is independent of all memory control signals including xWRZ, xOEZ.

# **VORAGO** TECHNOLOGIES

| EA | PIA | IA       | xCLK | <b>xCNTENZ</b> | xADSZ | <b>xREPEATZ</b> | Mode                                                            |

|----|-----|----------|------|----------------|-------|-----------------|-----------------------------------------------------------------|

| х  | Х   | An       | /    | Х              | Х     | L               | Address Counter is reset to<br>Mirror Register's value          |

| An | Х   | An       | /    | х              | L     | н               | Load Mirror Register; Load<br>Counter; External Address<br>used |

| Х  | Ар  | Ap+<br>1 | /    | L              | Н     | н               | Counter enabled,<br>Internal Address generation                 |

| Х  | Ар  | Ар       | /    | Н              | Н     | н               | External Address Blocked,<br>Counter Disabled (Ap<br>reused)    |

## Table 5: SRAM Device Control Operation for Address Counter

Notes:

- 1. / : Rising edge, L: Low logic, H : High logic, X : Don't care

- 2. EA : External Address, PIA : Previous Internal Address Used, IA : Internal Address Used

- 3. An: External address, Ap: Previous stored address; Ap+1: current address in counter mode

- 4. Control signals are set to appropriate values for Write/Read modes; refer to Table 4

- 5. xCE0Z low and xCE1 high for enabling address counter

- Scrub Operation

- Periodically, scrub engine reads and corrects every word of 512K. The whole memory will be scrubbed (cleaned) in finite duration.

- The scrub rate can be defined by user from 0.313Hz to 1.28MHz. Note that high scrub rate will reduce memory availability (throughput).

| ×MBE | xOE | SCRUBZ | BUSYZ | I/O Mode | Mode                                    |

|------|-----|--------|-------|----------|-----------------------------------------|

|      | Ζ   |        |       |          |                                         |

| Н    | L   | Н      | Н     | Read     | Error Data (**), Corrected Error bit if |

|      |     |        |       |          | it is single error, Uncorrectable Error |

|      |     |        |       |          | bit if it is double error               |

| L    | L   | Н      | Н     | Read     | Valid Data Out (**)                     |

| Х    | Х   | Н      | Н     | Х        | Device Ready                            |

| Х    | Х   | Н      | L     | Х        | Device Ready/Early Scrub Request        |

|      |     |        |       |          | Coming                                  |

## Table 6: SRAM Device Control Operation for EDAC

HS512K16

|   | Х | Х | L | Х | Not        | Scrubbing - Device Busy | ] |

|---|---|---|---|---|------------|-------------------------|---|

| _ |   |   |   |   | Accessible |                         |   |

#### Notes:

xMBE is only valid in EDAC operation modes (Read with EDAC enable or Scrub by Port-A or Port-B).

xMBE indicates Double Bit Error if ETR bit in the Control Register is '0'.

xMBE indicates Single Bit Error if ETR bit in the Control Register is '1'.

"X": is defined as "don't care" condition.

# Table 7: AC Electrical Characteristics

|                                           |                     |     |               |        |       |          |        | [        | Datashee | t   |        |         |     |        |           |     | -    |

|-------------------------------------------|---------------------|-----|---------------|--------|-------|----------|--------|----------|----------|-----|--------|---------|-----|--------|-----------|-----|------|

| Temp=125C,                                |                     |     |               | Flow-T | hroug | า        |        | Pipeline |          |     |        |         |     | Co     | nfigurati | on  |      |

| Vdd1=1.35V, Vdd2=3V                       |                     |     | EDAC Disabled |        |       | AC Enabl | ed     | ED/      | AC Disab | led | ED     | AC Enab | ed  |        | Register  |     |      |

|                                           | mode 0              |     |               | mode 1 |       |          | mode 4 |          |          |     | mode 2 |         |     | mode 3 | 1         | ⊢   |      |

| Parameter                                 | Symbol              | Min | Typical       | Max    | Min   | Typical  | Max    | Min      | Typical  | Max | Min    | Typical | Max | Min    | Typical   | Max | Unit |

| Clock cycle                               | T <sub>chch</sub>   | 20  |               |        | 20    |          |        | 15       |          |     | 15     |         |     | 15     |           |     | ns   |

| Clock high pulse width                    | T <sub>chcl</sub>   | 5   |               |        | 5     |          |        | 5        |          |     | 5      |         |     | 5      |           |     | ns   |

| Clock low pulse width                     | T <sub>clch</sub>   | 5   |               |        | 5     |          |        | 5        |          |     | 5      |         |     | 5      |           |     | ns   |

| Address setup time                        | Tavch               | 5   |               |        | 5     |          |        | 5        |          |     | 5      |         |     | 5      |           |     | ns   |

| Address hold time                         | T <sub>chax</sub>   | 0.5 |               |        | 0.5   |          |        | 0.5      |          |     | 0.5    |         |     | 0.5    |           |     | ns   |

| Chip Enable setup time                    | T <sub>cvch</sub>   | 5   |               |        | 5     |          |        | 5        |          |     | 5      |         |     | 5      |           |     | ns   |

| Chip Enable hold time                     | T <sub>chcx</sub>   | 2   |               |        | 2     |          |        | 2        |          |     | 2      |         |     | 2      |           |     | ns   |

| Write / Read Enable setup time            | Twvch               | 2   |               |        | 2     |          |        | 2        |          |     | 2      |         |     | 2      |           |     | ns   |

| Write / Read Enable hold time             | T <sub>chwx</sub>   | 0.5 |               |        | 0.5   |          |        | 0.5      |          |     | 0.5    |         |     | 0.5    |           |     | ns   |

| Data input setup time                     | T <sub>dvch</sub>   | 1.5 |               |        | 2.5   |          |        | 1.5      |          |     | 2.5    |         |     | 2.5    |           |     | ns   |

| Data input hold time                      | T <sub>chdx</sub>   | 1.5 |               |        | 1.5   |          |        | 1.5      |          |     | 1.5    |         |     | 1.5    |           |     | ns   |

| xADSZ setup time                          | Tasvch              | 4   |               |        | 4     |          |        | 4        |          |     | 4      |         |     | 4      |           |     | ns   |

| xADSZ hold time                           | T <sub>chasx</sub>  | 0.5 |               |        | 0.5   |          |        | 0.5      |          |     | 0.5    |         |     | 0.5    |           |     | ns   |

| xCNTENZ setup time                        | T <sub>cevch</sub>  | 4   |               |        | 4     |          |        | 4        |          |     | 4      |         |     | 4      |           |     | ns   |

| xCNTENZ hold time                         | T <sub>chcex</sub>  | 0.5 |               |        | 0.5   |          |        | 0.5      |          |     | 0.5    |         |     | 0.5    |           |     | ns   |

| xREPEATZ setup time                       | T <sub>rpvch</sub>  | 4   |               |        | 4     |          |        | 4        |          |     | 4      |         |     | 4      |           |     | ns   |

| xREPEATZ hold time                        | T <sub>chrpx</sub>  | 0.5 |               |        | 0.5   |          |        | 0.5      |          |     | 0.5    |         |     | 0.5    |           |     | ns   |

| Access time from Clock high               | T <sub>chqv</sub>   |     |               | 16     |       |          | 17     |          |          | 12  |        |         | 12  |        |           | 16  | ns   |

| Output hold time from Clock high          | T- <sub>chax</sub>  | 6   |               |        | 6     |          |        | 6        |          |     | 6      |         |     | 6      |           |     | ns   |

| Clock high to xMBE valid                  | T <sub>chmy</sub>   |     |               |        |       |          | 17     |          |          |     |        |         | 12  |        |           |     | ns   |

| Clock high to xMBE change                 | T <sub>chmx</sub>   |     |               |        | 6     |          |        |          |          |     | 6      |         |     |        |           |     | ns   |

| Access time from Output Enable low.       | T <sub>olqv</sub>   |     |               | 8      |       |          | 8      |          |          | 8   |        |         | 8   |        |           | 8   | ns   |

| Output Enable high to Data Output High-Z  | Tohqz               |     |               | 5      |       |          | 5      |          |          | 5   |        |         | 5   |        |           | 5   | ns   |

| Output Enable low to Data Output change   | T <sub>olgx</sub>   |     |               | 6      |       |          | 6      |          |          | 6   |        |         | 6   |        |           | 6   | ns   |

| Access time from Flow-Through enable      | T <sub>ftvqv</sub>  |     |               | 6      |       |          | 6      |          |          | 6   |        |         | 6   |        |           | 6   | ns   |

| Output hold time from Flow-Through enable | T <sub>ftvqx</sub>  |     |               | 4      |       |          | 4      |          |          | 4   |        |         | 4   |        |           | 4   | ns   |

| Flow-Through enable to xMBE valid         | T <sub>ftvmv</sub>  |     |               | 5      |       |          | 5      |          |          | 5   |        |         | 5   |        |           | 5   | ns   |

| Flow-Through enable to xMBE change        | T <sub>ftvmx</sub>  |     |               | 5      |       |          | 5      |          |          | 5   |        |         | 5   |        |           | 5   | ns   |

| Chip Enable turn off to output tri-state  | T <sub>civqz</sub>  |     |               | 5      |       |          | 5      |          |          | 5   |        |         | 5   |        |           | 5   | ns   |

| Chip Enable turn on to output change      | T <sub>civqx</sub>  |     |               | 5      |       |          | 5      |          |          | 5   |        |         | 5   |        |           | 5   | ns   |

| xOEZ setup time with Clock                | Tovch               | 9   |               |        | 9     |          |        | 9        |          |     | 9      |         |     |        |           |     | ns   |

| xOEZ hold time with Clock                 | T <sub>chox</sub>   | 0.5 |               |        | 0.5   |          |        | 0.5      |          |     | 0.5    |         |     |        |           |     | ns   |

| Clock-to-Clock Offset                     |                     | 7   |               |        | 7     |          |        | 7        |          |     | 7      |         |     |        |           |     |      |

| (clock skew Write-Read)                   | T <sub>chchs1</sub> |     |               |        |       |          |        |          |          |     | /      |         |     |        |           |     | ns   |

| Clock-to-Clock Offset                     | T <sub>chchs2</sub> | 7   |               |        | 7     |          |        | 7        |          |     | 7      |         |     |        |           |     | ns   |

| (clock skew Read-Write)                   | · ununsz            | · · |               |        |       |          |        |          |          |     |        |         |     |        |           |     | Ľ    |

#### Notes:

- 1. All timings are used for both ports where applicable.

- 2. Flow-Through parameters are applied when xFTSELZ set to low for that port

- 3. Pipeline parameters are applied when xFTSELZ set to high for that port.

- 4. Conditions: Temperature = 125C,  $V_{dd1}$  = 1.35V,  $V_{dd2}$  = 3V

- 5. SLEW: 2.0ns, Load: 5pF

\* The clock-to-clock offset is minimum delay required between clocks when both ports access same location with one port Write and the other Read or vice versa. Violation of this timing creates uncertainty in Read port Data Out, which can be old data, new data or combined of old and new data. See Timing Waveform 4.

# **VORAGO** TECHNOLOGIES

# Table 7: AC Electrical Characteristics (continued)

| Town 1250                                                  |                     |        |               | Flow-T | hroug  | h            |     |               |         | Pipe | line            |         |     | Co              | onfigurati | on  |      |

|------------------------------------------------------------|---------------------|--------|---------------|--------|--------|--------------|-----|---------------|---------|------|-----------------|---------|-----|-----------------|------------|-----|------|

| Temp=125C,<br>Vdd1=1.35V, Vdd2=3V                          |                     |        | EDAC Disabled |        |        | EDAC Enabled |     | EDAC Disabled |         |      | ED              | AC Enab | led |                 | Register   |     |      |

|                                                            |                     | mode 0 |               |        | mode 1 |              |     | mode 4        |         |      | mode 2          |         |     | mode 3          |            |     |      |

| Parameter                                                  | Symbol              | Min    | Typical       | Max    | Min    | Typical      | Max | Min           | Typical | Max  | Min Typical Max |         |     | Min Typical Max |            | Max | Unit |

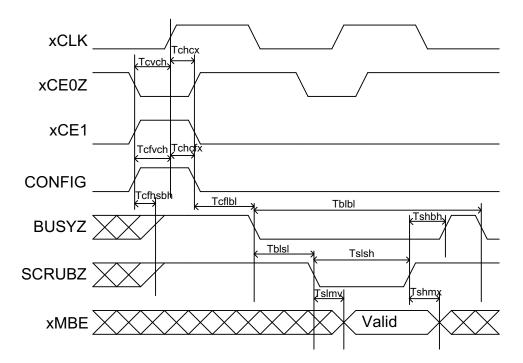

| BUSYZ low to SCRUBZ low<br>(SDR = 0, SRR = 7)              | T <sub>blsl</sub>   |        |               |        |        | 70           |     |               |         |      |                 | 70      |     |                 |            |     | ns   |

| BUSYZ low to BUSYZ low (Scrub Cycle)<br>(SDR = 0, SRR = 7) | T <sub>blbl</sub>   |        |               |        |        | 12400        |     |               |         |      |                 | 12400   |     |                 |            |     | ns   |

| SCRUBZ low to SCRUBZ high                                  | $T_{slsh}$          |        |               |        |        | 420          |     |               |         |      |                 | 420     |     |                 |            |     | ns   |

| SCRUBZ high to BUSYZ high                                  | Tshbh               |        |               |        |        | 110          |     |               |         |      |                 | 110     |     |                 |            |     | ns   |

| SCRUBZ low to xMBE valid (flow-through)                    | T <sub>slmv</sub>   |        |               |        |        | 200          |     |               |         |      |                 | 200     |     |                 |            |     | ns   |

| SCRUBZ high to xMBE change                                 | Tshmx               |        |               |        |        | 8            |     |               |         |      |                 | 8       |     |                 |            |     | ns   |

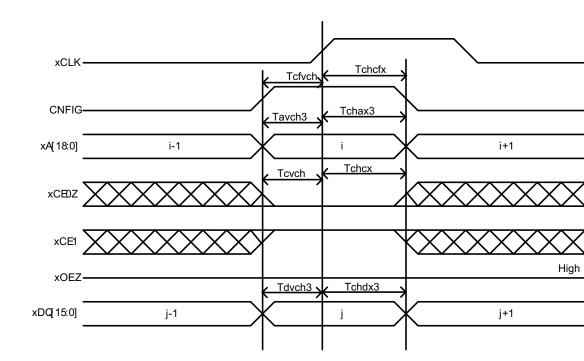

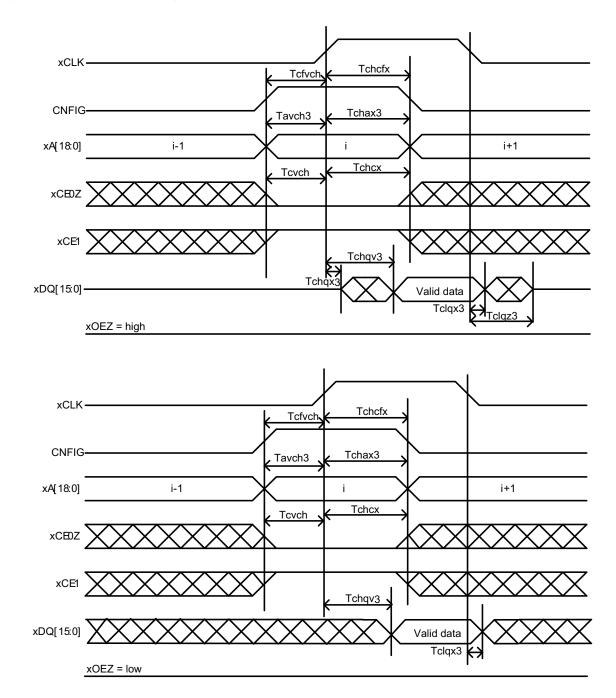

| CNFIG setup time with Clock                                | Tcfvch              |        |               |        |        |              |     |               |         |      |                 |         |     | 6               |            |     | ns   |

| CNFIG hold time with Clock                                 | T <sub>chcfx</sub>  |        |               |        |        |              |     |               |         |      |                 |         |     | 3               |            |     | ns   |

| Read Register access time                                  | T <sub>chqv3</sub>  |        |               |        |        |              |     |               |         |      |                 |         |     |                 |            | 11  | ns   |

| Read Register output hold time                             | T <sub>chqx 3</sub> |        |               |        |        |              |     |               |         |      |                 |         |     | 4               |            |     | ns   |

| Chip enable turn off to BUSYZ high                         | $T_{civbh}$         |        |               |        |        |              | 10  |               |         |      |                 |         | 10  |                 |            |     | ns   |

| Chip enable turn off to SCRUBZ high                        | Tcivsh              |        |               |        |        |              | 15  |               |         |      |                 |         | 15  |                 |            |     | ns   |

| MSSEL high to BUSYZ high.<br>(Slave mode)                  | T <sub>mhbh</sub>   |        |               |        |        |              | 9   |               |         |      |                 |         | 9   |                 |            |     | ns   |

| Config low to BUSYZ low (Tini)                             | T <sub>cflbl</sub>  |        |               |        |        |              | 130 |               |         |      |                 |         | 130 |                 |            |     | ns   |

| Config high to BUSYZ high                                  | Tcfhbh              |        |               |        |        |              | 9   |               |         |      |                 |         | 9   |                 |            |     | ns   |

| Config high to SCRUBZ high                                 | T <sub>cfhsh</sub>  |        |               |        |        |              | 13  |               |         |      |                 |         | 13  |                 |            |     | ns   |

| SCRUBZ low to output tri-state                             | Tslqz               |        |               |        |        |              | 3   |               |         |      |                 |         | 3   |                 |            |     | ns   |

| Pulse width of RST                                         | Tpwrst              |        |               |        | 5      |              |     |               |         |      |                 |         |     |                 |            |     | ns   |

- 1. All timings are used for both ports where applicable.

- 2. Flow-Through parameters are applied when xFTSELZ set to low for that port.

- 3. Pipeline parameters are applied when xFTSELZ set to high for that port.

- 4. Conditions: Temperature = 125C,  $V_{dd1}$  = 1.35V,  $V_{dd2}$  = 3V

- 5. SLEW: 2ns, Load: 5pF

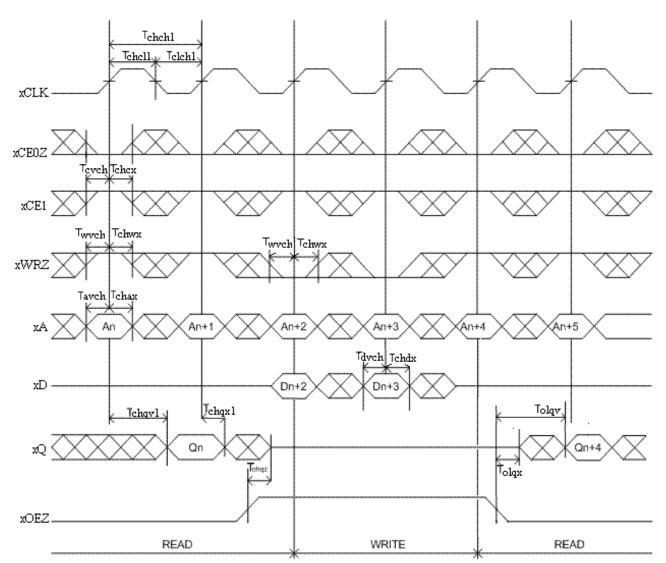

# Timing Waveform1: Flow-Through (mode 0, 1) Read-to-Write-to-Read

- 1. Output state (High, Low or High-impedance) is determined by previous cycle control signals.

- 2. xADSZ is set to low for external address using.

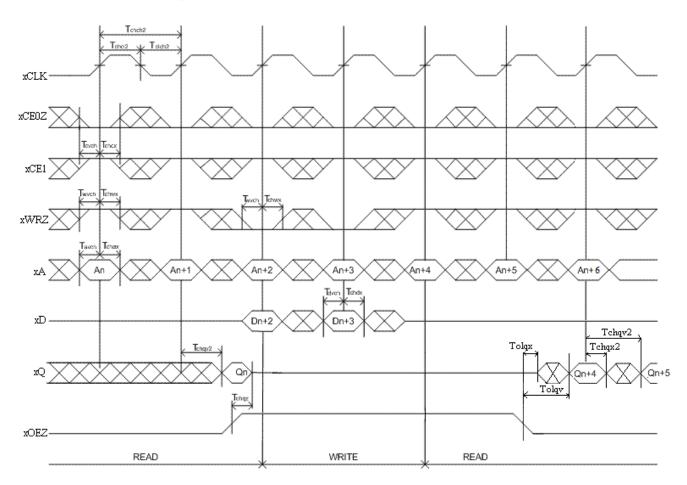

# Timing Waveform 2: Pipeline (mode 2, 4) Read-to-Write-to-Read

- 1. Output state (High, Low or High-impedance) is determined by previous cycle control signals.

- 2. xADSZ is set to low for external address using.

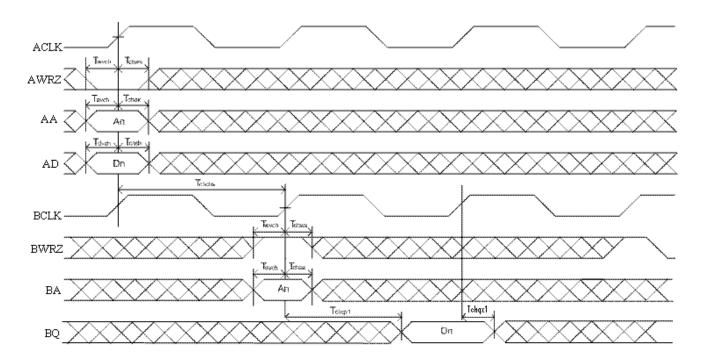

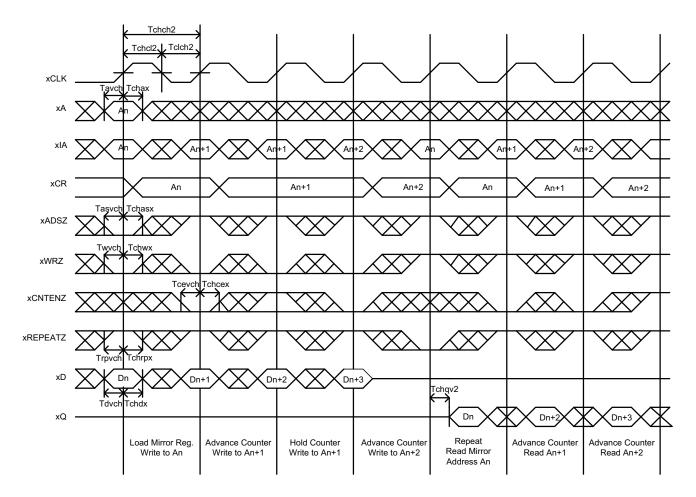

# Timing Waveform 3: Port "A" Write to Port "B" Read Flow-Through (mode 0, 1) (at the same address)

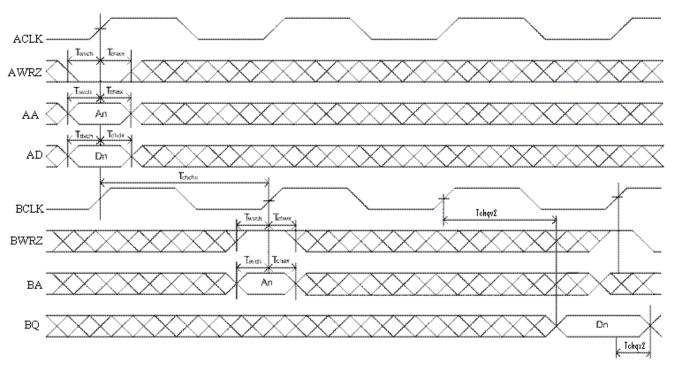

# Timing Waveform 4: Port "A" Write to Port "B" Read Pipeline (mode 2, 4) (at the same address)

- 1. xCE0Z and xADSZ are set to low; xCE1, xCNTENZ and xREPEATZ are set to high.

- 2. BOEZ is low for Port "B" when Port B is reading, AOEZ is set to high for Port "A" when Port A is writing.

- **3.** If T<sub>chchs</sub> < minimum specified value, then the data from read port is not valid.

- 4. All timings are the same for both ports.

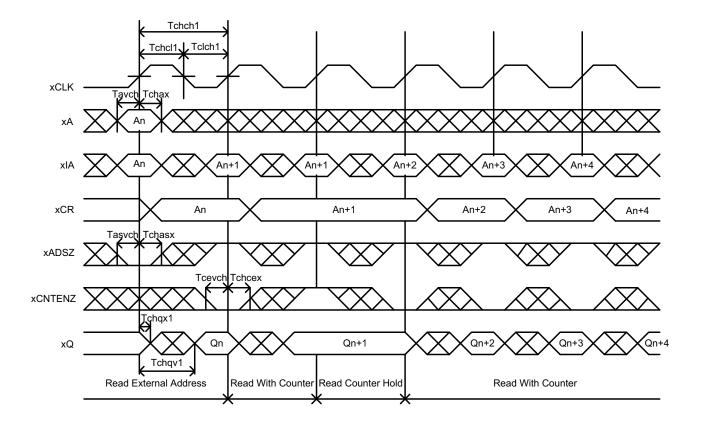

# Timing Waveform 5: Read Flow-Through (mode 0, 1) with Address Counter Advance

# Timing Waveform 6: Read Pipeline (mode 4, 2) with Address Counter Advance

- 1. xCE0Z, xOEZ are set to low; xCE1, xWRZ, xREPEATZ are set to high.

- 2. If there is no address change via xADSZ = Low (loading a new address) or xCNTENZ = Low (advancing the address), i.e. xADSZ = High and xCNTENZ = High, then the data output remains constant for subsequent cycles.

- 3. xIA: used Address for Write/Read operation of memory

- **4.** xCR: Counter Register

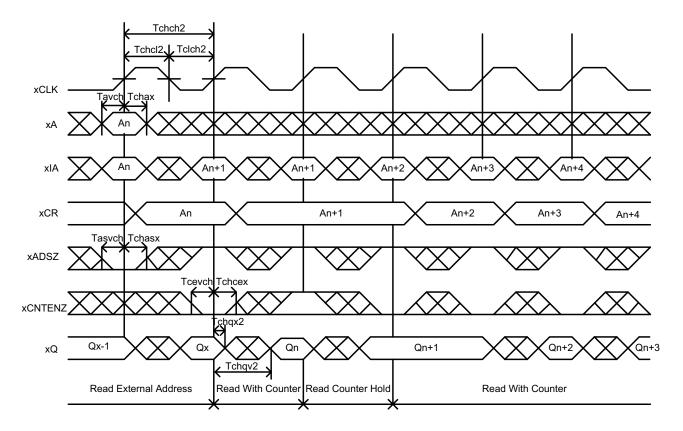

## Timing Waveform 7: Write with Address Counter (Flow-through/Pipeline, (modes 0, 1, 4, 2))

#### Notes:

1. xCE0Z, xWRZ are set to low; xCE1, xOEZ, xREPEATZ are set to high.

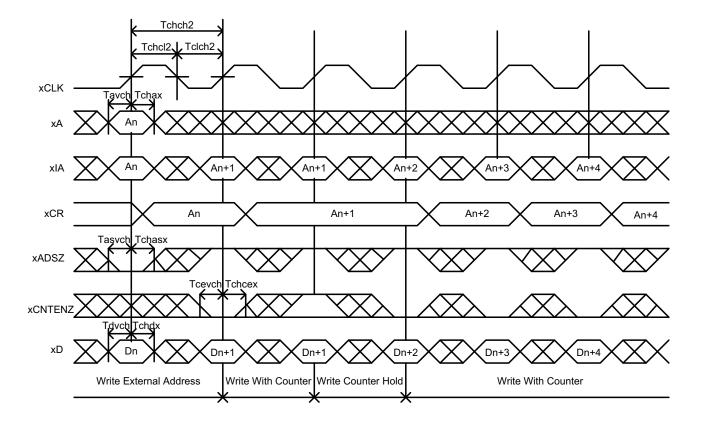

## **Timing Waveform 8: Counter Repeat**

- 1. xCEOZ is set to low; xCE1 is set to high, xOEZ is set to low for Read operation, xOEZ is set to high for Write operation

- 2. Output state (High, Low or High-impedance) is determined by previous cycle control signals

- 3. xIA: used Address for Write/Read operation of memory

- 4. xCR: Counter Register

# Timing Waveform 9: Scrub Operation for master mode (modes 1, 2)

- Scrub operation when ACE0Z = 0 or BCE0Z = 0 and CONFIG = 0, Enable EDAC and Enable scrub

- 2. xMBE is valid for flowthrough mode xCR: Counter Register

- 3. xMBE is invalid for pipeline mode

- 4. BUSYZ is kept high during slave mode operation

# Timing Waveform 10: Configuration/Test Write mode

- 1. ACE0Z is set to low; ACE1, AOEZ, CNFIG are set to high for writing into Control Register and Test Registers of Port-A

- 2. For Port-B test: BCE0Z is set to low; BCE1, BOEZ, CNFIG are set to high for writing into Test Registers of Port-B

# Timing Waveform 11: Configuration/Test Read mode (mode 3)

#### <u>Notes:</u>

- 1. ACE0Z is set to low; ACE1, CNFIG are set to high for reading from Control Register and Test Registers of Port-A

- 2. For Port-B Test: BCE0Z is set to low; BCE1, CNFIG are set to high for reading from Test Registers of Port-B

3.

#### > Test Modes (not recommended for customer/system use)

This chip supports both SRAM test modes (clock mode, pull down control enable and margin tests) and EDAC test modes.

Direct Mux Test: stored data of the whole RAM can be tested directly by disabling EDAC in the configuration mode (BER = 1) and controlling the PTE pin. When setting PTE to low, 16 data bits can be read out directly to 16 I/O pins on each port; if PTE is set to high, six parity bits will be read out to xDQ[5:0].

• Design for Test mode is done by strapping DFT pin to high. In this mode, the value of CKR register and PDR[3:0] registers must be configured after power up.

- **Clock Mode**: This mode is controlled by CKR. When this register is set to high, internal self-time write circuit is disabled, the sense amplify latches data at the falling edge of xCLK

- Self-Time Control Test: PDR{3:0} defines the timing margin for self-time circuit. In normal mode, the value 0110 of PDR[3:0] (13 pull down cells) gives ~150mV difference between BL and BLX for the sense amplify latching.

• Margin (stress) Test: There are four modes related to margin test for the RAM. These are controlled by STRESS[1:0]. The functions of these modes are briefly summarized as below:

- "01" normal mode: users use this mode in normal operation.

- "00" screen mode: speed up internally the timing. It is to detect weak or defective circuits.

- "10" slow mode: this mode is to add more delays to latch data output.

- "11" very slow mode: this is another yield mode to latch data output.

• A set of two registers is used to test the encoder, decoder of each ECC. All internal registers (Scrub Counter, Address Counters, Mirror Register and Control Register) can also be read out to test. The test is done separately for ECC of Port-A/Port-B. The CNFIG must be set to high to enter EDAC test modes. In test modes, memory access and scrub operation are inhibited.

## HS512K16

- Test Write Register (6 bits) is used to test the encoder block. 16 data bits will be encoded to 6 parity bits and stored in this register for later reading out to test. In read phase, 6 parity bits from test write register and xMBE bit from test read register are read out on data bus xDQ(6:0)

- Test Read Register (16 decoded data bits + 1 error bit) is used to test the decoder block. 16 data bits and 6 lowest bits of address bus will be decoded and fixed error, then 16 decoded and fixed error data bits + 1 error bit xMBE stored in this register. In read phase, 16 data bits from test read register are read out on data bus xDQ(15:0).

- Address Counters and Mirror Registers (19 bits) can be read out by its I/O port (16 bits) in two times. The setting is described in Table 9a/9b.

- Scrub Counter (19 bits) can be read out by I/O (16 bits) of Port-A. in two times.

| ACLK | AA7 | AA8 | AA9 | AA10 | Mode                                                            |

|------|-----|-----|-----|------|-----------------------------------------------------------------|

| /    | Х   | L   | L   | L    | Write Control Register                                          |

| /    | Х   | Н   | L   | L    | Read Control Register on ADQ(15:0)                              |

| /    | Х   | L   | Н   | L    | Scrub Counter Out (16 lower bits) on                            |

| /    | Х   | Н   | Н   | L    | ADQ(15:0)<br>Scrub Counter Out (3 higher bits) on<br>ADQ(15:13) |

| /    | L   | L   | L   | Н    | ECC Write Block Test                                            |

| /    | Н   | L   | L   | Н    | ECC Write Block Register Out on ADQ(6:0)                        |

| /    | L   | Н   | L   | Н    | ECC Read Block Test                                             |

| /    | Н   | Н   | L   | Н    | ECC Read Block Register Out on ADQ(15:0)                        |

| /    | L   | L   | Н   | Н    | Mirror Register Out (16 lowest bits) on<br>ADQ(15:0)            |

| /    | Н   | L   | Н   | Н    | Mirror Register Out (3 highest bits) on ADQ(15:13)              |

| /    | L   | Н   | Н   | Н    | Counter Register Out (16 lowest bits) on ADQ(15:0)              |

| /    | Н   | Н   | Н   | Н    | Counter Register Out (3 highest bits) on ADQ(15:13)             |

## Table 9a: Test Mode Operation for Port-A

## Table 9b: Test Mode Operation for Port-B

| BCLK | BA7 | BA8 | BA9 | <b>BA10</b> | Mode                                                  |

|------|-----|-----|-----|-------------|-------------------------------------------------------|

| /    | L   | L   | L   | Н           | ECC Write Block Test                                  |

| /    | Н   | L   | L   | Н           | ECC Write Block Register Out on BDQ(6:0)              |

| /    | L   | Н   | L   | Н           | ECC Read Block Test                                   |

| /    | Н   | Н   | L   | Н           | ECC Read Block Register Out on BDQ(15:0)              |

| /    | L   | L   | Н   | Н           | Mirror Register Out (16 lowest bits) on BDQ(15:0)     |

| /    | Η   | L   | H   | Н           | Mirror Register Out (3 highest bits) on BDQ(15:13)    |

| /    | L   | Н   | Н   | Н           | Counter Register Out (16 lowest bits) on<br>BDQ(15:0) |

| /    | Н   | Н   | Н   | Н           | Counter Register Out (3 highest bits) on BDQ(15:13)   |

## Table 10: Absolute Maximum Rating

| Symbol           | Parameter                            | Limits        |

|------------------|--------------------------------------|---------------|

| V <sub>DD1</sub> | DC supply voltage (Core)             | -0.3 to 2.0V  |

| V <sub>DD2</sub> | DC supply voltage (I/O)              | -0.3 to 3.6V  |

| V <sub>I/O</sub> | Voltage on any pin                   | -0.3 to 3.6V  |

| T <sub>STG</sub> | Storage temperature                  | -65 to +150°C |

| P <sub>D</sub>   | Maximum power dissipation            | 1.2W          |

| T,               | Maximum junction temperature         | +150°C        |

| οıc              | Thermal resistance, junction-to-case | 5°C/W         |

| I <sub>I</sub>   | DC input current                     | ±5 mA         |

#### Notes:

Stresses outside the listed absolute maximum ratings above may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond these rating conditions is not recommended. Exposure to maximum rating conditions for extended periods may affect the device's reliability and performance.

## Table 11: Recommended Operating Conditions

| Symbol           | Parameter                | Limits                                                             |

|------------------|--------------------------|--------------------------------------------------------------------|

| V <sub>DD1</sub> | DC supply voltage (Core) | 1.35 to 1.65V                                                      |

| V <sub>DD2</sub> | DC supply voltage (I/O)  | 3.15 to 3.45V                                                      |

| T <sub>c</sub>   | Case temperature range   | (C) Screening: -55 to<br>+150°C<br>(W) Screening: -40 to<br>+150°C |

| V <sub>IN</sub>  | DC input voltage         | OV to V <sub>DD2</sub>                                             |

## <u>Notes</u>:

- 1. Measured for initial qualification. After process or design, changes could affect input/output capacitance.

- 2. Provided as a design limit but not guaranteed or tested.

- 3. Not more than one output maybe shorted at a time for maximum duration of one second.

- 4.  $V_{IH} = V_{DD2}(max), V_{IL} = 0$

# Table 12: DC Electrical Characteristics

| Symbol                              | Parameter                                         | Condition                                                                                                                                     | Min            | Max           | Unit |

|-------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|------|

| VIH                                 | High-level input voltage                          |                                                                                                                                               | $0.7^*V_{DD2}$ |               | V    |

| VIL                                 | Low-level input voltage                           |                                                                                                                                               |                | $0.3*V_{DD2}$ | V    |

| Vol                                 | Low-level output voltage                          | $I_{OL}=4mA$ , $V_{DD2}=V_{DD2}(min)$                                                                                                         |                | $0.2*V_{DD2}$ | V    |

| V <sub>OH</sub>                     | High-level output voltage                         | $I_{OH}$ =-4mA, $V_{DD2}$ = $V_{DD2}$ (min)                                                                                                   | $0.8*V_{DD2}$  |               | V    |

| C <sub>IN</sub> <sup>1</sup>        | Input capacitance                                 | f = 1MHz @ 0V                                                                                                                                 |                | 1.799         | рF   |

| C <sub>IO</sub> <sup>1</sup>        | Bidirectional I/O<br>capacitance                  | f = 1MHz @ 0V                                                                                                                                 |                | 1.798         | pF   |

| l <sub>in</sub>                     | Input leakage current                             | V <sub>IN</sub> =V <sub>DD2</sub> and V <sub>SS</sub>                                                                                         | -6             | 206           | nA   |

| `l <sub>oz</sub>                    | Tri-state output leakage<br>current               | V <sub>O</sub> =V <sub>DD2</sub> and V <sub>SS</sub><br>V <sub>DD2</sub> = V <sub>DD2</sub> (max),<br>GZ=V <sub>DD2</sub> (max)               | ο              | 0             | А    |

| los <sup>2,3</sup>                  | Short-circuit output<br>current                   | $V_{DD2} = V_{DD2}(max), V_{O} = V_{DD2}$ $V_{DD2} = V_{DD2}(max), V_{O} = V_{SS}$                                                            | -1             | 9             | mA   |

| I <sub>DD1</sub> (OP <sub>1</sub> ) | V <sub>DD1</sub> supply operating current @ 1MHz  | Input: $V_{II}=V_{SS}+0.2V$ ,<br>$V_{IH}=V_{DD2}-0.2V$ , $I_{OUT}=0A$<br>$V_{DD1}=V_{DD1}$ (max), $V_{DD2}=$<br>$V_{DD2}$ (max)               |                | 8             | mA   |

|                                     | V <sub>DD1</sub> supply operating current @ 50MHz | Input: $V_{II}=V_{SS}+0.2V$ ,<br>$V_{IH}=V_{DD2}-0.2V$ , $I_{OUT}=0A$<br>$V_{DD1}=V_{DD1}(max)$ , $V_{DD2}=$<br>$V_{DD2}(max)$                |                | 293           | mA   |

| I <sub>DD2</sub> (OP <sub>1</sub> ) | V <sub>DD2</sub> supply operating current @ 1MHz  | Input: $V_{IL} = V_{SS} + 0.2V$ ,<br>$V_{IH} = V_{DD2} - 0.2V$ , $I_{OUT} = 0A$<br>$V_{DD1} = V_{DD1} (max)$ , $V_{DD2} =$<br>$V_{DD2} (max)$ |                | 1             | mA   |

| I <sub>DD2</sub> (OP <sub>2</sub> ) | V <sub>DD2</sub> supply operating current @ 50MHz | Input: $V_{IL} = V_{SS} + 0.2V$ ,<br>$V_{IH} = V_{DD2} - 0.2V$ , $I_{OUT} = 0A$<br>$V_{DD1} = V_{DD1} (max)$ , $V_{DD2} =$<br>$V_{DD2} (max)$ |                | 52            | mA   |

| I <sub>DD1</sub> (SB)⁴              |                                                   | CMOS inputs, I <sub>OUT</sub> =0A                                                                                                             |                | 5             | mA   |

| I <sub>DD2</sub> (SB) <sup>4</sup>  | Supply stand-by current<br>@ 0MHz                 | $E1Z = V_{DD2}-0.2V, E2 = GND$<br>$V_{DD1} = V_{DD1}(max), V_{DD2} =$<br>$V_{DD2}(max)$                                                       |                | 5             | υA   |

| I <sub>DD1</sub> (SB) <sup>4</sup>  |                                                   | CMOS inputs, I <sub>OUT</sub> =0A                                                                                                             |                | 63            | mA   |

| I <sub>DD2</sub> (SB) <sup>4</sup>  | Supply stand-by current<br>@ 50MHz                | $E1Z = V_{DD2}$ -0.2V, $E2 = GND$<br>$V_{DD1} = V_{DD1}(max)$ , $V_{DD2} =$<br>$V_{DD2}(max)$                                                 |                | 0.2           | mA   |

#### Notes:

PTV: Strong\_125\_1.65V\_3.6V

Stresses outside the listed absolute maximum ratings above may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond these rating conditions is not recommended. Exposure to maximum rating conditions for extended periods may affect the device's reliability and performance.

# Table 13: Radiation Hardened Performance

| Parameter | Description                                   | Min    | Тур | Max | Unit             |

|-----------|-----------------------------------------------|--------|-----|-----|------------------|

| TID       | Total Ionizing Dose                           | 300K   | -   | -   | Rad (Si)         |

| SER       | Soft Error Rate (EDAC enabled)                | <1e-10 | -   | -   | errors / bit-day |

| LET       | Linear Energy Transfer (latch-up<br>immunity) | 110    | -   | -   | MeV-cm2          |

\*Geosynchronous orbit solar min. with 100 mils of Al shielding

With EDAC enabled, the Scrub Engine should also be enabled and running at an appropriate frequency to prevent accumulation of errors in the memory in order to achieve consistently low SER over time.

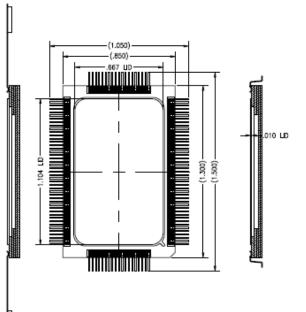

# Figure 3: Packaging Dimensions

# Table 14: Part Ordering Information

| Description                                         | Part number         | Environment         | Temperature<br>Range | Package         |

|-----------------------------------------------------|---------------------|---------------------|----------------------|-----------------|

| High-temperature<br>Synchronous Dual-port<br>SRAM   | HS512K16-CQ128A103E | Extreme temperature | -55° to 200°C        | Ceramic 128 QFP |

| Radiation-hardened<br>Synchronous Dual-port<br>SRAM | HS512K16-CQ128A1F0E | Radiation-hardened  | -55° to 125°C        | Ceramic 128 QFP |

| High-temperature<br>Synchronous Dual-port<br>SRAM   | HS512K16-DA103E     | Extreme temperature | -55° to 200°C        | Die             |

| Radiation-hardened<br>Synchronous Dual-port<br>SRAM | HS512K16-DA1F0E     | Radiation hardened  | -55° to 125°C        | Die             |

## Table 15: Revision History

| Revision Date           | Changes                                                             | Author |

|-------------------------|---------------------------------------------------------------------|--------|

| March 30, 2010          | Correct the read access time controlled by OEZ for timing           | SDS    |

|                         | waveform 1, 2 at the pages 13, 14                                   | 303    |

| May 14, 2010            | Updated control register table with typical measured Scrub Rate     |        |

|                         | and Scrub delay values by setting                                   |        |

|                         | Reformatted AC Tables to place all modes side-by-side to simplify   |        |

|                         | comparing modes                                                     |        |

|                         | Updated AC Tables with values extracted from characterization       |        |

|                         | measurements                                                        | SST    |

|                         | Changed AC Timing Slew and Load footnote to reflect more            | 331    |

|                         | reasonable load conditions                                          |        |

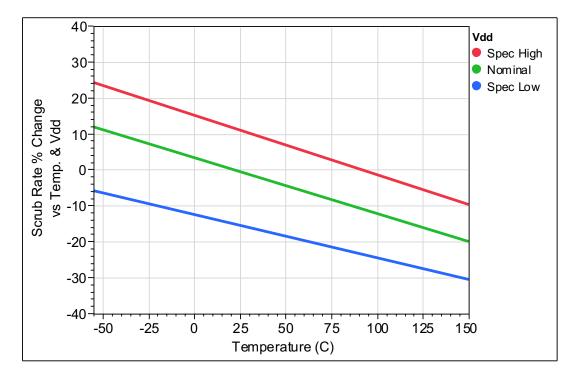

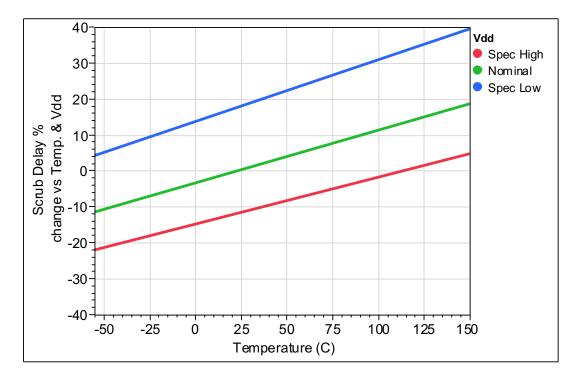

|                         | Replaced Scrub Rate & Scrub Delay vs temperature tables with        |        |

|                         | typical Scrub Rate and Scrub Delay % change vs Temperature          |        |

|                         | graphs & typical temperature coefficients                           |        |

|                         | Added package drawing                                               |        |

| May 27, 2010            | Updated control register table with typical measured Scrub rate     |        |

|                         | and Scrub delay values by setting using nominal Vdd voltage         |        |

|                         | instead of minimum Vdd voltage                                      | SST    |

|                         | Updated typical Scrub Rate and Scrub Delay % change graphs to       |        |

|                         | include fits at Vdd = Spec Low, Nominal and Spec High values        |        |

| Feb. 7, 2011            | Updated clock to data valid (Tchqv) for pipeline modes to reflect   | SST    |

|                         | larger sample testing results                                       | 331    |

| Feb. 17, 2011           | Updated radiation performance numbers to reflect the actual results | SST    |

|                         | from radiation testing.                                             | 331    |

| Apr. 4, 2011            | Added "Draft" watermark                                             |        |

|                         | Added "SST Confidential" Footer                                     | SST    |

|                         | Changed contact info to David Duff                                  |        |

| Nov 14, 2013            | Radiation performance spec changed as follows                       |        |

|                         | TID > 300Krads                                                      |        |

|                         | SER < 1e-10 errors/bit-day (with ECC and Scrub)                     | SST    |

|                         | Dose rate up set threshold > 3e9 rads/sec (Si)                      | 331    |

|                         | Dose rate Survivability > 1e11 rads/sec (Si)                        |        |

|                         | SEL > 110 Mev (T=125C)                                              |        |

| Jan.1, 2014             | Changed part number (remove CO35); removed watermark                | SST    |

| December 2015           | Update to VORAGO format                                             |        |

| April 6, 2016 (Rev 1.1) | Added Radiation spec. Table 13                                      | VORAGO |

|                         | Added Part Ordering Information Table 14                            | VORAGO |

The use of this product is subject to the manufacturer's standard terms and conditions available on the manufacturer's website: https://www.voragotech.com/sites/default/files/Vorago%20Standard%20Terms%20and%20Conditions%20of%20Sale%204\_18\_2016.pdf

VORAGO Technologies 1501 S MoPac Expressway, Suite #350 Austin, Texas 78746 Email: info@voragotech.com Phone: (512) 347-1800

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for SRAM category:

Click to view products by Vorago manufacturer:

Other Similar products are found below :

CY6116A-35DMB CY7C1049GN-10VXI GS8161Z36DD-200I GS88237CB-200I RMLV0408EGSB-4S2#AA0 IDT70V5388S166BG IS64WV3216BLL-15CTLA3 IS66WVE4M16ECLL-70BLI PCF8570P K6F2008V2E-LF70000 K6T4008C1B-GB70 CY7C1353S-100AXC AS6C8016-55BIN AS7C164A-15PCN 515712X IDT71V67603S133BG IS62WV51216EBLL-45BLI IS63WV1288DBLL-10HLI IS66WVE2M16ECLL-70BLI IS66WVE4M16EALL-70BLI IS61WV102416DBLL-10TLI CY7C1381KV33-100AXC CY7C1381KVE33-133AXI 8602501XA 5962-3829425MUA 5962-3829430MUA 5962-8866201YA 5962-8866204TA 5962-9062007MXA 5962-9161705MXA GS882Z18CD-150I 8413202RA 5962-8866208YA 5962-8866203YA IS61WV102416DBLL-10BLI IS66WVC2M16ECLL-7010BLI CY7C1380KV33-250AXC AS6C8016-55BINTR GS81284Z18B-250I AS7C34096B-10TIN GS84018CB-200I IS62WV25616EALL-55TLI IS61WV204816BLL-10TLI GS8128418B-167IV CY7C1460KV25-200BZXI CY7C1315KV18-333BZXC CY62157G30-45ZSXI 71V016SA12YG RMLV0416EGBG-4S2#AC0 CY62126EV18LL-70BVXI