# W7100A Datasheet

Version 1.2.5

© 2013~2014 WIZnet Co.,Ltd. All Rights Reserved. For more information, visit our website at <u>http://www.wiznet.co.kr</u>.

W7100A Datasheet v1.2.5

## **Table of Contents**

| 1 |     | Overv | /iew11                                      |

|---|-----|-------|---------------------------------------------|

|   | 1.1 | Intro | duction 11                                  |

|   | 1.2 | W710  | 0A Features 11                              |

|   | 1.3 | W710  | 0A Block Diagram & Features12               |

|   |     | 1.3.1 | ALU (Arithmetic Logic Unit) 12              |

|   |     | 1.3.2 | TCPIPCore 14                                |

|   | 1.4 | Pin D | escription                                  |

|   |     | 1.4.1 | Pin Layout                                  |

|   |     | 1.4.2 | Pin Description                             |

|   |     | 1.4.2 | 2.1 Configuration                           |

|   |     | 1.4.2 | 2.2 Timer                                   |

|   |     | 1.4.2 | 2.3 UART                                    |

|   |     | 1.4.2 | 2.4 DoCD <sup>™</sup> Compatible Debugger19 |

|   |     | 1.4.2 | 2.5 Interrupt / Clock 19                    |

|   |     | 1.4.2 | 2.6 GPIO 20                                 |

|   |     | 1.4.2 | 2.7 Media Interface                         |

|   |     | 1.4.2 | 2.8         Network Indicator LED           |

|   |     | 1.4.2 |                                             |

|   | 1.5 | 64pir | package description                         |

|   |     | 1.5.1 | Difference between 100 and 64pin package24  |

| 2 |     | Memo  | ory                                         |

|   | 2.1 | Code  | Memory                                      |

|   |     | 2.1.1 | Code Memory Wait States                     |

|   | 2.2 | Data  | Memory                                      |

|   |     | 2.2.1 | Data Memory Wait States                     |

|   | 2.3 | Exter | nal Data Memory Access 30                   |

|   |     | 2.3.1 | Standard 8051 Interface 30                  |

|   |     | 2.3.2 | Direct Interface                            |

|   | 2.4 | Inter | nal Data Memory and SFR 33                  |

|   | 2.5 | SFR c | efinition                                   |

|   |     | 2.5.1 | Program Code Memory Write Enable Bit        |

|   |     | 2.5.2 | Program Code Memory Wait States Register    |

|   |     | 2.5.3 | Data Pointer Extended Registers             |

|   |     | 2.5.4 | Data Pointer Registers                      |

|   |     | 2.5.5 | Clock Control Register                      |

|   |     | 2.5.6  | Internal Memory Wait States Register                         |

|---|-----|--------|--------------------------------------------------------------|

|   |     | 2.5.7  | Address Latch Enable Register                                |

|   |     | 2.5.8  | External Memory Wait States Register                         |

|   |     | 2.5.9  | Stack Pointer                                                |

|   |     | 2.5.10 | New & Extended SFR 40                                        |

|   |     | 2.5.11 | Peripheral Registers                                         |

| 3 |     | Inter  | rupt 44                                                      |

| 4 |     | 1/O P  | orts                                                         |

| 5 |     | Time   | rs                                                           |

|   | 5.1 | Time   | rs 0, 1                                                      |

|   |     | 5.1.1  | Overview                                                     |

|   |     | 5.1.2  | Interrupts                                                   |

|   |     | 5.1.3  | Timer0 - Mode0 54                                            |

|   |     | 5.1.4  | Timer0 - Mode1 55                                            |

|   |     | 5.1.5  | Timer0 - Mode2 55                                            |

|   |     | 5.1.6  | Timer0 - Mode3                                               |

|   |     | 5.1.7  | Timer1 - Mode0                                               |

|   |     | 5.1.8  | Timer1 - Mode1                                               |

|   |     | 5.1.9  | Timer1 - Mode2                                               |

|   |     | 5.1.10 | Timer1 - Mode3                                               |

|   | 5.2 | Time   | r2                                                           |

|   |     | 5.2.1  | Overview                                                     |

|   |     | 5.2.2  | Interrupts                                                   |

| 6 |     | UART   |                                                              |

|   | 6.1 | Inter  | rupts                                                        |

|   | 6.2 | Mode   | 0, Synchronous                                               |

|   | 6.3 | Mode   | 1, 8-Bit UART, Variable Baud Rate, Timer 1 or 2 Clock Source |

|   | 6.4 | Mode   | 2, 9-Bit UART, Fixed Baud Rate66                             |

|   | 6.5 | Mode   | 3, 9-Bit UART, Variable Baud Rate, Timer1 or 2 Clock Source  |

|   | 6.6 | Exam   | ples of Baud Rate Setting                                    |

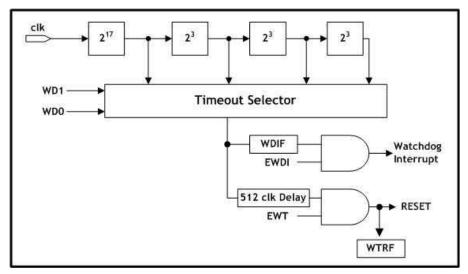

| 7 |     | Watc   | hdog Timer                                                   |

|   | 7.1 | Overv  | <i>v</i> iew                                                 |

|   | 7.2 | Inter  | rupts                                                        |

|   | 7.3 | Watc   | hdog Timer Reset                                             |

|   | 7.4 | Simp   | le Timer                                                     |

|   | 7.5 | Syste  | m Monitor                                                    |

|   | 7.6 | Watc   | hdog Related Registers                                       |

|   | 7.7 | Watc   | hdog Control                                                 |

|    | 7.   | 7.1    | Clock Control                                |

|----|------|--------|----------------------------------------------|

|    | 7.8  | Time   | d Access Registers                           |

| 8  |      | тсрі   | PCore                                        |

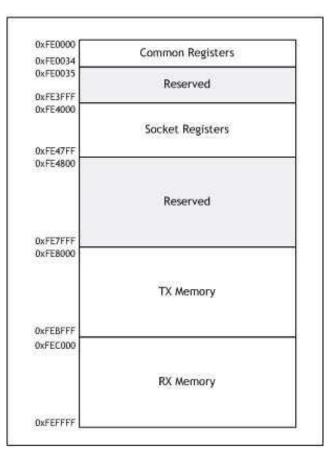

|    | 8.1  | Mem    | ory Map                                      |

|    | 8.2  | Regis  | ters list                                    |

|    | 8.   | 2.1    | Common Registers                             |

|    | 8.   | 2.2    | SOCKET Registers                             |

|    | 8.3  | Regis  | ter Description                              |

|    | 8.   | 3.1    | Mode Register                                |

|    | 8.   | 3.2    | SOCKET Registers                             |

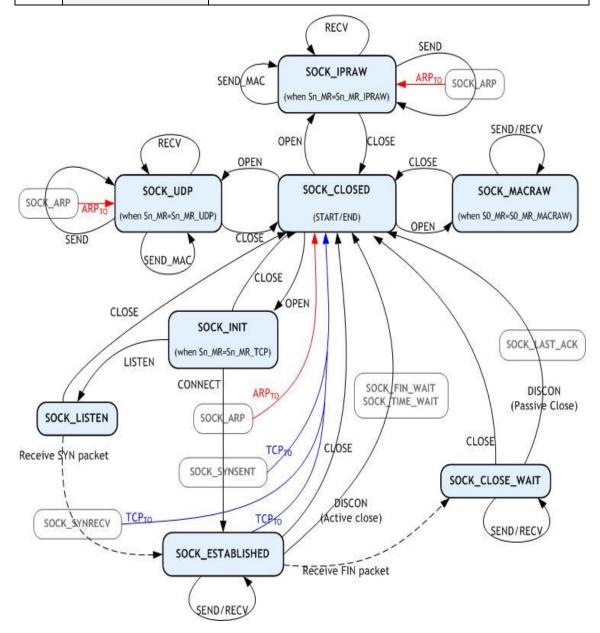

| 9  |      | Func   | tional Description110                        |

|    | 9.1  | Initia | lization110                                  |

|    | 9.2  | Data   | Communication115                             |

|    | 9.   | 2.1    | TCP115                                       |

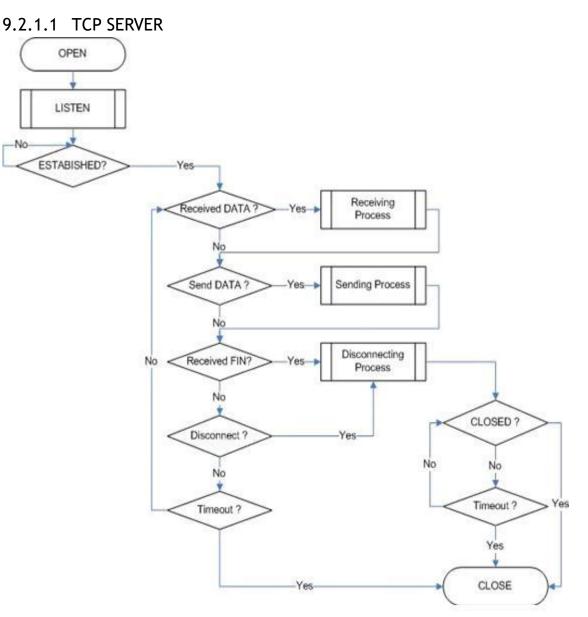

|    |      | 9.2.   | 1.1 TCP SERVER116                            |

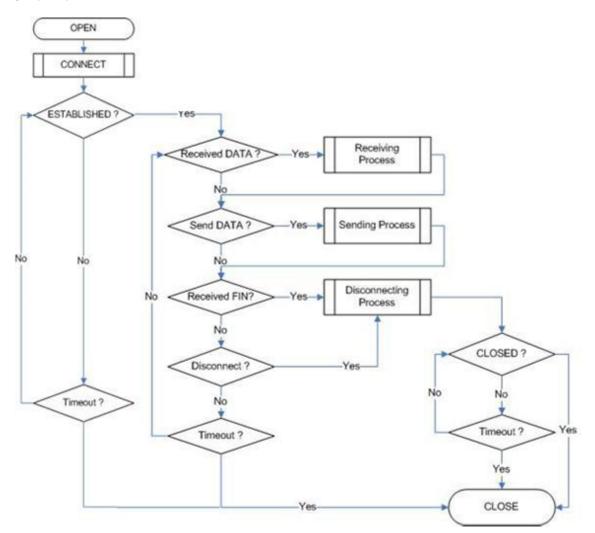

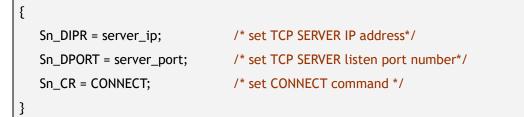

|    |      | 9.2.   | 1.2 TCP CLIENT                               |

|    | 9.   | 2.2    | UDP                                          |

|    |      | 9.2.   | 2.1 Unicast & Broadcast124                   |

|    |      | 9.2.   | 2.2 Multicast                                |

|    | 9.   | 2.3    | IPRAW                                        |

|    | 9.   | 2.4    | MACRAW134                                    |

| 10 |      | Elect  | rical Specification141                       |

|    | 10.1 | Abso   | lute Maximum Ratings141                      |

|    | 10.2 | DC C   | haracteristics                               |

|    | 10.3 | Powe   | er consumption(Driving voltage 3.3V)142      |

|    | 10.4 | AC C   | haracteristics                               |

|    | 10.5 | Cryst  | al Characteristics                           |

|    | 10.6 | Trans  | former Characteristics143                    |

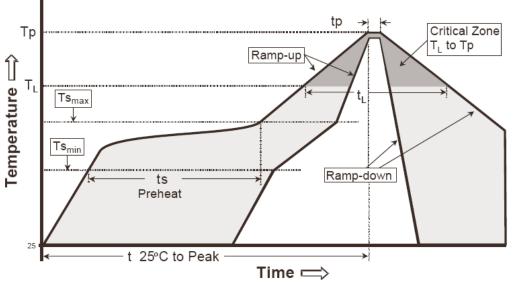

| 11 |      | IR Re  | flow Temperature Profile (Lead-Free)144      |

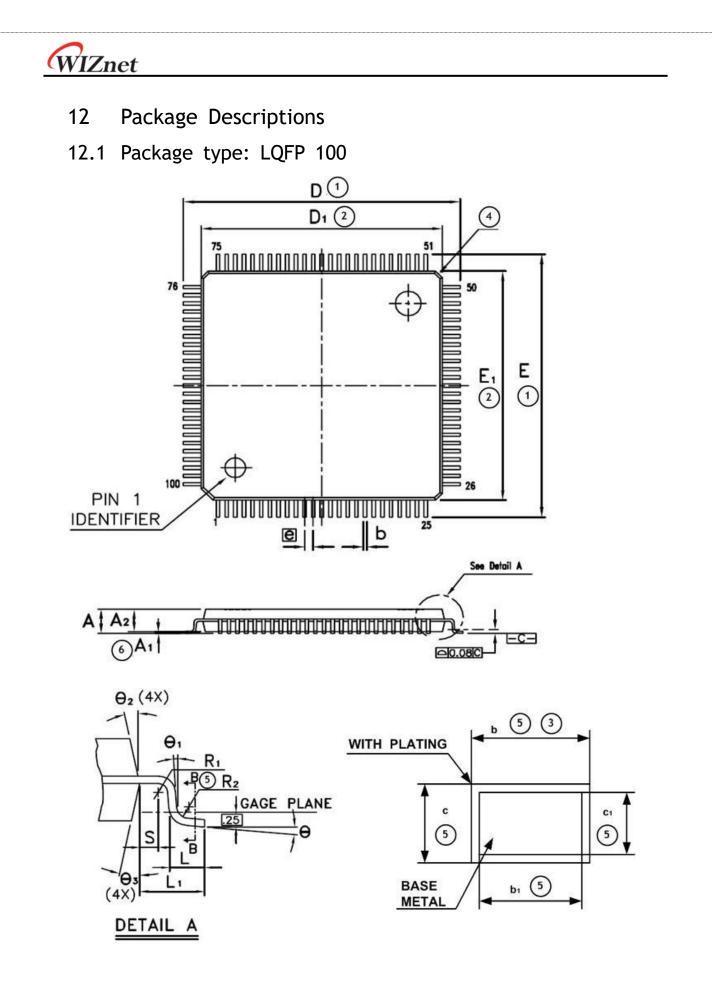

| 12 |      | Pack   | age Descriptions                             |

|    | 12.1 | Pack   | age type: LQFP 100145                        |

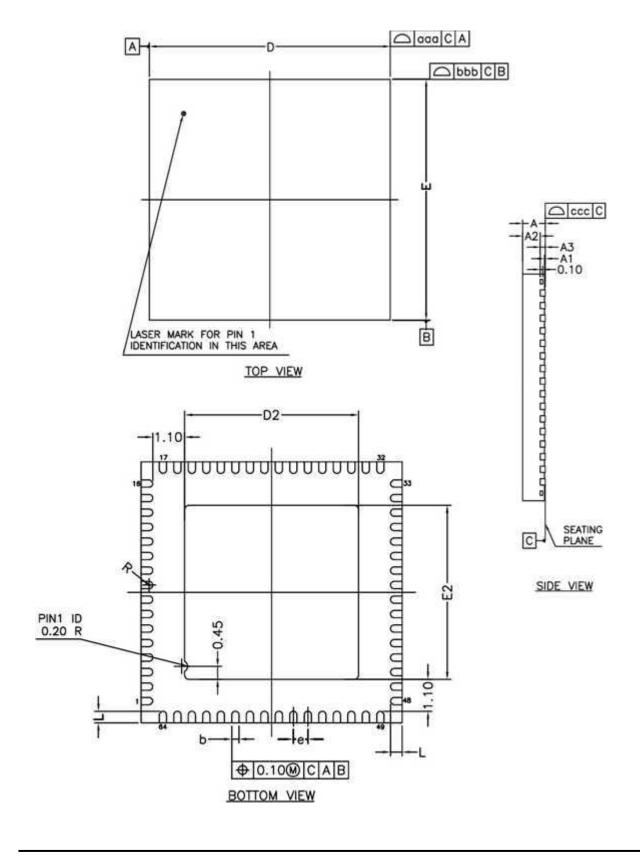

|    | 12.2 | Pack   | age type: QFN 64147                          |

| 13 |      | Арре   | ndix:Performance Improvement about W7100A149 |

|    | 13.1 | Sumr   | nary149                                      |

|    | 13.2 | 8-Bit  | Arithmetic Functions149                      |

|    | 13   | .2.1   | Addition                                     |

|    | 13   | .2.2   | Subtraction151                               |

|    |      | .2.3   | Multiplication                               |

| 13   | .2.4  | Division               | 152 |

|------|-------|------------------------|-----|

| 13.3 | 16-Bi | t Arithmetic Functions | 152 |

| 13   | .3.1  | Addition               | 152 |

| 13   | .3.2  | Subtraction            | 153 |

| 13   | .3.3  | Multiplication         | 153 |

| 13.4 | 32-bi | t Arithmetic Functions | 154 |

| 13   | .4.1  | Addition               | 154 |

| 13   | .4.2  | Subtraction            | 155 |

| 13   | .4.3  | Multiplication         | 155 |

## List of Figures

| Figure 1.1 W7100A Block Diagram 12                                                   |

|--------------------------------------------------------------------------------------|

| Figure 1.2 Accumulator A Register                                                    |

| Figure 1.3 B Register                                                                |

| Figure 1.4 Program Status Word Register                                              |

| Figure 1.5 PSW Register                                                              |

| Figure 1.6 TCPIPCore Block Diagram14                                                 |

| Figure 1.7 W7100A Pin Layout 16                                                      |

| Figure 1.8 W7100A QFN 64 Pin Layout 17                                               |

| Figure 1.9 Power Design 24                                                           |

| Figure 2.1 Code / Data Memory Connections                                            |

| (Example ICs : MAX811, MIC811, DS1811)26                                             |

| Figure 2.2. Boot Sequence Flowchart                                                  |

| Figure 2.3 APP Entry Process                                                         |

| Figure 2.4 Changing the code memory Status at <b>RB</b> = '0'                        |

| Figure 2.5 Data Memory Map29                                                         |

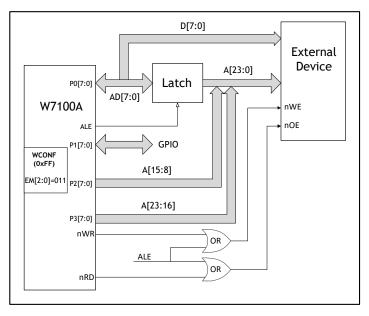

| Figure 2.6 Standard 8051 External Pin Access Mode (EM[2:0] = "001")31                |

| Figure 2.7 Standard 8051 External Pin Access Mode (EM[2:0] = "011")31                |

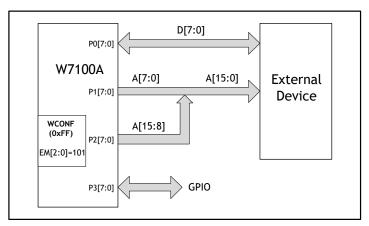

| Figure 2.8 Direct 8051 External Pin Access Mode (EM[2:0] = "101")32                  |

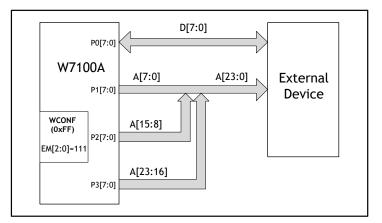

| Figure 2.9 Direct 8051 External Pin Access Mode (EM[2:0] = "111")32                  |

| Figure 2.10 Internal Memory Map                                                      |

| Figure 2.11 SFR Memory Map 33                                                        |

| Figure 2.12 PWE bit of PCON Register                                                 |

| Figure 2.13 Code memory Wait States Register                                         |

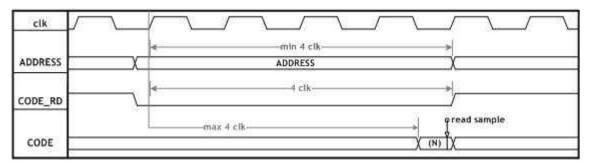

| Figure 2.14 Waveform for code memory Synchronous Read Cycle with Minimal Wait States |

| (WTST = '4')                                                                         |

| Figure 2.15 Waveform for code memory Synchronous Write Cycle with Minimal Wait       |

| States(WTST = '4')                                                                   |

| Figure 2.16 Data Pointer Extended Register                                           |

| Figure 2.17 Data Pointer Extended Register                                           |

| Figure 2.18 MOVX @RI Extended Register                                               |

| Figure 2.19 Data Pointer Register DPTR0                                              |

| Figure 2.20 Data Pointer 1 Register DPTR1                                            |

| Figure 2.21 Data Pointer Select Register                                             |

| Figure 2.22 Clock Control Register - STRETCH bits                                    |

| Figure 2.23 Internal Memory Wait States Register                                     |

| Figure 2.24 Internal Memory Wait States Register                                     |

| Figure 2.25 First Byte of Internal Memory Wait States Register  |

|-----------------------------------------------------------------|

| Figure 2.26 Second Byte of Internal Memory Wait States Register |

| Figure 2.27 Stack Pointer Register                              |

| Figure 2.28 PHY Status Register 40                              |

| Figure 2.29 Internal PHY Configuration Register                 |

| Figure 2.30 W7100A Configuration Register                       |

| Figure 2.31 Core clock count register 42                        |

| Figure 2.32 Core clock count register 42                        |

| Figure 2.33 Core clock count register 42                        |

| Figure 2.34 Core clock count register                           |

| Figure 3.1 Interrupt Enable Register                            |

| Figure 3.2 Interrupt Priority Register                          |

| Figure 3.3 Timer0, 1 Configuration Register                     |

| Figure 3.4 UART Configuration Register                          |

| Figure 3.5 Extended Interrupt Enable Register                   |

| Figure 3.6 Extended Interrupt Priority Register                 |

| Figure 3.7 Extended Interrupt Flag Register                     |

| Figure 3.8 Watchdog Control Register                            |

| Figure 4.1 Port0 Pull-down register                             |

| Figure 4.2 Port0 Register                                       |

| Figure 4.3 Port1 Register                                       |

| Figure 4.4 Port2 Register                                       |

| Figure 4.5 Port3 Register                                       |

| Figure 4.6 Port0 Pull-down register                             |

| Figure 4.7 Port1 Pull-down register                             |

| Figure 4.8 Port2 Pull-down register                             |

| Figure 4.9 Port3 Pull-down register                             |

| Figure 4.10 Port0 Pull-up register                              |

| Figure 4.11 Port1 Pull-up register                              |

| Figure 4.12 Port2 Pull-up register                              |

| Figure 4.13 Port3 Pull-up register                              |

| Figure 5.1 Timer0, 1 Control Mode Register                      |

| Figure 5.2 Timer0, 1 Configuration Register                     |

| Figure 5.3 Interrupt Enable Register                            |

| Figure 5.4 Interrupt Priority Register                          |

| Figure 5.5 Timer0, 1 Configuration Register                     |

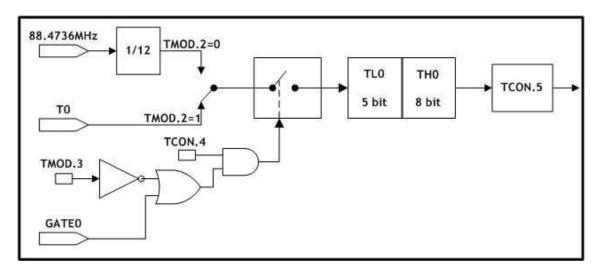

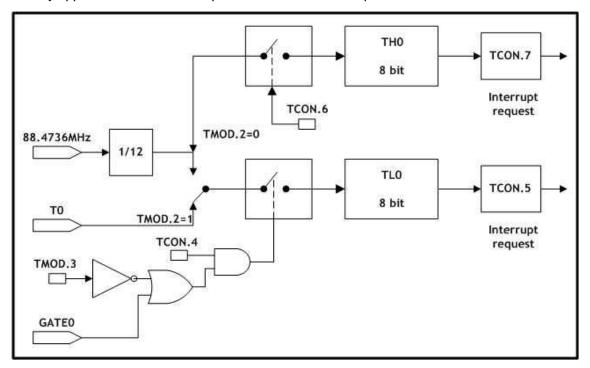

| Figure 5.6 Timer Counter0, Mode0: 13-Bit Timer/Counter55        |

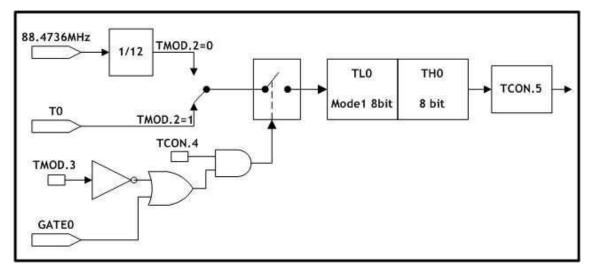

| Figure 5.7 Timer/Counter0, Mode1: 16-Bit Timer/Counter55        |

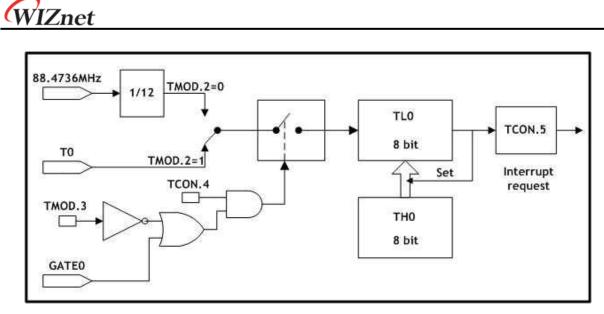

| Figure 5.8 Timer/Counter0, Mode2: 8-Bit Timer/Counter with Auto-Reload    |

|---------------------------------------------------------------------------|

| Figure 5.9 Timer/Counter0, Mode3: Two 8-Bit Timers/Counters               |

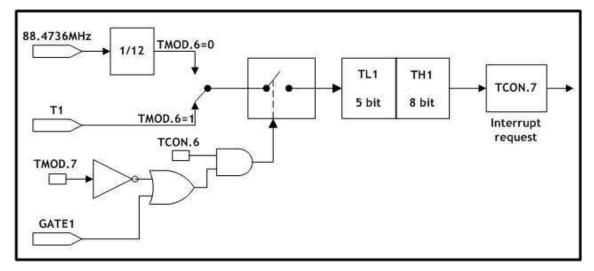

| Figure 5.10 Timer/Counter1, Mode0: 13-Bit Timer/Counter                   |

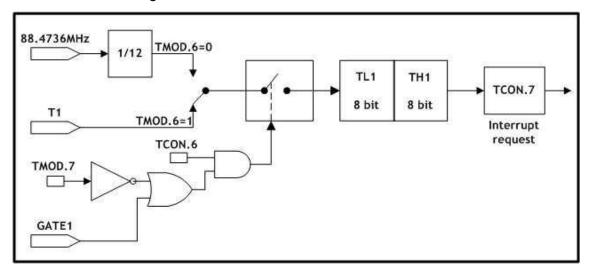

| Figure 5.11 Timer/Counter1, Mode1: 16-Bit Timers/Counters                 |

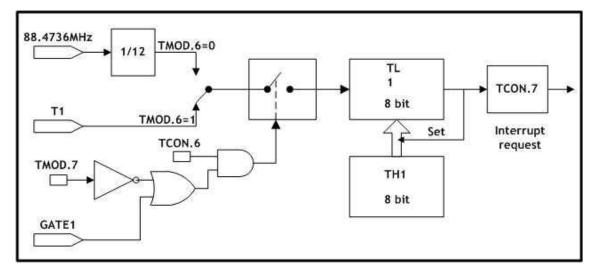

| Figure 5.12 Timer/Counter1, Mode2: 8-Bit Timer/Counter with Auto-Reload   |

| Figure 5.13 Timer2 Configuration Register 59                              |

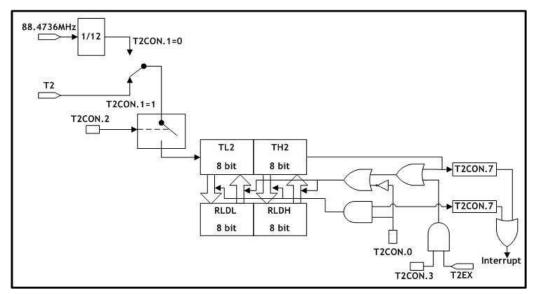

| Figure 5.14 Timer/Counter2, 16-Bit Timer/Counter with Auto-Reload         |

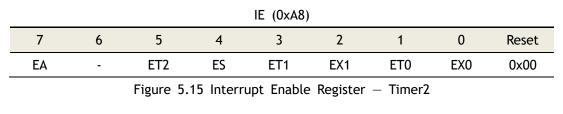

| Figure 5.15 Interrupt Enable Register — Timer2                            |

| Figure 5.16 Interrupt Priority Register – Timer2                          |

| Figure 5.17 Timer2 Configuration Register – TF2                           |

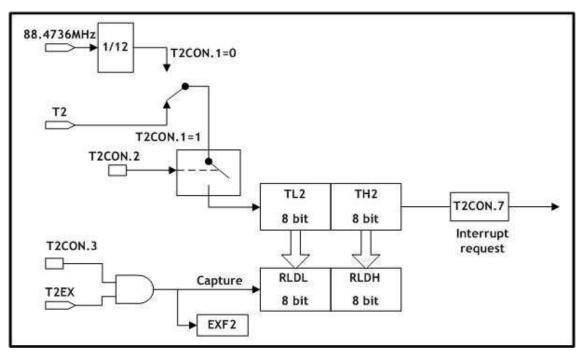

| Figure 5.18 Timer/Counter2, 16-Bit Timer/Counter with Capture Mode        |

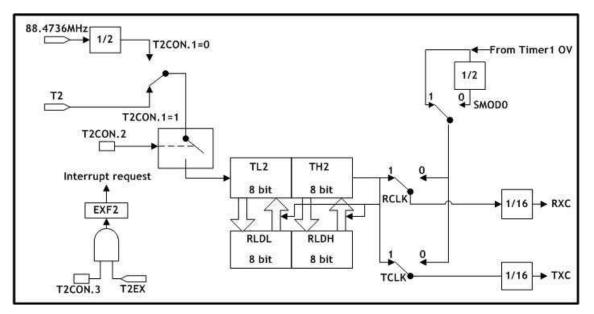

| Figure 5.19 Timer2 for Baud Rate Generator Mode                           |

| Figure 6.1 UART Buffer Register63                                         |

| Figure 6.2 UART Configuration Register63                                  |

| Figure 6.3 UART Bits in Power Configuration Register                      |

| Figure 6.4 UART Bits in Interrupt Enable Register65                       |

| Figure 6.5 UART Bits in Interrupt Priority Register                       |

| Figure 6.6 UART Configuration Register65                                  |

| Figure 6.7 Timing Diagram for UART Transmission Mode0 (clk = 88.4736 MHz) |

| Figure 6.8 Timing Diagram for UART Transmission Mode1                     |

| Figure 6.9 Timing Diagram for UART Transmission Mode2                     |

| Figure 6.10 Timing Diagram for UART Transmission Mode3                    |

| Figure 7.1 Watchdog Timer Structure                                       |

| Figure 7.2 Interrupt Enable Register                                      |

| Figure 7.3 Extended Interrupt Enable Register                             |

| Figure 7.4 Extended interrupt Priority Register                           |

| Figure 7.5 Watchdog Control Register                                      |

| Figure 7.6 Watchdog Control Register71                                    |

| Figure 7.7 Clock Control register - Watchdog bits                         |

| Figure 8.1 TCPIPCore Memory Map73                                         |

| Figure 8.2 SOCKET <i>n</i> Status transition100                           |

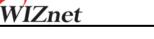

| Figure 8.3 Calculate Physical Address107                                  |

| Figure 9.1 Allocation Internal TX/RX memory of SOCKET <i>n</i> 114        |

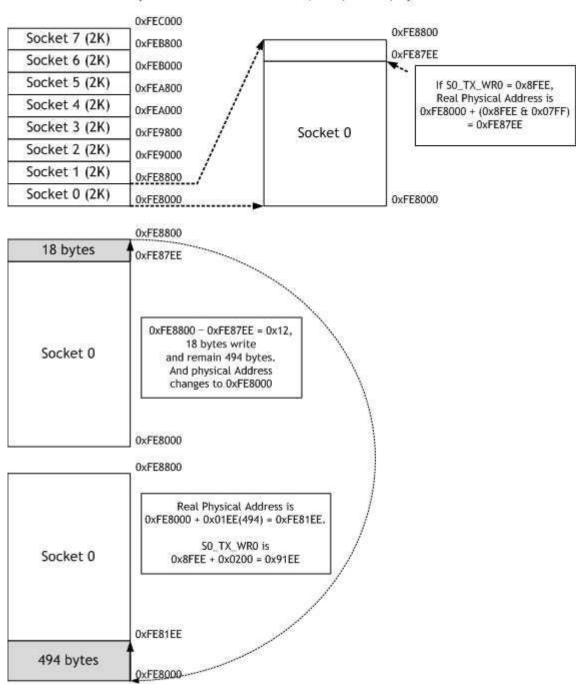

| Figure 9.2 TCP SERVER & TCP CLIENT115                                     |

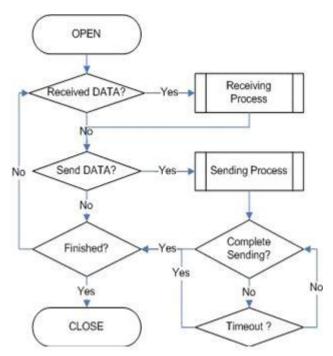

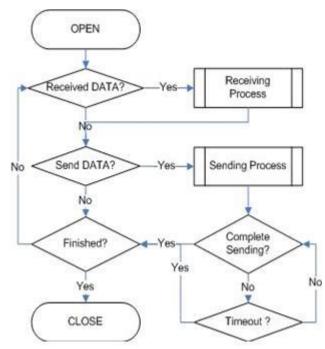

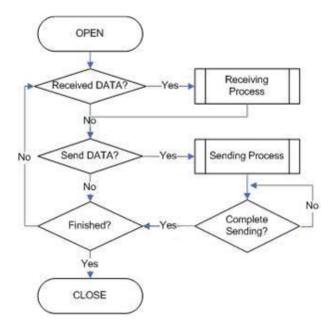

| Figure 9.3 "TCP SERVER" Operation Flow116                                 |

| Figure 9.4 "TCP CLIENT" Operation Flow123                                 |

| Figure 9.5 UDP Operation Flow124                                          |

| Figure 9.6 The received UDP data format126                                |

WIZnet

| Figure 9.7 IPRAW Operation Flow             | 133 |

|---------------------------------------------|-----|

| Figure 9.8 The received IPRAW data format   | 134 |

| Figure 9.9 MACRAW Operation Flow            | 135 |

| Figure 9.10 The received MACRAW data format | 136 |

## List of Tables

.....

| Table 2.1 External memory access mode    30         |

|-----------------------------------------------------|

| Table 2.2 WTST Register Values    34                |

| Table 2.3 DPTR0, DPTR1 Operations                   |

| Table 2.4 MD[2:0] Bit Values                        |

| Table 2.5 Ram WTST Bit Values                       |

| Table 2.6 TCPIPCore / Flash WTST Bit Values         |

| Table 3.1 External Interrupt Pin Description    44  |

| Table 3.2 W7100A Interrupt Summary                  |

| Table 4.1 I/O Ports Pin Description                 |

| Table 4.2 Read-Modify-Write Instructions         49 |

| Table 5.1 Timers 0, 1 Pin Description52             |

| Table 5.2 Timers 0, 1 Mode         52               |

| Table 5.3 Timer0, 1 interrupts                      |

| Table 5.4 Timer2 Pin Description    59              |

| Table 5.5 Timer2 Modes                              |

| Table 5.6 Timer2 Interrupt    62                    |

| Table 6.1 UART Pin Description    63                |

| Table 6.2 UART Modes                                |

| Table 6.3 UART Baud Rates 64                        |

| Table 6.4 UART Interrupt                            |

| Table 6.5 Examples of Baud Rate Setting             |

| Table 7.1 Watchdog Interrupt69                      |

| Table 7.2 Summary for Watchdog Related Bits    70   |

| Table 7.3 Watchdog Bits and Actions71               |

| Table 7.4 Watchdog Intervals    72                  |

| Table 7.5 Timed Access Registers    72              |

| Table 9.1 Timer / Counter Mode                      |

| Table 9.2 Baud rate111                              |

| Table 9.3 Mode of UART111                           |

## 1 Overview

## 1.1 Introduction

iMCU W7100A is the one-chip solution which integrates an 8051 compatible microcontroller, 64KB SRAM and hardwired TCP/IP Core for high performance and easy development.

The TCP/IP core is a market-proven hardwired TCP/IP stack with an integrated Ethernet MAC & PHY. The Hardwired TCP/IP stack supports the TCP, UDP, IPv4, ICMP, ARP, IGMP and PPPoE which has been used in various applications for years.

## 1.2 W7100A Features

- Fully software compatible with industrial standard 8051

- Pipelined architecture which enables execution of instructions 4~5 times faster than a standard 8051

- 10BaseT/100BaseTX Ethernet PHY embedded

- Power down mode supported for saving power consumption

- Hardwired TCP/IP Protocols: TCP, UDP, ICMP, IPv4 ARP, IGMP, PPPoE, Ethernet

- Auto Negotiation (Full-duplex and half duplex), Auto MDI/MDIX

- ADSL connection with PPPoE Protocol with PAP/CHAP Authentication mode support

- · 8 independent sockets which are running simultaneously

- 32Kbytes Data buffer for the Network

- Network status LED outputs (TX, RX, Full/Half duplex, Collision, Link, and Speed)

- Not supports IP fragmentation

- · 2 Data Pointers (DPTRs) for fast memory blocks processing

- Advanced INC & DEC modes

- Auto-switch of current DPTR

- 64KBytes Data Memory (RAM)

- 255Bytes data FLASH, 64KBytes Code Memory, 2KBytes Boot Code Memory

- Up to 16M bytes of external (off-chip) data memory

- Interrupt controller

- 2 priority levels

- 4 external interrupt sources

- 1 Watchdog interrupt

- Four 8-bit I/O Ports

- Three timers/counters

- Full-duplex UART

- Programmable Watchdog Timer

- DoCD<sup>™</sup> compatible debugger

- High Product Endurance

- Minimum 100,000 program/erase cycles

- Minimum 10 years data retention

### 1.3 W7100A Block Diagram & Features

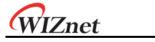

Figure 1.1 W7100A Block Diagram

The W7100A internal block diagram is shown in the Figure 1.1. Details of block functions are described as follows:

**ALU** - Performs arithmetic and logic operations during execution of an instruction. It contains accumulator (ACC), Program Status Word (PSW), B registers, and related logics such as arithmetic unit, logic unit, multiplier, and divider.

**SFR** - Controls the access of special registers. It contains standard and user defined registers and related logic. User defined external devices can be quickly accessed (read, write, modified) using all direct addressing mode instructions.

#### 1.3.1 ALU (Arithmetic Logic Unit)

W7100A is fully compatible with the standard 8051 microcontroller, and maintains all instruction mnemonics and binary compatibility. W7100A incorporates many great architectural enhancements which enable the W7100A MCU to execute instructions with high speed.

The ALU of W7100A MCU performs extensive data manipulation and is comprised of the 8-bit arithmetic logic unit (ALU), an ACC (0xE0) register, a B (0xF0) register and a PSW (0xD0) register

|                                   |       |       |       | ACC (0xEC | ))    |       |       |       |  |

|-----------------------------------|-------|-------|-------|-----------|-------|-------|-------|-------|--|

| 7                                 | 6     | 5     | 4     | 3         | 2     | 1     | 0     | Reset |  |

| ACC.7                             | ACC.6 | ACC.5 | ACC.4 | ACC.3     | ACC.2 | ACC.1 | ACC.0 | 0x00  |  |

| Figure 1.2 Accumulator A Register |       |       |       |           |       |       |       |       |  |

The B register is used during multiplication and division operations. In other cases, this register is used as normal SFR.

| B (0xF0)              |     |     |     |     |     |     |     |       |  |

|-----------------------|-----|-----|-----|-----|-----|-----|-----|-------|--|

| 7                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Reset |  |

| B.7                   | B.6 | B.5 | B.4 | B.3 | B.2 | B.1 | B.0 | 0x00  |  |

| Figure 1.3 B Register |     |     |     |     |     |     |     |       |  |

The ALU performs arithmetic operations such as addition, subtraction, multiplication, and division, and other operations such as increment, decrement, BCD-decimal-add-adjust, and compare. Logic unit uses AND, OR, Exclusive OR, complement, and rotation to perform different operations. The Boolean processor performs bit operations such as set, clear, complement, jump-if-not-set, jump-if-set-and-clear, and move to/from carry.

|    |    |    |     | PSW (0xD0 | )) |    |   |       |

|----|----|----|-----|-----------|----|----|---|-------|

| 7  | 6  | 5  | 4   | 3         | 2  | 1  | 0 | Reset |

| CY | AC | F0 | RS1 | RS0       | OV | F1 | Р | 0x00  |

| CY      | Carry flag                           |  |  |  |  |  |

|---------|--------------------------------------|--|--|--|--|--|

| AC      | Auxiliary carry                      |  |  |  |  |  |

| F0      | General purpose flag 0               |  |  |  |  |  |

|         | Register bank select bits            |  |  |  |  |  |

|         | RS[1:0] Function Description         |  |  |  |  |  |

| DC[1.0] | 00 -Bank 0, data address 0x00 - 0x07 |  |  |  |  |  |

| RS[1:0] | 01 -Bank 1, data address 0x08 - 0x0F |  |  |  |  |  |

|         | 10 -Bank 2, data address 0x10 - 0x17 |  |  |  |  |  |

|         | 11 -Bank 3, data address 0x18 - 0x1F |  |  |  |  |  |

| OV      | Overflow flag                        |  |  |  |  |  |

| F1      | General purpose flag 1               |  |  |  |  |  |

| Р       | Parity flag                          |  |  |  |  |  |

Figure 1.5 PSW Register

The PSW register contains several bits that can reflect the current state of MCU.

WIZnet

### 1.3.2 TCPIPCore

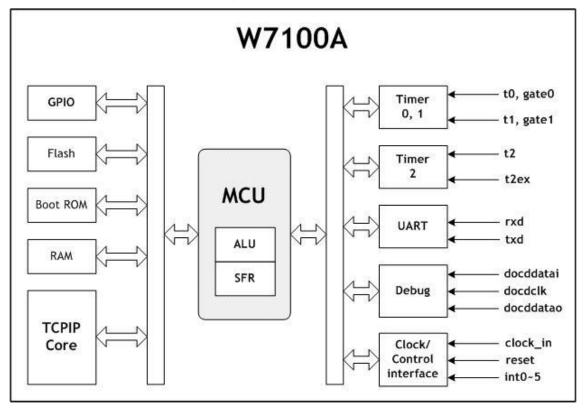

Figure 1.6 TCPIPCore Block Diagram

#### **Ethernet PHY**

The W7100A includes 10BaseT/100BaseTX Ethernet PHY. It supports half-duplex/full-duplex, auto-negotiation and auto-MDI/MDIX. It also supports 6 network indicator LED outputs such as Link, TX, RX status, Collision, speed and duplex.

#### **TCPIP Engine**

TCPIP Engine is a hardwired logic based network protocol which contains technology of WIZnet.

#### - 802.3 Ethernet MAC(Media Access Control)

This controls Ethernet access of CSMA/CD( $\underline{C}$ arrier  $\underline{S}$ ense  $\underline{M}$ ultiple  $\underline{A}$ ccess with  $\underline{C}$ ollision  $\underline{D}$ etect). The protocol is based on a 48-bit source/destination MAC address.

#### PPPoE(Point-To-Point Protocol over Ethernet)

This protocol uses PPP service over Ethernet. The payload (PPP frame) is encapsulated inside an Ethernet frame during a transmission. When receiving, it de-capsulates the PPP frame. PPPoE supports PPP communication with PPPoE server and PAP/CHAP authentications.

#### ARP(Address Resolution Protocol)

ARP is the MAC address resolution protocol by using IP address. This protocol exchanges ARP-reply and ARP-request from peers to determine the MAC address of each other

#### - IP (Internet Protocol)

This protocol operates in the IP layer and provides data communication. IP fragmentation is not supported. It is not possible to receive the fragmented packets. All protocol number is supported except for TCP or UDP. In case of TCP or UDP, use the hardwired embedded TCPIP stack.

#### - ICMP(Internet Control Message Protocol)

ICMP is a protocol which provides information, unreachable destination. When a Pingrequest ICMP packet is received, a Ping-reply ICMP packet is sent.

#### - IGMPv1/v2(Internet Group Management Protocol version 1/2)

This protocol processes IGMP messages such as the IGMP Join/Leave. The IGMP is only enabled in UDP multicast mode. Only version 1 and 2 of IGMP logic is supported. When using a newer version of IGMP, IGMP should be manually implemented in the IP layer.

#### - UDP(User Datagram Protocol)

It is a protocol which supports data communication at the UDP layer. User datagram such as unicast, multicast, and broadcast are supported

#### - TCP(Transmission Control Protocol)

This protocol operates in the TCP layer and provides data communication. Both TCP server and client modes are supported.

## 1.4 Pin Description

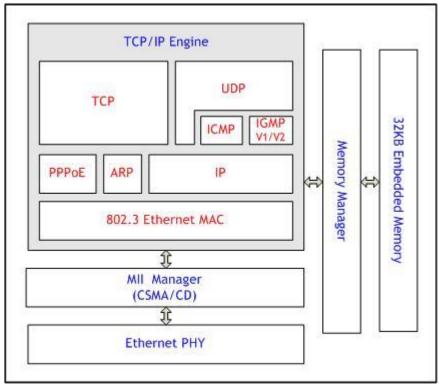

1.4.1 Pin Layout

Package type: LQFP 100

Figure 1.7 W7100A Pin Layout

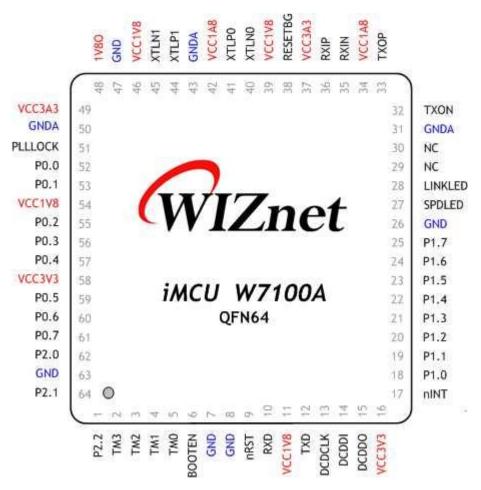

#### Package type: QFN 64

Figure 1.8 W7100A QFN 64 Pin Layout

### 1.4.2 Pin Description

The pin functionalities are described in the following table. There are no tri-state output pins and internal signals.

| Туре | Description                                     |

|------|-------------------------------------------------|

| I    | Input                                           |

| 0    | Output with 8mA driving current                 |

| 10   | Input/Output (Bidirectional)                    |

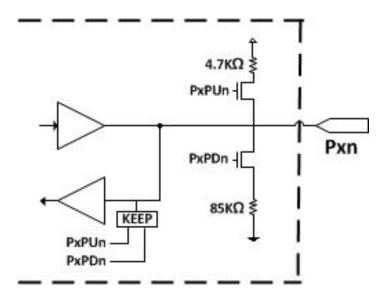

| Pu   | Internal pulled-up with 4.7K $\Omega$ resistor  |

| Pd   | Internal pulled-down with $85 K\Omega$ resistor |

## 1.4.2.1 Configuration

| Pin name | Pin nu | mber  | 1/0 | Pu/Pd | Desc  | cript | ion   |                                        |

|----------|--------|-------|-----|-------|-------|-------|-------|----------------------------------------|

|          | 100pin | 64pin |     |       |       |       |       |                                        |

| nRST     | 8      | 9     | Ι   | Pu    | Glob  | oal a | syn   | chronous reset, Active low             |

| TM3-0    | 1,2,   | 2,3,  | Ι   | Pd    | Must  | t be  | con   | nected to GND; value '0000'            |

|          | 3,4    | 4,5   |     |       |       |       |       |                                        |

| PM2 - 0  | 70,    | -     | I   | Pd    | PHY   | Мос   | le    |                                        |

|          | 71,    |       |     |       |       | ΡM    |       |                                        |

|          | 72     |       |     |       | 2     | 1     | 0     | Description                            |

|          |        |       |     |       |       |       |       |                                        |

|          |        |       |     |       |       |       |       | Normal Operation Mode                  |

|          |        |       |     |       | 0     | 0     | 0     | Auto-negotiation enabled with all      |

|          |        |       |     |       |       |       |       | functionalities                        |

|          |        |       |     |       | 0     | 0     | 1     | Auto-negotiation with 100 BASE-TX      |

|          |        |       |     |       |       |       |       | FDX/HDX ability                        |

|          |        |       |     |       | 0     | 1     | 0     | Auto-negotiation with 10 BASE-T        |

|          |        |       |     |       |       |       |       | FDX/HDX ability                        |

|          |        |       |     |       | 0     | 1     | 1     | Reserved                               |

|          |        |       |     |       | 1     | 0     | 0     | Manual selection of 100 BASE-TX FDX    |

|          |        |       |     |       | 1     | 0     | 1     | Manual selection of 100 BASE-TX HDX    |

|          |        |       |     |       | 1     | 1     | 0     | Manual selection of 10 BASE-T FDX      |

|          |        |       |     |       | 1     | 1     | 1     | Manual selection of 10 BASE-T HDX      |

|          |        |       |     |       | FDX   | : Fu  | Ill-D | ouplex, HDX : Half-Duplex              |

| BOOTEN   | 5      | 6     | Ι   | Pd    | Boot  | t Ena | able  | e/Disable                              |

|          |        |       |     |       | 0 - E | Enab  | le l  | Jser Application mode                  |

|          |        |       |     |       | Ju    | mp    | to C  | 0x0000, the start address of user Code |

|          |        |       |     |       | FLAS  |       |       |                                        |

|          |        |       |     |       |       |       |       | oot mode                               |

|          |        |       |     |       |       |       |       | ode in Boot ROM                        |

| PLOCK    | 77     | 51    | 0   | -     |       |       | k l   | ine, It notifies when internal PLL is  |

|          |        |       |     |       | lock  | ed    |       |                                        |

## 1.4.2.2 Timer

| Pin name    | Pin number |       | 1/0 | Pu/Pd | Description                   |

|-------------|------------|-------|-----|-------|-------------------------------|

|             | 100pin     | 64pin |     |       |                               |

| Timer0, 1   | Interface  |       |     |       |                               |

| Т0          | 9          | -     | Ι   | Pu    | Timer0 external clock input   |

| T1          | 10         | -     | Ι   | Pu    | Timer1 external clock input   |

| GATE0       | 11         | -     | Ι   | Pd    | Timer0 gate control           |

| GATE1       | 12         | -     | I   | Pd    | Timer1 gate control           |

| Timer2 Inte | erface     |       |     |       |                               |

| Т2          | 13         | -     | Ι   | Pu    | Timer2 external clock input   |

| T2EX        | 14         | -     | Ι   | Pu    | Timer2 Capture/Reload trigger |

### 1.4.2.3 UART

| Pin name | Pin nu | mber  | I/0 | Pu/Pd | Description        |

|----------|--------|-------|-----|-------|--------------------|

|          | 100pin | 64pin |     |       |                    |

| RXD      | 15     | 10    | Ι   | -     | Serial receiver    |

| TXD      | 17     | 12    | 0   | •     | Serial transmitter |

## 1.4.2.4 DoCD<sup>™</sup> Compatible Debugger

| Pin name | Pin nu | mber  | I/0 | Pu/Pd | Description      |

|----------|--------|-------|-----|-------|------------------|

|          | 100pin | 64pin |     |       |                  |

| DCDCLK   | 18     | 13    | 0   | -     | DoCD clock       |

| DCDDI    | 19     | 14    | I   | Pu    | DoCD data input  |

| DCDDO    | 20     | 15    | 0   |       | DoCD data output |

## 1.4.2.5 Interrupt / Clock

| Pin name | Pin nu | Imber | 1/0 | Pu/Pd | Description                                                                                                                                   |

|----------|--------|-------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|          | 100pin | 64pin |     |       |                                                                                                                                               |

| nINT0    | 22     | 17    | I   | -     | External interrupt0                                                                                                                           |

| nINT1    | 23     | -     | I   | Pu    | External interrupt1                                                                                                                           |

| nINT2    | 24     | -     | I   | Pu    | External interrupt2                                                                                                                           |

| nINT3    | 25     | -     | I   | Pu    | External interrupt3                                                                                                                           |

| XTLN0    | 61     | 40    | 0   | -     | Crystal output for WIZnet Core, A parallel-<br>resonant 25MHz crystal or ceramic is connected.<br>If use oscillator, this pin can be floated. |

| XTLP0    | 62     | 41    | Ι   | -     | Crystal input for WIZnet Core, A parallel-                                                                                                    |

|       |    |    |   |   | resonant 25MHz crystal or ceramic is connected.<br>If use oscillator, this pin connected with 1.8V<br>output of OSC.                                                       |

|-------|----|----|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTLN1 | 67 | 45 | 0 | - | Crystal output for MCU core, A parallel-resonant<br>11.0592MHz crystal or ceramic is connected. If<br>oscillator is uesd, this pin can be floated.                         |

| XTLP1 | 66 | 44 | I | - | Crystal input for MCU core, A parallel-resonant<br>11.0592MHz crystal or ceramic is connected. If<br>oscillator is used, this pin is connected with 1.8V<br>output of OSC. |

#### 1.4.2.6 GPIO

| Pin name | Pin nu | mber  | 1/0 | Pu/Pd | Description                                 |

|----------|--------|-------|-----|-------|---------------------------------------------|

|          | 100pin | 64pin |     |       |                                             |

| P0.0     | 81     | 52    | 10  | -     | Port0 input/output, Ext Memory Data0, Addr0 |

| P0.1     | 82     | 53    | 10  | -     | Port0 input/output, Ext Memory Data1, Addr1 |

| P0.2     | 84     | 55    | 10  | -     | Port0 input/output, Ext Memory Data2, Addr2 |

| P0.3     | 85     | 56    | 10  | -     | Port0 input/output, Ext Memory Data3, Addr3 |

| P0.4     | 86     | 57    | 10  | -     | Port0 input/output, Ext Memory Data4, Addr4 |

| P0.5     | 88     | 59    | 10  | -     | Port0 input/output, Ext Memory Data5, Addr5 |

| P0.6     | 89     | 60    | 10  | -     | Port0 input/output, Ext Memory Data6, Addr6 |

| P0.7     | 90     | 61    | 10  | -     | Port0 input/output, Ext Memory Data7, Addr7 |

| P1.0     | 26     | 18    | 10  | -     | Port1 input/output, Ext Memory Addr0        |

| P1.1     | 27     | 19    | 10  | -     | Port1 input/output, Ext Memory Addr1        |

| P1.2     | 28     | 20    | 10  | -     | Port1 input/output, Ext Memory Addr2        |

| P1.3     | 29     | 21    | 10  | -     | Port1 input/output, Ext Memory Addr3        |

| P1.4     | 30     | 22    | 10  | -     | Port1 input/output, Ext Memory Addr4        |

| P1.5     | 31     | 23    | 10  | -     | Port1 input/output, Ext Memory Addr5        |

| P1.6     | 32     | 24    | 10  | -     | Port1 input/output, Ext Memory Addr6        |

| P1.7     | 33     | 25    | 10  | -     | Port1 input/output, Ext Memory Addr7        |

| P2.0     | 91     | 62    | 10  | -     | Port2 input/output, Ext Memory Addr8        |

| P2.1     | 93     | 64    | 10  | -     | Port2 input/output, Ext Memory Addr9        |

| P2.2     | 94     | 1     | 10  | -     | Port2 input/output, Ext Memory Addr10       |

| P2.3     | 95     | -     | 10  | -     | Port2 input/output, Ext Memory Addr11       |

| P2.4     | 96     | -     | 10  | -     | Port2 input/output, Ext Memory Addr12       |

| P2.5     | 97     | -     | 10  | -     | Port2 input/output, Ext Memory Addr13       |

| P2.6     | 98     | -     | 10  | -     | Port2 input/output, Ext Memory Addr14       |

W7100A Datasheet v1.2.5

| P2.7 | 99 | - | 10 | - | Port2 input/output, Ext Memory Addr15 |

|------|----|---|----|---|---------------------------------------|

| P3.0 | 34 | - | 10 | - | Port3 input/output, Ext Memory Addr16 |

| P3.1 | 35 | - | 10 | - | Port3 input/output, Ext Memory Addr17 |

| P3.2 | 37 | - | 10 | - | Port3 input/output, Ext Memory Addr18 |

| P3.3 | 39 | - | 10 | - | Port3 input/output, Ext Memory Addr19 |

| P3.4 | 40 | - | 10 | - | Port3 input/output, Ext Memory Addr20 |

| P3.5 | 41 | - | 10 | - | Port3 input/output, Ext Memory Addr21 |

| P3.6 | 42 | - | 10 | - | Port3 input/output, Ext Memory Addr22 |

| P3.7 | 43 | - | 10 | - | Port3 input/output, Ext Memory Addr23 |

Note: User can control the GPIO I/O driving voltage using PxPU/PxPD SFR.

Note: In that case, GPIO0-3 is used to transfer External memory address and data. Please refer to the '2.3 External Data Memory Access'

### 1.4.2.7 External Memory Interface

| Pin name | Num | I/O Type | Description                                |

|----------|-----|----------|--------------------------------------------|

| ALE      | 78  | 0        | Data memory address bus [7:0] latch enable |

| nWR      | 79  | OL       | External data memory write                 |

| nRD      | 80  | OL       | External data memory read                  |

Note: When user using External memory by standard 8051 interface, P0[7:0] can transfer Data[7:0] or Address[7:0] by ALE pin control.

| Pin name | Pin nu | mber  | 1/0 | Pu/Pd | Description                                                     |

|----------|--------|-------|-----|-------|-----------------------------------------------------------------|

|          | 100pin | 64pin |     |       |                                                                 |

| TXON     | 52     | 32    | 0   | -     | TXON/TXOP Signal Pair, The differential data is                 |

| ТХОР     | 53     | 33    | 0   | -     | transmitted to the media on the TXON/TXOP                       |

|          |        |       |     |       | signal pair                                                     |

| RXIN     | 55     | 35    | I   | -     | RXIN/RXIP Signal Pair, The differential data from               |

| RXIP     | 56     | 36    | I   | -     | the media is received on the RXIN/RXIP Signal                   |

|          |        |       |     |       | pair                                                            |

| RESETBG  | 59     | 38    | I   | -     | PHY Off-chip resistor, Connect a resistor of 12.3               |

|          |        |       |     |       | $\mathrm{k}\Omega\pm1\%$ to the ground. Refer to the "Reference |

|          |        |       |     |       | schematic"                                                      |

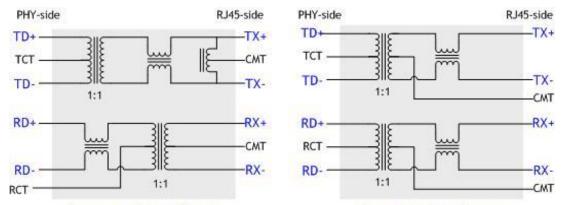

#### 1.4.2.8 Media Interface

For the best performance,

1. Make the length of RXIP / RXIN signal pair (RX) same if possible.

2. Make the length of TXOP / TXON signal pair (TX) same if possible.

3. Locate the RXIP and RXIN signal as near as possible.

- 4. Locate the TXOP and TXON signal as near as possible.

- 5. Locate the RX and TX signal pairs far from noisy signals such as bias resistor or crystal.

- 6. Keep regular between TX/RX signal pair.

For more details, refer to "W5100 Layout Guide.pdf."

| Pin name | Pin nu | mber  | 1/0 | Pu/Pd | Description                                |

|----------|--------|-------|-----|-------|--------------------------------------------|

|          | 100pin | 64pin |     |       |                                            |

| SPDLED   | 45     | 27    | 0   | -     | Link speed LED                             |

|          |        |       |     |       | Low: 100Mbps                               |

|          |        |       |     |       | High: 10Mbps                               |

| FDXLED   | 46     | -     | 0   | -     | Full duplex LED                            |

|          |        |       |     |       | Low: Full-duplex                           |

|          |        |       |     |       | High: Half-duplex                          |

| COLLED   | 47     | -     | 0   | -     | Collision LED                              |

|          |        |       |     |       | Low: Collision detected (only half-duplex) |

| RXLED    | 48     | -     | 0   | -     | Receive activity LED                       |

|          |        |       |     |       | Low: Receive signal detected on RXIP/RXIN  |

| TXLED    | 49     | -     | 0   | -     | Transmit activity LED                      |

|          |        |       |     |       | Low: Transmit signal detected on TXOP/TXON |

| LINKLED  | 50     | 28    | 0   | -     | Link LED                                   |

|          |        |       |     |       | Low: Link (10/100M) is detected            |

#### 1.4.2.9 Network Indicator LED

#### 1.4.2.10 Power Supply Signal

| Pin    | Pin nu | Imber  | I/0   | Pu/ | Description                                      |

|--------|--------|--------|-------|-----|--------------------------------------------------|

| name   | 100pin | 64pin  |       | Pd  |                                                  |

| VCC3A3 | 58, 75 | 37, 49 | Power | -   | Analog 3.3V power supply                         |

|        |        |        |       |     | Be sure to connect a 10uF tantalum capacitor     |

|        |        |        |       |     | between VCC3A3 and GNDA in order to prevent      |

|        |        |        |       |     | power compensation                               |

| VCC3V3 | 21,    | 16, 58 | Power | -   | Digital 3.3V power supply                        |

|        | 38,    |        |       |     | A 0.1uF decoupling capacitor should be connected |

|        | 73,    |        |       |     | between each pair of VCC and GND. A 1uH ferrite  |

|        | 87,    |        |       |     | bead should be used to separate the VCC3V3 and   |

|        | 100    |        |       |     | VCC3A3                                           |

| VCC1A8 | 54,    | 34, 42 | Power | -   | Analog 1.8V power supply                         |

W7100A Datasheet v1.2.5

|           |                                                                                                                               |                                                                                                                                                                             | A 10uF tantalum capacitor and a 0.1uF capacitor                                                                                                                                                                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                                                                                                               |                                                                                                                                                                             | should be connected between VCC1A8 and GNDA                                                                                                                                                                                                                                                           |

|           |                                                                                                                               |                                                                                                                                                                             | to filter out core power noise                                                                                                                                                                                                                                                                        |

| 39,       | Power                                                                                                                         | -                                                                                                                                                                           | Digital 1.8V power supply                                                                                                                                                                                                                                                                             |

| 46,       |                                                                                                                               |                                                                                                                                                                             | Between each pair of VCC and GND, a 0.1uF                                                                                                                                                                                                                                                             |

| 83 54, 11 |                                                                                                                               |                                                                                                                                                                             | decoupling capacitor should be connected                                                                                                                                                                                                                                                              |

| 31,       | Power                                                                                                                         | -                                                                                                                                                                           | Analog ground                                                                                                                                                                                                                                                                                         |

| 43, 50    |                                                                                                                               |                                                                                                                                                                             | Design the analog ground plane as wide as                                                                                                                                                                                                                                                             |

|           |                                                                                                                               |                                                                                                                                                                             | possible during PCB layout                                                                                                                                                                                                                                                                            |

|           |                                                                                                                               |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                       |

|           |                                                                                                                               |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                       |

| 7, 7, 8,  | Power                                                                                                                         | -                                                                                                                                                                           | Digital ground                                                                                                                                                                                                                                                                                        |

| , 26,     |                                                                                                                               |                                                                                                                                                                             | Design the digital ground plane as wide as                                                                                                                                                                                                                                                            |

| 92 47, 63 |                                                                                                                               |                                                                                                                                                                             | possible during PCB layout                                                                                                                                                                                                                                                                            |

| 48        | Power                                                                                                                         | -                                                                                                                                                                           | 1.8V regulated output voltage                                                                                                                                                                                                                                                                         |

|           |                                                                                                                               |                                                                                                                                                                             | 1.8V/150mA power generated by internal power                                                                                                                                                                                                                                                          |

|           |                                                                                                                               |                                                                                                                                                                             | regulator which is used for core operation power                                                                                                                                                                                                                                                      |

|           |                                                                                                                               |                                                                                                                                                                             | (VCC1A8, VCC1V8).                                                                                                                                                                                                                                                                                     |

|           |                                                                                                                               |                                                                                                                                                                             | Between the 1V8O and GND, Be sure to connect a                                                                                                                                                                                                                                                        |

|           |                                                                                                                               |                                                                                                                                                                             | 3.3uF tantalum capacitor for output frequency                                                                                                                                                                                                                                                         |

|           |                                                                                                                               |                                                                                                                                                                             | compensation and a 0.1uF capacitor for high                                                                                                                                                                                                                                                           |

|           |                                                                                                                               |                                                                                                                                                                             | frequency noise decoupling.                                                                                                                                                                                                                                                                           |

|           |                                                                                                                               |                                                                                                                                                                             | 1V8O is connected to VCC1V8, separated to 1uH                                                                                                                                                                                                                                                         |

|           |                                                                                                                               |                                                                                                                                                                             | inductor and connected to VCC1A8.                                                                                                                                                                                                                                                                     |

|           |                                                                                                                               |                                                                                                                                                                             | <notice> 1V8O is the power supply for W7100A use</notice>                                                                                                                                                                                                                                             |

|           |                                                                                                                               |                                                                                                                                                                             | only. This supply should not be connected with                                                                                                                                                                                                                                                        |

|           |                                                                                                                               |                                                                                                                                                                             | any other devices.                                                                                                                                                                                                                                                                                    |

| 6         | 39,         46,         54, 11         31,         43, 50         7,       7, 8,         6,       26,         92       47, 63 | 39,       Power         46,       -         54, 11       -         31,       Power         43, 50       -         7,       7, 8,         26,       -         47, 63       - | 39,       Power       -         46,       -       -         46,       -       -         54, 11       -       -         31,       Power       -         43, 50       -       -         7,       7, 8,       Power       -         6,       26,       -       -         92       47, 63       -       - |

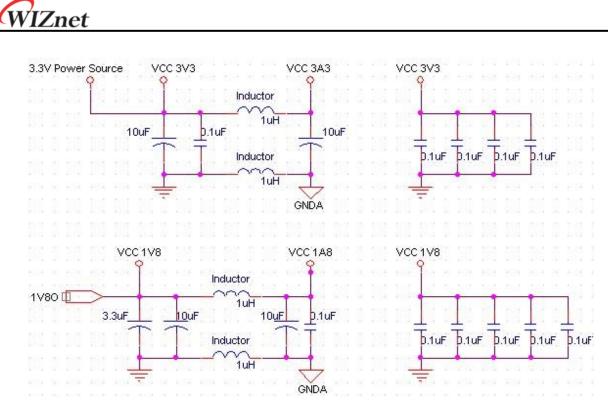

Figure 1.9 Power Design

## 1.5 64pin package description

| 1.5.1 | Difference | between | 100 | and | 64pin | package |

|-------|------------|---------|-----|-----|-------|---------|

|-------|------------|---------|-----|-----|-------|---------|

|                  | · · · ·                                       |                    |

|------------------|-----------------------------------------------|--------------------|

| Difference       | 64 pin                                        | 100 pin            |

|                  | T0, T1, GATE0, GATE1, T2, T2EX, nINT1, nINT2, |                    |

| Deleted siz      | nINT3, FDXLED, COLLED, RXLED, TXLED, PM2,     |                    |

| Deleted pin      | PM1, PM0, EXTALE, EXTDATAWR, EXTDATARD,       | -                  |

|                  | GPIO3[0:7], GPIO2[3:7]                        |                    |

| External memory  | Х                                             | 0                  |

| PHY mode setting | only use SFR                                  | use SFR or PM pins |

| GPIO             | max 19pin                                     | max 32pin          |

\*Note: In case of 64pin package, the PHY mode is must be set by PHYCONF SFR. So, user must set the MODE\_EN bit to enable the MODE2 ~ 0 bit configuration. Then set the MODE2 ~ 0 value and reset the PHY controlling the PHY\_RSTn bit. After the reset the 64pin package chip will be successfully initialized and operate properly. When the user uses the 64pin package chip, the code below must be executed in chip initialize routine.

For more detailed information about the PHYCONF SFR, please refer to the section 2.5.10 'New & Extended SFR'.

PHYCONF |= 0x08; // MODE\_EN bit enable

PHYCONF &= 0xF8; // MODE2 ~ 0 value is 0 (normal mode); Auto configuration mode

PHYCONF |= 0x20; // Set the PHY\_RSTn bit (reset bit)

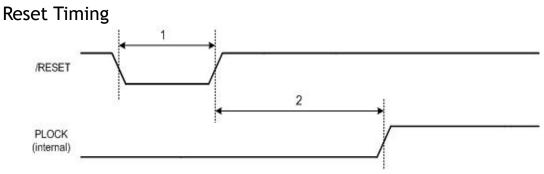

Delay(); // Delay for reset timing (refer to the section 10 'Reset Timing')

PHYCONF &= ~(0x20); // Clear the PHY\_RSTn bit

## 2 Memory

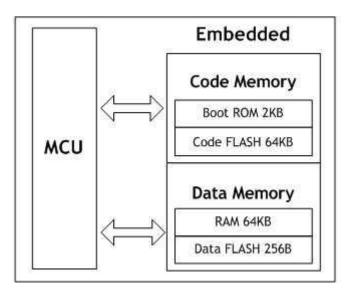

The W7100A's memory is divided into two types of memories: "Code Memory" and "Data Memory". Each memory can use the memory lock function. If the lock is set, internal memory accessing from outside is denied and also cannot use the W7100A debugger. For more detailed information about the memory lock function, please refer to the "WizISP Program Guide". The memory structure of W7100A is roughly shown figure 2.1.

Figure 2.1 Code / Data Memory Connections

#### \*Note:

We recommend the use of an external Power Supply Low Voltage Detector to prevent system malfunction during periods of insufficient power supply voltage.

It can be prevented Non-volatile Memory Corruption, SRAM Corruption and CPU Register Corruption. Please refer to the iMCU7100EVB's Schematic on <u>WIZnet website</u>.

(Example ICs : MAX811, MIC811, DS1811)

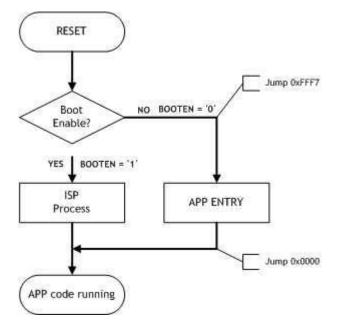

### 2.1 Code Memory

"Code Memory" consists the Boot ROM from 0x0000 to 0x07FF and Code FLASH from 0x0000 to 0xFFFF. After the system is reset, the W7100A always executes the code of Boot ROM at "Code Memory." According to the BOOTEN pin, the code of Boot ROM executes differently. Figure 2.2 shows the flow of Boot ROM code. After the booting, the system proceeds to either the ISP process or the APP Entry according to the BOOTEN pin. When ISP process is selected (BOOTEN = '1'), the ISP code of the Boot ROM will run. Otherwise (BOOTEN = '0'), the system jumps to the APP Entry without running the ISP code of Boot ROM.

ISP code is used for WizISP program when writing user code to code FLASH. And the APP Entry is used for running user application code. The APP Entry contains the 'memory map switching code' and the jumping code which jumps to the start address 0x0000 of the user application in Code FLASH memory. The memory map switching is as below.

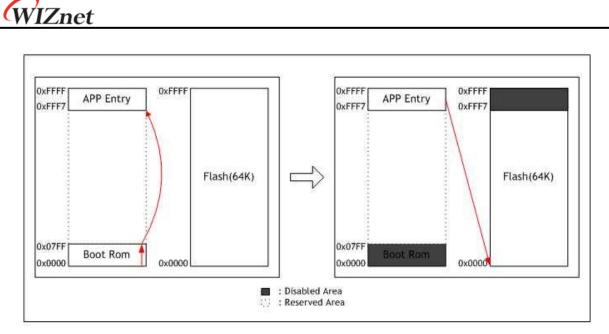

Figure 2.2. Boot Sequence Flowchart

The initial state of W7100A has both 'Boot ROM / APP Entry' and FLASH as shown in Figure 2.3. But since the addresses of 'Boot ROM / APP Entry' and FLASH are overlapped, they use same address at 0x0000 ~ 0x07FF / 0xFFF7 ~ 0xFFFF. The iMCU W7100A respectively maps the 'Boot ROM / APP Entry' and FLASH(64K) to the code and data memory.

The user application code can be written to the FLASH(mapped to data memory). But in this state, the FLASH cannot be used as a code memory because this state is for writing user application code. To use the FLASH as a code memory, the memory map needs to be switched. To do this, user should select APP Mode by setting the BOOTEN pin to '0', and then the Boot ROM code jumps to APP Entry immediately. Next, the APP Entry un-maps the Boot ROM and maps the Code FLASH to code memory. After switching the code memory map, the APP Entry

Figure 2.3 APP Entry Process

jumps to start address of Code FLASH (0x0000). This flow is shown in Figure 2.3.

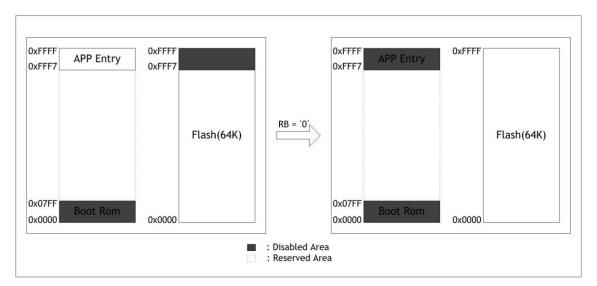

If the APP Mode is selected, the Code FLASH 64KB can be used as a code memory. But both FLASH and APP Entry are still overlapped at the same address. Therefore, to use all FLASH 64KB, the APP Entry must be un-mapped from "Code Memory." To un-map APP Entry, user should set RB bit in WCONF(0xFF) to '0' at the user startup code. Then the APP Entry is un-mapped as shown below.

Figure 2.4 Changing the code memory Status at RB = '0'

|    |       |     | W   | CONF (0) | kFF)     |    |    |       |

|----|-------|-----|-----|----------|----------|----|----|-------|

| 7  | 6     | 5   | 4   | 3        | 2        | 1  | 0  | Reset |

| RB | ISPEN | EM2 | EM1 | EM0      | Reserved | FB | BE | 0x00  |

W7100A Datasheet v1.2.5

When the Code FLASH takes more than 0xFFF7, the below code must be inserted into startup code. If using this method, the W7100A immediately disables the APP Entry address after its system reset.

| ANL 0FFH, #07FH ; Clear Reboot flag |

|-------------------------------------|

|-------------------------------------|

Set the BOOTEN pin to '0' and clear the **RB** bit of WCONF register at the startup code. Then the embedded Code FLASH 64KB memory of the W7100A can be completely used as a code memory.

### 2.1.1 Code Memory Wait States

The wait states are managed by internal WTST(0x92) register. The number of wait states is fixed by the value stored in the WTST register. Please refer to the section 2.5.10 'New & Extended SFR' for more details.

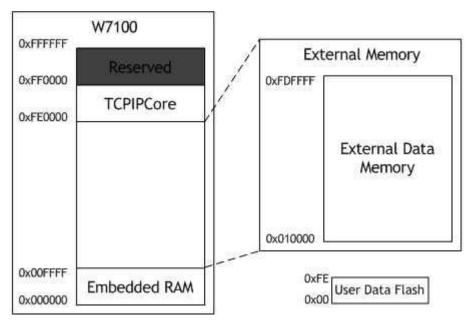

### 2.2 Data Memory

The W7100A contains 64KB of embedded RAM, 64KB of TCPIPCore and the 255Byte of the Data FLASH. The Data FLASH can be used for saving user IP, MAC, subnet mask or port number. Also the W7100A can address up to 16M bytes of external Data Memory. The figure below shows the Data Memory map. This memory is accessed by MOVX instructions only. The external memory can be extended by user.

Figure 2.5 Data Memory Map

### 2.2.1 Data Memory Wait States

The Data Memory wait states are managed by CKCON(0x8E). The number of wait states is fixed to the value stored inside CKCON register. Please refer to the section 2.5.10 'New & Extended SFR' for more detailed information.

## 2.3 External Data Memory Access

The external address pin and data pin has two access modes. The first mode is to use latch to address line in standard 8051. And the second method is directly connecting all lines to address line. Also user can use address pin and data pin as GPIO (General Purpose I/O). Please refer to the section 10 'Electrical specification' for the speed of external memory accessing.

| Mode       | EM[2:0] | PO                  | P1        | P2         | P3          |

|------------|---------|---------------------|-----------|------------|-------------|

| Standard 1 | 001     | Addr[7:0]/Data[7:0] | GPIO      | Addr[15:8] | GPIO        |

| Standard 2 | 011     | Addr[7:0]/Data[7:0] | GPIO      | Addr[15:8] | Addr[23:16] |

| Direct 1   | 101     | Data[7:0]           | Addr[7:0] | Addr[15:8] | GPIO        |

| Direct 2   | 111     | Data[7:0]           | Addr[7:0] | Addr[15:8] | Addr[23:16] |

Table 2.1 External memory access mode

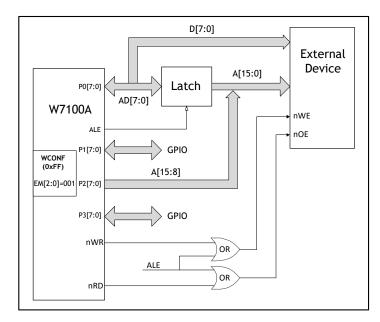

#### 2.3.1 Standard 8051 Interface

This method is same as external interface of general 8051. But the range of accessible address is changed refer to the setting of EM[2:0] (External Memory Mode) which spaced WCONF(0xFF) of SFR register. When user sets the EM[2:0] to "001", the port0 is used as address/data bus and the port2 is used as upper side address (A[15:8]). The port1 and port3 is used as GPIO.

#### Note :

The external memory interface using standard 8051 interface has an erratum where the ALE signal turns on after the WR/RD signal is enabled; the ALE signal is supposed to turn on before the WR/RD signal is enabled. To resolve this erratum, OR the WR/RD signal with ALE signal and connect it to the external memory's nWR and nOE.

For more details, please refer to document 'W7100A Errata sheet - Erratum3.'

It is shown the figure below.

Figure 2.6 Standard 8051 External Pin Access Mode (EM[2:0] = "001")

When user sets the EM[2:0] to "011", as in the previous case, the port0 is used as address/data bus and the port2 is used as upper side address (A[15:8]). But, since the port3 is used as topside address (A[23:16]), the range of accessible address is expanded. The remained port1 is used as GPIO. It is shown the figure below.

Figure 2.7 Standard 8051 External Pin Access Mode (EM[2:0] = "011")

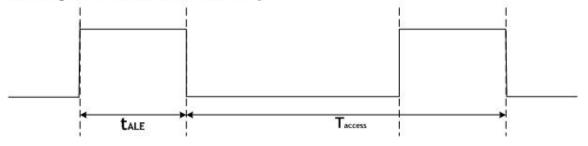

In the Standard 8051 External pin access mode, MCU controls the ALE (Address Latch Enable) signal to classify the address and data signal. User can configure the duration of ALE signal using the ALECON(0x9F) SFR. For more detailed information about ALECON, please refer to the section 2.5.10 'New & Extended SFR'.

### 2.3.2 Direct Interface

This method is directly connecting the data line to address line. When user sets the EM[2:0] to "101", the port0 is used as data line (D[7:0]) and the port1 is lower side address (A[7:0]) and the port2 is used as upper side address (A[15:8]). The remained port3 can be used as GPIO. Using this method, user can connect data line to address line without latch. It is shown the figure 2.8 as below.

Figure 2.8 Direct 8051 External Pin Access Mode (EM[2:0] = "101")

When user sets the EM[2:0] to "111", the port0, port1 and port2 has same usage in the previous case and the port3 is used as topside address (A[23:16]). In this method, there is no port to use GPIO. It is shown the figure below.

Figure 2.9 Direct 8051 External Pin Access Mode (EM[2:0] = "111")

WIZnet

## 2.4 Internal Data Memory and SFR

The Figure below shows the Internal Memory and Special Function Registers (SFR) map.

| 0xFF<br>0x80 | Upper Internal RAM shared<br>with Stack space<br>(indirect addressing) | SFR<br>Special Function Registers<br>(direct addressing) |

|--------------|------------------------------------------------------------------------|----------------------------------------------------------|

| 0x7F<br>0x30 |                                                                        | nared with Stack space                                   |

| 0x2F<br>0x20 | bit addres                                                             | ssable area                                              |

| 0x1F<br>0x00 | 4 banks, R                                                             | 0-R7 each                                                |

|  | Figure | 2.10 | Internal | Memory | Map |

|--|--------|------|----------|--------|-----|

|--|--------|------|----------|--------|-----|

The lower internal RAM consists of four register banks with eight registers each, a bitaddressable segment with 128 bits (16 bytes) that begins at 0x20, and a scratchpad area with 208 bytes is embedded. With **indirect** addressing mode ranging from 0x80 to 0xFF, the highest 128 bytes is accessed as an internal memory. But with **direct** addressing mode ranging from 0x80 to 0xFF, this area is accessed as a SFR memory.

| 0xF8 | EIP   | DPSBK | 2       | 62      | 3        | 15       | PHYCONF       | WCONF    |

|------|-------|-------|---------|---------|----------|----------|---------------|----------|

| 0xF0 | В     | ISPID | ISPADDR | ISPADDR | ISPDATA  | CKĊBK    | DPXOBK        | DPX1BK   |

| DxE8 | EIE   | 5     | MXAX    | PO_PU   | P1_PU    | P2_PU    | P3_PU         | PHY_IND  |

| DxE0 | ACC   | 1     | ŝ       | PO_PD   | P1_PD    | P2_PD    | P3_PD         |          |

| DxD8 | WDCON |       |         |         | CLK_CNT0 | CLK_CNT1 | CLK_CNT2      | CLK_CNT3 |

| 0xD0 | PSW   |       | Ş.      |         |          | §        | 8             |          |

| 0xC8 | T2CON |       | RLDL    | RLDH    | TL2      | TH2      | .0 6.         |          |

| 0xC0 |       | 2     | 5       |         |          | Reserved | 21 - 33       | TA       |

| 0xB8 | IP    |       | 0       |         |          | 5 V      | 8 5           | 9        |

| DxB0 | P3    | -     | 0       |         | -        | e 9      | ei - 77       | 9        |

| DxA8 | IE    | 0     | ÷.      |         |          | 1. T     | 10 <i>1</i> 2 | tr )     |

| 0AXC | P2    | 0     | 10      |         |          | N        | 8 V           |          |

| 0x98 | SCONO | SBUF  |         |         | INTWTST  | EXT      | NTST          | ALECON   |

| 0x90 | P1    | EIF   | WTST    | DPX0    |          | DPX1     |               |          |

| 0×88 | TCON  | TMOD  | TLO     | TL1     | TH0      | TH1      | CKCON         | 11       |