# Spartan-6 FPGA Connectivity Targeted Reference Design

User Guide

UG392 (v1.5) October 5, 2010

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

#### **CRITICAL APPLICATIONS DISCLAIMER**

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

© Copyright 2009–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

# **Revision History**

The following table shows the revision history for this document.

| Date Version                                                      |     | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 12/08/09                                                          | 1.0 | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 12/17/09 1.1                                                      |     | Updated Figure 1-1, page 12. Revised register and LUT utilization numbers in Table and Table 1-2.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                   |     | Updated Software Bring Up in Chapter 2 section. Updated the MAC address to<br>\$./setmac_id ethX <sp605_mac_id>. Added clarification to Test Setup and Payload<br/>Statistics. Edited Using Various Features including removal of Checksum Offload<br/>section and updating NIC Statistics. Updated Packet Size. Revised the following<br/>command line instruction to: \$ ./implement_1000basex.sh. Added a note above<br/>Figure 2-23.</sp605_mac_id>                                                                                      |  |  |

|                                                                   |     | Minor edits to Figure 3-1, Figure 3-3, Figure 3-4, Figure 3-5, Figure 3-8, Figure 3-9 and Figure 3-11. Changed Checksum Field Mapping for C2SDescUserStatus[63:32] in Table 3-3. Clarifying edits to the Clocking Strategy section.                                                                                                                                                                                                                                                                                                          |  |  |

|                                                                   |     | Added Checksum Offload in Chapter 5. Revised some of the TRD file/folder names.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                   |     | Added troubleshooting tips in Table D-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 05/13/10 1.2 Updated resource utilization numbers in Table 1-1 ar |     | Updated resource utilization numbers in Table 1-1 and Table 1-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                                                   |     | Added ProjNav Based Flow.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                                                   |     | Added the html folder to Figure B-1 and updated the design and driver discussion.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                   |     | Updated DDR3 interface performance to 667 Mb/s in Figure 1-1 and on page 13.<br>Updated LUT resource utilization numbers in Table 1-1 and Table 1-2.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                                   |     | Revised Simulation Requirements and IP Cores with TRD sections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                   |     | Revised the differential clock input requirement to 333.5 MHz on page 57 and updated the PLL settings in the memc3_infrastructure.v file. Also updated the Clocking Strategy section. Updated to 667 MHz clock in Figure 3-9.                                                                                                                                                                                                                                                                                                                |  |  |

|                                                                   |     | Updated the Theoretical Calculation section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 08/11/10                                                          | 1.4 | Removed references to specific ISE software releases in Hardware Test Setup<br>Requirements and Simulation Requirements. In IP Cores with TRD, changed<br>gig_eth_pcs_pma_v10_4 to gig_eth_pcs_pma_v10_5 and mig_v3_4.xco to<br>mig_v3_5.xco.                                                                                                                                                                                                                                                                                                |  |  |

| 10/05/10                                                          | 1.5 | Updated resource utilization numbers in Table 1-1 and Table 1-2. Updated description<br>Simulation Requirements. Updated core/netlist names and added information abou<br>readme.txt in IP Cores with TRD. Added Simulating the Design with ISim. Chang<br>"Simulating the Design" to Simulating the Design with ModelSim and updated the<br>description. Moved User Controlled Macros and Test Selection sections. Added Desi<br>Version Register (0x8000). Updated 0x8000 to 0x8004 in UserApp Advertisement<br>Register (0x8004) heading. |  |  |

# Table of Contents

| Revision History                                                                                                             | 3      |

|------------------------------------------------------------------------------------------------------------------------------|--------|

| Preface: About This Guide                                                                                                    |        |

| Guide Contents                                                                                                               | 9      |

| Additional Documentation                                                                                                     | )      |

| Additional Support Resources                                                                                                 | )      |

| Chapter 1: Introduction to the Reference Design                                                                              |        |

| The Targeted Reference Design 11                                                                                             | 1      |

| Introduction                                                                                                                 | 1      |

| Features       13         Base Features       13         Application Features       13         Resource Utilization       14 | 3<br>3 |

| Chapter 2: Getting Started                                                                                                   |        |

| Introduction                                                                                                                 | 5      |

| <b>Requirements</b>                                                                                                          |        |

| Hardware Test Setup Requirements                                                                                             |        |

| Simulation Requirements                                                                                                      |        |

| Hardware Test Setup       15         Hardware Bring Up       16                                                              |        |

| Software Bring Up                                                                                                            |        |

| Network Bring Up 24                                                                                                          | 4      |

| Using Application GUI 29                                                                                                     |        |

| Using Various Features                                                                                                       |        |

| Ethernet Specific Features                                                                                                   |        |

| Autonegotiation                                                                                                              |        |

| Promiscuous Mode                                                                                                             |        |

| Memory Application Specific Features                                                                                         |        |

| Packet Size                                                                                                                  |        |

| Shutting Down the System                                                                                                     |        |

| IP Cores with TRD                                                                                                            |        |

| Implementing the Design       35         Script Based Flow       35                                                          |        |

| Script Based Flow                                                                                                            | -      |

| Programming the SP605 37                                                                                                     | 7      |

| Board Settings    37      Board Programming    37                                                                            |        |

| Simulation                          | 40 |

|-------------------------------------|----|

| Overview                            | 40 |

| User Controlled Macros              | 41 |

| Test Selection                      |    |

| Simulating the Design with ISim     | 42 |

| Simulating the Design with ModelSim |    |

## **Chapter 3: Functional Description**

| Hardware Design Description 45         |

|----------------------------------------|

| Base Design Architecture 47            |

| Integrated Endpoint for PCI Express    |

| Packet DMA                             |

| Network Path Architecture              |

| XPS-LL-TEMAC                           |

| Ethernet 1000BASE-X PCS-PMA Core       |

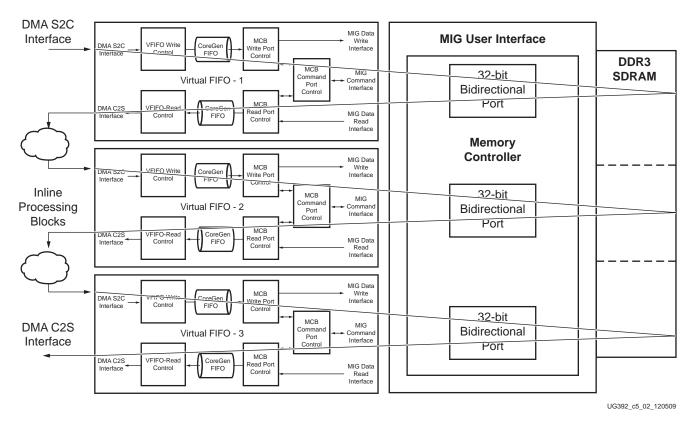

| Memory Path Architecture 57            |

| Memory Interface Generator             |

| Virtual FIFO                           |

| Common Registers                       |

| TRN Monitor Registers                  |

| Clocking and Reset                     |

| Clocking Strategy                      |

| Reset Scheme                           |

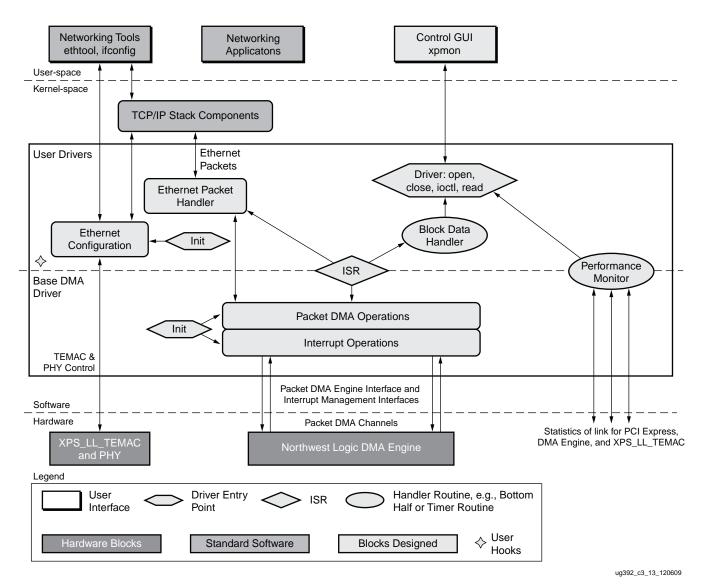

| Software Design Description            |

| User-Space Application Features        |

| Kernel-Space Driver Features           |

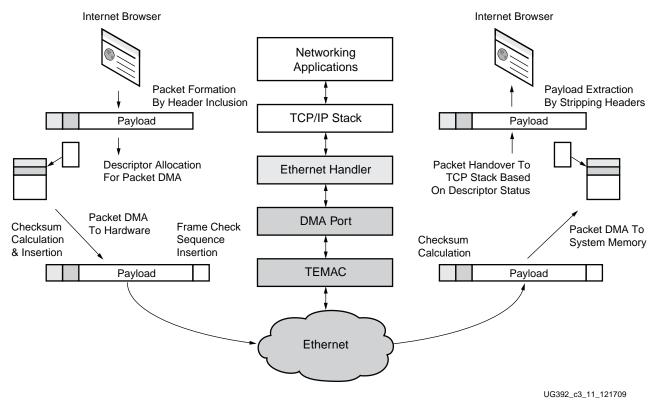

| Data Flow Model                        |

| Ethernet Data Flow                     |

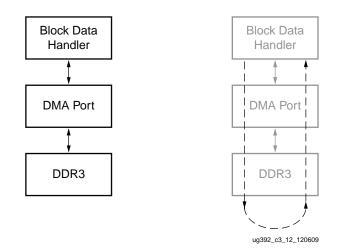

| Memory Data Flow                       |

| Software Architecture                  |

| Applications                           |

| Kernel Components                      |

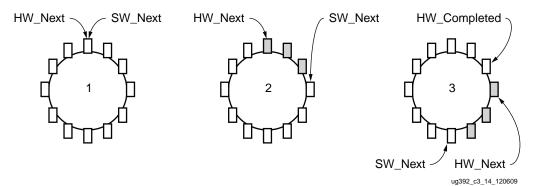

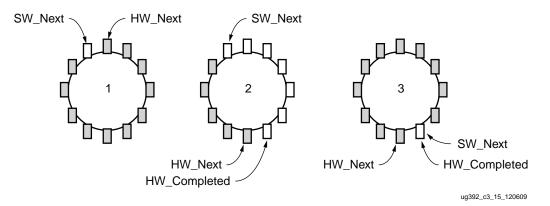

| DMA Descriptor Management              |

| Dynamic DMA Updates                    |

| User Interface—Control and Monitor GUI |

| System Logging                         |

## **Chapter 4: Performance Estimation**

| PCI Express Performance          | 73 |

|----------------------------------|----|

| Ethernet Performance             | 75 |

| Memory Controller Performance    | 75 |

| Measuring Performance            | 76 |

| Ethernet Performance Measurement | 77 |

| Throughput Estimate and Analysis | 77 |

| CPU Utilization Analysis         | 77 |

## Chapter 5: Designing with the TRD Platform

| Software-Only Modifications | 79 |

|-----------------------------|----|

| Macro-Based Modifications   |    |

| Descriptor Ring Size        | 79 |

## Appendix A: Register Description

| DMA Registers                                          | . 86 |

|--------------------------------------------------------|------|

| Channel Specific Registers                             |      |

| DMA Engine Control (0x0004)                            | 87   |

| Next Descriptor Pointer (0x0008)                       |      |

| Software Descriptor Pointer (0x000C)                   |      |

| Completed Byte Count (0x001C)                          |      |

| Common Registers                                       |      |

| Common Control and Status (0x4000)                     | 88   |

| Network Path IP Registers                              | . 88 |

| XPS-LL-TEMAC Registers                                 | . 88 |

| Reset and Address Filter Register (0x0)                | . 89 |

| Statistics Registers                                   |      |

| Receive Configuration Word Register (Indirect, 0x240)  | . 89 |

| Transmit Configuration Word Register (Indirect, 0x280) | . 90 |

| Management Configuration Register (Indirect, 0x340)    | . 90 |

| Address Filter Mode Register (Indirect, 0x390)         | 91   |

| User Application Registers                             | . 91 |

| Design Version Register (0x8000)                       | . 91 |

| User Application Advertisement Registers               | . 92 |

| UserApp Advertisement Register (0x8004)                | . 92 |

| User Interrupt Registers                               |      |

| User Interrupt Enable Register (0x8100)                | . 92 |

| User Interrupt Status Register (0x8104)                | . 93 |

| TRN Monitor Registers                                  | . 93 |

| Transmit Utilization Byte Count (0x8200)               | 93   |

| Receive Utilization Byte Count (0x8204)                | 94   |

| Upstream Memory Write Byte Count (0x8208)              | 94   |

| Downstream Completion Payload Byte Count (0x820C)      | 94   |

| TRN Monitor Control (0x8210)                           | 95   |

| User App1 Registers                                    | 95   |

| Virtual FIFO Status Register (0x9100)                  |      |

| Virtual FIFO Receive Packet Length Register (0x9104)   | 95   |

| Virtual FIFO Start Address Register (0x9108)           | 95   |

| Virtual FIFO End Address Register (0x910C)             |      |

| Virtual FIFO Error Statistics Register (0x9110)        | 96   |

| Appendix B: Directory Structure                      |

|------------------------------------------------------|

| Introduction                                         |

| Appendix C: Setting Up a Private LAN<br>Introduction |

| Appendix D: Troubleshooting                          |

| Introduction                                         |

# Preface

# About This Guide

The Spartan®-6 FPGA Connectivity Targeted Reference Design delivers all the basic components of a targeted design platform for the connectivity domain in a single package. Targeted Design Platforms from Xilinx provide customers with simple, smart design platforms for the creation of FPGA-based solutions in a wide variety of industries.

This user guide details a targeted reference design developed for the connectivity domain on a Spartan-6 FPGA. The aim is to accelerate the design cycle and enable FPGA designers to spend less time developing the infrastructure of an application and more time creating a unique value-add design.

## Guide Contents

This document contains the following chapters:

- Chapter 1, Introduction to the Reference Design provides an introduction to the targeted reference design and outlines its features.

- Chapter 2, Getting Started provides a quick-start guide to help the user get started with the hardware setup and simulation.

- Chapter 3, Functional Description provides a detailed architectural description of the hardware and software driver implemented. A separate software programming manual listing the software APIs is delivered with the software source.

- Chapter 4, Performance Estimation provides a detailed report on theoretical estimation and analysis of the design performance.

- Chapter 5, Designing with the TRD Platform provides suggested variations and add-ons to the platform to implement different functions.

- Appendix A, Register Description details certain registers programmed by the software driver. This section provides a comprehensive register programming manual.

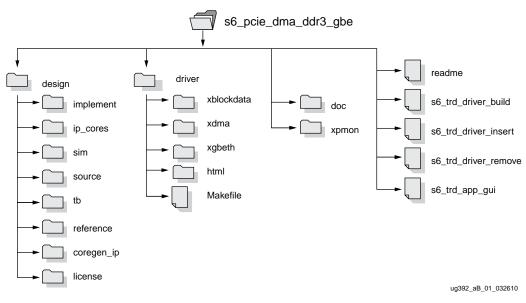

- Appendix B, Directory Structure details the directory structure and the organization of various files and folders.

- Appendix C, Setting Up a Private LAN provides instructions on setting up a private LAN connection to enable testing with Netperf.

- Appendix D, Troubleshooting provides tips on areas to look for when debugging a design.

# **Additional Documentation**

The following documents have been used as a reference to develop this Targeted Reference Design (TRD).

- <u>UG654</u>, Spartan-6 FPGA Integrated Endpoint Block for PCI Express User Guide

- Northwest Logic Packet DMA Backend Core User Guide

- <u>Product Sheet</u>

- <u>DS537</u>, XPS LL TEMAC (v2.03a) Data Sheet

- <u>UG388</u>, Spartan-6 FPGA Memory Controller User Guide

- UG155, LogiCORE IP Ethernet 1000BASE-X PCS/PMA or SGMII v10.4 User Guide

- <u>DS563</u>, PLBV46 Master Single (v1.00a) Data Sheet

- MARVELL PHY 88E1111 Data Sheet

- <u>UG526</u>, SP605 Hardware User Guide

- Fedora Project

- Netperf v2.4 Manual

- GTK+ 2.0 <u>Manual</u>

# **Additional Support Resources**

To search the database of silicon and software questions and answers or to create a technical support case in WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

Chapter 1

# Introduction to the Reference Design

## The Targeted Reference Design

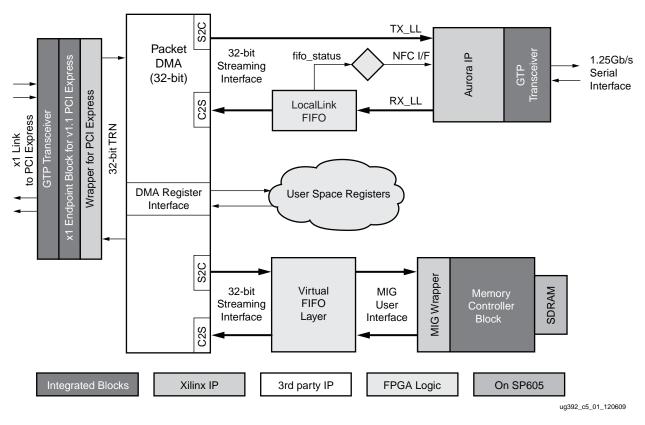

The targeted reference design demonstrates the key integrated components in a Spartan®-6 FPGA, namely the integrated Endpoint block for PCI Express®, the transceivers, and the memory controller working together in an application along with additional IP cores including the third-party (Northwest Logic) Packet Direct Memory Access (DMA) engine, Xilinx® Platform Studio LocalLink Tri-Mode Ethernet MAC (XPS-LL-TEMAC), and the Xilinx Memory Interface Generator (MIG) in the CORE Generator<sup>TM</sup> tool.

This chapter introduces the targeted reference design for Spartan-6 FPGAs and outlines its features.

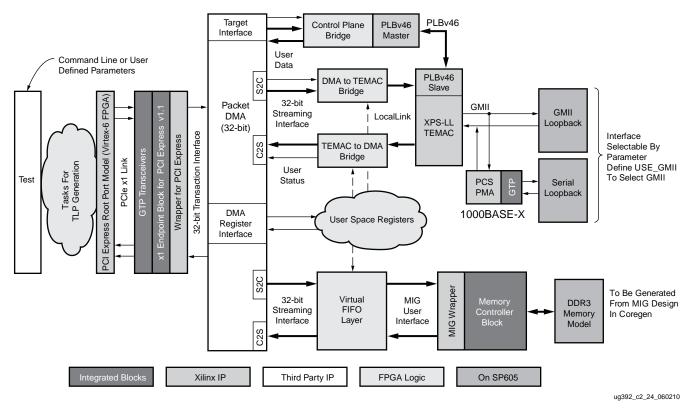

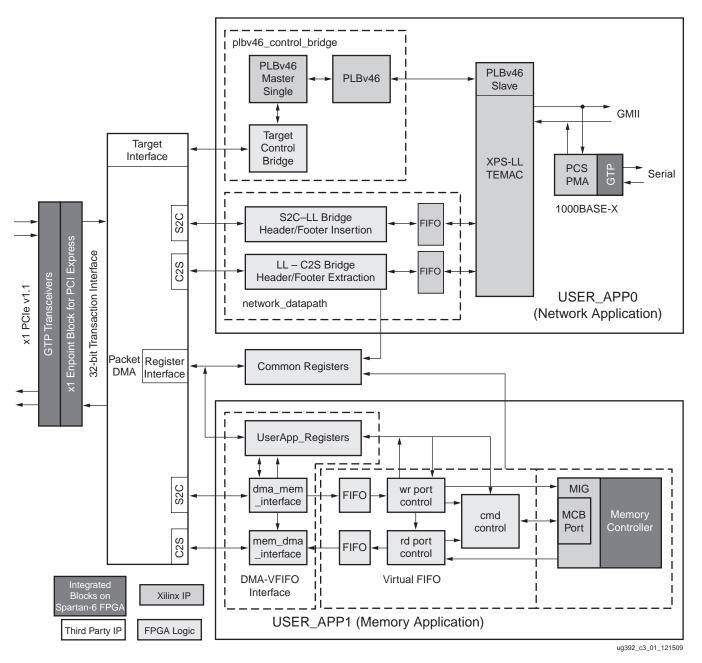

## Introduction

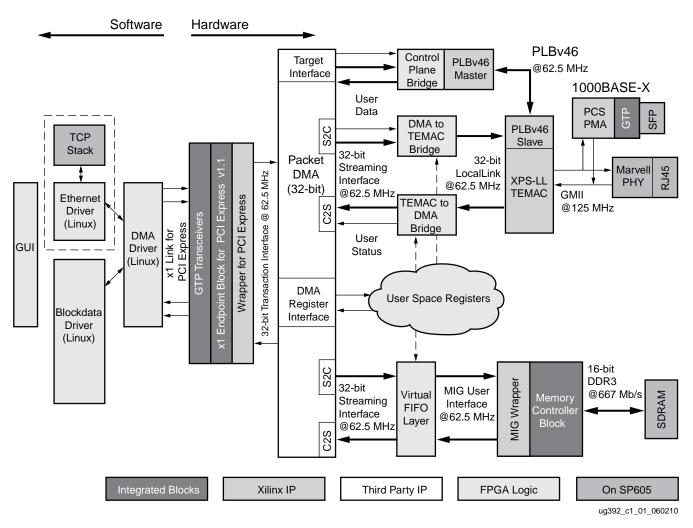

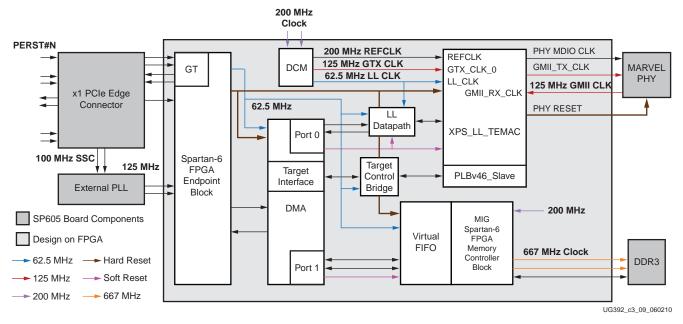

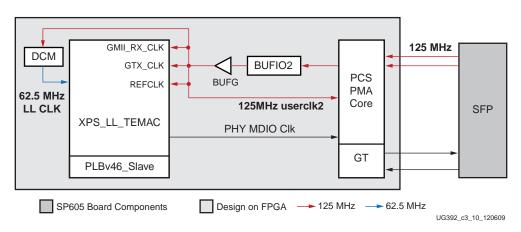

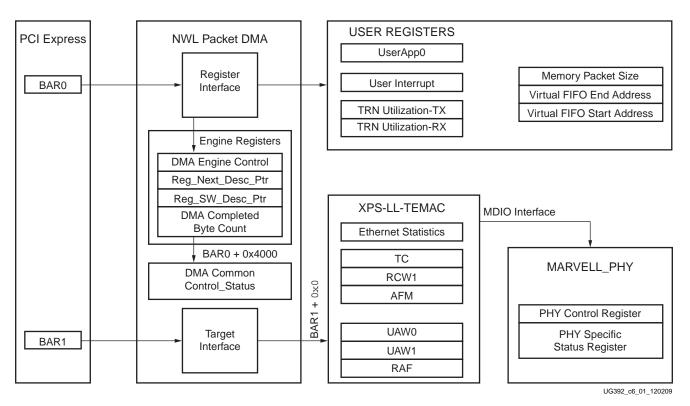

The block diagram of the Targeted Reference Design (TRD) is shown in Figure 1-1, page 12. This design is a PCI Express v1.1 compliant x1 Endpoint block showcasing these independent applications.

- Network interface card (network path), providing either:

- GMII mode using an external Ethernet PHY (typically used to connect to Copper networks) or

- 1000BASE-X mode using the GTP transceivers on the FPGA (typically used to connect to optical fiber Ethernet networks).

This card allows the designer to connect to an external network and run networking applications including browsing web pages, telnet, and ftp sites.

• External memory interface over PCI Express—also referred to as the memory path.

This application showcases data movement between system memory and DDR3 SDRAM through the Spartan-6 FPGA.

The TRD uses a bus-mastering packet Direct Memory Access (DMA) engine to offload processor data transfer overhead. The DMA works in conjunction with the integrated Endpoint for PCI Express and enables high-speed data movement between system memory and the FPGA.

The TRD framework is built with the integrated Endpoint and DMA blocks forming the foundation of an entire platform. The network path and memory path are two applications developed around this foundation.

www.xilinx.com

🗶 XILINX.

- GMII mode using the external PHY onboard

- 1000BASE-X mode using the Spartan-6 FPGA transceivers through an additional 1000BASE-X PCS-PMA IP core

The memory path showcases the integrated memory controller on a Spartan-6 FPGA. The controller communicates to onboard DDR3 SDRAM through MIG. Using the connected components, data can be written to and read back from the external memory.

Figure 1-1: Top-Level Design Overview

## Features

The design features are classified as either:

- Base Features: Features of the base components of the design including DMA and the integrated Endpoint block for PCI Express.

- Application Features: Features supported by each application developed on top of the base features.

Additionally, the source code of the software driver for a Linux platform is provided. The layered implementation of the software driver enables the designer to choose any layer (pertaining to specific hardware functionality) and customize it to specific requirements.

## **Base Features**

This section lists the base features of the integrated Endpoint block for PCI Express and Packet DMA which form the backbone of the entire design.

- PCI Express v1.1 compliant x1 Endpoint block

- One lane operation with GTP transceiver at a line rate of 2.5 Gb/s/direction

- MSI and Legacy interrupt support

- Transaction interface utilization engine for PCI Express

- Optional high-performance mode utilizing extra block RAMs

- Bus Mastering Packet DMA

- Multichannel operation

- Packetized interface (similar to LocalLink)

- Scatter Gather operation

- DMA performance engine

- Full-duplex operation (independent transmit and receive channels)

## Application Features

The various application features are:

- Network Path Features

- Ethernet address filtering

- Ethernet statistics engine

- TCP/UDP checksum offload

- Auto-negotiation

- Jumbo frames

- Optional 1000BASE-X mode

- Memory Path Features

- Integrated DDR3 controller providing up to 667 Mb/s performance

- 16-bit single-component memory interface providing up to 10.672 Gb/s aggregate bandwidth

- Reusable virtual FIFO interface with programmable depth

## **Resource Utilization**

Table 1-1 and Table 1-2 list the resource utilization obtained from the map report during implementation phase. The XC6SLX45T-3-FGG484 is the target FPGA.

**Note:** The utilization numbers reported are obtained with the default options as provided in the top-level design. A change in default options will result in a change in utilization. The transceiver utilization is reported for the GTPA1\_DUAL; one transceiver each is utilized from the GTPA1\_DUAL (not both).

| Resource        | Utilization | Total Available | Percentage<br>Utilization |

|-----------------|-------------|-----------------|---------------------------|

| Slice registers | 21,990      | 54,576          | 40                        |

| Slice LUTs      | 17,623      | 27,288          | 64                        |

| IOB             | 82          | 296             | 28                        |

| RAMB16BWER      | 35          | 116             | 29                        |

| RAMB8BWER       | 3           | 232             | 1                         |

| DCM             | 1           | 8               | 12                        |

| PLL_ADV         | 2           | 4               | 50                        |

| BUFG            | 10          | 16              | 62                        |

| GTPA1_DUAL      | 1           | 2               | 50                        |

#### Table 1-2: Resource Utilization—1000BASE-X Mode

| Resource        | Utilization | Total Available | Percentage<br>Utilization |

|-----------------|-------------|-----------------|---------------------------|

| Slice registers | 22,439      | 54,576          | 41                        |

| Slice LUTs      | 17,662      | 27,288          | 64                        |

| IOB             | 58          | 296             | 19                        |

| RAMB16BWER      | 35          | 116             | 29                        |

| RAMB8BWER       | 3           | 232             | 1                         |

| DCM             | 1           | 8               | 12                        |

| PLL_ADV         | 2           | 4               | 50                        |

| BUFG            | 10          | 16              | 62                        |

| GTPA1_DUAL      | 2           | 2               | 100                       |

The 1000BASE-X mode utilizes the PCS-PMA core, which increases the utilization of LUTs. Because the 1000BASE-X mode provides a serial interface as compared to a parallel interface with GMII mode, a corresponding reduction is seen in IOB usage. The 1000BASE-X mode uses an additional GTP transceiver.

# Chapter 2

# **Getting Started**

## Introduction

This chapter is a quick-start guide enabling the user to test the Targeted Reference Design (TRD) in hardware with the software driver provided and also simulate it. It provides step-by-step instructions for testing the design in hardware.

## Requirements

This section lists the minimum prerequisites of hardware testing and simulation.

## Hardware Test Setup Requirements

The prerequisites for testing the design in hardware are:

- SP605 board with an XC6SLX45T-3 device

- ISE® software design tools

- USB JTAG for FPGA programming

- RJ45 cable and network connectivity

- PC with PCIe® v1.1 compliant slot, with at least 1GB of RAM and a 1MB cache

- Fedora 10 Linux (32-bit) OS corresponding with Linux kernel version 2.6.27

- GTK+ v2.0 package required for GUI application

- Netperf v2.4 (optional)

### Simulation Requirements

This section lists the prerequisites for simulation:

- ISE software design tools (system or embedded edition with EDK installed)

- ModelSim v6.5c or later

## Hardware Test Setup

This section details the hardware setup and use of the provided application GUI to help the user get started quickly with the design in hardware. It provides a step-by-step explanation on hardware bring-up, software bring-up, Ethernet bring-up, and using the application GUI provided.

All procedures listed require super-user access on Linux machines. When using the Fedora 10 Linux OS LiveCD provided with the kit, super-user access is granted by default due to

the way the kernel image is built; if not using LiveCD, contact your system administrator for super-user access.

**Note:** The changes made during LiveCD environment are not saved. For example, if the driver files were copied on the desktop after booting with LiveCD, they do not exist anymore after the system is shutdown and booted again with LiveCD. This is because the root file system for OS on LiveCD is created on system RAM and is not permanently on the hard disk.

## Hardware Bring Up

This section lists the detailed steps for hardware bring-up.

- 1. With the host system switched to off, insert the SP605 board in the PCI Express® slot through the PCI Express x1 edge connector.

- 2. Connect the 12V ATX power supply 4-pin disk drive type connector to the board and also connect an Ethernet LAN cable in the RJ-45 slot provided. Do not power the board with both an external supply and the ATX supply at the same time.

- 3. Make sure the connections are secure so as to avoid loose contact problems. Power on the system.

UG392\_c2\_01\_120609

Figure 2-1: Board Setup

4. If using a PC with the Fedora 10 installed, proceed directly to step 7.

5. When using the Fedora 10 LiveCD provided in the SP605 kit, configure the desktop PC to boot from the CD ROM in the BIOS while the system starts. The Fedora 10 LiveCD provided in the kit is for Intel compatible PCs. The CD contains a complete bootable Fedora 10 Live environment and packages required for the targeted reference design demonstration. While the system boots from the CD, the screen is as shown in Figure 2-2.

UG392\_c2\_02\_120609

Figure 2-2: Fedora 10 LiveCD Boot Screen

6. On the login screen (Figure 2-3), follow the instructions and proceed.

Figure 2-3: Fedora 10 LiveCD Automatic Login

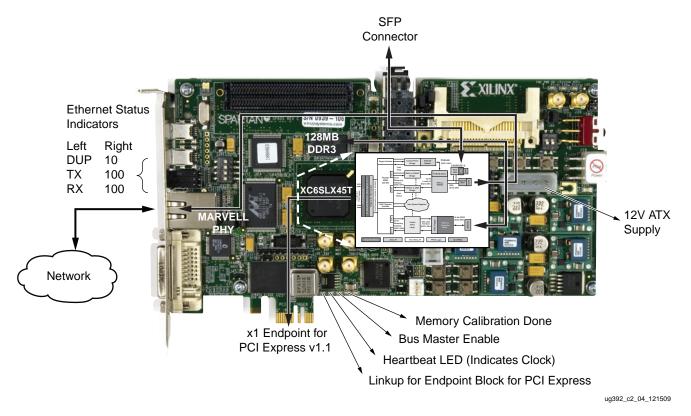

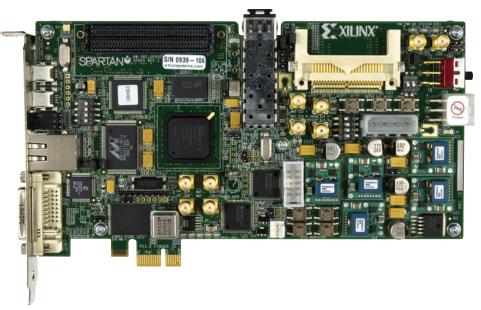

- 7. Verify the hardware status through visual inspection. Make sure that the following indicators glow after powering on the system. Figure 2-4 indicates the location of the indicators.

- PCI Express link up

- Ethernet link status (seen on the left-hand side in Figure 2-4, side-view of the board)

- Memory calibration complete

Figure 2-4 shows the entire design as mapped to hardware and the various components used on the SP605 board. The figure also highlights the visual indicators.

Figure 2-4: Design on SP605 Board

8. Check if the Endpoint block for PCI Express is detected by the system after the system boots by opening a terminal window (go to **Application**→**System Tools**→**Terminal**) and perform the following:

At the terminal command line:

\$ lspci

One of the entries should show the following information:

01:00.0 Communication controller: Xilinx Corporation Device 6011 (rev 04)

Where, 01:00.0 shows the PCI Express bus, device, and function number. As details in the output of the lspci command can vary from system to system, it is important that the Xilinx device is identified.

To view details about the device configuration space, perform the following:

\$ lspci -d 10EE:6011 -v -x

where, 10EE is the vendor ID and 6011 is the device ID for the Endpoint. As details can vary from system to system, it is important to check that the vendor ID (10EE) and device ID (6011) match.

| Iiveuser@localhost:~                                                                                                                                                                                                                                                                                                                                           | + X |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>T</u> erminal <u>T</u> abs <u>H</u> elp                                                                                                                                                                                                                                                                              |     |

| <pre>[liveuser@localhost ~]\$ lspci -d 10ee:6011 -x<br/>01:00.0 Communication controller: Xilinx Corporation Device 6011 (rev 04)<br/>00: ee 10 11 60 07 00 10 00 04 00 80 07 10 00 00 00<br/>10: 00 00 21 d9 00 00 20 d9 00 00 00 00 00 00 00 00 00<br/>20: 00 00 00 00 00 00 00 00 00 00 00 ee 10 11 60<br/>30: 00 00 00 00 40 00 00 00 00 00 00 00 00</pre> | <(  |

|                                                                                                                                                                                                                                                                                                                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                | )>  |

UG392\_c2\_05\_120609

Figure 2-5: Ispci Output

To see more configuration space details type:

\$sudo lspci -d 10EE:6011 -vvv -xxx

## Software Bring Up

This section gives steps for bringing up the software driver, application, and using the various scripts provided.

1. After the device is detected, copy the s6\_pcie\_dma\_ddr3\_gbe folder from the USB flash drive provided in the Connectivity kit to the desktop (or a folder of choice). After the folder is copied, unmount and disconnect the USB drive.

Double-click on the copied s6\_pcie\_dma\_ddr3\_gbe folder.

The screen capture in Figure 2-6 shows the contents of the s6\_pcie\_dma\_ddr3\_gbe TRD folder.

UG392\_c2\_06\_120609

Figure 2-6: TRD Folder on the USB Flash Drive

2. This step involves driver compilation and insertion of the kernel modules. Separate steps are defined for a command line user conversant with Linux or for a user preferring button-click operations.

#### Command Line Mode using Makefile

To compile and insert the driver, type at the command line in the terminal in the driver folder. Navigate to the s6\_pcie\_dma\_ddr3\_gbe/driver folder and follow the steps.

To clean the area:

\$ make clean

To compile the files and build the kernel objects:

\$ make

To insert the kernel object files:

\$ make insert

#### Command Line Mode using Executable Scripts

The executable scripts provided can be run as-is on the command line:

For compilation of the driver modules:

\$ ./s6\_trd\_driver\_build

For insertion of the driver modules and to invoke the application GUI:

\$ ./s6\_trd\_driver\_insert

#### Mouse Click Driven Mode

To compile the driver, open the s6\_pcie\_dma\_ddr3\_gbe folder.

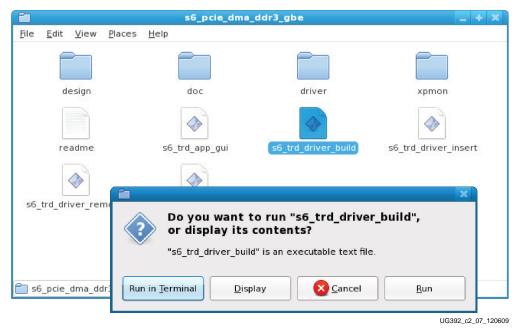

Double-click on **s6\_trd\_driver\_build**. This cleans the area and builds the kernel objects. A window prompt appears (shown in Figure 2-7), click on **Run in Terminal** and proceed.

Figure 2-7: Executing the Build Script

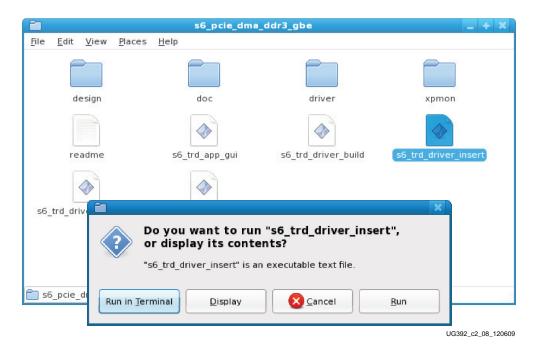

Double-click on **s6\_trd\_driver\_insert** (Figure 2-8). A Window prompt appears (shown in Figure 2-8), click on **Run in Terminal** and proceed. This inserts the driver modules into the kernel.

Figure 2-8: Executing the Insert Script

Proceed to Network Bring Up for network bring-up and GUI application usage.

3. To check if the driver modules are loaded into the kernel, try to use the lsmod utility in Linux. To see a list of kernel objects loaded:

\$lsmod | more

xblockdata\_s6, xgbeth, and xdma\_s6 modules are the Xilinx driver modules loaded as part of this TRD.

|                                        | liveuser@localhost:~                       | _ + X    |

|----------------------------------------|--------------------------------------------|----------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew | <u>T</u> erminal <u>T</u> abs <u>H</u> elp |          |

| [liveuser@local                        | nost ~]\$ lsmod   more                     | <u>^</u> |

| Module                                 | Size Used by                               |          |

| xblockdata s6                          | 42524 0                                    |          |

| xgbeth                                 | 25872 0                                    |          |

| xdma s6                                | 419868 2 xblockdata_s6,xgbeth              |          |

| vfat                                   | 12672 1                                    |          |

| fat                                    | 42784 1 vfat                               | 11       |

| usb_storage                            | 82440 1                                    |          |

| fuse                                   | 49436 2                                    | ~        |

UG392\_c2\_09\_120609

Figure 2-9: Ismod Output

## Network Bring Up

After successful completion of the steps listed in Hardware Bring Up, page 16 and Software Bring Up, page 20, proceed to enable the Ethernet interface.

This section details Ethernet bring-up and uses the Network Configuration GUI on Linux.

1. To add a new network device, open the Network Configuration GUI (Figure 2-10)

UG392\_c2\_10\_120509

#### Figure 2-10: Network Configuration GUI Path

Note: If the LiveCD is not being used, invoking the Network Configuration GUI requires super-user password.

The GUI in Figure 2-11 appears.

| 📲 Network Configuration 📃 🕂 🗶                                                                                                                               |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <u>F</u> ile <u>P</u> rofile <u>H</u> elp                                                                                                                   |  |  |  |  |  |  |

| New Edit Copy Delete Activate Deactivate                                                                                                                    |  |  |  |  |  |  |

| Devices Hardware DNS Hosts                                                                                                                                  |  |  |  |  |  |  |

| You may configure network devices associated with<br>physical hardware here. Multiple logical devices can be<br>associated with a single piece of hardware. |  |  |  |  |  |  |

| Profile Status Device Nickname Type                                                                                                                         |  |  |  |  |  |  |

|                                                                                                                                                             |  |  |  |  |  |  |

| Active profile: Common                                                                                                                                      |  |  |  |  |  |  |

UG392\_c2\_11\_120609

With the LiveCD, the devices tab does not show anything as no interface is active. Make sure that the Ethernet cable is not connected to the existing LAN port on the PC.

**Note:** Activating multiple Ethernet ports on the same system requires each of the ports to be on different subnets. For this setup, do not connect any other network cable to the existing Ethernet ports on the PC. Connect the network cable only to the SP605 board RJ45 slot provided.

The **Hardware** tab shows the hardware devices present. As an example for this section, assume the NIC is detected as eth1 as shown in Figure 2-12.

| Network Configuration 🔤 🕂 🗶               |                |        |        |  |  |  |  |

|-------------------------------------------|----------------|--------|--------|--|--|--|--|

| <u>F</u> ile <u>P</u> rofile <u>H</u> elp |                |        |        |  |  |  |  |

| New Edit Copy                             | )<br>Delete    |        |        |  |  |  |  |

| Devices Hardware DNS                      | H <u>o</u> sts |        |        |  |  |  |  |

| You may configur<br>physically attache    |                |        |        |  |  |  |  |

| Description                               | Туре           | Device | Status |  |  |  |  |

|                                           | Ethernet       | ethl   | system |  |  |  |  |

|                                           | Ethernet       | 🗃 pan0 | system |  |  |  |  |

| Intel Corporation 82567LM                 | Ethernet       | 📻 eth0 | system |  |  |  |  |

|                                           |                |        |        |  |  |  |  |

| Active profile: Common                    |                |        |        |  |  |  |  |

UG392\_c2\_12\_120609

Figure 2-12: Network Configuration GUI—Hardware Tab

To have the SP605 NIC show up in the **Devices** tab, a new Ethernet connection needs to be created.

#### Click on New $\rightarrow$ Create New Ethernet Connection.

Complete the setup process by following the instructions carefully on the screen. If an existing Ethernet connection(s) is available, this NIC is detected as an additional ethX interface where X would depend on the number of existing Ethernet interfaces.

The IP address assignment can be static or dynamic depending on the network setup. Contact the network administrator to understand IP address assignments on the network and also to obtain the necessary settings for network configuration.

Enter appropriate DNS settings for DHCP configuration as per the network administrator's instructions.

Once done, what is shown in Figure 2-13 should appear on the screen.

| Network Configuration 📃 💠 🗶                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>File Profile Help</u>                                                                                                                                    |

| New Edit Copy Delete Activate Deactivate                                                                                                                    |

| Dev <u>i</u> ces Hard <u>w</u> are D <u>N</u> S H <u>o</u> sts                                                                                              |

| You may configure network devices associated with<br>physical hardware here. Multiple logical devices can be<br>associated with a single piece of hardware. |

| Profile Status Device Nickname Type                                                                                                                         |

| ✔ 🚿 Inactive 🚟 eth1 eth1 🛛 Ethernet                                                                                                                         |

|                                                                                                                                                             |

| Active profile: Common (modified)                                                                                                                           |

UG392\_c2\_13\_120609

#### Figure 2-13: Network Configuration after Adding Interface

Save changes by clicking on the **File** $\rightarrow$ **Save Changes** option. Do not close the network configuration GUI as it will be required later to activate the interface.

2. MAC Address Assignment

Use the ifconfig utility to check the device:

\$ /sbin/ifconfig eth1

Initially the NIC is assigned an Ethernet interface eth1 with a default MAC address of AA:BB:CC:DD:EE:FF.

Make note of the MAC ID assigned to the SP605 board with your kit (Figure 2-14).

UG392\_c2\_14\_120609

Figure 2-14: MAC Address Label on SP605 Board

Open a terminal and navigate to the s6\_pcie\_dma\_ddr3\_gbe folder. Set the MAC address for the Ethernet MAC in the design using the script provided:

\$ ./setmac\_id ethX <SP605\_MAC\_ID>

For the MAC ID shown, the command would be:

\$ ./setmac\_id eth1 00:0A:35:01:EF:1B

After the MAC ID is assigned, try ifconfig again and the assigned MAC ID assigned to the NIC should appear.

Refer to the screen capture in Figure 2-15.

| liveuser@localhost:~/Desktop/s6_pcie_dma_ddr3_gbe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _ + X       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>T</u> erminal <u>T</u> abs <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| <pre>[liveuser@localhost s6_pcie_dma_ddr3_gbe]\$ ifconfig eth1<br/>eth1 Link encap:Ethernet HWaddr AA:BB:CC:DD:EE:FF<br/>BROADCAST MTU:1500 Metric:1<br/>RX packets:0 errors:0 dropped:0 overruns:0 frame:0<br/>TX packets:0 errors:0 dropped:0 overruns:0 carrier:0<br/>collisions:0 txqueuelen:1000<br/>RX bytes:0 (0.0 b) TX bytes:0 (0.0 b)</pre>                                                                                                                                                                                                                                                          | â           |

| <pre>[liveuser@localhost s6_pcie_dma_ddr3_gbe]\$ ./setmac_id ethl 00:0A::<br/>MAC ID 00:0A:35:01:E5:18 assigned to ethl.<br/>Please use Network Configuration GUI to activate ethl.<br/>[liveuser@localhost s6_pcie_dma_ddr3_gbe]\$ ifconfig ethl<br/>ethl Link encap:Ethernet HWaddr 00:0A:35:01:E5:18<br/>inet6 addr: fe80::20a:35ff:fe01:e518/64 Scope:Link<br/>UP BROADCAST RUNNING MTU:1500 Metric:1<br/>RX packets:0 errors:0 dropped:0 overruns:0 frame:0<br/>TX packets:3 errors:0 dropped:0 overruns:0 carrier:0<br/>collisions:0 txqueuelen:1000<br/>RX bytes:0 (0.0 b) TX bytes:238 (238.0 b)</pre> | 35:01:E5:18 |

| [liveuser@localhost s6_pcie_dma_ddr3_gbe]\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | )>          |

UG392\_c2\_15\_120609

#### Figure 2-15: MAC ID Assignment

- 3. Invoke the Network Configuration GUI and activate the interface by clicking on the **Activate** button.

- 4. Invoke the browser and set the browser proxy settings as required for your network (contact your network administrator). Now online service should be available.

## Using Application GUI

This section explains the application GUI provided and various features available.

1. This step involves GUI invocation. Separate steps are defined for a command line user conversant with Linux or for a user preferring button-click operations.

#### Command Line Mode Using Makefile

To compile and invoke the GUI navigate to the s6\_pcie\_dma\_ddr3\_gbe/xpmon folder, follow these steps:

To clean the area.

\$ make clean

To compile the files.

\$ make

To invoke the GUI.

\$./xpmon

#### Command Line Mode Using Executable Scripts

The executable scripts provided in s6\_pcie\_dma\_ddr3\_gbe folder can be used as is on the command line:

\$ ./s6\_trd\_app\_gui

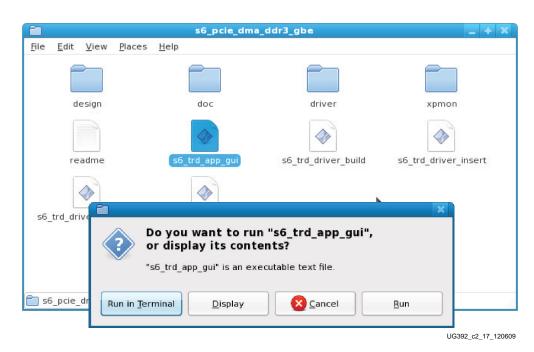

Mouse Click Driven Mode

Double click on **s6\_trd\_app\_gui**. A window prompt appears (Figure 2-16), click on **Run in Terminal** and proceed.

Figure 2-16: Invoking GUI through Script

2. GUI walk-through screen-by-screen:

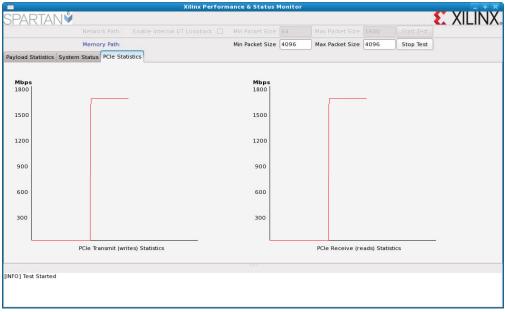

Test Setup and Payload Statistics

This screen defines the various test options provided for the memory path. The packet size for Ethernet can not be controlled by the application GUI as it is managed by the network (TCP/IP) stack.

There is an option to set the minimum and maximum packet size in bytes. While executing the test, the software driver builds packets of random length within the specified range. The range supported is 256-4096 bytes.

The screen in Figure 2-17 plots the data throughput obtained from the various DMA engines.

|                     |                       |                | Xilinx Perforn              | nance & Status I | Monitor |                  |           |              | _ + X  |

|---------------------|-----------------------|----------------|-----------------------------|------------------|---------|------------------|-----------|--------------|--------|

| SPAF                | RTANÝ                 |                |                             |                  |         |                  |           |              | XILINX |

|                     |                       |                | Enable Internal GT Loopback |                  |         | Max Packet Size  |           |              |        |

|                     | Me                    | emory Path:    |                             | Min Packet Size  | 4096    | Max Packet Size  | 4096      | Stop Test    |        |

| Payload S           | Statistics System Sta | Atus PCIe Stat | istics                      |                  |         |                  |           |              |        |

|                     |                       |                |                             |                  |         |                  |           |              |        |

| <b>Mbps</b><br>1000 |                       |                |                             | Mbps<br>1000     |         |                  |           |              |        |

| 800                 |                       |                |                             | 800              |         |                  |           |              |        |

| 600                 |                       |                |                             | 600              |         |                  |           |              |        |

| 400                 |                       |                |                             | 400              |         |                  |           |              |        |

| 200                 |                       |                |                             | 200              |         |                  |           |              |        |

|                     | Net                   | work Path: DM  | A Transmit Statistics       |                  |         | Network Path: DI | MA Receiv | e Statistics |        |

| Mbps                |                       |                |                             | Mbps             |         |                  |           |              |        |

| 1800                |                       | 2              |                             | 1800             |         | _                |           |              |        |

| 1500                |                       |                |                             | 1500             |         |                  |           |              |        |

| 1200                |                       | ļ              |                             | 1200             |         |                  |           |              |        |

| 900                 |                       |                |                             | 900              |         |                  |           |              |        |

| 600                 |                       |                |                             | 600              |         |                  |           |              |        |

| 300                 |                       |                |                             | 300              |         |                  |           |              |        |

|                     | Mer                   | nory Path: DM  | A Transmit Statistics       |                  |         | Memory Path: DI  | MA Receiv | e Statistics |        |

|                     |                       |                |                             |                  |         |                  |           |              |        |

|                     |                       |                |                             |                  |         |                  |           |              |        |

| [INFO] Tes          | t Started             |                |                             |                  |         |                  |           |              |        |

|                     |                       |                |                             |                  |         |                  |           |              |        |

|                     |                       |                |                             |                  |         |                  |           |              |        |

|                     |                       |                |                             |                  |         |                  |           |              |        |

UG392\_c2\_18\_120609

### Figure 2-17: Test Setup and Payload Statistics Screen

#### System Status Screen

This screen gives the status of the PCI Express and DMA engine.

|                                 |                    | X               | linx Perform | nance & Status I | donitor      |                 |       |           |

|---------------------------------|--------------------|-----------------|--------------|------------------|--------------|-----------------|-------|-----------|

|                                 | Network Path:      |                 | oopback 🗌    | Min Packet Size  |              | Max Packet Size |       |           |

|                                 | Memory Path:       |                 |              | Min Packet Size  | 4096         | Max Packet Size | 4096  | Stop Test |

| ad Statistics Syste             | m Status PCIe Stat | tistics         |              |                  |              |                 |       |           |

|                                 |                    |                 |              |                  |              |                 |       |           |

| DMA & Soft                      | ware Status        |                 |              |                  |              |                 |       |           |

| Network Path:                   | Transmit           | Receive         |              | Memo             | ory Path:    | Transmit        | R     | eceive    |

| hroughput (Gbps)                | 0.000              | 0.000           |              | Through          | put (Gbps)   | 1.496           | 1.496 |           |

| A Active Time (ns)              | 1000000000         | 100000000       | 1            | DMA Activ        | e Time (ns)  | 1000000000      | 10000 | 00000     |

| MA Wait Time (ns)               | 1000000000         | 16              | 1            | DMA Wa           | it Time (ns) | 16              | 16    |           |

| BD Errors                       | 0                  | 0               | Ĩ.           | BD               | Errors       | 0               | 0     | i         |

| BD Short Errors                 | 0                  | n/a             |              | BD She           | ort Errors   | 0               | n/a   |           |

| # SW BDs                        | 1023               | 1023            | 1            | # S              | W BDs        | 1023            | 1023  | 1         |

| # SW Buffers                    | 0                  | 1022            | 1            | # SW             | Buffers      | 1000            | 1000  | 1         |

| nterrupts Enabled               |                    | Int GT Loopback |              | Interrup         | ts Enabled   |                 |       |           |

| PCIe Transmit (<br>PCIe Receive |                    | 1.625<br>1.625  | ]            |                  |              |                 |       |           |

| PCIe Status                     |                    |                 |              |                  |              |                 |       |           |

| Link Status                     | Up                 | Vendor ID       | 0x10ee       | MPS              | (bytes)      | 256             |       |           |

| Link Speed                      | 2.5 Gbps           | Device ID       | 0x6011       | MRRS             | (bytes)      | 512             |       |           |

| Link Width                      | ×1                 |                 |              |                  | rrupts       | Legacy          |       |           |

|                                 |                    |                 |              |                  |              |                 |       |           |

|                                 |                    |                 |              |                  |              |                 |       |           |

| Test Started                    |                    |                 |              |                  |              |                 |       |           |

|                                 |                    |                 |              |                  |              |                 |       |           |

|                                 |                    |                 |              |                  |              |                 |       |           |

|                                 |                    |                 |              |                  |              |                 |       |           |

Figure 2-18: System Status Screen

### **Transaction Statistics**

This screen plots the transaction utilization statistics on the PCI Express Transaction interface.

UG392\_c2\_20\_120609

Figure 2-19: Transaction Utilization Statistics

## **Using Various Features**

This section explains the various features of Ethernet configurable via standard tools or software driver macros. These features, when tested with LiveCD, will require the Linux commands given to be preceded by sudo.

## **Ethernet Specific Features**

The Ethernet specific features can be exercised by using command line utilities like ifconfig and ethtool present in Linux.

The Ethernet driver provides functions which are used by ifconfig and ethtool to report information about the NIC. For reporting packet drops due to FCS errors, registers provided by the Ethernet Statistics IP are used.

The ifconfig utility is defined as the interface configurator and is used to configure the kernel-resident network interface and the TCP/IP stack. It is commonly used for setting an interface's IP address and netmask and disabling or enabling a given interface apart from assigning MAC address, and changing maximum transfer unit (MTU) size.

The ethtool utility is used to change or display Ethernet card settings. ethtool with a single argument specifying the device name prints the current setting of the specific device.

More information about ifconfig and ethtool can be obtained from the manual (man) pages on Linux machines.

### **NIC Statistics**

The NIC statistics can be obtained using the ethtool command:

www.xilinx.com

\$ ethtool -S ethX

The error statistics are obtained by reading the registers provided by the Ethernet Statistics IP.

PHY registers (MARVELL PHY registers in case of GMII mode and PCS-PMA registers in case of 1000BASE-X mode) can be read using the following command:

\$ ethtool -d ethX

Certain statistics can also be obtained from the ifconfig command:

\$ ifconfig ethX

#### Autonegotiation

The tri-mode Ethernet MAC (TEMAC) is capable of operating at 10 Mb/s, 100 Mb/s or 1,000 Mb/s speeds. Autonegotiation is the process by which two devices capable of supporting different speeds choose a common speed and establish a link.

The following command results in the information about the Ethernet interface selected, which also lists the speed of operation currently selected.

\$ ethtool -S ethX

To change the speed, use the following command and select a speed. If the device is currently operating at 1000 Mb/s, select the 100 Mb/s or 10 Mb/s options to set a different speed. The speed change should succeed if the link partner supports the newly advertised speed.

\$ ethtool -s ethX speed [10|100|1000]

#### Promiscuous Mode

Enabling promiscuous mode disables address filtering in the TEMAC. This causes the driver to receive all the traffic which increases the CPU load.

The following command can be used to enable promiscuous mode:

\$ ifconfig ethX promisc

The following command disables the promiscuous mode:

\$ ifconfig ethX -promisc

Using a packet sniffer like Wireshark in promiscuous mode puts the driver and in turn the device in promiscuous mode.

## Memory Application Specific Features

This section describes the feature usage specific to the memory path connected to external DDR3 SDRAM through the Spartan-6 Memory Controller block. The packet size feature is available through the GUI.

#### Packet Size

As there are no sidebands to store the start-of-packet and end-of-packet information in DDR3, the design builds packets of a programmed size when sending data to system memory. This packet size can be programmed by writing to a specific register in the memory path user-space register. The application GUI programs this register with an average of the minimum and the maximum packet size value entered by the user.

## Shutting Down the System

The driver modules are automatically removed if the system is rebooted; however, the following steps are advised before shutting down the system for a graceful exit.

1. This step involves removal of the kernel modules. The steps are defined for both a command line user conversant with Linux and for a user preferring button-click operations.

### Command Line Mode using Makefile

To remove the driver, type in the following command line in the terminal in the driver folder.

```

$ make remove

```

### Command Line Mode using Executable Scripts

The executable scripts provided can be run as-is on the command line.

For removal of driver modules:

\$./s6\_trd\_driver\_remove

### Mouse-Click Driven Mode

To compile the driver, navigate to the s6\_pcie\_dma\_ddr3\_gbe folder.

To unload the driver modules (Figure 2-20), click on **s6\_trd\_driver\_remove**.

|                                                      | s6_pcie_dma                                     | _ddr3_gbe                                                    | _ + X                |

|------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------|----------------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>P</u> lace | s <u>H</u> elp                                  |                                                              |                      |

| design                                               | doc                                             | driver                                                       | xpmon                |

| readme                                               | s6_trd_app_gui                                  | s6_trd_driver_build                                          | s6_trd_driver_insert |

| s6_trd_driver_remove                                 | setmac_id                                       | k                                                            |                      |

| s6_pcie_dr                                           | or display its cont<br>"s6_trd_driver_remove" i | n "s6_trd_driver_rem<br>ents?<br>is an executable text file. | eve",                |

Figure 2-20: Executing Driver Removal Script

2. To shut down the system select the **System**→ **Shutdown** option. The LiveCD will be ejected. Follow the onscreen instructions. Any files saved during the LiveCD session are not accessible the next time LiveCD is run.

## **IP Cores with TRD**

The Xilinx LogiCORE IPs required for the TRD are shipped with the TRD. The following cores/netlists are located in the design/coregen\_ip directory:

- s6\_pcie\_ip

- gig\_eth\_pcs\_pma\_ip

- Netlist for FIFOs

The XPS-LL-TEMAC IP is present in the EDK install directory and is used from there.

MIG is generated from the CORE Generator tool.

Open a terminal window (on Linux) or a DOS command (on Windows) and navigate to the design/coregen\_ip directory. Type the following on the command line:

coregen -b mig\_ip.xco -p coregen.cgp

Additionally a golden set of XCO files are also provided under the reference/xco\_files directory so that the cores can be regenerated.

Generating MIG cores overwrites the mig\_ip.xco provided. To regenerate the core, copy the mig\_ip.xco and mig.prj from the design/reference/xco\_files.

Information on the version of IP cores used can be obtained from the readme.txt provided with the design directory.

A node-free hardware evaluation license is shipped with the TRD under the design/license directory.

Start the Xilinx License Manager and click on **Copy License** to install the license provided on your PC. For details on license installation, refer to <u>UG665</u>: *Spartan-6 FPGA Connectivity Kit Getting Started Guide* or <u>http://www.xilinx.com/tools/faq.htm</u>.

## Implementing the Design

This section explains how to implement the design after making certain modifications. The implementation flow is provided in two modes, script based and ProjNav based (ISE software GUI flow).

### Script Based Flow

Implementation scripts for both Linux and Windows operating systems are provided under the design/implement folder.

#### Implementation on Linux

- 1. Navigate to the design/implement/lin folder.

- 2. To generate a design using GMII through a MARVELL PHY, execute the following on a command line:

\$ ./implement\_gmii.sh

To generate a design with a PCS-PMA core in the 1000BASE-X mode, execute the following on a command line:

- \$ ./implement\_1000basex.sh

- 3. After completion of the implementation process, a results folder is created with the bitstream, all the reports, and intermediate implementation results.

### Implementation on Windows

- 1. Navigate to the design/implement/nt folder

- 2. To generate a design using GMII through a MARVELL PHY, double-click on implement\_gmii.bat

- 3. To generate a design with a PCS-PMA core in the 1000BASE-X mode, double-click on implement\_1000basex.bat

After completion of the implementation process, a results folder is created with the bitstream, all the reports, and intermediate implementation results.

## **ProjNav Based Flow**

The Spartan-6 FPGA Connectivity TRD provides files for a GUI-based flow, where designers can view the design hierarchy and source code. Execution of this flow requires a Xilinx ISE tools' installation, where both the XILINX and XILINX\_EDK environment variables are defined.

- To implement a GMII design, navigate to the design/implement/projnav\_flow\_gmii folder.

- To implement a 1000BASE-X design, navigate to the design/implement/projnav\_flow\_1000basex folder.

The scripts for the GMII design flow are in projnav\_gmii.bat and for the 1000BASE-X design flow are in projnav\_1000basex.bat. Execution of these scripts:

- Generates the MIG IP core

- Generates the ISE design tools project files from the Tcl file provided (xise files)

- Opens the ISE software GUI and loads the relevant project

**Note:** Do not manually modify the Tcl or xise files.

On Linux

```

$ ./projnav_gmii.bat

or

$ ./projnav_1000basex.bat

```

On Windows

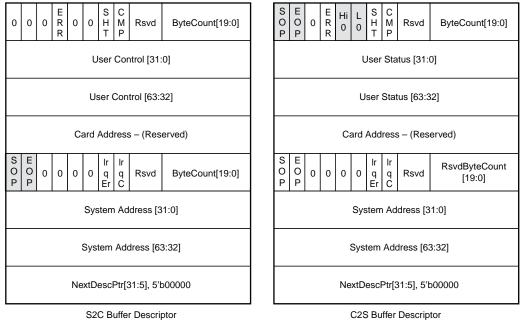

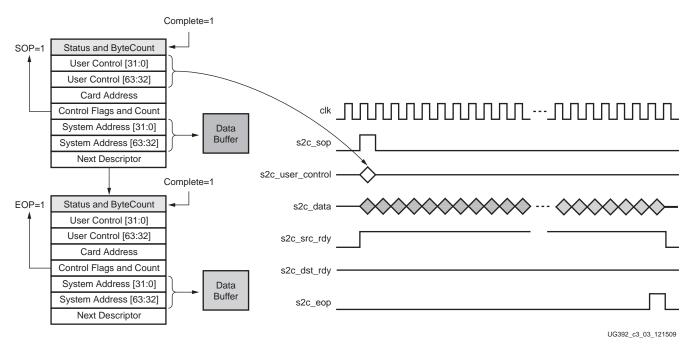

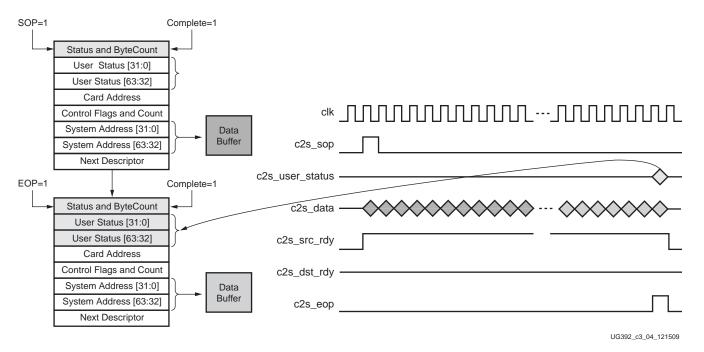

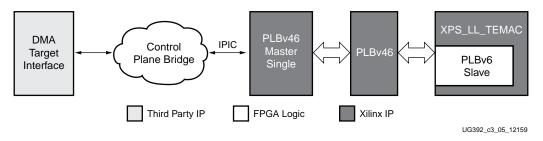

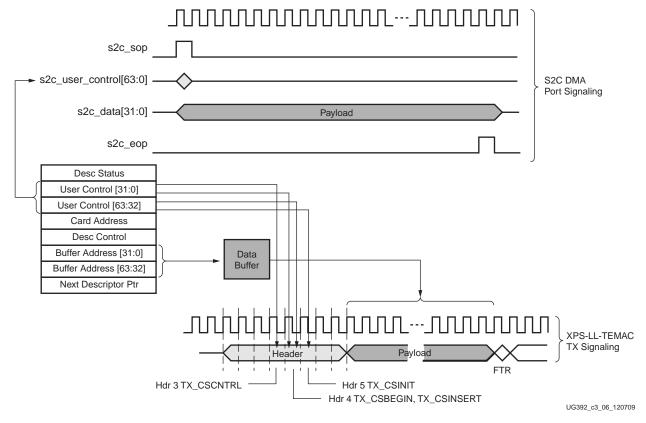

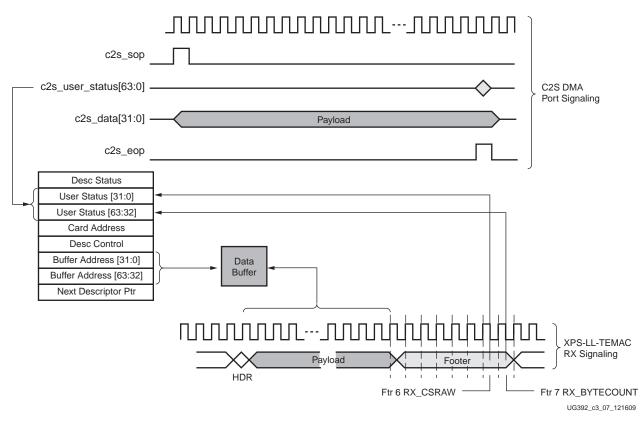

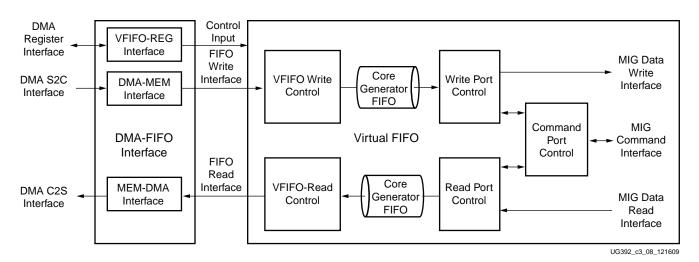

Source the ISE environment and execute the bat file.