# LogiCORE IP 3GPP LTE MIMO Decoder v3.0

PB020 (v3.0) November 18, 2015

**Product Brief**

#### Introduction

The Xilinx® LogiCORE™ IP LTE MIMO Decoder v3.0 implements the uplink MIMO decoding functions for applications following the 3rd Generation Partnership Projects (3GPP); Evolved Universal Radio Access (E-UTRA); Physical Channels and Modulation (Release 11), 3GPP TS 36.211 V11.0.0 (2012-09) specification [Ref 1].

#### **Additional Documentation**

A product guide is available for this core.

Access to this material can be requested by clicking on this registration link:

www.xilinx.com/member/

3gpp\_lte\_mimo\_decoder\_eval/index.htm.

- MMSE MIMO Decoder for spatial multiplexing MIMO systems

- Compliance with 3GPP-LTE specification, AXI4-Stream interface

- Key component of Xilinx LTE Baseband Targeted Design Platform

- High resource efficiency

- Supports four receive and four transmit antennas (4x4 spatial multiplexing MIMO system)

- Supports up to four antennas at the base station

- Supports up to four mobiles with one transmit antenna each, in MU-MIMO mode

- Supports one mobile with up to four transmit antennas in SU-MIMO mode

- Support for receive diversity only mode

- Synchronous clear input; clock enable input

| LogiCORE IP Facts Table                     |                                                                                                    |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------|--|

| Core Specifics                              |                                                                                                    |  |

| Supported<br>Device Family <sup>(1)</sup>   | UltraScale+™ Families<br>UltraScale™ Architecture<br>Zynq®-7030, Zynq-7045<br>Virtex®-7, Kintex®-7 |  |

| Supported User<br>Interfaces                | AXI4-Stream                                                                                        |  |

| Provided with Core                          |                                                                                                    |  |

| Design Files                                | Encrypted RTL                                                                                      |  |

| Example Design                              | Not Provided                                                                                       |  |

| Test Bench                                  | Contact Xilinx Support                                                                             |  |

| Constraints File                            | Not Provided                                                                                       |  |

| Simulation<br>Model                         | VHDL Behavioral<br>VHDL or Verilog Simulation Model<br>Bit Accurate C Model                        |  |

| Tested Design Tools <sup>(2)</sup>          |                                                                                                    |  |

| Design Entry<br>Tools                       | Vivado® Design Suite                                                                               |  |

| Simulation                                  | For supported simulators, see the Xilinx Design Tools: Release Notes Guide.                        |  |

| Synthesis Tools                             | Vivado Synthesis                                                                                   |  |

| Support                                     |                                                                                                    |  |

| Provided by Xilinx @ www.xilinx.com/support |                                                                                                    |  |

#### Notes:

- For a complete list of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# **Applications**

- Base station applications implementing eNodeB following the LTE specification [Ref 1]. The LTE MIMO Decoder v3.0 can perform the MMSE MIMO decoding function for uplink reception.

- Applications that can use a spatial multiplexing MMSE MIMO decoder that meet the timing and latency constraints of the LTE specification [Ref 1].

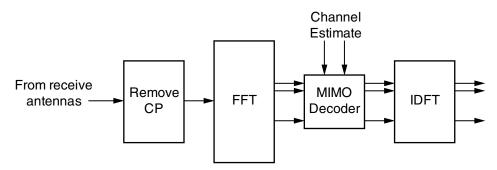

The LTE MIMO Decoder v3.0 is designed to fulfill the demanding processing requirements of MIMO decode in evolved 3GPP-LTE compliant base stations. A high level block diagram of the MIMO decoder and its location in the uplink system is shown in Figure 1. It is an MMSE MIMO decoder for spatial multiplexing MU-MIMO or SU-MIMO systems and is also optimized for receive diversity only systems. The core has been designed to meet the 3GPP-LTE timing and latency constraints.

Figure 1: Block Diagram of a 3GPP-LTE Uplink Receiver

#### References

- 1. 3rd Generation Partnership Projects (3GPP); Evolved Universal Radio Access (E-UTRA); Physical Channels and Modulation (Release 11), 3GPP TS 36.211 V11.0.0 (2012-09)

- 2. LogiCORE IP 3GPP LTE MIMO Decoder v3.0 Product Guide (PG123), registration required.

- 3. Vivado AXI Reference Guide (UG1037)

# **Technical Support**

Xilinx provides technical support at <a href="www.xilinx.com/support">www.xilinx.com/support</a> for this LogiCORE IP product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices that are not defined in the documentation, if customized beyond that allowed in the product documentation, or if changes are made to any section of the design labeled DO NOT MODIFY.

For the master Answer Record related to the 3GPP LTE MIMO Decoder core, see AR: <u>54468.</u>

# **Licensing and Ordering Information**

This Xilinx LogiCORE IP module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information on pricing and availability.

To evaluate this core in hardware, generate an evaluation license, which can be accessed from the Xilinx IP Evaluation page. After purchasing the core, you will receive instructions for registering and generating a full license. The full license can be requested and installed from the Xilinx IP Center for use with the Vivado Design Suite.

For more information, visit the <u>3GPP LTE MIMO Decoder product page</u>.

Information about other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

# **Revision History**

The following table shows the revision history for this document:

| Date       | Version | Revision                                               |

|------------|---------|--------------------------------------------------------|

| 11/18/2015 | 3.0     | UltraScale+ device support added.                      |

| 06/04/2014 | 3.0     | Initial Xilinx release. This document replaces XMP040. |

# **Please Read: Important Legal Notices**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of Xilinx's limited warranty, please refer to Xilinx's Terms of Sale which can be viewed at <a href="http://www.xilinx.com/legal.htm#tos">http://www.xilinx.com/legal.htm#tos</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in such critical applications, please refer to Xilinx's Terms of Sale which can be viewed at <a href="http://www.xilinx.com/legal.htm#tos">http://www.xilinx.com/legal.htm#tos</a>.

#### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Development Software category:

Click to view products by Xilinx manufacturer:

Other Similar products are found below:

RAPPID-567XFSW SRP004001-01 SW163052 SYSWINEV21 Core429-SA WS01NCTF1E W128E13 SW89CN0-ZCC IPS-EMBEDDED IP-UART-16550 MPROG-PRO535E AFLCF-08-LX-CE060-R21 WS02-CFSC1-EV3-UP SYSMAC-STUDIO-EIPCPLR LIB-PL-PC-N-1YR-DISKID LIB-PL-A-F SW006026-COV 1120270005 1120270006 MIKROBASIC PRO FOR FT90X (USB DONGLE) MIKROC PRO FOR FT90X (USB DONGLE) MIKROC PRO FOR PIC (USB DONGLE LICENSE) MIKROBASIC PRO FOR AVR (USB DONGLE LICEN MIKROBASIC PRO FOR FT90X MIKROC PRO FOR DSPIC30/33 (USB DONGLE LI MIKROPASCAL PRO FOR ARM (USB DONGLE LICE MIKROPASCAL PRO FOR FT90X MIKROPASCAL PRO FOR FT90X (USB DONGLE) MIKROPASCAL PRO FOR PIC32 (USB DONGLE LI SW006021-2H ATATMELSTUDIO 2400573 2702579 2988609 2702546 SW006022-DGL 2400303 2701356 VDSP-21XX-PCFLOAT VDSP-BLKFN-PC-FULL 88970111 DG-ACC-NET-CD 55195101-102 SW1A-W1C MDK-ARM PCI-EXP1-E3-US PCI-T32-E3-US SW006021-2NH SW006021-1H SW006021-2