# LogiCORE IP Endpoint v3.7 for PCI Express®

DS506 April 19, 2010 Product Specification

### Introduction

The LogiCORE<sup>TM</sup> Endpoint for PCI Express® offers high-bandwidth, scalable, and reliable serial interconnect intellectual property building blocks for use with Virtex®-4, and Virtex-5 devices. All cores in the solution (1-lane, 4-lane, and 8-lane) are protocol-compliant and electrically compatible with the *PCI Express Base Specification v1.1*.

PCI Express (PCIe®) offers a serial architecture that alleviates some of the limitations of parallel bus architectures by using clock data recovery (CDR) and differential signaling. Using CDR (as opposed to source synchronous clocking) lowers pin count, enables superior frequency scalability, and makes data synchronization easier. The layered architecture of PCIe provides for future attachment to copper, optical, or emerging physical signaling media. PCIe technology, adopted by PCI-SIG as the next generation PCI, is backward-compatible to the existing PCI software model.

With higher bandwidth per pin, low overhead, low latency, reduced signal integrity issues, and CDR architecture, the Xilinx Endpoint solution for PCI Express sets the industry standard for a high-performance, costefficient third-generation I/O solution.

The Xilinx Endpoint solution for PCIe is compatible with industry-standard application form factors such as the PCI Express Card Electromechanical (CEM) v1.1 and the PCI Industrial Computer Manufacturers Group (PICMG) 3.4 specifications.

The Endpoint solutions for PCIe are defined in the following table.

| Product                | FPGA Support             | Data Path<br>Width |

|------------------------|--------------------------|--------------------|

| 1-lane 64-bit Endpoint | Virtex-4 FX              | 64                 |

| 4-lane 64-bit Endpoint | Virtex-4 FX              | 64                 |

| 8-lane 64-bit Endpoint | Virtex-5 LX, Virtex-4 FX | 64                 |

| 1-lane 32-bit Endpoint | Virtex-5 LX, Virtex-4 FX | 32                 |

| 4-lane 32-bit Endpoint | Virtex-5 LX, Virtex-4 FX | 32                 |

| LogiCORE Facts                               |                                                             |                                                                                                                                   |                    |                                        |                |  |  |

|----------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------|----------------|--|--|

| Core Specifics                               |                                                             |                                                                                                                                   |                    |                                        |                |  |  |

| Device<br>Families <sup>(1)</sup>            | Virtex-4 FX <sup>(2)</sup> , Virtex-5 LX <sup>(2),(3)</sup> |                                                                                                                                   |                    |                                        |                |  |  |

|                                              | 1-lane 64-                                                  | bit Endpoint                                                                                                                      | XC4VFX20 -10       |                                        |                |  |  |

| Minimum                                      | 4-lane 64-                                                  | bit Endpoint                                                                                                                      |                    | XC                                     | 4VFX20 -10     |  |  |

| Device<br>Require-                           | 8-lane 64-                                                  | bit Endpoint                                                                                                                      | XC4\               | /FX60 -11/XC                           | 5VLX50T-1      |  |  |

| ment                                         | 1-lane 32-                                                  | bit Endpoint                                                                                                                      | XC4\               | /FX20 -10/XC                           | 5VLX50T-1      |  |  |

|                                              | 4-lane 32-                                                  | bit Endpoint                                                                                                                      | XC4\               | /FX20 -11/XC                           | 5VLX50T-1      |  |  |

|                                              | Endpoin                                                     | t (EP) Product                                                                                                                    | I/O <sup>(4)</sup> | LUT                                    | FF             |  |  |

|                                              | 1-lane 64-                                                  | bit Endpoint                                                                                                                      | 1 (5)              | 7800                                   | 7000           |  |  |

|                                              | 4-lane 64-                                                  | bit Endpoint                                                                                                                      | 4                  | 10550                                  | 9200           |  |  |

|                                              |                                                             | bit EP Virtex-4<br>bit EP Virtex-5                                                                                                | 8                  | 13500<br>11400                         | 12000<br>11200 |  |  |

|                                              |                                                             | bit EP Virtex-4<br>bit EP Virtex-5                                                                                                | 1 <sup>(5)</sup>   | 6300<br>5100                           | 5100<br>4700   |  |  |

|                                              |                                                             | bit EP Virtex-4<br>bit EP Virtex-5                                                                                                | 4                  | 8700<br>7200                           | 7000<br>6700   |  |  |

| Resources<br>Used                            |                                                             |                                                                                                                                   | Block<br>RAM       | CMPS <sup>(6)</sup><br># Tx<br>Buffers | CMPS           |  |  |

|                                              | 1-lane 64-                                                  | bit Endpoint                                                                                                                      | 12                 | 16                                     | 512            |  |  |

|                                              | 4-lane 64-                                                  | bit Endpoint                                                                                                                      | 12                 | 16                                     | 512            |  |  |

|                                              |                                                             | bit EP Virtex-4<br>bit EP Virtex-5                                                                                                | 12<br>6            | 32                                     | 256            |  |  |

|                                              |                                                             | bit EP Virtex-4<br>bit EP Virtex-5                                                                                                | 8<br>4             | 8                                      | 512            |  |  |

|                                              |                                                             | bit EP Virtex-4<br>bit EP Virtex-5                                                                                                | 12<br>6            | 16                                     | 512            |  |  |

| Special Feat                                 | ures                                                        |                                                                                                                                   |                    | cket IO™ Tran<br>ock Manager,          |                |  |  |

|                                              |                                                             | Provided wit                                                                                                                      | th Core            |                                        |                |  |  |

| Documentation                                | on                                                          | Product                                                                                                                           |                    | on, Getting Sta<br>de, Instantiation   |                |  |  |

| Design Files                                 |                                                             | Verilog® and VHDL Simulation Models<br>Xilinx Generic Netlist Format (ngo netlist)<br>Verilog Example Test Bench & Example Design |                    |                                        |                |  |  |

| Constraints F                                | ile                                                         |                                                                                                                                   | Us                 | er Constraints                         | s File (UCF)   |  |  |

|                                              |                                                             | Design Tool                                                                                                                       | Support            |                                        |                |  |  |

| HDL Synthes                                  | HDL Synthesis Tool Synplicity® Synplify®, Xilinx XST        |                                                                                                                                   |                    |                                        |                |  |  |

| Implementati                                 | Implementation Tools Xilinx ISE® v12.1                      |                                                                                                                                   |                    |                                        |                |  |  |

| Verification Tools<br>(SWIFT-compliant       |                                                             | Cadence™ Incisive Enterprise Simulator (IES) v9.2<br>and above,<br>Synopsys® VCS and VCS MX 2009.12 and above                     |                    |                                        |                |  |  |

| , Mentor Graphics® ModelSim® v6.5c and above |                                                             |                                                                                                                                   |                    |                                        |                |  |  |

| Provided by 2                                | Xilinx, Inc. @                                              | Suppo<br>www.xilinx.c                                                                                                             |                    | ort                                    |                |  |  |

- For the complete list of supported devices, see the 12.1 release notes for this

core.

- Virtex-4 and Virtex-5 solutions require the latest production silicon stepping and are pending hardware validation. The Xilinx LogiCORE warranty does not include production usage with engineering sample silicon (ES).

- 3. XC5VLX50T, XC5VLX110T, and XC5VLX330T are supported.

- RocketlO Multi-Gigabit Transceiver (MGT) for Virtex-4, RocketlO GTP Transceiver for Virtex-5.

- 5. In Virtex-4 and Virtex-5 devices, the 1-lane Endpoint core consumes an entire RocketlO transceiver pair. One RocketlO transceiver tile is used for lane 0: the other is unused and tied off inside the core.

- 6. CMPS: Capability Maximum Payload Size.

© 2002–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG.

#### **Features**

- High-performance, highly flexible, scalable, and reliable, general purpose I/O solution

- ◆ Compliant with the *PCI Express Base Specification v1.1*

- Compatible with conventional PCI software model

- Incorporates Xilinx Smart-IP™ technology to guarantee critical timing

- Uses embedded RocketIO<sup>TM</sup> transceivers to achieve high-transceiver capability

- ♦ 2.5 Gbps line speed

- Supports 1-lane, 4-lane, and 8-lane operation

- Elastic buffers and clock compensation

- Automatic clock data recovery

- 8B/10B encode and decode

- Offers standardized user interface

- Easy-to-use packet-based protocol

- ♦ Full-duplex communication

- Back-to-back transactions enable greater link bandwidth utilization

- Supports flow control of data and discontinuation of an in-process transaction in transmit direction

- Supports flow control of data in receive direction

- Support for automatic handling of error forwarded packets

- Supports removal of corrupted packets for error detection and recovery

- Compliant with PCI/PCI-Express power management functions

- Supports a maximum transaction payload of up to 512 bytes

- Bandwidth scalability with frequency and/or interconnect width

- Fully compliant with PCI Express transaction ordering rules

- Design verified using a Xilinx proprietary test bench

# **Applications**

The Endpoint for PCI Express core architecture enables a broad range of computing and communications target applications, emphasizing performance, cost, scalability, feature extensibility and mission-critical reliability. Typical applications include

www.xilinx.com

- Data communications networks

- Telecommunications networks

- Broadband wired and wireless applications

- Cross-connects

- Network interface cards

- Chip-to-chip and backplane interconnect

- Crossbar switches

- Wireless base stations

# **Functional Description**

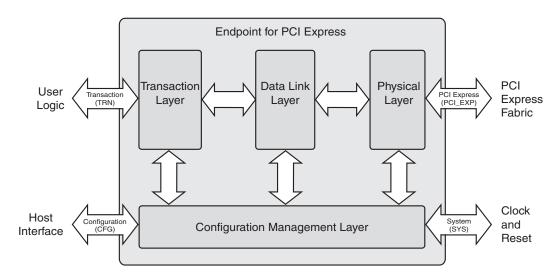

The Endpoint cores for PCI Express are organized into four main modules based on the three discrete logical layers defined by the *PCI Express Base Specification*. The four logic modules, which manage all the system-level functions, include the following:

- Physical Layer Module (PLM)

- Data Link Layer Module (LLM)

- Transaction Layer Module (TLM)

- Configuration Management Module (CMM)

Each module is further partitioned into the Receive and the Transmit sections. The Receive section processes the inbound information, and the Transmit section processes the outbound information. Figure 1 illustrates the main modules interfacing with one another and the user application using the following set of four interfaces:

- System interface (SYS)

- PCI Express interface (PCI EXP)

- Configuration interface (CFG)

- Transaction interface (TRN)

Figure 1: Endpoint Top-level Functional Blocks and Interfaces

The core allows the use of packets to exchange information between modules. Packets are formed in the Transaction and Data Link Layers to carry information from the transmitting component to the receiving component. Necessary information is added to the packet being transmitted, which is required to handle the packet at specific layers. At the receiving end, each layer of the receiving element processes the incoming packet, strips the relevant information and forwards the packet to the next layer. As a result, the received packets are transformed from their Physical Layer representation to their Data Link Layer representation and Transaction Layer representation.

The primary logic modules comprising the Endpoint core for PCI Express and their interfaces are described in the sections that follow.

## **Logic Modules**

The logic modules handle the functionality related to each of the layers defined by the *PCI Express Base Specification*. The functions of these modules include

- Generating and processing of TLPs

- Flow-control management

- Initialization and power management functions

- Data protection

- Error checking and retry functions

- Physical link interface initialization

- Maintenance and status tracking

- Serialization, de-serialization and other circuitry for interface operation

Each of the logic models, introduced in the "Functional Description," page 3, are defined in the following sections.

### **Physical Layer Module**

The Physical Layer exchanges information with the Data Link Layer in an implementation-specific format. This layer is responsible for converting information received from the Data Link Layer into an appropriate serialized format and transmitting it across the PCI Express Link at a frequency and width compatible with the remote device.

#### **Data Link Layer Module**

The Data Link Layer acts as an intermediate stage between the Transaction Layer and the Physical Layer. Its primary responsibility is to provide a reliable mechanism for the exchange of Transaction Layer Packets (TLPs) between the two Components on a Link.

Services provided by the Data Link Layer include data exchange (TLPs), error detection and recovery, initialization services and the generation and consumption of Data Link Layer Packets (DLLPs). DLLPs are the mechanism used to transfer information between Data Link Layers of two directly connected Components on the Link. They are used for conveying information such as Flow Control and TLP acknowledgments.

#### Transaction Layer Module

4

The upper layer of the PCI Express architecture is the Transaction Layer. The primary goal of the Transaction Layer is the assembly and disassembly of Transaction Layer Packets (TLPs). Packets are formed in the Transaction and Data Link Layers to carry the information from the transmitting component to the receiving component. TLPs are used to communicate transactions, such as read and write, as well as certain types of events. To maximize the efficiency of communication between devices, the Transaction Layer implements a pipelined, full split-transaction protocol, manages credit-based flow control of TLPs, and offers optional support for data poisoning.

#### **Configuration Management Module**

The Configuration Management Module supports generation and reception of System Management Messages by communicating with the other modules and the user application. This module contains the device configuration space and other system functions. The CMM implements PCI/PCI-Express power management capabilities, and facilitates exchange of power management messages, including

support for PME event generation. Also implemented are user-triggered error message generation and user-read access to the device configuration space.

# **PCI Configuration Space**

The PCI Configuration Space block provides a standard Type 0 configuration space, consisting of a 64-byte, Type 0 configuration space header with an additional 192 bytes used for extended capabilities. Four extended capabilities are provided in the interface:

- Express capability structure

- Power management capability structure

- Message signaled interrupt capability structure

- Device serial number extended capability structure

These capabilities, together with the standard Type 0 header shown in Table 1, support software driven *Plug and Play* initialization and configuration.

Table 1: PCI Configuration Space Header

| 31                                     | 16                                                                 | 15                  |           | 0    |

|----------------------------------------|--------------------------------------------------------------------|---------------------|-----------|------|

| Devi                                   | Device ID                                                          |                     | Vendor ID |      |

| Sta                                    | Status                                                             |                     | Command   |      |

|                                        | Class Code                                                         |                     | Rev ID    | 008h |

| BIST                                   | Header                                                             | Lat Timer           | Cache Ln  | 00Ch |

|                                        | Base Addres                                                        | ss Register 0       |           | 010h |

|                                        | Base Addres                                                        | ss Register 1       |           | 014h |

|                                        | Base Addres                                                        | ss Register 2       |           | 018h |

|                                        | Base Addres                                                        | ss Register 3       |           | 01Ch |

|                                        | Base Addres                                                        | ss Register 4       |           | 020h |

|                                        | Base Addres                                                        | ss Register 5       |           | 024h |

|                                        | Cardbus C                                                          | CIS Pointer         |           | 028h |

| Subsy                                  | stem ID                                                            | Subsystem           | Vendor ID | 02Ch |

|                                        | Expansion ROM                                                      | M Base Address      |           | 030h |

|                                        | Reserved                                                           |                     | CapPtr    | 034h |

|                                        | Rese                                                               | erved               |           | 038h |

| Max Lat                                | Min Gnt                                                            | Intr Pin            | Intr Line | 03Ch |

| РМ Са                                  | pability                                                           | NxtCap              | РМ Сар    | 040h |

| Data                                   | BSE                                                                | PMC                 | CSR       | 044h |

| MSI                                    | Control                                                            | NxtCap              | MSI Cap   | 048h |

|                                        | Message Add                                                        | dress (Lower)       |           | 04Ch |

|                                        | Message Add                                                        | dress (Upper)       |           | 050h |

| Rese                                   | erved                                                              | Message Data        |           | 054h |

| PE Ca                                  | pability                                                           | NxtCap              | PE Cap    | 058h |

|                                        | PCI Express De                                                     | vice Capabilities   |           | 05Ch |

| Device                                 | Status                                                             | Device Control      |           | 060h |

|                                        | PCI Express Li                                                     | ink Capabilities    |           | 064h |

| Link                                   | Status                                                             | Link Control        |           | 068h |

|                                        | Reserved Legacy Configuration Space (Returns 0x00000000)           |                     |           |      |

| Next Cap                               | Capability                                                         | PCI Exp. Capability |           | 100h |

| PCI Express Device Serial Number (1st) |                                                                    |                     |           | 104h |

|                                        | PCI Express Device Serial Number (2nd)                             |                     |           |      |

|                                        | Reserved Extended Configuration Space (Returns Completion with UR) |                     |           |      |

# **Endpoint Interfaces**

The Endpoint core includes top-level signal interfaces that have sub-groups for the receive direction, transmit direction, and the signals common to both directions.

## **System Interface**

Table 2 defines the System (SYS) interface signals. The system reset (sys\_reset\_n) signal is an asynchronous input (active low). The assertion of this signal causes a hard reset of the entire endpoint, including the Rocket IO transceiver. In the CEM add-in card form factor, the PERST# signal should be connected to the sys\_reset\_n signal. For form factors where no sideband reset is available, it must be generated locally.

The system clock signal (sys\_clk) is used to clock the entire endpoint, including the Rocket IO transceiver. The system clock is used to clock logic that coordinates the hardware reset process. This clock must be a free-running clock that is not a DCM output. See the "Digital Design Considerations" chapter of the Rocket I/O Transceiver User Guide for more information. Additional information about core clocking consideration can be found in Answer Record 20600.

Table 2: System Interface Signals

| Name        | Direction | Description                                                                                                                                         |          |          |  |  |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--|--|

| sys_reset_n | Input     | <b>System Reset</b> : An asynchronous input (active low) signal reset from the root complex/system that puts the endpoint in a known initial state. |          |          |  |  |

|             |           | <b>Reference Clock</b> : The reference clock for the PCI Express Endpoint solutions.                                                                |          |          |  |  |

|             |           | Product                                                                                                                                             | Virtex-4 | Virtex-5 |  |  |

|             |           | 1-lane 64-bit Endpoint                                                                                                                              | 250 MHz  | N/A      |  |  |

| sys_clk     | Input     | 4-lane 64-bit Endpoint                                                                                                                              | 250 MHz  | N/A      |  |  |

|             |           | 8-lane 32-bit Endpoint                                                                                                                              | 250 MHz  | 100 MHz  |  |  |

|             |           | 1-lane 32-bit Endpoint                                                                                                                              | 250 MHz  | 100 MHz  |  |  |

|             |           | 4-lane 32-bit Endpoint                                                                                                                              | 250 MHz  | 100 MHz  |  |  |

## **PCI Express Interface**

The PCI Express (PCI\_EXP) interface consists of differential transmit and receive pairs organized in multiple lanes. A PCI Express lane consists of a pair of transmit differential signals (pci\_exp\_txp, pci\_exp\_txn) and a pair of receive differential signals (pci\_exp\_rxp, pci\_exp\_rxn). The 1-lane core supports only lane 0, while the 4-lane core supports lanes 0-3, and the 8-lane core support lanes 0-7. Table 3 and Table 4 define the transmit and receive signals of the PCI\_EXP interface signals for 1- and 4-lane cores, respectively. Table 5 describes the signals for the 8-lane core.

Table 3: PCI Express Interface Signals for the 1-lane Endpoint Core

| Lane<br>Number | Name         | Direction | Description                                                     |

|----------------|--------------|-----------|-----------------------------------------------------------------|

| 0              | pci_exp_txp0 | Output    | PCI Express Transmit Positive: Serial Differential Output 0 (+) |

| 0              | pci_exp_txn0 | Output    | PCI Express Transmit Negative: Serial Differential Output 0 (-) |

| 0              | pci_exp_rxp0 | Input     | PCI Express Receive Positive: Serial Differential Input 0 (+)   |

| 0              | pci_exp_rxn0 | Input     | PCI Express Receive Negative: Serial Differential Input 0 (-)   |

Table 4: PCI Express Interface Signals for the 4-lane Endpoint Core

| Lane<br>Number | Name         | Direction | Description                                                     |

|----------------|--------------|-----------|-----------------------------------------------------------------|

| 0              | pci_exp_txp0 | Output    | PCI Express Transmit Positive: Serial Differential Output 0 (+) |

| 0              | pci_exp_txn0 | Output    | PCI Express Transmit Negative: Serial Differential Output 0 (-) |

| 0              | pci_exp_rxp0 | Input     | PCI Express Receive Positive: Serial Differential Input 0 (+)   |

| 0              | pci_exp_rxn0 | Input     | PCI Express Receive Negative: Serial Differential Input 0 (-)   |

| 1              | pci_exp_txp1 | Output    | PCI Express Transmit Positive: Serial Differential Output 1 (+) |

| 1              | pci_exp_txn1 | Output    | PCI Express Transmit Negative: Serial Differential Output 1 (-) |

| 1              | pci_exp_rxp1 | Input     | PCI Express Receive Positive: Serial Differential Input 1 (+)   |

| 1              | pci_exp_rxn1 | Input     | PCI Express Receive Negative: Serial Differential Input 1 (-)   |

| 2              | pci_exp_txp2 | Output    | PCI Express Transmit Positive: Serial Differential Output 2 (+) |

| 2              | pci_exp_txn2 | Output    | PCI Express Transmit Negative: Serial Differential Output 2 (-) |

| 2              | pci_exp_rxp2 | Input     | PCI Express Receive Positive: Serial Differential Input 2 (+)   |

| 2              | pci_exp_rxn2 | Input     | PCI Express Receive Negative: Serial Differential Input 2 (–)   |

| 3              | pci_exp_txp3 | Output    | PCI Express Transmit Positive: Serial Differential Output 3 (+) |

| 3              | pci_exp_txn3 | Output    | PCI Express Transmit Negative: Serial Differential Output 3 (-) |

| 3              | pci_exp_rxp3 | Input     | PCI Express Receive Positive: Serial Differential Input 3 (+)   |

| 3              | pci_exp_rxn3 | Input     | PCI Express Receive Negative: Serial Differential Input 3 (-)   |

Table 5: PCI Express Interface Signals for the 8-lane Endpoint Core

| Lane<br>Number | Name         | Direction | Description                                                     |

|----------------|--------------|-----------|-----------------------------------------------------------------|

| 0              | pci_exp_txp0 | Output    | PCI Express Transmit Positive: Serial Differential Output 0 (+) |

| 0              | pci_exp_txn0 | Output    | PCI Express Transmit Negative: Serial Differential Output 0 (-) |

| 0              | pci_exp_rxp0 | Input     | PCI Express Receive Positive: Serial Differential Input 0 (+)   |

| 0              | pci_exp_rxn0 | Input     | PCI Express Receive Negative: Serial Differential Input 0 (–)   |

| 1              | pci_exp_txp1 | Output    | PCI Express Transmit Positive: Serial Differential Output 1 (+) |

| 1              | pci_exp_txn1 | Output    | PCI Express Transmit Negative: Serial Differential Output 1 (–) |

| 1              | pci_exp_rxp1 | Input     | PCI Express Receive Positive: Serial Differential Input 1 (+)   |

| 1              | pci_exp_rxn1 | Input     | PCI Express Receive Negative: Serial Differential Input 1 (-)   |

| 2              | pci_exp_txp2 | Output    | PCI Express Transmit Positive: Serial Differential Output 2 (+) |

| 2              | pci_exp_txn2 | Output    | PCI Express Transmit Negative: Serial Differential Output 2 (-) |

| 2              | pci_exp_rxp2 | Input     | PCI Express Receive Positive: Serial Differential Input 2 (+)   |

| 2              | pci_exp_rxn2 | Input     | PCI Express Receive Negative: Serial Differential Input 2 (-)   |

| 3              | pci_exp_txp3 | Output    | PCI Express Transmit Positive: Serial Differential Output 3 (+) |

| 3              | pci_exp_txn3 | Output    | PCI Express Transmit Negative: Serial Differential Output 3 (-) |

| 3              | pci_exp_rxp3 | Input     | PCI Express Receive Positive: Serial Differential Input 3 (+)   |

| 3              | pci_exp_rxn3 | Input     | PCI Express Receive Negative: Serial Differential Input 3 (-)   |

| 4              | pci_exp_txp4 | Output    | PCI Express Transmit Positive: Serial Differential Output 4 (+) |

| 4              | pci_exp_txn4 | Output    | PCI Express Transmit Negative: Serial Differential Output 4 (–) |

| 4              | pci_exp_rxp4 | Input     | PCI Express Receive Positive: Serial Differential Input 4 (+)   |

| 4              | pci_exp_rxn4 | Input     | PCI Express Receive Negative: Serial Differential Input 4 (-)   |

| 5              | pci_exp_txp5 | Output    | PCI Express Transmit Positive: Serial Differential Output 5 (+) |

| 5              | pci_exp_txn5 | Output    | PCI Express Transmit Negative: Serial Differential Output 5 (-) |

| 5              | pci_exp_rxp5 | Input     | PCI Express Receive Positive: Serial Differential Input 5 (+)   |

| 5              | pci_exp_rxn5 | Input     | PCI Express Receive Negative: Serial Differential Input 5 (-)   |

| 6              | pci_exp_txp6 | Output    | PCI Express Transmit Positive: Serial Differential Output 6 (+) |

| 6              | pci_exp_txn6 | Output    | PCI Express Transmit Negative: Serial Differential Output 6 (-) |

| 6              | pci_exp_rxp6 | Input     | PCI Express Receive Positive: Serial Differential Input 6 (+)   |

| 6              | pci_exp_rxn6 | Input     | PCI Express Receive Negative: Serial Differential Input 6 (-)   |

| 7              | pci_exp_txp7 | Output    | PCI Express Transmit Positive: Serial Differential Output 7 (+) |

| 7              | pci_exp_txn7 | Output    | PCI Express Transmit Negative: Serial Differential Output 7 (-) |

| 7              | pci_exp_rxp7 | Input     | PCI Express Receive Positive: Serial Differential Input 7 (+)   |

| 7              | pci_exp_rxn7 | Input     | PCI Express Receive Negative: Serial Differential Input 7 (-)   |

# **Configuration Interface**

The Configuration (CFG) interface provides a mechanism for the user design to inspect the state of the Endpoint core's PCI Express configuration space. The user provides a 10-bit configuration address that selects one of the 1024 configuration space double word (DWORD) registers. The endpoint then returns

the state of the selected register over the 32-bit data output port. Table 6 describes the configuration interface signals.

Table 6: Configuration Interface Signals

| Name                        | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cfg_do[31:0]                | Output    | <b>Configuration Data Out</b> : A 32-bit data output port used to obtain read data from the configuration space inside the core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| cfg_rd_wr_done_n            | Output    | Configuration Read Write Done: Active-low, read-write done signal indicates a successful completion of the user configuration register access operation.  For a user configuration register read operation, the signal validates the cfg_do[31:0] data-bus value.  For a user configuration register write operation, the                                                                                                                                                                                                                                                                                     |

|                             |           | assertion signals completion of a successful write operation.  Not supported for write operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| cfg_di[31:0]                | Input     | Configuration Data In: A 32-bit data input port used to provide write data to the configuration space inside the core. Unimplemented, reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| cfg_dwaddr[9:0]             | Input     | Configuration DWORD Address: A 10-bit address input port used to provide a configuration register DWORD address during configuration register accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| cfg_interrupt_n             | Input     | Configuration Interrupt: Active-low interrupt-request signal. The User Application may assert this to cause the selected interrupt message-type to be transmitted by the core. The signal should be held low until cfg_interrupt_rdy_n is asserted.                                                                                                                                                                                                                                                                                                                                                           |

| cfg_interrupt_rdy_n         | Output    | Configuration Interrupt Ready: Active-low interrupt grant signal. The simultaneous assertion of cfg_interrupt_rdy_n and cfg_interrupt_n indicates that the core has successfully transmitted the requested interrupt message.                                                                                                                                                                                                                                                                                                                                                                                 |

| cfg_interrupt_mmenable[2:0] | Output    | Configuration Interrupt Multiple Message Enable: This is the value of the Multiple Message Enable field. Values range from 000b to 101b. A value of 000b indicates that single vector MSI is enabled, while other values indicate the number of bits that may be used for multi-vector MSI.                                                                                                                                                                                                                                                                                                                   |

| cfg_interrupt_msienable     | Output    | Configuration Interrupt MSI Enabled: Indicates that the Message Signaling Interrupt (MSI) messaging is enabled. If 0, then only Legacy (INTx) interrupts may be sent.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| cfg_interrupt_di[7:0]       | Input     | Configuration Interrupt Data In: For Message Signaling Interrupts (MSI), the portion of the Message Data that the endpoint must drive to indicate MSI vector number, if Multi-Vector Interrupts are enabled. The value indicated by cfg_interrupt_mmenable[2:0] determines the number of lower-order bits of Message Data that the endpoint provides; the remaining upper bits of cfg_interrupt_di[7:0] are not used. For Single-Vector Interrupts, cfg_interrupt_di[7:0] is not used. For Legacy interrupt messages (Assert_INTx, Deassert_INTx), the following list defines the type of message to be sent: |

|                             |           | Value Legacy Interrupt  00h INTA 01h INTB 02h INTC 03h INTD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| cfg_interrupt_do[7:0]       | Output    | Configuration Interrupt Data Out: The value of the lowest 8 bits of the Message Data field in the endpoint's MSI capability structure. This value is used in conjunction with cfg_interrupt_mmenable[2:0] to drive cfg_interrupt_di[7:0].                                                                                                                                                                                                                                                                                                                                                                     |

Table 6: Configuration Interface Signals (Cont'd)

| Name                         | Direction | Description                                                                                                                                                                                                                                                                                         |

|------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cfg_interrupt_assert_n       | Input     | Configuration Legacy Interrupt Assert/Deassert Select: Selects between Assert and Deassert messages for Legacy interrupts when cfg_interrupt_n is asserted. Not used for MSI interrupts.  Value  Message Type  0  Assert 1  Deassert                                                                |

| cfg_turnoff_ok_n             | Input     | <b>Configuration Turnoff OK</b> : The active low power turn-off ready signal. The user application can assert this to notify the endpoint that it is safe for power to be turned off.                                                                                                               |

| cfg_wr_en_n                  | Input     | <b>Configuration Write Enable</b> : The active low write enable for configuration register access signal. Unimplemented, it is reserved for future use.                                                                                                                                             |

| cfg_byte_en_n[3:0]           | Input     | <b>Configuration Byte Enable</b> : The active low byte enables for configuration register access signal. Unimplemented, is reserved for future use.                                                                                                                                                 |

| cfg_err_ecrc_n               | Input     | <b>ECRC Error Report</b> : The user can assert this signal to report an end-to-end CRC (ECRC) error. Active low.                                                                                                                                                                                    |

| cfg_err_cpl_timeout_n        | Input     | Configuration Error Completion Timeout: The user can assert this signal to report a completion timed out. Active low.                                                                                                                                                                               |

| cfg_err_cpl_abort_n          | Input     | Configuration Error Completion Aborted: The user can assert this signal to report that a completion was aborted. Active low.                                                                                                                                                                        |

| cfg_err_cpl_unexpect_n       | Input     | <b>Configuration Error Completion Unexpected</b> : The user can assert this signal to report that an unexpected completion was received. Active low.                                                                                                                                                |

| cfg_err_posted_n             | Input     | Configuration Error Posted: Used to further qualify any of the cfg_err_* input signals. When this input is asserted concurrently with one of the other signals, it indicates that the transaction which caused the error was a posted transaction. Active low.                                      |

| cfg_err_tlp_cpl_header[47:0] | Input     | Configuration Error TLP Completion Header: Input that accepts the header information from the user when an error is signaled. This information is required so that the core can issue a correct completion, if required.                                                                            |

| cfg_bus_number[7:0]          | Output    | Configuration Bus Number: This output provides the assigned bus number for the device. The User Application must use this information in the Bus Number field of outgoing TLP requests. Default value after reset is 00h. Refreshed whenever a Type 0 Configuration packet is received.             |

| cfg_device_number[4:0]       | Output    | Configuration Device Number: This output provides the assigned device number for the device. The User Application must use this information in the Device Number field of outgoing TLP requests. Default value after reset is 00000b. Refreshed whenever a Type 0 Configuration packet is received. |

| cfg_function_number[2:0]     | Output    | Configuration Function Number: Provides the function number for the device. The User Application must use this information in the Function Number field of outgoing TLP request. Function number is hard-wired to 000b.                                                                             |

| cfg_status[15:0]             | Output    | <b>Configuration Status</b> : Status register from the Configuration Space Header.                                                                                                                                                                                                                  |

Table 6: Configuration Interface Signals (Cont'd)

| Name                                    | Direction | Description                                                                                                                                                                                                                                                                                    |

|-----------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cfg_command[15:0]                       | Output    | Configuration Command: Command register from the Configuration Space Header.                                                                                                                                                                                                                   |

| cfg_dstatus[15:0]                       | Output    | <b>Configuration Device Status</b> : Device status register from the PCI Express Extended Capability Structure.                                                                                                                                                                                |

| cfg_dcommand[15:0]                      | Output    | Configuration Device Command: Device control register from the PCI Express Extended Capability Structure.                                                                                                                                                                                      |

| cfg_lstatus[15:0]                       | Output    | Configuration Link Status: Link status register from the PCI Express Extended Capability Structure.                                                                                                                                                                                            |

| cfg_lcommand[15:0]                      | Output    | Configuration Link Command: Link control register from the PCI Express Extended Capability Structure.                                                                                                                                                                                          |

| cfg_cfg[1023:0]                         | Input     | <b>Configuration Configure</b> : This 1024-bit input port is used to configure core options. This port must by driven by a1024-bit constant valued binary pattern by the user.                                                                                                                 |

| cfg_err_ur_n                            | Input     | Configuration Error Unsupported Request: The user can assert this signal to report that an unsupported request was received. Active low.                                                                                                                                                       |

| cfg_err_cor_n                           | Input     | Configuration Error Correctable Error: The user can assert this signal to report that a correctable error was detected. Active low.                                                                                                                                                            |

| cfg_to_turnoff_n                        | Output    | Configuration To Turnoff: Output that notifies the user that a PME_TURN_Off message has been received and the CMM will start polling the cfg_turnoff_ok_n input coming in from the user. Once cfg_turnoff_ok_n is asserted, CMM sends a PME_To_Ack message to the upstream device. Active low. |

|                                         |           | Configuration Power Management Wake: A one-clock cycle active low assertion on this signal enables the core to generate and send a Power Management PME Message TLP to the upstream link partner.                                                                                              |

| cfg_pm_wake_n                           | Input     | <b>Note:</b> The user is required to assert this input only under stable link conditions as reported on the cfg_pcie_link_state[2:0] bus. Assertion of this signal when the PCI Express Link is in transition will result in incorrect behavior on the PCI Express Link.                       |

| cfg_pcie_link_state_n[2:0] <sup>1</sup> | Output    | PCI Express Link State: This one-hot encoded bus reports the PCI Express Link State information to the user.  110b - PCI Express Link State is L0  101b - PCI Express Link State is L0s  011b - PCI Express Link State is L1  111b - PCI Express Link State is in transition                   |

| cfg_trn_pending_n                       | Input     | User Transaction Pending: When asserted, sets the Transaction Pending bit in the Device Status Register. User is required to assert this input if the user application has not received a completion to an upstream request. Active low.                                                       |

| cfg_dsn[63:0]                           | Input     | Configuration Device Serial Number: Serial Number Register fields of the PCI Express Device Serial Number extended capability.                                                                                                                                                                 |

Table 6: Configuration Interface Signals (Cont'd)

| Name                       | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fast_train_simulation_only | Input     | Fast Train: Should only be asserted for simulation. Training counters are lowered when this input is asserted (set to "1") to allow the simulation to train faster. Do not assert this input when using the core in hardware. Doing so will cause the core to fail link training.                                                                                                                                                                                                                          |

| two_plm_auto_config        | Input     | Two-PLM Auto-Config: Used only for simulation; forces device to act as a down stream device for link training purposes. This signal should only be set to "11," if in simulation, two endpoint cores are connected back-to-back. When using the provided downstream port model for simulation, this signal should be set to "00" on the endpoint core under test. This signal should be set to "00" when using the core in hardware as an endpoint device. Any other setting in hardware is not supported. |

## **Transaction Interface**

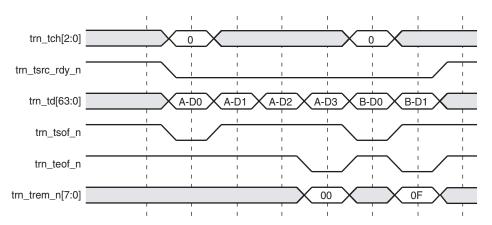

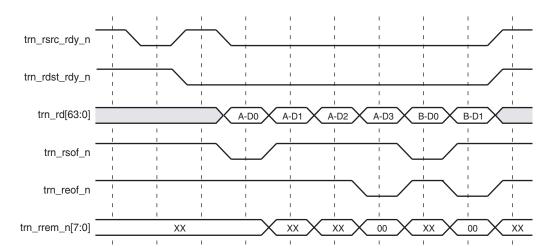

The Transaction (TRN) interface provides a mechanism for the user design to generate and consume TLPs. The signal names and signal descriptions, as well as the clock cycles and event descriptions for both interfaces, are described in Table 7 through Table 10 and illustrated in Figure 2 and Figure 3.

## **Transmit TRN Interface**

Table 7 defines the transmit (Tx) TRN interface signals.

**Table 7: Transmit Transaction Interface Signals**

| Name                           | Direction | Description                                                                                                                                                                                                                        |                                                        |  |

|--------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| trn_tsof_n                     | Input     | Transmit Start-of-Frame (SOF): Signals the start of a packet. Active low.                                                                                                                                                          |                                                        |  |

| trn_teof_n                     | Input     | Transmit End-of-Frame (EOF): Signals the end of a packet. Active low.                                                                                                                                                              |                                                        |  |

| trn_td[W-1:0]                  | Input     | Transmit Data: Packet data to be Product Name 1-lane 64-bit Endpoint 4-lane 64-bit Endpoint 8-lane 64-bit Endpoint 1-lane 32-bit Endpoint 4-lane 32-bit Endpoint                                                                   | e transmitted.  Data Bus Width (W)  64  64  64  32  32 |  |

| trn_trem_n[7:0] <sup>(1)</sup> | Input     | Transmit Data Remainder: Valid only if both trn_teof_n and trn_tdst_rdy_n are asserted. Legal values are:  0000_0000b = packet data on all of trn_td[63:0],  0000_1111b = packet data only on trn_td[63:32]                        |                                                        |  |

| trn_terrfwd_n                  | Input     | <b>Transmit Error Forward</b> : Marks the current packet in progress as errorpoisoned. Can be asserted any time between SOF and EOF, inclusive. Active low.                                                                        |                                                        |  |

| trn_tsrc_rdy_n                 | Input     | <b>Transmit Source Ready</b> : Indicates that the user application is presenting valid data on trn_td[W-1:0]. Active low.                                                                                                          |                                                        |  |

| trn_tdst_rdy_n                 | Output    | <b>Transmit Destination Ready</b> : Indicates that the core is ready to accept data on trn_td[W-1:0]. Active low.  Simultaneous assertion of trn_tsrc_rdy_n and trn_tdst_rdy_n marks successful transfer of data on trn_td[W-1:0]. |                                                        |  |

| trn_tsrc_dsc_n                 | Input     | <b>Transmit Source Discontinue</b> : Indicates that the user application is aborting the current packet. Active low.                                                                                                               |                                                        |  |

Table 7: Transmit Transaction Interface Signals (Cont'd)

| Name                | Direction | Description                                                                                                                                                                                        |                      |           |

|---------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------|

| trn_tdst_dsc_n      | Output    | <b>Transmit Destination Discontinue</b> : Indicates that the core is aborting the current packet. Asserted when the physical link is going into reset. Active low.                                 |                      |           |

|                     | Output    | <b>Transmit Buffers Available</b> : Number of transmit buffers available in the core. The maximum number is 32. Each transmit buffer can accommodate one TLP up to the supported Max_Payload_Size. |                      |           |

|                     |           | Product Name                                                                                                                                                                                       | Tx Buffers Available | Width (N) |

| trn_tbuf_av [N-1:0] |           | 1-lane 64-bit Endpoint                                                                                                                                                                             | 16                   | 5         |

|                     |           | 4-lane 64-bit Endpoint                                                                                                                                                                             | 16                   | 5         |

|                     |           | 8-lane 64-bit Endpoint                                                                                                                                                                             | 32                   | 6         |

|                     |           | 1-lane 32-bit Endpoint                                                                                                                                                                             | 8                    | 5         |

|                     |           | 4-lane 32-bit Endpoint                                                                                                                                                                             | 16                   | 5         |

<sup>1.</sup> trn\_trem[7:0] is not supported or necessary for the 1-lane and 4-lane 32-bit endpoint products.

Figure 2 illustrates the transfer on the TRN interface of two TLPs to be transmitted on the PCI Express Link. Every valid transfer can be up to a Quad Word (QWORD) of data.

Figure 2: Tx TRN Interface (64-bit Transaction Interface shown)

Table 8 defines and describes the transmit path clock cycle signals.

Table 8: Transmit Path Clock Cycle Signals

| Clock Cycle | Event Description                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | The Endpoint core for PCI Express signals that it can accept the transfer of a TLP, with the assertion of trn_tdst_rdy_n.                                                           |

| 2           | The user application initiates the transfer with the assertion of trn_tsrc_rdy_n and trn_tsof_n. The combined assertion of trn_tsrc_rdy_n and trn_tdst_rdy_n marks a data transfer. |

| 3           | Frame A QWORD D1 is transferred.                                                                                                                                                    |

| 4           | Frame A QWORD D2 is transferred.                                                                                                                                                    |

| 5           | The trn_trem_n[7:0] bus specifies the valid bytes on the last QWORD.                                                                                                                |

| 6           | Frame B QWORD D0 is transferred.                                                                                                                                                    |

Table 8: Transmit Path Clock Cycle Signals

| Clock Cycle | Event Description                                                                                                                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7           | Frame B QWORD D1 is transferred. The trn_trem_n[7:0] bus specifies the valid bytes on the last QWORD.                                                                                                                 |

| 8           | Note that trn_tdst_rdy_n is not deasserted to offer the user application the option to start the transmission of the next TLP, even though it can be stalled before being completed until a buffer becomes available. |

## **Receive TRN Interface**

Table 9 defines the receive (Rx) TRN interface signals.

Table 9: Receive Transaction Interface Signals

| Name                           | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|--------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| trn_rsof_n                     | Output    | Receive Start-of-Frame (SOF): Signals the start of a packet. Active low.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| trn_reof_n                     | Output    | Receive End-of-Frame (EOF): Signals the end of a packet. Active low.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| trn_rd[W-1:0]                  | Output    | Receive Data: Packet data being received. Product Name Data Bus Width (W)  1-lane 64-bit Endpoint 64  4-lane 64-bit Endpoint 64  8-lane 64-bit Endpoint 64  1-lane 32-bit Endpoint 32  4-lane 32-bit Endpoint 32                                                                                                                                                                                                                                                                                              |  |

| trn_rrem_n[7:0] <sup>(1)</sup> | Output    | Receive Data Remainder: Valid only if both trn_reof_n and trn_rdst_rdy_n are asserted. Legal values are: 0000_0000b = packet data on all of trn_rd[63:0], 0000_1111b = packet data only on trn_rd[63:32]                                                                                                                                                                                                                                                                                                      |  |

| trn_rerrfwd_n                  | Output    | Receive Error Forward: Marks the current packet in progress as error-poisoned. Asserted by the core at EOF. Active low.                                                                                                                                                                                                                                                                                                                                                                                       |  |

| trn_rsrc_rdy_n                 | Output    | Receive Source Ready: Indicates that the core is presenting valid data on trn_rd[W-1:0]. Active low.                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| trn_rdst_rdy_n                 | Input     | Receive Destination Ready: Indicates that the user application is ready to accept data on trn_rd[W1:0]. Active low. Simultaneous assertion of trn_rsrc_rdy_n and trn_rdst_rdy_n marks the successful transfer of data on trn_rd[W-1:0].                                                                                                                                                                                                                                                                       |  |

| trn_rsrc_dsc_n                 | Output    | Receive Source Discontinue: Indicates that the core is aborting the current packet transfer. Asserted when the physical link is going into reset. Active low.                                                                                                                                                                                                                                                                                                                                                 |  |

| trn_rnp_ok_n                   | Input     | Receive Non-Posted OK: The user application asserts this whenever it is ready to accept a Non-Posted Request packet. This allows Posted and Completion packets to bypass Non-Posted packets in the inbound queue if necessitated by the user application. Active low.  When the user application approaches a state where it is unable to service Non-Posted Requests, it must deassert trn_rnp_ok_n one clock cycle before the core presents EOF of the last Non-Posted TLP the user application can accept. |  |

Table 9: Receive Transaction Interface Signals (Cont'd)

| Name                               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| trn_rbar_hit_n[6:0]                | Output    | Receive BAR Hit: Indicates BAR(s) targeted by the current receive transaction. Active low.  • trn_rbar_hit_n[0] => BAR0  • trn_rbar_hit_n[1] => BAR1  • trn_rbar_hit_n[2] => BAR2  • trn_rbar_hit_n[3] => BAR3  • trn_rbar_hit_n[4] => BAR4  • trn_rbar_hit_n[5] => BAR5  • trn_rbar_hit_n[6] => Expansion ROM Address  Note that, if two BARs are configured into a single 64-bit address, both corresponding trn_rbar_hit_n bits will be asserted. |

| trn_rfc_ph_av[7:0] <sup>(2)</sup>  | Output    | Receive Posted Header Flow Control Credits Available: The number of Posted Header FC credits available to the remote link partner.                                                                                                                                                                                                                                                                                                                   |

| trn_rfc_pd_av[11:0] <sup>2</sup>   | Output    | Receive Posted Data Flow Control Credits Available: The number of Posted Data FC credits available to the remote link partner.                                                                                                                                                                                                                                                                                                                       |