# SPDIF/AES3 v2.0

# LogiCORE IP Product Guide

Vivado Design Suite

PG045 April 4, 2018

# **Table of Contents**

#### **IP Facts**

#### **Chapter 1: Overview**

| Functional Description | 5  |

|------------------------|----|

| Feature Summary        | 10 |

| Applications           | 10 |

| Unsupported Features   | 10 |

| Licensing and Ordering | 11 |

#### **Chapter 2: Product Specification**

| Standards         | 12 |

|-------------------|----|

| Performance       | 12 |

| Port Descriptions | 13 |

| Register Space    | 16 |

#### **Chapter 3: Designing with the Core**

| Clocking                                   | 24 |

|--------------------------------------------|----|

| Resets                                     | 25 |

| Electrical Circuit Considerations on Board | 25 |

#### **Chapter 4: Design Flow Steps**

| Customizing and Generating the Core | 27 |

|-------------------------------------|----|

| Constraining the Core               | 30 |

| Simulation                          | 31 |

| Synthesis and Implementation        | 31 |

#### Chapter 5: Example Design

#### Chapter 6: Test Bench

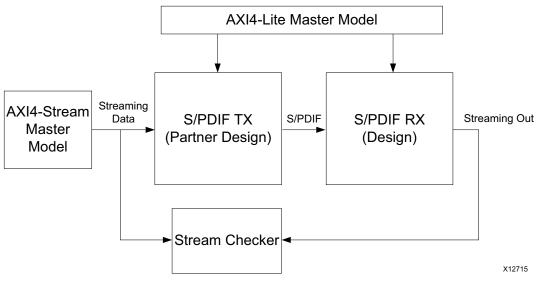

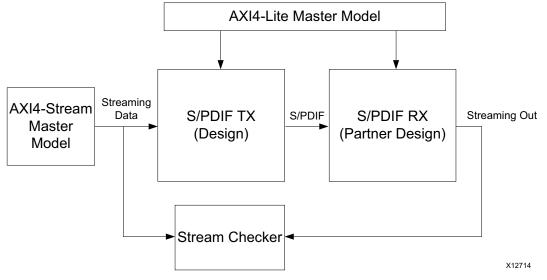

| Test Bench Functionality   | 34 |

|----------------------------|----|

| SPDIF/AES3 Core in RX Mode | 34 |

| SPDIF/AES3 Core in TX Mode | 35 |

#### Appendix A: Upgrading

| Migrating to the Vivado Design Suite | 36 |

|--------------------------------------|----|

| Upgrading in the Vivado Design Suite | 36 |

#### Appendix B: Debugging

| Finding Help on Xilinx.com | 37 |

|----------------------------|----|

| Debug Tools                | 39 |

| Hardware Debug             | 39 |

| Interface Debug            | 40 |

#### Appendix C: Additional Resources and Legal Notices

| Xilinx Resources                        | 42 |

|-----------------------------------------|----|

| Documentation Navigator and Design Hubs | 42 |

| References                              | 42 |

| Revision History                        | 44 |

| Please Read: Important Legal Notices    | 45 |

## **IP Facts**

### Introduction

The SPDIF/AES3 core is a digital audio interface controller that implements the International Electronic Commission (IEC) 60958-3 interface for transmitting and receiving audio data.

AES3 (also known as AES/EBU) is an audio interface standard for the exchange of digital audio signals between professional audio and video devices. AES3 was jointly developed by Audio Engineering Society (AES) and the European Broadcasting Union (EBU). An AES3 signal can carry two channels of PCM audio. AES3 is available in a consumer-grade variant known as S/PDIF. AES3 is commonly used in professional video and audio equipment used in broadcast studios such as cameras, servers, and switches. S/PDIF is more common in the consumer version of the audio equipment.

This includes standard bus interfaces to the AMBA<sup>®</sup> AXI4-Lite and AXI4-Stream interfaces [Ref 1], allowing for integration to the IP core with a master system for further processing of audio data. Data collected by the LogiCORE<sup>™</sup> IP SPDIF/AES3 core is stored in the core internal FIFO, allowing the system to process a relatively slow audio stream.

### Features

- Configurable as an SPDIF/AES3 audio data transmitter or an SPDIF/AES3 audio data receiver

- Configurable FIFO buffer stores the audio sample data

- IEC 60958-3 standard SPDIF/AES3 digital audio bus interface

- Two audio channels

- Audio sample lengths of 16/20/24 bits

- Variable sampling rates (32/44.1/48/88.2/96/ 176.4/192 kHz)

- The transmitter sends the invalid null audio frames over the SPDIF/AES3 line in case of a FIFO under-run condition

| LogiCORE IP Facts Table                      |                                                                                                                      |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Core Specifics                               |                                                                                                                      |  |  |  |

| Supported<br>Device<br>Family <sup>(1)</sup> | UltraScale+™ Families,<br>UltraScale™ Architecture, Zynq <sup>®</sup> -7000 All<br>Programmable SoC, Xilinx 7 series |  |  |  |

| Supported<br>User Interfaces                 | SPDIF/AES3, AXI4-Stream, AXI4-Lite                                                                                   |  |  |  |

| Resources                                    | Performance and Resource Utilization web page                                                                        |  |  |  |

| Provided with Core                           |                                                                                                                      |  |  |  |

| Design Files                                 | Encrypted HDL                                                                                                        |  |  |  |

| Example<br>Design                            | Verilog, VHDL                                                                                                        |  |  |  |

| Test Bench                                   | VHDL                                                                                                                 |  |  |  |

| Constraints<br>File                          | XDC                                                                                                                  |  |  |  |

| Simulation<br>Model                          | Verilog and VHDL Structural Models                                                                                   |  |  |  |

| Supported<br>S/W Driver                      | Provided                                                                                                             |  |  |  |

| Tested Design Flows <sup>(2)</sup>           |                                                                                                                      |  |  |  |

| lested Design Hows       |                                                                             |  |  |  |

|--------------------------|-----------------------------------------------------------------------------|--|--|--|

| Design Entry             | Vivado <sup>®</sup> Design Suite<br>Vivado                                  |  |  |  |

| Simulation               | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |

| Synthesis Vivado Synthes |                                                                             |  |  |  |

| Support                  |                                                                             |  |  |  |

| Dusuistad                | Duravid ad law Village at the Village Course automake second                |  |  |  |

Provided by Xilinx at the Xilinx Support web page

#### Notes:

- 1. For a complete listing of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

## Chapter 1

## Overview

## **Functional Description**

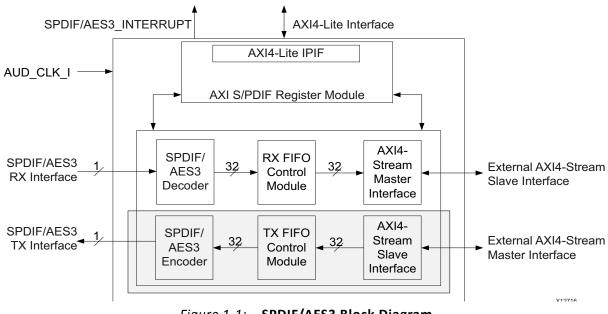

The LogiCORE<sup>™</sup> IP SPDIF/AES3 core is compatible with the SPDIF or AES3 protocol. It can be used in a receive or transmit mode and delivers or accepts audio data from an AXI4-Stream input. The SPDIF/AES3 core is designed for use in audio systems, and provide AES3 interface for LogiCORE Ips such as UHD-SDI, Display port and HDMI core for audio data transfers. Figure 1-1 shows the SPDIF/AES3 block diagram.

Figure 1-1: SPDIF/AES3 Block Diagram

The SPDIF/AES3 core can operate in two modes:

- **SPDIF/AES3 Receiver** Receives SPDIF/AES3 audio data and sends it through the AXI4-Stream interface

- **SPDIF/AES3 Transmitter** Receives audio data through the AXI4-Stream interface and transmits it through the SPDIF/AES3 interface

The core contains the following blocks in SPDIF/AES3 receive mode:

- AXI4-Lite IPIF

- AXI SPDIF/AES3 Register Module

- SPDIF/AES3 Decoder

- RX FIFO Control Module

- AXI4-Stream Master Interface

The core contains the following blocks in SPDIF/AES3 transmit mode:

- AXI4-Lite IPIF

- AXI SPDIF/AES3 Register Module

- AXI4-Stream Slave Interface

- TX FIFO Control Module

- SPDIF/AES3 Encoder

### **SPDIF/AES3** Register Module

This section describes the blocks within the SPDIF/AES3 register module.

#### AXI4-Lite IPIF

The SPDIF/AES3 register module provides the read/write control logic for the SPDIF/AES3 core register set. The registers are accessible by the AXI4-Lite master interface through the AXI4-Lite IPIF module, which is part of the SPDIF/AES3 register module.

The data width of the AXI4-Lite interface is fixed at 32 bits. The registers are defined in Table 2-3, page 16.

The interrupt control and soft reset functionality are also implemented as part of the SPDIF/ AES3 register module. The SPDIF/AES3 core can be reset by writing 0xA to the soft reset register. For an SPDIF/AES3 transmitter, an SPDIF/AES3 interrupt can be generated based on the FIFO Full/FIFO empty conditions. For an SPDIF/AES3 receiver, in addition to the FIFO Full/FIFO Empty conditions, the interrupt is triggered if any preamble error/bi-phase mark code (BMC) error is detected over the SPDIF/AES3 line or if the SPDIF/AES3 core receives the start of block over the SPDIF/AES3 line. In the Rx mode, the interrupt is also triggered when the channel-status value changes from one block to another.

### SPDIF/AES3 Decoder

The enable bit in the Control register of the SPDIF/AES3 register module has to be set to enable the SPDIF/AES3 decoder module. The SPDIF/AES3 decoder recovers data from the bi-phase mark coded SPDIF/AES3 data stream (see Bi-Phase Mark Code). The audio clock

frequency should be at least sixteen times the bit rate 64 x FS. FS is the sampling frequency where each sample has 64 bits. In bi-phase mark code, each bit changes twice in a bit period.

For example, to recover data from a 192 kHz sampling rate, the minimum audio clock frequency should be  $16 \times 64 \times 192$  kHz = 98.304 MHz to recover the data samples. As per the SPDIF/AES3 Protocol Preamble violates the bi-phase mark code format, SPDIF/AES3 decoder module identifies the channel number and the start of the audio block from the Preamble pattern.

The serial-to-parallel data conversion also takes place in the SPDIF/AES3 Decoder module and then generates the FIFO write enables with the 32-bit FIFO input data. The sampling frequency information (that is, the count of audio clocks during the bit period) is updated in the Status register of the SPDIF/AES3 register module.

This module detects the BMC/Preamble errors over the SPDIF/AES3 line and reports to the SPDIF/AES3 register module. This module also generates a recovered clock that is equivalent to the Fs of the incoming line.

### **RX FIFO Control Module**

The Asynchronous RX FIFO is used to store the 32-bit audio data received from the SPDIF/ AES3 decoder. The FIFO size is configurable and based on the C\_AXIS\_BUFFER\_SIZE parameter generated. The data width of the FIFO is fixed to 32 bits. This module receives the FIFO write input control and write data from the SPDIF/AES3 decoder. When the FIFO reaches the full condition, an interrupt is generated and the RX FIFO Full status is updated through the Status register of the SPDIF/AES3 register module. Similarly, the RX FIFO empty interrupt and corresponding status are updated through the SPDIF/AES3 Interrupt Status register.

#### **AXI4-Stream Interface**

The data width over the AXI4-Stream interface is fixed at 32 bits. Table 1-1 shows the 32-bit data format over the AXI4-Stream interface during audio data transmission and reception. All bit positions are as per the IEC60958-3 standard except for the preamble bit format.

| Bit[31] | Bit[30]            | Bit[29]       | Bit[28]      | Bits[27:4]        | Bits[3:0] |

|---------|--------------------|---------------|--------------|-------------------|-----------|

| Parity  | Channel Status Bit | User Data Bit | Validity Bit | Audio Sample Data | Preamble  |

Table 1-1: AXI4-Stream Audio Data Format

The preamble provides the start of the audio block and audio channel information. The preamble patterns for the start of block, channelA audio data, and channelB audio data are listed in Table 1-2.

| Table 1-2: Preamble |                                               |  |  |  |

|---------------------|-----------------------------------------------|--|--|--|

| Bits[3:0]           | Description                                   |  |  |  |

| 0001                | Start of audio block and Channel A audio data |  |  |  |

| 0010                | ChannelA audio data                           |  |  |  |

| 0011                | ChannelB audio data                           |  |  |  |

Bits[27:4] carry the audio data MSB bit at the 27th position and the LSB position is based on the audio sample length. Bit[28] provides the audio validity information. Bit[29] carries the user data information, and Bit[30] carries the channel status bit. Bit[31] is the even parity over 32 bits except for the preamble bits.

#### AXI4-Stream Master Interface

The AXI4-Stream Master interface transfers the 32-bit parallel data read from the non-empty FIFO to the AXI4-Stream interface. The corresponding data valid signal (m\_axis\_tvalid) is set and the channel identifier signal (m\_axis\_tid) is driven with the corresponding channel number. The channel number information is available to the AXI4-Stream Master interface through the SPDIF/AES3 decoder. This module depends on the handshaking signal m\_axis\_tready issued from the AXI4-Stream interface target slave for completion of the transfer.

#### AXI4-Stream Slave Interface

The AXI4-Stream Slave interface receives the 32-bit streaming data from the target connected to the AXI4-Stream interface. This module generates the handshaking signal <code>s\_axis\_tready</code> after receiving the streaming data (<code>s\_axis\_tdata</code>), data valid signal (<code>s\_axis\_tvalid</code>), and channel number identification (<code>s\_axis\_tdata</code>). This also generates the TX FIFO write control signals and transfers the data received from the AXI4-Stream interface to the TX FIFO Control Module. If the SPDIF/AES3 TX FIFO is full, this module stops receiving the audio samples by driving the handshake signal <code>s\_axis\_tready\_Low</code>. This avoids the FIFO overrun condition in the SPDIF/AES3 transmitter.

### **TX FIFO Control Module**

The Asynchronous TX FIFO is used to store the 32-bit streaming data received from the AXI4-Stream slave interface. The FIFO size is user configurable. The data width of the FIFO is fixed at 32 bits.

This module receives the FIFO write input control and write data from the AXI4-Stream slave interface. When the FIFO reaches the full condition, an interrupt is generated and the TX FIFO Full status is updated through the Interrupt Status register of the SPDIF/AES3 register module. This condition can occur when the SPDIF/AES3 enable bit is not set in the Control register of the SPDIF/AES3 register module, and the target is sending continuous streaming data or when the FIFO Size is not sufficient. After a reset, the IP starts transmitting data (when enabled) only when the FIFO is at least half filled.

The TX FIFO Control Module generates a TX FIFO\_EMPTY interrupt when the TX FIFO becomes empty. This condition can occur if enough samples are not received by the SPDIF/AES3 transmitter to send over the SPDIF/AES3 line.

## SPDIF/AES3 Encoder

This module has to get the clock configuration bits through the Control register to know the bit rate before SPDIF/AES3 data transmission starts. The enable bit in the Control register of the SPDIF/AES3 registers module must be set to enable the SPDIF/AES3 encoder module. The SPDIF/AES3 encoder converts the 32-bit parallel data received from the TX FIFO to serial data. The serial data is transferred over the SPDIF/AES3 interface in bi-phase mark code (BMC) format with respect to the received bit rate information. The audio clock input must be the harmonic of the sampling rate and should be higher than the bit rate. For example, for a 192 kHz sampling rate, 49.152 MHz or 98.3 MHz must be provided as the core frequency (AUD\_CLK\_I) and the corresponding clock divisor information must be given through the clock configuration register bits).

In case of a TX FIFO under-run condition, this module sends the null audio frames over the SPDIF/AES3 line with the validity bit set. When the validity bit is set to 1, it means per the SPDIF/AES3 protocol that the audio sample is invalid and the codec has to ignore the sample.

**IMPORTANT:** The audio clock generation and the setting of clock configuration bits in the Control register must be done with care to support these sampling rates: 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, 176.4 kHz, and 192 kHz. The minimum audio clock frequency of 49.152 MHz or harmonic frequency of the same which is higher than this frequency supports the sampling rates of 32 kHz, 48 kHz, 96 kHz, and 192 kHz. The minimum audio clock frequency of 45.1584 MHz or harmonic frequency of the same which is higher than this frequency supports the sampling rates of 44.1 kHz, 88.2 kHz, 88.2 kHz, 96 kHz, and 192 kHz.

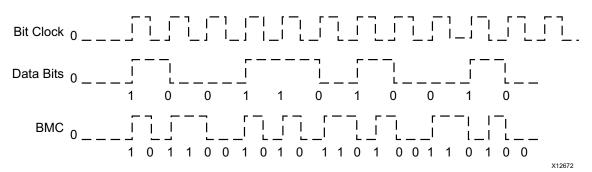

#### Bi-Phase Mark Code

The SPDIF/AES3 interface (IEC-60958) is a consumer version of the AES/EBU-interface. The SPDIF/AES3 digital signal is coded using the bi-phase mark code, which is a type of phase modulation. The bit clock, data bits, and BMC signals are shown in Figure 1-2.

Figure 1-2: Bi-Phase Mark Code

The frequency of the clock is twice the bit rate. Every bit of the original data is represented as two logical states, which, together, form a cell. The length of a cell (time slot) is equal to the length of a data bit. The logical level at the start of a bit is always inverted to the level at the end of the previous bit. The level at the end of a bit is equal (a 0 is transmitted) or inverted (a 1 is transmitted) to the start of that bit. The BMC has either one or two transitions for every bit. Data bit 1 has two transitions during a bit period, and Data bit 0 has one transition during a bit period. As per protocol, except for the preambles, SPDIF/AES3 audio data is transferred in the BMC format. Preambles violate the BMC to identify the channel information by the SPDIF/AES3 receivers.

## **Feature Summary**

The LogiCORE IP SPDIF/AES3 core is a digital audio interface controller that implements the PCM IEC 60958-3 interface features for transmitting and receiving audio data. The core can be configured as an SPDIF/AES3 audio data transmitter or an SPDIF/AES3 audio data receiver. The IEC 60958-3 standard SPDIF/AES3 digital audio bus interface has two audio channels and audio sample lengths of 16, 20, and 24 bits. Sample rates range from 32 kHz to 192 kHz.

The core includes an AMBA<sup>®</sup> AXI4-Lite interface for register access and an AXI4-Stream interface for audio data transfers. The AXI4-Stream interface allows integration between the IP core and an AXI system for further processing of audio data. Data collected by the SPDIF/ AES3 core is stored in the core internal FIFO, allowing the system to process a relatively slow audio stream.

## **Applications**

The SPDIF/AES3 core can be used as a short distance audio interconnect. It can be used to carry digital audio as defined by the standard IEC60958-3.

**Note:** The SPDIF/AES3 core can used be used to transmit and receive SPDIF as well as AES3 data. A necessary circuit (electrical interface, impedance matching) should be in place, on the board, based on the usage.

## **Unsupported Features**

The SPDIF/AES3 core does not support non-linear PCM encoded audio data streams. The core does not verify the Parity or CRC.

## **Licensing and Ordering**

This Xilinx<sup>®</sup> LogiCORE IP module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, visit the DisplayPort web page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

#### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado design tools: Vivado Synthesis

- Vivado Implementation

- write bitstream (Tcl command)

**IMPORTANT:** *IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.*

Chapter 2

# **Product Specification**

## Standards

The LogiCORE<sup>™</sup> IP SPDIF/AES3 core implements IEC 60958-3 interface features for transmitting and receiving audio data.

## Performance

Performance characterization of this core has been done using margin system methodology. The details of the margin system characterization methodology is described in the *Vivado Design Suite User Guide, Designing With IP* (UG896) [Ref 3].

**Note:** Maximum frequency numbers for UltraScale<sup>™</sup> architecture and Zynq<sup>®</sup>-7000 devices are expected to be similar to 7 series device numbers.

| Family   | Speed Grade | F <sub>Max</sub> (MHz) |             |  |

|----------|-------------|------------------------|-------------|--|

| ranny    | Speed Glade | AXI4-Lite              | AXI4-Stream |  |

| Virtex-7 |             | 180                    | 200         |  |

| Kintex-7 | -1          | 180                    | 200         |  |

| Artix-7  | -           | 120                    | 150         |  |

| Virtex-7 |             | 200                    | 240         |  |

| Kintex-7 | -2          | 200                    | 240         |  |

| Artix-7  | -           | 140                    | 180         |  |

| Virtex-7 |             | 220                    | 280         |  |

| Kintex-7 | -3          | 220                    | 280         |  |

| Artix-7  |             | 160                    | 200         |  |

Table 2-1:Maximum Frequencies

## **Port Descriptions**

The SPDIF/AES3 Input/Output (I/O) signals are listed and described in Table 2-2.

| Table 2-2: | I/O Signal Description |

|------------|------------------------|

|------------|------------------------|

| Signal Name                                 | Interface | I/O     | Initial<br>State | Description                                                                                                                |

|---------------------------------------------|-----------|---------|------------------|----------------------------------------------------------------------------------------------------------------------------|

|                                             | -         |         | System S         | ignals                                                                                                                     |

| aud_clk_i                                   | System    | Ι       | -                | Audio clock input used at the SPDIF/AES3 interface                                                                         |

| spdif_interrupt                             | System    | 0       | 0                | SPDIF/AES3 core interrupt output. When the interrupt occurs, this signal is continuously 1 until cleared/disabled.         |

|                                             | AX        | 4-Lite  | Interface        | System Signals                                                                                                             |

| s_axi_aclk                                  | System    | I       | -                | AXI4-Lite clock                                                                                                            |

| s_axi_aresetn                               | System    | Ι       | -                | AXI4-Lite reset, active-Low                                                                                                |

|                                             | AXI4-L    | ite Wr  | ite Addre        | ss Channel Signals                                                                                                         |

| s_axi_awaddr[c_s_axi_<br>addr_width – 1:0]  | AXI4-Lite | Ι       | _                | AXI4-Lite Write address. The write address bus gives<br>the address of the first transfer in a write burst<br>transaction. |

| s_axi_awvalid                               | AXI4-Lite | Ι       | _                | Write address valid. This signal indicates that valid write address and control information are available.                 |

| s_axi_awready                               | AXI4-Lite | 0       | 0                | Write address ready. This signal indicates that the slave is ready to accept an address and associated control signals.    |

|                                             | AXI4      | -Lite W | /rite Data       | a Channel Signals                                                                                                          |

| s_axi_wdata[c_s_axi_<br>data_width – 1:0]   | AXI4-Lite | Ι       | _                | Write data bus                                                                                                             |

| s_axi_wstrb[c_s_axi_<br>data_width/8 – 1:0] | AXI4-Lite | I       | -                | Write strobes. Each signal indicates which byte lanes<br>to update in memory. These are unused in the SPDIF/<br>AES3 core. |

| s_axi_wvalid                                | AXI4-Lite | Ι       | -                | Write valid. This signal indicates that valid write data and strobes are available.                                        |

| s_axi_wready                                | AXI4-Lite | 0       | 0                | Write ready. This signal indicates that the slave can accept the write data.                                               |

|                                             | AXI4-Li   | te Writ | te Respor        | nse Channel Signals                                                                                                        |

| s_axi_bresp[1:0]                            | AXI4-Lite | 0       | 0                | Write response. This signal indicates the status of the write transaction.                                                 |

| s_axi_bvalid                                | AXI4-Lite | 0       | 0                | Write response valid. This signal indicates that a valid write response is available.                                      |

| s_axi_bready                                | AXI4-Lite | Ι       | _                | Response ready. This signal indicates that the master can accept the response information.                                 |

#### Table 2-2: I/O Signal Description (Cont'd)

| Signal Name                                | Interface   | I/O     | Initial<br>State | Description                                                                                                                                                                                   |

|--------------------------------------------|-------------|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | AXI4-L      | ite Rea | ad Addre         | ss Channel Signals                                                                                                                                                                            |

| s_axi_araddr[c_s_axi_addr<br>_width – 1:0] | AXI4-Lite   | Ι       | -                | Read address. The read address bus gives the initial address of a read burst transaction.                                                                                                     |

| s_axi_arvalid                              | AXI4-Lite   | Ι       | _                | Read address valid. When High, this signal indicates that the read address and control information are valid and remain stable until the address acknowledgment signal s_axi_arready is High. |

| s_axi_arready                              | AXI4-Lite   | 0       | 0                | Read address ready. This signal indicates that the slave is ready to accept an address and associated control signals.                                                                        |

|                                            | AXI4        | -Lite R | ead Data         | Channel Signals                                                                                                                                                                               |

| s_axi_rdata[c_s_axi_<br>data_width – 1:0]  | AXI4-Lite   | 0       | 0                | Read data bus                                                                                                                                                                                 |

| s_axi_rresp[1:0]                           | AXI4-Lite   | 0       | 0                | Read response. This signal indicates the status of the read transfer.                                                                                                                         |

| s_axi_rvalid                               | AXI4-Lite   | 0       | 0                | Read valid. This signal indicates that the required read data is available and the read transfer can complete.                                                                                |

| s_axi_rready                               | AXI4-Lite   | Ι       | -                | Read ready. This signal indicates that the master can accept the read data and response information.                                                                                          |

|                                            | SP          | DIF/AE  | S3 RX In         | terface Signals                                                                                                                                                                               |

| spdif_i                                    | SPDIF/AES3  | Ι       | -                | Audio input from the SPDIF/AES3 interface                                                                                                                                                     |

| rxclk_out                                  | NA          | 0       | 0                | Recovered Fs signal based on the incoming SPDIF/<br>AES3 input                                                                                                                                |

|                                            | SP          | DIF/AE  | S3 TX Int        | terface Signals                                                                                                                                                                               |

| spdif_o                                    | SPDIF/AES3  | 0       | 0                | Audio output to the SPDIF/AES3 interface                                                                                                                                                      |

|                                            | AXI4-       | Stream  | n Master         | Interface Signals                                                                                                                                                                             |

| m_axis_aclk                                | M_AXIStream | Ι       | -                | The AXI4-Stream global clock signal in receive mode.<br>All streaming signals are sampled on the rising edge<br>of m_axis_aclk.                                                               |

| m_axis_aresetn                             | M_AXIStream | Ι       | _                | The AXI4-Stream global reset signal in receive mode.<br>m_axis_aresetn is active-Low.                                                                                                         |

| m_axis_tvalid                              | M_AXIStream | 0       | 0                | AXI4-Stream Valid Out. Indicates stream data bus,<br>m_axis_tdata, is valid.<br>0 = Write data is not valid<br>1 = Write data is valid                                                        |

| m_axis_tready                              | M_AXIStream | Ι       | _                | AXI4-Stream Ready. Indicates to the AXI4-Stream<br>Master interface that the target is ready to receive<br>stream data.<br>0 = Not ready to receive data<br>1 = Ready to receive data         |

#### Table 2-2: I/O Signal Description (Cont'd)

| Signal Name                                | Interface   | I/O    | Initial<br>State | Description                                                                                                                                                    |

|--------------------------------------------|-------------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axis_tdata[c_axis_<br>tdata_width – 1:0] | M_AXIStream | 0      | 0                | AXI4-Stream Data Out                                                                                                                                           |

| m_axis_tid[c_axis_tid_<br>width – 1:0]     | M_AXIStream | 0      | 0                | m_axis_tid is the data stream identifier that<br>indicates channel number of audio data.                                                                       |

|                                            | AXI4        | -Strea | m Slave I        | nterface Signals                                                                                                                                               |

| s_axis_aclk                                | S_AXIStream | I      | -                | The AXI4-Stream global clock signal in transmit mode. All signals are sampled on the rising edge of s_axis_aclk.                                               |

| s_axis_aresetn                             | S_AXIStream | Ι      | _                | The AXI4-Stream global reset signal in transmit mode. s_axis_aresetn is active-Low.                                                                            |

| s_axis_tvalid                              | S_AXIStream | Ι      | _                | AXI4-Stream Valid In. Indicates the stream data bus,<br>s_axis_tdata, is valid.<br>0 = Write data is not valid<br>1 = Write data is valid                      |

| s_axis_tready                              | S_AXIStream | 0      | 0                | AXI4-Stream Ready. Indicates the AXI4-Stream Slave<br>interface is ready to receive stream data.<br>0 = Not ready to receive data<br>1 = Ready to receive data |

| s_axis_tdata[c_axis_<br>tdata_width – 1:0] | S_AXIStream | Ι      | -                | AXI4-Stream Data In                                                                                                                                            |

| s_axis_tid[c_axis_tid_<br>width – 1:0]     | S_AXIStream | Ι      | _                | <pre>s_axis_tid is the data stream identifier that<br/>indicates channel number of audio data.</pre>                                                           |

## **Register Space**

Table 2-3 specifies the offset address, register name, and accessibility of each firmware addressable register from the three classes of registers within the SPDIF/AES3 core. User access to each register is from an offset to the base address.

For Channel Status registers, capturing channel status bits into channel status registers is configurable. When the Channel Status registers are enabled, only these registers are part of SPDIF/AES3 receiver logic. Channel Status registers hold the 192-bit channel status information received over the SPDIF/AES3 input when the SPDIF/AES3 core is in receive mode. The channel status is assumed to be common for both channel a and channel b. Thus the channels status bits are captured from one of the channels. These registers are updated after one complete audio frame is received. Usually, the channel status register data does not change frame to frame. For more information on these bits including their descriptions, see the IEC-60958-3 specification.

For the Channel a/b User Data registers, capturing SPDIF/AES3 user data bits into user data registers is configurable. When the User Enabled registers are enabled, only these registers are part of the SPDIF/AES3 receiver logic. User Data registers hold the 192-bit user data received over the SPDIF/AES3 input when the SPDIF/AES3 core is in receive mode. The user data is captured for both channel a and channel b in the corresponding registers. These registers are updated after one complete audio frame is received.

| Offset Address<br>(Hex) | Register Name                   | Description                              |

|-------------------------|---------------------------------|------------------------------------------|

|                         | Interrup                        | t Registers                              |

| 0x1C                    | Global Interrupt Enable (GIE)   | Device Global interrupt enable register  |

| 0x20                    | Interrupt Status Register (ISR) | IP interrupt status register             |

| 0x28                    | Interrupt Enable Register (IER) | IP interrupt enable register             |

|                         | Soft Res                        | et Register                              |

| 0x40                    | Soft Reset Register             | Soft Reset Register                      |

|                         | SPDIF/AES3 Configuration,       | Control, and Data Registers              |

| 0x44                    | SPDIF/AES3 Control Register     | Control register                         |

| 0x48                    | SPDIF/AES3 Status Register      | Status register                          |

| 0x4C                    | Channel Status Register0        | Audio Channel status bits 31 downto 0    |

| 0x50                    | Channel Status Register1        | Audio Channel status bits 63 downto 32   |

| 0x54                    | Channel Status Register2        | Audio Channel status bits 95 downto 64   |

| 0x58                    | Channel Status Register3        | Audio Channel status bits 127 downto 96  |

| 0x5C                    | Channel Status Register4        | Audio Channel status bits 159 downto 128 |

#### Table 2-3: Register Map

#### Table 2-3: Register Map (Cont'd)

| Offset Address<br>(Hex) | Register Name                 | Description                              |

|-------------------------|-------------------------------|------------------------------------------|

| 0x60                    | Channel Status Register5      | Audio Channel status bits 191 downto 160 |

| 0x64                    | Channel A User Data Register0 | Channel A User Data bits 31 downto 0     |

| 0x68                    | Channel A User Data Register1 | Channel A User Data bits 63 downto 32    |

| 0x6C                    | Channel A User Data Register2 | Channel A User Data bits 95 downto 64    |

| 0x70                    | Channel A User Data Register3 | Channel A User Data bits 127 downto 96   |

| 0x74                    | Channel A User Data Register4 | Channel A User Data bits 159 downto 128  |

| 0x78                    | Channel A User Data Register5 | Channel A User Data bits 191 downto 160  |

| 0x7C                    | Channel B User Data Register0 | Channel B User Data bits 31 downto 0     |

| 0x80                    | Channel B User Data Register1 | Channel B User Data bits 63 downto 32    |

| 0x84                    | Channel B User Data Register2 | Channel B User Data bits 95 downto 64    |

| 0x88                    | Channel B User Data Register3 | Channel B User Data bits 127 downto 96   |

| 0x8C                    | Channel B User Data Register4 | Channel B User Data bits 159 downto 128  |

| 0x90                    | Channel B User Data Register5 | Channel B User Data bits 191 downto 160  |

#### Notes:

1. The soft reset functionality is implemented by the soft\_reset module.

### **Global Interrupt Enable (GIE)**

The Global Interrupt Enable register, described in Table 2-4, has a single defined bit that globally enables the final interrupt out to the system.

| Table 2-4: | Global Interrupt Enable Register (Offset 0x1C | ) |

|------------|-----------------------------------------------|---|

|------------|-----------------------------------------------|---|

| Bits | Name   | Reset<br>Value | Access<br>Type | Description                                                                                                                                                |

|------|--------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31   | GIE    | 0              | R/W            | Global Interrupt Enable<br>0 = All interrupts disabled. No interrupts from SPDIF/AES3<br>1 = Unmasked SPDIF/AES3 interrupts are passed to the<br>processor |

| 30:0 | Unused | N/A            | N/A            | Reserved                                                                                                                                                   |

## Interrupt Status Register (ISR)

Firmware uses the ISR to determine which interrupt events from the SPDIF/AES3 core need servicing. Writing a 1 to a bit position within the register causes the corresponding bit to toggle. All register bits are cleared upon reset. The register uses a toggle on write method to allow the firmware to clear selected interrupts by writing a 1 to the desired interrupt bit field position.

This mechanism avoids the requirement on the User Interrupt Service routine to perform a Read/Modify/Write operation to clear a single bit within the register. An interrupt value of 1 indicates the interrupt has occurred. A value of 0 indicates that no interrupt occurred or it was cleared. The Interrupt Status register bit fields are described in Table 2-5.

| Bits | Name                     | Reset<br>Value | Access Type                 | Description                                                                                                                                                                                                  |

|------|--------------------------|----------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:6 | Unused                   | 0              | N/A                         | Reserved                                                                                                                                                                                                     |

| 5    | Channel Status<br>Change | 0              | Read/Toggle<br>on writing 1 | This bit is set whenever a change in the channel status information is detected.                                                                                                                             |

| 4    | Preamble Error           | 0              | Read/Toggle<br>on writing 1 | This bit is set when the incorrect preamble format is<br>received over the SPDIF/AES3 core in receive mode, for<br>example, if the channel a preamble is received after the<br>start of block.               |

| 3    | BMC Error                | 0              | Read/Toggle<br>on writing 1 | This bit is set when there is a bi-phase mark code (BMC) violation over the SPDIF/AES3 audio data bits in receive mode (except for the preamble). The core drops the affected sample in case of a BMC error. |

| 2    | Start Of Block           | 0              | Read/Toggle<br>on writing 1 | This bit is set when the SPDIF/AES3 core is in receive<br>mode and when it detects the start of block preamble<br>over the<br>S/PDIF_I input. This bit is set from the second block<br>onwards.              |

| 1    | TX/RX FIFO Empty         | 0              | Read/Toggle<br>on writing 1 | This bit is set when the TX FIFO changes from non-empty<br>to empty in Transmit mode and when the RX FIFO<br>changes from non-empty to empty.                                                                |

| 0    | TX/RX FIFO Full          | 0              | Read/Toggle<br>on writing 1 | This bit is set when the TX FIFO becomes full in transmit<br>mode and when the RX FIFO becomes full in receive<br>mode.                                                                                      |

Table 2-5: Interrupt Status Register (Offset 0x20)

### Interrupt Enable Register

The Interrupt Enable register is a read and write register that enables the SPDIF/AES3 interrupts. The Interrupt Enable register bit fields are described in Table 2-6.

| Bits | Name                                 | Reset<br>Value | Access<br>Type | Description                                                                                                                                                                                                                            |

|------|--------------------------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:6 | Unused                               | N/A            | N/A            | Reserved                                                                                                                                                                                                                               |

| 5    | Channel Status Change                | 0              | R/W            | This bit must be set to generate the Channel Status<br>change interrupt. This is applicable only in receive<br>mode.                                                                                                                   |

| 4    | Preamble Error                       | 0              | R/W            | This bit must be set to generate the preamble error interrupt. In transmit mode, this bit is unused.                                                                                                                                   |

| 3    | BMC Error Interrupt<br>Enable        | 0              | R/W            | This bit must be set to generate the BMC error interrupt. In transmit mode, this bit is unused.                                                                                                                                        |

| 2    | Start Of Block Interrupt<br>Enable   | 0              | R/W            | This bit must be set to generate the start of block<br>interrupt in receive mode. In transmit mode, this bit is<br>unused.                                                                                                             |

| 1    | TX/RX FIFO Empty<br>Interrupt Enable | 0              | R/W            | This bit must be set to generate the TX FIFO empty<br>interrupt when the SPDIF/AES3 core is in transmit mode<br>and the same bit must be set when the SPDIF/AES3 core<br>is in transmit mode to enable the RX FIFO empty<br>interrupt. |

| 0    | TX/RX FIFO Full Interrupt<br>Enable  | 0              | R/W            | This bit must be set to generate the TX FIFO full<br>interrupt when the SPDIF/AES3 core is in transmit mode<br>and the same bit has to be set when the SPDIF/AES3<br>core is in receive mode to enable the RX FIFO full<br>interrupt.  |

Table 2-6: Interrupt Enable Register (Offset 0x28)

### Soft Reset Register

The firmware writes to the Soft Reset register to initialize all of the SPDIF/AES3 registers to their default states. To accomplish this, the firmware must write the value of 0xA to the least-significant nibble of the 32-bit word. After recognizing a write of 0xA, the soft\_reset module issues a pulse four clocks long to reset the SPDIF/AES3 core. At the end of the pulse, the Soft Reset register acknowledges the AXI4 transaction, which prevents anything further from happening while the reset occurs. Writing any value to Bits[3:0] other than 0xA results in an AXI4 transaction acknowledge with an error status. This register is not readable. The Soft Reset register bit fields are described in Table 2-7.

| Bits | Name      | Reset<br>Value | Access<br>Type | Description                                                                                                                                                                                                                                  |

|------|-----------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:4 | Unused    | N/A            | N/A            | Reserved                                                                                                                                                                                                                                     |

| 3:0  | Reset Key | 0              | W              | The firmware must write a value of $0xA$ to this field to cause a soft reset of the interrupt registers of the SPDIF/AES3 controller. Writing any other value results in an AXI4 transaction acknowledgment with SLVERR and no reset occurs. |

Table 2-7: Soft Reset Register (Offset 0x40)

## SPDIF/AES3 Control Register

The SPDIF/AES3 Control register is a read and write register that configures the SPDIF/AES3 core. This register has an SPDIF/AES3 enable bit, a TX/RX FIFO flush bit, and clock configuration bits. The SPDIF/AES3 Control register bit fields are described in Table 2-8.

| Bits | Name                        | Reset<br>Value | Access<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-----------------------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:6 | Unused                      | N/A            | N/A            | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5:2  | TX clock Configuration Bits | 0              | R/W            | These bits provide the audio clock division number to<br>transmit the SPDIF/AES3 bits. The bit frequency is<br>generated based on these bits. For example, to<br>generate a 32 kHz audio sampling frequency, the bit<br>rate is 2.048 MHz (that is, 32 kHz × 64 because the<br>audio sample width is of 64 bits, 32 bits for channel a<br>and 32 bits for channel b). If the supplied AUD_CLK_I<br>is 16.384, the Bits Division Number has to be 0001.<br>Bits Division Number:<br>0000 = 4<br>0001 = 8<br>0010 = 16<br>0011 = 24<br>0100 = 32<br>0101 = 48<br>0110 = 64<br>Others = Reserved |

| 1    | TX FIFO/RX FIFO Flush       | 0              | R/W            | This bit must be set to 1 to reset the TX FIFO in transmit mode and to reset the RX FIFO in receive mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0    | TX/RX Enable                | 0              | R/W            | This bit must be set to 1 to enable the SPDIF/AES3 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 2-8: SPDIF/AES3 Control Register (Offset 0x44)

### SPDIF/AES3 Status Register

The SPDIF/AES3 Status register is a read-only register that contains the status of the SPDIF/AES3 core. The SPDIF/AES3 Status register bit fields are described in Table 2-9.

| Table 2-9: | SPDIF/AES3 Status Register (Offset 0x48) |

|------------|------------------------------------------|

|------------|------------------------------------------|

| Bits  | Name               | Reset<br>Value | Access<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|--------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:10 | Unused             | N/A            | N/A            | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9:0   | Sample clock count | 0              | R              | These bits are updated with the number of audio clocks for<br>the SPDIF/AES3 data bit period. This audio clock count is<br>recovered by the SPDIF/AES3 decoder module. This count<br>gives the approximate count for the SPDIF/AES3 bit period<br>when the audio clock is not the harmonic of core<br>frequency. These bits are used in receive mode only. In<br>transmit mode, these bits are unused. This value can be<br>used to determine the appx Fs of the incoming SPDIF/AES3<br>frame as follows:<br>Fs = 1000000 /(Sample_clock_count*64*CLK_PERIOD)<br>where, CLK_PERIOD is the period (in ns) of the clock<br>connected to aud_clk_i. |

#### **Channel Status Registers**

A set of six configurable registers store the 192-bit SPDIF/AES3 Audio Channel Status information. These registers are active when the SPDIF/AES3 core is in receive mode and when the Enable Channel Status registers are 1. This channel status information is captured from one of the channels, assuming both channel a and channel b carry the same channel status information over SPDIF/AES3. The Channel Status register bit fields are described in Table 2-10. For complete descriptions of these bit fields, see the IEC-60958-3 specification.

| Table 2-10: | Channel Status Registers (Offsets 0x4C to 0x60) |

|-------------|-------------------------------------------------|

|             |                                                 |

| Bits | Name                     | Reset<br>Value | Access<br>Type | Description                                                                                                |

|------|--------------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------|

| 31:0 | Channel Status Register0 | 0              | R              | This register holds bits 31 downto 0 of the audio channel status information received over SPDIF/ AES3.    |

| 31:0 | Channel Status Register1 | 0              | R              | This register holds bits 63 downto 32 of the audio channel status information received over SPDIF/ AES3.   |

| 31:0 | Channel Status Register2 | 0              | R              | This register holds bits 95 downto 64 of the audio channel status information received over SPDIF/ AES3.   |

| 31:0 | Channel Status Register3 | 0              | R              | This register holds bits 127 downto 96 of the audio channel status information received over SPDIF/ AES3.  |

| 31:0 | Channel Status Register4 | 0              | R              | This register holds bits 159 downto 128 of the audio channel status information received over SPDIF/ AES3. |

| 31:0 | Channel Status Register5 | 0              | R              | This register holds bits 191 downto 160 of the audio channel status information received over SPDIF/ AES3. |

## **Channel A User Data Registers**

A set of six configurable registers store the 192-bit SPDIF/AES3 Channela User data information. These registers are active when the SPDIF/AES3 core is in receive mode and when the Enable User Data registers are 1. This user data information is captured from channel a. The Channel A User Data registers bit fields are described in Table 2-11.

| Bits | Name                         | Reset<br>Value | Access<br>Type | Description                                                                                                  |

|------|------------------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------|

| 31:0 | Channela User Data Register0 | 0              | R              | This register holds bits 31 downto 0 of the user data information received over SPDIF/AES3 channel a.        |

| 31:0 | Channela User Data Register1 | 0              | R              | This register holds bits 63 downto 32 of the audio user data information received over SPDIF/AES3 channel a. |

| 31:0 | Channela User Data Register2 | 0              | R              | This register holds bits 95 downto 64 of the user data information received over SPDIF/AES3 channel a.       |

| 31:0 | Channela User Data Register3 | 0              | R              | This register holds bits 127 downto 96 of the user data information received over SPDIF/AES3 channel a.      |

| 31:0 | Channela User Data Register4 | 0              | R              | This register holds bits 159 downto 128 of the user data information received over SPDIF/AES3 channel a.     |

| 31:0 | Channela User Data Register5 | 0              | R              | This register holds bits 191 downto 160of the user data information received over SPDIF/AES3 channel a.      |

Table 2-11: Channel A User Data Registers (Offsets 0x64-0x78)

### **Channel B User Data Registers**

A set of six configurable registers store the 192-bit SPDIF/AES3 Channelb User data information. These registers are active when the SPDIF/AES3 core is in receive mode and when the Enable User Data registers are 1. This user data information is captured from channel b. The Channel B User data registers bit fields are described in Table 2-12.

Table 2-12: Channel B User Data Registers (Offsets 0x7C to 0x90)

| Bits | Name                         | Reset<br>Value | Access<br>Type | Description                                                                                                        |

|------|------------------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------|

| 31:0 | Channelb User Data Register0 | 0              | R              | This register holds bits 31 downto 0 of the user data information received over SPDIF/AES3 channel b.              |

| 31:0 | Channelb User Data Register1 | 0              | R              | This register holds bits 63 downto 32 of the audio<br>user data information received over SPDIF/AES3<br>channel b. |

| Bits | Name                         | Reset<br>Value | Access<br>Type | Description                                                                                              |

|------|------------------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------|

| 31:0 | Channelb User Data Register2 | 0              | R              | This register holds bits 95 downto 64 of the user data information received over SPDIF/AES3 channel b.   |

| 31:0 | Channelb User Data Register3 | 0              | R              | This register holds bits 127 downto 96 of the user data information received over SPDIF/AES3 channel b.  |

| 31:0 | Channelb User Data Register4 | 0              | R              | This register holds bits 159 downto 128 of the user data information received over SPDIF/AES3 channel b. |

| 31:0 | Channelb User Data Register5 | 0              | R              | This register holds bits 191 downto 160 of the user data information received over SPDIF/AES3 channel b. |

#### Table 2-12: Channel B User Data Registers (Offsets 0x7C to 0x90) (Cont'd)

Chapter 3

# Designing with the Core

This chapter includes guidelines and additional information to facilitate designing with the core.

## Clocking

The SPDIF/AES3 core interfaces with three different clocks which are described as follows. Asynchronous FIFOs are used for the audio data cross clocking paths.

aud\_clk\_i – The SPDIF/AES3 audio interface works with this clock. The frequency of the clock should be ≥ 1024 times the audio sampling rate for SPDIF/AES3 in receive mode. In receive mode, if the incoming Fs is not known, then it is recommended to connect a 200 MHz clock to this port.

For SPDIF/AES3 in transmit mode, the frequency of this clock should be a harmonic of the audio sampling rate and the corresponding divisor should be set in the SPDIF/AES3 control register. For example, a 32 kHz sampling rate, 16.384 MHz is the minimum aud\_clk\_i rate required.

- **s\_axi\_aclk** This is the processor domain. The AXI4-Lite interface to the SPDIF/AES3 register access works with this clock.

- **s\_axis\_aclk/m\_axis\_aclk** This is the audio streaming interface clock.

## Resets

The SPDIF/AES3 core uses the following resets.

- AXI4-Lite interface s\_axi\_aresetn which is active-Low.

- AXI Streaming interface s\_axis\_aresetn/m\_axis\_aresetn which is active-Low.

- Soft reset through the register interface

The AXI4-Lite interface reset and soft reset clears the entire design. AXI streaming interface reset clears the FIFO and the streaming interface logic. There is also a register bit to flush the internal FIFO alone.

## **Electrical Circuit Considerations on Board**

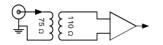

You must ensure that a proper electrical circuit is present on the board for SPDIF or AES3 connectivity. For more details, see the AES3 specifications (www.aes.org).

The Xilinx reference board supports unbalanced 75  $\Omega$  coaxial connections that are widely used in the broadcast industry to support the AES3 audio transmission. The AES3 input and output interfaces support unbalanced HD-BNC 75  $\Omega$  coaxial connections per AES3-4-2009, Annex D.

The AES3 input circuit utilizes an audio transformer circuit which provides a 75  $\Omega$  impedance unbalanced input. The Transformer magnetics convert the unbalanced signal to balanced (differential 100  $\Omega$ ) signal that sources a differential to single ended converter, which in turn drives the singled ended input to the Xilinx FPGA.

Figure 3-1: Simplified Input Circuit Diagram

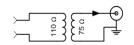

On the AES3 output side, the FPGAs output is a 1.2V LVCMOS complementary pair that drives the 110  $\Omega$  balanced side of the audio transformer, which is converted to an unbalanced 75  $\Omega$  singled ended output signal to the 75  $\Omega$  coaxial HD-BNC connector.

Figure 3-2: Simplified Output Circuit Diagram

Since the IP core supports up to 192 KHz stereo audio, the AES3 input and output circuity is designed to handle a maximum data bit rate of 192KHz × 2ch × 32bit/ch = 12.288 Mbps. The AES3 electrical interface specifications are defined in AES3-4-2009, Annex D.

# **Design Flow Steps**

This chapter describes customizing and generating the core, constraining the core, and the simulation, synthesis and implementation steps that are specific to this IP core. More detailed information about the standard Vivado® design flows and the Vivado IP integrator can be found in the following Vivado Design Suite user guides:

- Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator (UG994) [Ref 2]

- Vivado Design Suite User Guide: Designing with IP (UG896) [Ref 3]

- Vivado Design Suite User Guide: Getting Started (UG910) [Ref 4]

- Vivado Design Suite User Guide: Logic Simulation (UG900) [Ref 5]

## **Customizing and Generating the Core**

This section includes information about using  $Xilinx^{\mathbb{R}}$  tools to customize and generate the core in the Vivado Design Suite.

If you are customizing and generating the core in the IP integrator, see the *Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator* (UG994) [Ref 2] for detailed information. IP integrator might auto-compute certain configuration values when validating or generating the design. To check whether the values change, see the description of the parameter in this chapter. To view the parameter value, run the validate bd design command in the Tcl console.

### Vivado Integrated Design Environment

You can customize the IP for use in your design by specifying values for the various parameters associated with the IP core using the following steps:

- 1. Select the IP from the IP catalog.

- 2. Double-click the selected IP or select the Customize IP command from the toolbar or right-click menu.

For details, see the Vivado Design Suite User Guide: Designing with IP (UG896) [Ref 3] and the Vivado Design Suite User Guide: Getting Started (UG910) [Ref 4].

www.xilinx.com

*Note:* Figures in this chapter are illustrations of the Vivado IDE. This layout might vary from the current version.

| Figure 4-1 shows the Customize IP | dialog box with information about customizing |

|-----------------------------------|-----------------------------------------------|

| parameters in the Transmit Mode.  |                                               |

| A                                                                                                                                       | Re-customize IP (on xhdl3181)                     | ×      |

|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------|

| SPDIF/AES3 (2.0)                                                                                                                        |                                                   | 4      |

| Ocumentation 📄 IP Location                                                                                                              |                                                   |        |

| Show disabled ports                                                                                                                     | Component Name spdif_0                            |        |

| + AXM_LITE<br>+ SAXSTREAM<br>aud_clk_i SPDIE_TX +<br>- saxi,acite<br>- s_axi,acite<br>- s_axi,acite<br>- s_axib_acite<br>- s_axib_acite | SPDIF Mode Receiver () Transmitter FIFO Depth 512 |        |

|                                                                                                                                         | OK                                                | Cancel |

Figure 4-1: SPDIF/AES3 in Transmit Mode

- **Component Name** Enter a name for the core instance. This example uses the name *spdif\_0*.

- **SPDIF/AES3 Mode** This selects the mode of operation of SPDIF/AES3. It can either be a receiver or transmitter based on selection.

- **FIFO Depth** This sets the Internal FIFO depth to store audio samples. Set the depth of FIFO based on the aud\_clk\_i and streaming clock connected (m\_axis\_aclk in case of SPDIF/AES3 Receiver/s\_axis\_aclk in case of SPDIF/AES3 Transmitter). This option needs to be set for both SPDIF/AES3 Receiver and Transmitter. The actual depth of the FIFO is one less than what is configured.

Figure 4-2 shows the Customize IP dialog box with information about customizing parameters in the Receive Mode.

| A                                                                                                                                    | Re-customize IP (on xhdl3181)                                                                                                                  | ×      |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| SPDIF/AES3 (2.0)                                                                                                                     |                                                                                                                                                | 4      |

| Documentation Documentation                                                                                                          |                                                                                                                                                |        |

| Show disabled ports                                                                                                                  | Component Name spdif_0                                                                                                                         |        |

|                                                                                                                                      | SPDIF Mode                                                                                                                                     |        |

| + AXM_LITE<br>+ SPDR_RX<br>aud_clk_i W_AXISTREAM +<br>s_wij.ack spdii_intempt<br>s_wij.ack spdii_intempt<br>m_axis_ack<br>m_axis_ack | <ul> <li>Receiver Transmitter</li> <li>FIFO Depth 512 </li> <li>Enable Channel Status Registers</li> <li>Enable User Data Registers</li> </ul> |        |

|                                                                                                                                      | OK                                                                                                                                             | Cancel |

Figure 4-2: SPDIF/AES3 in Receive Mode

In addition to the stated SPDIF/AES3 Mode and FIFO Depth, select the following options for the SPDIF/AES3 in receive mode.

- **Enable Channel Status Registers** Set this option when SPDIF/AES3 is selected in Receive mode. When set, SPDIF/AES3 Receiver captures the channel status data from the audio frames in the internal registers.

- **Enable User Data Registers** Set this option when SPDIF/AES3 is selected in Receive mode. When set, SPDIF/AES3 Receiver captures the channel status data from the audio frames in the internal registers.

#### **Output Generation**

For details, see the Vivado Design Suite User Guide: Designing with IP (UG896) [Ref 3].

## **Constraining the Core**

This section defines the constraint requirements of the SPDIF/AES3 endpoint example design. An example Xilinx Design Constraints (XDC) is provided with the example design, which implements the constraints defined in this chapter.

When a Virtex<sup>®</sup>-7 FPGA is selected as the target device, the XDC is generated for an XC7VX485TFFG1157-1 device as an example. The example designs and XDCs can be retargeted for other devices.

Information provided in this section indicates which constraints to modify when targeting devices other than those shown in the example designs.

### **Required Constraints**

This section is not applicable for this IP core.

#### Device, Package, and Speed Grade Selections

The SPDIF/AES3 cores can be implemented in the devices listed in the IP Facts table on page 4 with the following attributes:

- Large enough to accommodate the cores

- With a fast enough speed grade to meet the frequency requirements

### **Clock Frequencies**

**IMPORTANT:** To operate the core at the highest performance rating, the following constraints must be present. Prorate these numbers if slower performance is desired.

```

create_clock -name "TS_AUD_CLK_I" -period 10 -waveform {0 5.0} [get_ports AUD_CLK_I]

create_clock -name "TS_AXI_ACLK" -period 20 -waveform {0 10.0} [get_ports

S_AXI_ACLK]

```

### **Clock Management**

This section is not applicable for this IP core.

### **Clock Placement**

This section is not applicable for this IP core.

## Banking

This section is not applicable for this IP core.

### **Transceiver Placement**

This section is not applicable for this IP core.

## I/O Standard and Placement

This section is not applicable for this IP core.

## Simulation

This section contains information about simulating IP in the Vivado Design Suite. For comprehensive information about Vivado simulation components, as well as information about using supported third-party tools, see the *Vivado Design Suite User Guide: Logic Simulation* (UG900) [Ref 5].

## Synthesis and Implementation