# AXI Universal Serial Bus (USB) 2.0 Device v5.0

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG137 November 18, 2015

# **Table of Contents**

#### **IP Facts**

#### **Chapter 1: Overview**

| Functional Description             | 5 |

|------------------------------------|---|

| Applications                       | 9 |

| Unsupported Features               | 9 |

| Licensing and Ordering Information | 9 |

#### **Chapter 2: Product Specification**

| Standards            | 11 |

|----------------------|----|

| Performance          | 11 |

| Resource Utilization | 13 |

| Port Descriptions    | 13 |

| Register Space       | 14 |

#### **Chapter 3: Designing with the Core**

| Clocking                          | 32 |

|-----------------------------------|----|

| Reset                             | 32 |

| Programming Sequence              | 32 |

| Protocol Description in ULPI Mode | 37 |

#### **Chapter 4: Design Flow Steps**

| Customizing and Generating the Core | 45 |

|-------------------------------------|----|

| Output Generation                   | 48 |

| Constraining the Core               | 48 |

| Simulation                          | 50 |

| Synthesis and Implementation        | 50 |

#### Chapter 5: Example Design

| Implementing the Example Design | 53 |

|---------------------------------|----|

| Simulating the Example Design   | 54 |

www.xilinx.com

#### Chapter 6: Test Bench

| ppendix A: Migrating and Upgrading                |   |

|---------------------------------------------------|---|

| Migrating to the Vivado Design Suite       56     | 5 |

| Upgrading in the Vivado Design Suite 56           | 5 |

| ppendix B: Debugging                              |   |

| Finding Help on Xilinx.com    57                  | 7 |

| Debug Tools                                       | 3 |

| Hardware Debug                                    | Ð |

| ppendix C: Additional Resources and Legal Notices |   |

| Xilinx Resources                                  | נ |

| References                                        | ) |

| Revision History                                  | L |

| Please Read: Important Legal Notices       61     | L |

Vivado Synthesis

# Introduction

The AXI USB 2.0 Device core provides a USB interface to a user design. This interface is suitable for USB-centric, high-performance designs, bridges, and legacy port replacement operations.

# Features

- AXI interface based on AXI4 specification.

- Burst lengths of 1 to 256 beats with INCR type transfers.

- Optional DMA mode to increase throughput during the data transfers.

- Optional feature support for unaligned transfers on the master interface.

- Supports High Speed and Full Speed USB 2.0 specification.

- Supports high speed, high bandwidth isochronous transactions.

- Supports up to eight endpoints, including one control endpoint 0. Endpoints 1 to 7 can be bulk, interrupt, or isochronous. Endpoints are individually configurable.

- Two ping-pong buffers for each endpoint except for endpoint 0.

- Optional USB error detection, updates error count, and generates error interrupt.

- Supports ULPI (Universal Transceiver Macrocell Interface (UTMI) + Low Pin Interface) to an external USB PHY.

- Access to ULPI PHY registers and parameterized ULPI PHY reset.

- Resume and reset detection in low-power mode.

- Resuming of host from low-power mode with remote wake-up signaling.

| LogiCORE IP Facts Table                   |                                                                                                                                       |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

|                                           | Core Specifics                                                                                                                        |  |

| Supported<br>Device Family <sup>(1)</sup> | UltraScale+™ Families,<br>UltraScale <sup>™</sup> Architecture, Zynq®-7000 All<br>Programmable SoC, Virtex®-7, Kintex®-7,<br>Artix®-7 |  |

| Supported User<br>Interfaces              | AXI4, ULPI                                                                                                                            |  |

| Resources                                 | Performance and Resource Utilization web page                                                                                         |  |

| Provided with Core                        |                                                                                                                                       |  |

| Design Files                              | Encrypted RTL                                                                                                                         |  |

| Example Design                            | Verilog and VHDL                                                                                                                      |  |

| Test Bench                                | Provided                                                                                                                              |  |

| Constraints File                          | Xilinx Design Constraints (XDC)                                                                                                       |  |

| Simulation<br>Model                       | Not Provided                                                                                                                          |  |

| Supported<br>S/W Driver <sup>(2)</sup>    | Standalone and Linux                                                                                                                  |  |

| Tested Design Flows <sup>(3)</sup>        |                                                                                                                                       |  |

| Design Entry                              | Vivado® Design Suite                                                                                                                  |  |

| Simulation                                | For supported simulators, see the<br>Xilinx Design Tools: Release Notes Guide.                                                        |  |

Support

Provided by Xilinx at the Xilinx Support web page

#### Notes:

Synthesis

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- Standalone driver details can be found in the SDK directory (*<install\_directory*>/doc/usenglish/xilinx\_drivers.htm). Linux OS and driver support information is available from the <u>Xilinx Wiki page</u>.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

The USB 2.0 protocol multiplexes many devices over a single, half-duplex, serial bus. The bus runs at 480 Mb/s (High Speed) or at 12 Mb/s (Full Speed) and is designed to be plug-and-play. The host always controls the bus and sends tokens to each device specifying the required action. Each device has an address on the USB 2.0 bus and has one or more endpoints that are sources or sinks of data. All devices have the system control endpoint (endpoint 0).

## **Functional Description**

The AXI USB 2.0 Device has eight endpoints: one control endpoint (endpoint 0) and seven user endpoints. Endpoint 0 has different requirements compared to the seven user endpoints. Endpoint 0 handles control transactions only, which start with an 8-byte setup packet and are then followed by zero or more data packets. The setup packet is always stored in a dedicated location in the Dual Port Random Access Memory (DPRAM) at an address offset of 0x80. When a setup packet is received, the SETUPPkt bit of the Interrupt Status Register (ISR) is set. Data packets are a maximum of 64 bytes. These data packets are stored in a single bidirectional data buffer set up by the configuration memory of Endpoint 0, located at the address offset 0x0 in the DPRAM. When a data packet is transmitted or received successfully, the FIFOBufFree and FIFOBufRdy bits of the Interrupt Status Register (ISR) are set respectively.

The seven user endpoints of the AXI USB 2.0 Device can be configured as bulk, interrupt, or isochronous. In addition, endpoints can be configured as INPUT (to the host) or OUTPUT (from the host). Each of these endpoints has two ping-pong buffers of the same size for endpoint data. The user endpoints data buffers are unidirectional, and are configured by the Endpoint Configuration and Status register of the respective endpoint. The size of the buffers can be configured from 0 to 512 bytes for bulk, 64 bytes for interrupt, and up to 1,024 bytes for isochronous endpoints.

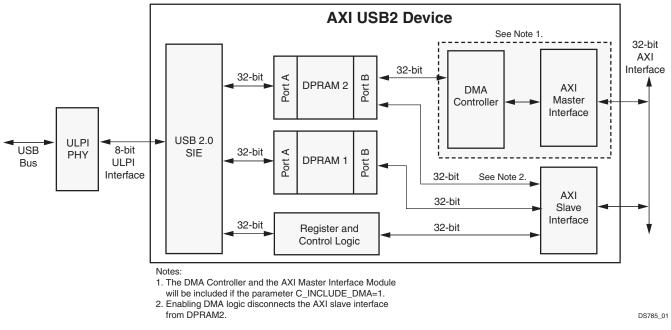

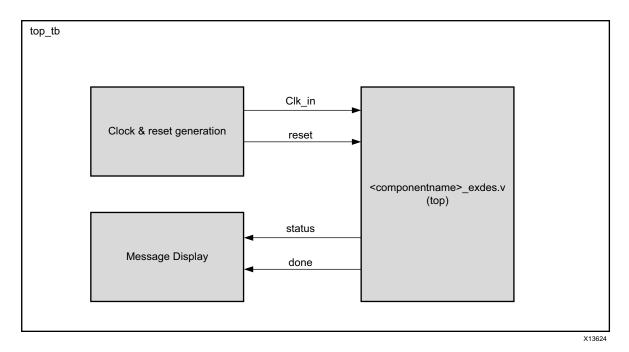

The AXI USB 2.0 Device core with the AXI and ULPI interfaces is shown in Figure 1-1.

Figure 1-1: AXI USB 2.0 Device with AXI and ULPI Interfaces

When the host attempts to send data to an endpoint of the device, it sends a token which consists of an OUT PID along with the address of the device and the endpoint number, followed by the data. The device uses handshake packets to report the status of the data transaction if, and only if, the token and data are received without any USB errors, such as Bit Stuff, PID, and CRC errors. Handshake packets indicate successful reception of data, flow control, and halt conditions.

To receive data, the host sends a token which consists of an IN PID along with the device address and endpoint number, then waits for data from the device. The device responds with the requested data to the host if the token is received without any USB errors. The device then waits for the handshake packet.

## **Register and Control Logic**

The AXI USB 2.0 Device core includes 32-bit registers, which provide control and status information for the core. These registers are accessible from the AXI Slave interface. For more information on the registers, see Register Description in Chapter 2.

## USB 2.0 Serial Interface Engine (SIE)

The USB 2.0 Serial Interface Engine (SIE) handles the serialization and de-serialization of USB traffic at the byte level and the multiplexing and demultiplexing of USB data to and from the endpoints of the core. The SIE also handles USB 2.0 state transitions, such as suspend, resume, USB reset, and remote wake-up signaling (to wake up the host from the suspend mode).

The SIE interfaces to the PHY using a ULPI interface that requires 12 pins. Data to the FPGA from the USB is received from the PHY, error checked, and loaded into the appropriate area of the DPRAM. Data from the FPGA that is to be sent over the USB is loaded from the DPRAM, protocol wrapped and then when the protocol allows, presented to the PHY, 1-byte at a time. Details of the ULPI interface are beyond the scope of this document.

If any packet has USB errors, the SIE ignores and discards it. The SIE increments the respective USB error count in the Error Count Register (ECR) and sets the respective USB error bits in the Interrupt Status Register (ISR).

The status of the current USB transactions is signaled by the SIE to the Interrupt Status Register (ISR). Certain conditions can be enabled through the IER to generate an interrupt.

Control of the SIE comes from four sources:

- 1. The lower 64 bytes of the DPRAM contain the control and status locations for each endpoint.

- 2. The Control and Status registers provide overall start and stop, status indication, enabling of interrupts using status register bits, address control on USB, current Start of Frame timing information, and endpoint Buffer Ready indication.

- 3. The logic of the SIE module is coded to reflect the requirements of Chapter 8 of the USB 2.0 Specification.

- 4. The USB physical bus is connected to the SIE over the ULPI PHY interface. The SIE natively implements the ULPI protocol.

#### **Dual Port Block RAM (DPRAM)**

The DPRAM is the data storage area between the SIE and AXI interface. Port A of the DPRAM is used by the SIE and Port B is used by the Processor/DMA Controller. Both ports are 32-bits wide. The AXI USB 2.0 Device uses two sets of four Block RAMs implemented as 64 × 8 bits (DPRAM1) and 2 K × 8 bits each (DPRAM2), with dual asynchronous clock ports. Data from the USB 2.0 Device is routed to the DPRAM by the SIE through Port A. The firmware or hardware being used accesses the data through Port B over the AXI Slave Interface. Data being input to the AXI USB 2.0 Device is loaded through the AXI Slave Interface to Port B, into appropriate locations in the DPRAM. When the host requests data from the device, the SIE accesses this data from Port A.

The DPRAM is seen by the SIE as DPRAM1 and DPRAM2. DPRAM2 has seven endpoint FIFOs for endpoint 1 to 7. DPRAM1 has the endpoint 0 FIFO and the control register area which defines how the memory is arranged and reports the status of each FIFO buffer (ready, not ready or count). Each FIFO is double buffered to help support the high throughput possible with USB 2.0. One buffer can be used for a current USB transaction, while the other buffer is available to the user application for processing. The SIE treats the storage area as FIFOs. The firmware or hardware can access the storage as ordinary RAM over the AXI Slave Interface.

## **AXI Slave Interface**

The AXI Slave interface in the core performs the following operations:

- Responds to AXI transactions to read from or write to the 32-bit control registers, status registers, and DPRAM.

- Supports byte, half word, and word transfers for the DPRAM, but only word transfers are supported for the registers.

## **AXI Master Interface**

The AXI Master interface in the core performs the following operations:

- Performs read and write transactions as a AXI master in DMA mode.

- In DMA mode, interrupts are generated based on DMA Done and DMA Error conditions.

## **Direct Memory Access (DMA) Controller**

The DMA controller is included in the AXI USB 2.0 Device core if the "Enable DMA Support" parameter is set to 1. The DMA controller provides simple DMA services between DPRAM2 and an external memory device or peripheral on the AXI interface. The DMA controller transfers data from a source address to a destination address without processor intervention for a given length.

It provides programmable registers (for both directions read from and write to DPRAM2), source address, destination address, and transfer length. The source and destination address counters are increment only. It also supports AXI burst transfers. The DMA controller in the core performs data transfers between DPRAM2K and external memory only.

In a DMA transfer, the DPRAM2 address should always be a word-aligned address. A user-configurable parameter "Enable unaligned transactions" is defined to configure the support of un-aligned external memory addresses. When the parameter "Enable unaligned transactions" is set to 1, the DMA controller takes care of the data re-alignment and the DMA source or destination registers can be un-aligned addresses depending on the direction bit in the DMA control register. When "Enable unaligned transactions" is set to 0, the DMA controller supports only aligned addresses.

#### ULPI PHY

The USB PHY can be any ULPI-compliant PHY. The primary function of the PHY is to manage the bit-level serialization and de-serialization of USB 2.0 traffic. To do so, it must detect and recover the USB clock. The clock runs at 480 MHz, a speed that is too fast for practical implementation on the FPGA. Because 480 MHz is also too fast for the USB SIE clock, the

PHY interfaces to the SIE on a byte serial basis and generates a 60 MHz clock which runs on the SIE side of the USB 2.0 Device.

# **Applications**

The AXI USB 2.0 Device core supports interrupt, bulk and isochronous transactions. The core can be used in applications such as:

- USB-enabled keyboard or mouse devices

- Mass storage devices

- Microphone and speaker device applications

## **Unsupported Features**

The following features are not supported in this core.

- Host functionality

- USB On-The-Go (OTG)

# **Licensing and Ordering Information**

#### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado design tools have several license check points for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following Vivado design tools.

- Vivado Synthesis

- Vivado Implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** *IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.*

## License Type

This Xilinx® LogiCORE<sup>™</sup> IP module is provided under the terms of the <u>Xilinx Core License</u> <u>Agreement</u>. The module is shipped as part of the Vivado® Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information on pricing and availability.

For more information, visit the AXI USB 2.0 Device product web page.

Information about other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual</u> <u>Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

Chapter 2

# **Product Specification**

# Standards

The AXI USB 2.0 Device core supports the following industry standards at the interface level.

- AXI4 Full/lite interface

- ULPI interface

This core supports the AXI4-Lite interface for register access and AXI4 interface for DMA operations. The ULPI interface is used for PHY connectivity.

# Performance

The AXI USB 2.0 Device core is characterized according to the benchmarking methodology described in the *Vivado Design Suite User Guide: Designing with IP* (UG896) [Ref 1]. Table 2-1 shows the results of the characterization runs.

| Family   | Speed Grade | F <sub>max</sub> | (MHz) |

|----------|-------------|------------------|-------|

| ганну    |             | AXI4-Lite        | AXI4  |

| Virtex-7 | -1          | 160              | 160   |

|          | -2          | 200              | 200   |

|          | -3          | 220              | 220   |

| Kintex-7 | -1          | 160              | 160   |

|          | -2          | 200              | 200   |

|          | -3          | 220              | 220   |

| Artix-7  | -1          | 150              | 150   |

|          | -2          | 180              | 180   |

|          | -3          | 200              | 200   |

Table 2-1: Maximum Frequencies

www.xilinx.com

The target  $F_{Max}$  is influenced by the exact system and is provided for guidance. It is not a guaranteed value across all systems.

*Note:* Characterization results for Zynq-7000 devices are similar to the results for the devices listed in Table 2-1.

## Throughput

To measure the system throughput of the AXI USB 2.0 Device core, a Kintex®-7 system is used similar to Figure 1-1 and tested on a Xilinx KC705 board.

For this test, the firmware running on the KC705 evaluation board configured as a mass storage device or isochronous device with different applications. A Windows application running on a Windows Desktop PC sets up the mass storage device for the throughput test on its BULK IN endpoint. The Windows application has an option of selecting the amount of traffic being sent on the bus for the throughput test. When the option was selected, the Windows application sets up the mass storage device to send the selected amount of data. Upon completion of the data transfer, the result is displayed on the Windows screen in MB/s. The throughput is measured using the amount of data sent over the bus and the time taken for transmission. A LeCroy USB analyzer is used to capture the transactions on the bus. The throughput results are based on the number of USB data packets received between two SOF packets. The throughput numbers are shown in Table 2-2 and Table 2-3.

| Throughput in the Functional Simulations    | Throughput on the KC705 Board               |

|---------------------------------------------|---------------------------------------------|

| 12 packets per micro frame = 49,152,000 B/s | 11 packets per micro frame = 45,056,000 B/s |

*Note:* In BULK IN mode, the performance of the device depends on the number of data transfer packets that the host application can initiate between the two SOFs. The throughput differs with the OS capability and load.

| Throughput in the Functional Simulations | Throughput on KC705 Board            |

|------------------------------------------|--------------------------------------|

| 3 packets per micro frame = 24 MB/s      | ~3 packets per micro frame = 23 MB/s |

# **Resource Utilization**

For details about Resource Utilization, visit <u>Performance and Resources Utilization</u> web page

# **Port Descriptions**

A description of the I/O signals for the AXI USB 2.0 Device core is provided in Table 2-4.

| Signal Name      | Interface           | I/O | Initial<br>State | Description                                                                                                                                   |  |

|------------------|---------------------|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| m_axi_aclk       | Clock               | Ι   | NA               | AXI Master Clock                                                                                                                              |  |

| m_axi_aresetn    | Reset               | Ι   | NA               | AXI Master Reset, active-Low                                                                                                                  |  |

| s_axi_aclk       | Clock               | Ι   | NA               | AXI Slave Clock                                                                                                                               |  |

| s_axi_aresetn    | Reset               | Ι   | NA               | AXI Slave Reset, active-Low                                                                                                                   |  |

| m_axi_*          | M_AXI               | NA  | NA               | AXI4 master interface signals for read and write channels. The m_axi interface is only available when DMA support is enabled <sup>(2)</sup> . |  |

| s_axi_*          | S_AXI               | NA  | NA               | AXI4-Lite Slave Interface signals <sup>(2)</sup>                                                                                              |  |

| usb_irpt         | System              | 0   | 0                | USB Interrupt                                                                                                                                 |  |

| ulpi_clock       | ULPI                | Ι   | NA               | All USB protocol interface signals are synchronous to this clock                                                                              |  |

| ulpi_dir         | ULPI                | Ι   | NA               | Direction of data flow between the PHY and SIE                                                                                                |  |

| ulpi_next        | ULPI                | Ι   | NA               | Indicator of when the PHY is ready for the next bit                                                                                           |  |

| ulpi_stop        | ULPI                | 0   | 0                | Indicator that transmission of last byte is complete                                                                                          |  |

| ulpi_data_i[7:0] | ULPI                | Ι   | NA               | Input data from the PHY to the SIE                                                                                                            |  |

| ulpi_reset(2)    | ULPI                | 0   | 1                | Reset to the ULPI PHY                                                                                                                         |  |

| ulpi_data_o[7:0] | ULPI                | 0   | 0                | Output data from the SIE to the PHY                                                                                                           |  |

| ulpi_data_t      | ULPI                | 0   | 0                | ULPI_Data is a 3-state port with<br>ULPI_Data_I as the IN port,<br>ULPI_Data_O as the OUT port, and<br>ULPI_Data_T as the 3-state output      |  |

| configured       | Debug<br>(Optional) | 0   | 0                | Used for USB 2.0 Certification – Test mode NAK                                                                                                |  |

| spare1           | Debug<br>(Optional) | 0   | 0                | Used for USB 2.0 Certification – Test mode J                                                                                                  |  |

Table 2-4: AXI USB I/O Signal Description

| Signal Name       | Interface           | I/O | Initial<br>State | Description                                                                                                                                       |

|-------------------|---------------------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| spare2            | Debug<br>(Optional) | 0   | 0                | Used for USB 2.0 Certification – Test mode K                                                                                                      |

| vbus_detect       | Debug<br>(Optional) | 0   | 0                | 0: Valid VBUS has not been detected<br>1: Valid VBUS has been detected                                                                            |

| show_currentspeed | Debug<br>(Optional) | 0   | 0                | 0: Full Speed<br>1: High Speed                                                                                                                    |

| running           | Debug<br>(Optional) | 0   | 0                | 0: The SIE is in reset state and does not respond to<br>USB traffic<br>1: The SIE is finished USB reset and is ready to<br>respond to USB traffic |

| suspended         | Debug<br>(Optional) | 0   | 0                | 0: AXI USB 2.0 Device core has not been suspended<br>1: AXI USB 2.0 Device core has been suspended                                                |

| disconnected      | Debug<br>(Optional) | 0   | 0                | 0: AXI USB 2.0 Device core is connected<br>1: AXI USB 2.0 Device is disconnected                                                                  |

#### Table 2-4: AXI USB I/O Signal Description (Cont'd)

1. See the Vivado AXI Reference Guide (UG1037) [Ref 2] for AXI4, AXI4-Lite and AXI4-Stream Signals

# **Register Space**

#### **Register Bit Ordering**

All registers use little endian bit ordering where bit 31 is the MSB and bit 0 is the LSB. Table 2-5 shows the bit ordering.

#### Table 2-5: Register Bit Ordering

| 31  | 30 | 29 | <br>2 | 1 | 0   |

|-----|----|----|-------|---|-----|

| MSB |    |    |       |   | LSB |

#### **Register Description**

The memory map for the AXI USB 2.0 Device core is shown in Table 2-6 which includes endpoint configuration space (offset 0x0000), setup packet storage space (offset 0x0080), RAM for endpoint 0 buffer (offset 0x0088), register space for the USB registers (offset 0x0100), and RAM for endpoint 1 to 7 buffers (offset 0x4000). Table 2-7 lists the mapping for endpoint configuration space. All offsets are word offsets.

#### Table 2-6:Register Address Map

| Register Name                                                   | Base Address + Offset (hex) | Reset Value (hex) | Access <sup>(1)(2)</sup> |

|-----------------------------------------------------------------|-----------------------------|-------------------|--------------------------|

| Endpoint Configuration and Status<br>Registers                  | C_BASEADDR + 0x0000         | 0x00000000        | R/W                      |

| Setup Packet Storage Word 0 <sup>(2)</sup>                      | C_BASEADDR + 0x0080         | 0x0000000         | R                        |

| Setup Packet Storage Word $1^{(2)}$                             | C_BASEADDR + 0x0084         | 0x0000000         | R                        |

| RAM for Endpoint 0 Buffer <sup>(6)</sup>                        | C_BASEADDR + 0x0088         | 0x0000000         | R/W                      |

| USB Address Register                                            | C_BASEADDR + 0x0100         | 0x0000000         | R/W                      |

| Control Register                                                | C_BASEADDR + 0x0104         | 0x0000000         | R/W                      |

| Interrupt Status Register                                       | C_BASEADDR + 0x0108         | 0x0000000         | R                        |

| Frame Number Register                                           | C_BASEADDR + 0x010C         | 0x0000000         | R                        |

| Interrupt Enable Register                                       | C_BASEADDR + 0x0110         | 0x0000000         | R/W                      |

| Buffer Ready Register                                           | C_BASEADDR + 0x0114         | 0x0000000         | R/W                      |

| Test Mode Register                                              | C_BASEADDR + 0x0118         | 0x0000000         | R/W                      |

| Error Count Register <sup>(7)</sup>                             | C_BASEADDR + 0x011C         | 0x0000000         | R                        |

| ULPI PHY Access Register <sup>(8)</sup>                         | C_BASEADDR + 0x0120         | 0x0000000         | R/W                      |

| DMA Software Reset Register <sup>(3)(4)</sup>                   | C_BASEADDR + 0x0200         | 0x0000000         | W                        |

| DMA Control Register <sup>(4)</sup>                             | C_BASEADDR + 0x0204         | 0x0000000         | R/W                      |

| DMA Source Address Register <sup>(10)</sup>                     | C_BASEADDR + 0x0208         | 0x0000000         | R/W                      |

| DMA Source Address Register (LSB 32 bit) <sup>(9)</sup>         | C_BASEADDR + 0x0308         | 0x00000000        | R/W                      |

| DMA Source Address Register (MSB 32 bit) <sup>(9)</sup>         | C_BASEADDR + 0x030C         | 0x00000000        | R/W                      |

| DMA Destination Address Register <sup>(10)</sup>                | C_BASEADDR + 0x020C         | 0x0000000         | R/W                      |

| DMA Destination Address Register<br>(LSB 32 bit) <sup>(9)</sup> | C_BASEADDR + 0x0310         | 0x00000000        | R/W                      |

| DMA Destination Address Register<br>(MSB 32 bit) <sup>(9)</sup> | C_BASEADDR + 0x0314         | 0x00000000        | R/W                      |

| DMA Length Register <sup>(4)</sup>                              | C_BASEADDR + 0x0210         | 0x00000000        | R/W                      |

| DMA Status Register <sup>(4)</sup>                              | C_BASEADDR + 0x0214         | 0x0000000         | R/W                      |

#### Table 2-6: Register Address Map (Cont'd)

| Register Name                               | Base Address + Offset (hex) | Reset Value (hex) | Access <sup>(1)(2)</sup> |

|---------------------------------------------|-----------------------------|-------------------|--------------------------|

| RAM for Endpoint 1–7 Buffers <sup>(6)</sup> | C_BASEADDR + 0x4000         | 0x0000000         | R/W                      |

#### Notes:

- 1. R/W Read and Write access

- 2. R Read Only access. Write to these registers has no effect

- 3. W Write Only access. Reading of these registers returns zero

- 4. This register is included in the design if the parameter C\_INCLUDE\_DMA = 1

- 5. RAM for endpoint 0 buffer should be 64 bytes, EpBase\_ADDRESS (endpoint 0)+ 0x40 should not exceed 0x00FF and master address width is 32.

- RAM for endpoint 1–7 buffers range (C\_BASEADDR + 0x4000) to (C\_BASEADDR + 0x4000) + 0x1FFF. When the DMA logic is enabled the RAM for endpoint 1–7 buffers cannot be accessed through the AXI slave interface; It is only accessible through the DMA controller.

- 7. This register is not included in the design if the parameter C\_INCLUDE\_USBERR\_LOGIC = 0. But the SIE performs USB error checks as part of the USB 2.0 specification and ignores any error packets received.

- 8. This register is defined to access the ULPI PHY registers.

9. This register is valid only when dma is enabled and master address width is greater than 32.

10. This register is included in the design if the parameter C\_INCLUDE\_DMA = 1 and master address width is equal to 32.

## **Endpoint Configuration and Status Registers**

The Endpoint Configuration and Status registers control the operational characteristics of each endpoint and reports its current condition. The total endpoint configuration register space is divided between the eight endpoints of the USB 2.0 Device as shown in Table 2-7.

| Address Offset | Memory/Register Space |  |  |

|----------------|-----------------------|--|--|

| 0x0000         | Endpoint 0            |  |  |

| 0x0010         | Endpoint 1            |  |  |

| 0x0020         | Endpoint 2            |  |  |

| 0x0030         | Endpoint 3            |  |  |

| 0x0040         | Endpoint 4            |  |  |

| 0x0050         | Endpoint 5            |  |  |

| 0x0060         | Endpoint 6            |  |  |

| 0x0070         | Endpoint 7            |  |  |

|                |                       |  |  |

Table 2-7: Endpoint Configuration Registers (C\_BASEADDR + Address Offset)

Each endpoint has four 32-bit registers that describe the behavior of the endpoint. These registers are located sequentially and arranged by endpoint number as shown in Table 2-8.

Table 2-8: Endpoint Configuration Register

| Address Offset | Memory/Register Space                      |

|----------------|--------------------------------------------|

| 0x0000         | Endpoint configuration and status register |

| 0x0004         | Reserved                                   |

| 0x0008         | Buffer 0 count: 0 to 1,024                 |

| 0x000C         | Buffer 1 count: 0 to 1,024                 |

The bit description for the Endpoint Configuration and Status registers is given in Table 2-9. All the bits of this register can be modified by the firmware. Under normal operation, some of the bits are modified by the USB SIE itself, and only their initial values need to be set by the firmware.

| Table 2-9: | Endpoint Configuration and Status Register (C_BASEADDR + 0x0000) |

|------------|------------------------------------------------------------------|

|------------|------------------------------------------------------------------|

| Bits | Name <sup>(1)(2)</sup> | Access | Reset<br>Value | Description                                                                                           |

|------|------------------------|--------|----------------|-------------------------------------------------------------------------------------------------------|

| 31   | EpValid <sup>(3)</sup> | R/W    | 0              | 0: Disables the endpoint<br>1: Enables the endpoint                                                   |

| 30   | EpStall                | R/W    | 0              | 0: Endpoint accepts INs and OUTs<br>1: Endpoint responds to the host only with a<br>STALL             |

| 29   | EpOutIn                | R/W    | 0              | 0: Core receives data from the host (OUT from<br>host)<br>1: Core sends data to the host (IN to host) |

| Bits  | Name <sup>(1)(2)</sup>   | Access | Reset<br>Value | Description                                                                                                                                                                                                                          |

|-------|--------------------------|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28    | EpIso <sup>(4)</sup>     | R/W    | 0              | 0: Not an isochronous endpoint<br>1: Isochronous endpoint                                                                                                                                                                            |

| 27    | EpDataTgl <sup>(5)</sup> | R/W    | 0              | 0: Next DATA packet must be a DATA0 packet<br>1: Next DATA packet must be a DATA1 packet                                                                                                                                             |

| 26    | EpBufSel <sup>(6)</sup>  | R/W    | 0              | 0: Buffer 0 is used<br>1: Buffer 1 is used                                                                                                                                                                                           |

| 25–15 | EpPktSze <sup>(7)</sup>  | R/W    | 0              | Endpoint packet size                                                                                                                                                                                                                 |

| 14–13 | EpIsoTrans               | R/W    | 0              | Number of Isochronous transfers supported in a (micro)frame by the endpoint.<br>00: Supports one isochronous transaction<br>01: Supports two isochronous transactions<br>10: Supports three isochronous transactions<br>11: Reserved |

| 12–0  | EpBase <sup>(8)</sup>    | R/W    | 0              | Base offset of the buffers in the DPRAM                                                                                                                                                                                              |

#### Table 2-9: Endpoint Configuration and Status Register (C\_BASEADDR + 0x0000) (Cont'd)

#### Notes:

- 1. The VALID, STALL, OUT\_IN, and ISO bits are set by the firmware to define how the endpoint operates. For example, to set up the endpoint to receive bulk OUTs from the host, set EpValid = 1, EpOutIn = 0, EpStall = 0, and EpIso = 0.

- 2. The EpDataTgl bit is toggled automatically by the SIE during the data stage of a transfer for the DATA0/DATA1 synchronization that is required. This bit can also be explicitly set when needed, for example during the status stage of a control transfer. The EpBufSel bit is also automatically modified by the SIE; the firmware only needs to set its initial value.

- 3. EpValid is an Master Enable bit for the respective endpoint.

- 4. EpIso enables endpoint as an isochronous endpoint.

- 5. The SIE uses EpDataTgl to detect DATA PID toggle errors during the data transfers and its weak form of synchronization technique. This bit can be explicitly set in response to a firmware command.

- 6. Used to support ping-pong buffers during data transfers. If this bit is set then the SIE toggles the buffer access during data transfers, one at each time.

- 7. EpPktSze refers to maximum packet size limited to the respective endpoint.

- 8. EpBase is word addressable and the endpoint buffer address should always be right shifted by 2 before writing EpBase.

## Buffer Count Register0 (BCR0)

The Buffer 0 Count registers shown in Table 2-10, indicate the size of data in bytes. If the endpoint is an OUT endpoint, then the SIE sets the value of this register at the end of a successful reception from the host. If the endpoint is an IN endpoint, then the firmware sets the value of this register before transmission.

These registers are 32-bit wide and have R/W access.

| Table 2-10: | Buffer Count Register0 (C_BASEADDR + 0x0008) |  |

|-------------|----------------------------------------------|--|

|-------------|----------------------------------------------|--|

| Bits  | Name        | Access | Reset Value | Description                |

|-------|-------------|--------|-------------|----------------------------|

| 31–11 | Reserved    | NA     | -           | Reserved                   |

| 10-0  | OutInPktCnt | R/W    | 0           | Packet count in the buffer |

## Buffer Count Register1 (BCR1)

The Buffer 1 Count registers shown in Table 2-11 indicate the size of data in bytes. If the endpoint is an OUT endpoint, the SIE sets the value of this register at the end of a successful reception from the host. If the endpoint is an IN endpoint, the firmware sets the value of this register before transmission. These registers are 32-bit wide and have R/W access.

Table 2-11: Buffer Count Register1 (C\_BASEADDR + 0x000C)

| Bits  | Name        | Access | Reset Value | Description                |

|-------|-------------|--------|-------------|----------------------------|

| 31–11 | Reserved    | NA     | -           | Reserved                   |

| 10-0  | OutInPktCnt | R/W    | 0           | Packet count in the buffer |

### **USB Address Register (UAR)**

The USB Address register, shown in Table 2-12 contains the host-assigned USB address of the device. There are 128 possible USB devices on the USB; therefore, the register takes values from 0 to 127. The lower seven bits of the register [6:0] are used to set the address. An address of 0 indicates that the device is un-enumerated. Address 0 is the default address of all USB devices at plug-in time and the address value on hardware reset. This register is 32-bits wide and has R/W access.

Table 2-12:

USB Address Register (C\_BASEADDR + 0x0100)

| Bits | Name     | Access | Reset Value | Description                             |

|------|----------|--------|-------------|-----------------------------------------|

| 31–7 | Reserved | NA     | -           | Reserved                                |

| 6–0  | USBAddr  | R/W    | 0           | Indicates the USB address of the device |

## **Control Register (CR)**

As shown in Table 2-13, the MstRdy bit indicates SIE operation. When clear, the USB SIE is paused and does not respond to any USB activity. When set, the SIE operates normally. The RmteWkup bit initiates remote wake-up signaling to the host when the device has been suspended by the host. The core generates a USBRsm interrupt after the successful completion of remote wake-up signaling with the host. The RmteWkup bit remains set until the firmware clears it.

| Table 2-13: | <b>Control Register</b> (C_ | BASEADDR + 0x0104) |

|-------------|-----------------------------|--------------------|

|-------------|-----------------------------|--------------------|

| Bits | Name     | Access | Reset Value | Description                                                                              |

|------|----------|--------|-------------|------------------------------------------------------------------------------------------|

| 31   | MstRdy   | R/W    | 0           | 0: SIE is paused and does not respond to any USB<br>activity<br>1: SIE operates normally |

| 30   | RmteWkup | R/W    | 0           | 0: SIE does nothing<br>1: SIE sends remote wake-up signaling to host                     |

| Bits | Name        | Access | Reset Value | Description                                                                                                                                   |

|------|-------------|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 29   | SIE_SoftRst | R/W    | 0           | 0: Normal operation<br>1: SIE gets reset and starts from PHY re-initialization.<br>This bit resets the Address and Buffer Ready<br>Registers. |

| 28–0 | Reserved    | R      | -           | Reserved                                                                                                                                      |

Table 2-13: Control Register (C\_BASEADDR + 0x0104) (Cont'd)

## Interrupt Status Register (ISR)

The Interrupt Status Register (ISR) shown in Table 2-14, reports status on the operation of the AXI USB 2.0 Device core. The bits in this register are cleared as soon as they are read.

Table 2-14:

Interrupt Status Register (C\_BASEADDR + 0x0108)

| Bits | Name                      | Access | Reset Value | Description                                                                                                                                                           |

|------|---------------------------|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31   | Reserved                  | NA     | -           | Reserved                                                                                                                                                              |

| 30   | ULPIAccComp               | R      | 0           | 0: ULPI PHY Access Complete has not occurred<br>1: ULPI PHY Access Complete has occurred                                                                              |

| 29   | BitStufErr <sup>(2)</sup> | R      | 0           | 0: Bit Stuff error has not occurred<br>1: Bit Stuff error has occurred                                                                                                |

| 28   | PidErr <sup>(2)</sup>     | R      | 0           | 0: PID error has not occurred<br>1: PID error has occurred                                                                                                            |

| 27   | CrcErr <sup>(2)</sup>     | R      | 0           | 0: CRC error has not occurred<br>1: CRC error has occurred                                                                                                            |

| 26   | DmaDne <sup>(1)</sup>     | R      | 0           | 0: DMA operation is not done<br>1: DMA operation is done                                                                                                              |

| 25   | DmaErr <sup>(1)</sup>     | R      | 0           | 0: DMA error has not occurred<br>1: DMA error has occurred                                                                                                            |

| 24   | USBRsm <sup>(3)</sup>     | R      | 0           | 0: Core has not received resume signaling from host<br>1: Core received resume signaling from host                                                                    |

| 23   | USBRst <sup>(3)</sup>     | R      | 0           | 0: Core has not received USB reset from host<br>1: Core received USB reset from host                                                                                  |

| 22   | USBSpnd <sup>(3)</sup>    | R      | 0           | 0: Core not in suspend state<br>1: Core in suspend state                                                                                                              |

| 21   | USBDsc <sup>(3)</sup>     | R      | 0           | 0: Core connected to host<br>1: Core is disconnected from host                                                                                                        |

| 20   | FIFOBufRdy                | R      | 0           | 0: Endpoint 0 packet has not been received by core<br>1: Endpoint 0 packet has been received by core                                                                  |

| 19   | FIFOBufFree               | R      | 0           | 0: Endpoint 0 packet has not been transmitted by<br>core<br>1: Endpoint 0 packet has been transmitted by core<br>This bit is valid only when bit 0 in the ISR is set. |

| Table 2-14: | Interrupt Status Register (C_BASEADDR + 0x0108) (Cont'd) |

|-------------|----------------------------------------------------------|

|-------------|----------------------------------------------------------|

| Bits | Name        | Access | Reset Value | Description                                                                                                     |

|------|-------------|--------|-------------|-----------------------------------------------------------------------------------------------------------------|

| 18   | SETUPPkt    | R      | 0           | 0: Endpoint 0 Setup packet has not been received by<br>core<br>1: Endpoint 0 Setup packet has been received     |

| 17   | SOFPkt      | R      | 0           | 0: Start of Frame packet has not been received by<br>core<br>1: Start of Frame packet has been received by core |

| 16   | HighSpd     | R      | 0           | 0: Core is running at Full Speed<br>1: Core is running at High Speed                                            |

| 15   | Ep7ProcBuf1 | R      | 0           | 0: Endpoint 7, buffer 1 not processed<br>1: Endpoint 7, buffer 1 processed                                      |

| 14   | Ep6ProcBuf1 | R      | 0           | 0: Endpoint 6, buffer 1 not processed<br>1: Endpoint 6, buffer 1 processed                                      |

| 13   | Ep5ProcBuf1 | R      | 0           | 0: Endpoint 5, buffer 1 not processed<br>1: Endpoint 5, buffer 1 processed                                      |

| 12   | Ep4ProcBuf1 | R      | 0           | 0: Endpoint 4, buffer 1 not processed<br>1: Endpoint 4, buffer 1 processed                                      |

| 11   | Ep3ProcBuf1 | R      | 0           | 0: Endpoint 3, buffer 1 not processed<br>1: Endpoint 3, buffer 1 processed                                      |

| 10   | Ep2ProcBuf1 | R      | 0           | 0: Endpoint 2, buffer 1 not processed<br>1: Endpoint 2, buffer 1 processed                                      |

| 9    | Ep1ProcBuf1 | R      | 0           | 0: Endpoint 1, buffer 1 not processed<br>1: Endpoint 1, buffer 1 processed                                      |

| 8    | Reserved    | NA     | -           | Reserved                                                                                                        |

| 7    | Ep7ProcBuf0 | R      | 0           | 0: Endpoint 7, buffer 0 not processed<br>1: Endpoint 7, buffer 0 processed                                      |

| 6    | Ep6ProcBuf0 | R      | 0           | 0: Endpoint 6, buffer 0 not processed<br>1: Endpoint 6, buffer 0 processed                                      |

| 5    | Ep5ProcBuf0 | R      | 0           | 0: Endpoint 5, buffer 0 not processed<br>1: Endpoint 5, buffer 0 processed                                      |

| 4    | Ep4ProcBuf0 | R      | 0           | 0: Endpoint 4, buffer 0 not processed<br>1: Endpoint 4, buffer 0 processed                                      |

| 3    | Ep3ProcBuf0 | R      | 0           | 0: Endpoint 3, buffer 0 not processed<br>1: Endpoint 3, buffer 0 processed                                      |

| 2    | Ep2ProcBuf0 | R      | 0           | 0: Endpoint 2, buffer 0 not processed<br>1: Endpoint 2, buffer 0 processed                                      |

| 1    | Ep1ProcBuf0 | R      | 0           | 0: Endpoint 1, buffer 0 not processed<br>1: Endpoint 1, buffer 0 processed                                      |

| Table 2-14: Interrupt Status Register (C | BASEADDR + 0x0108) (Cont'd) |

|------------------------------------------|-----------------------------|

|------------------------------------------|-----------------------------|

| Bits | Name        | Access | Reset Value | Description                                                                |

|------|-------------|--------|-------------|----------------------------------------------------------------------------|

| 0    | Ep0ProcBuf0 | R      |             | 0: Endpoint 0, buffer 0 not processed<br>1: Endpoint 0, buffer 0 processed |

#### Notes:

1. This bit is undefined if the parameter C\_INCLUDE\_DMA = 0.

2. This bit is undefined if the parameter C\_INCLUDE\_USBERR\_LOGIC = 0.

3. This bit indicates the current status of the AXI USB 2.0 Device core.

The AXI USB 2.0 Device core has a single interrupt line (USB\_Irpt) to indicate an interrupt. Interrupts are indicated by asserting the USB\_Irpt signal (transition of the USB\_Irpt from a logic 0 to a logic 1).

The Interrupt Enable Register (IER) allows specific bits of the Interrupt Status Register (ISR) to generate interrupts. The MstEnbl bit of the Interrupt Enable Register (IER) register allows all interrupts to be disabled simultaneously. The interrupt condition is cleared when the corresponding bit of the Interrupt Status Register (ISR) is cleared by writing a 1 to it. During power on, the USB\_Irpt signal is driven Low.

The following two conditions cause the USB\_Irpt signal to be asserted:

- If a bit in the ISR is 1 and the corresponding bit in the IER is 1.

- Changing an IER bit from a 0 to 1 when the corresponding bit in the ISR is already 1.

Two conditions cause the USB\_Irpt signal to be deasserted:

- Clearing a bit in the ISR, that is, by reading the ISR, provided that the corresponding bit in the IER is 1.

- Changing an IER bit from 1 to 0, when the corresponding bit in the ISR is 1.

When both deassertion and assertion conditions occur simultaneously, the USB\_Irpt signal is deasserted first, then is reasserted if the assertion condition remains TRUE.

#### Frame Number Register (FNR)

The Frame Number Register (FNR) shown in Table 2-15 is composed of two fields:

- Frame

- Microframe

Frames are sent once every 1 ms and denote the beginning of a USB frame. Host scheduling starts at the start of Frame Time.

**CAUTION!** The Microframe field is the result of additional Start of Frame tokens, sent once every 125 µs. When the USB is operated in High Speed mode, this can generate a potentially high rate of interrupts. Therefore, the interrupt enable of Start of Frame should be used with caution.

www.xilinx.com

Frame count values are of 11 bits and Microframe count values are of 3 bits.

|       |          |        | 0_0/10/2/10/2/1 | · • • • • • • • • • • • • • • • • • • • |

|-------|----------|--------|-----------------|-----------------------------------------|

| Bits  | Name     | Access | Reset Value     | Description                             |

| 31–14 | Reserved | NA     | -               | Reserved for future use                 |

| 13-3  | FrmNum   | R      | 0               | Frame numbers—0 to 2,047                |

| 2–0   | uFrmNum  | R      | 0               | Microframe numbers—0 to 7               |

Table 2-15:

Frame Number Register (C\_BASEADDR + 0x010C)

Interrupt Enable Register (IER)

The Interrupt Enable Register (IER) shown in Table 2-16 allows specific bits of the Interrupt Status Register (ISR) to generate interrupts. The MstEnbl bit of this register allows all interrupts to be disabled simultaneously. The interrupt condition is cleared when the corresponding bit of the Interrupt Status Register (ISR) is cleared. A specific bit of the IER can be cleared to prevent a long duration condition, such as USB reset, from continuously generating an interrupt.

| Bits | Name                      | Access | Reset Value | Description                                                                                     |

|------|---------------------------|--------|-------------|-------------------------------------------------------------------------------------------------|

| 31   | MstEnbl                   | R/W    | 0           | 0: Disables the setting of all other interrupts<br>1: Enables setting of all other interrupts   |

| 30   | ULPIAccComp               | R/W    | 0           | 0: Disables ULPI PHY Access Complete interrupt<br>1: Enables ULPI PHY Access Complete interrupt |

| 29   | BitStufErr <sup>(2)</sup> | R/W    | 0           | 0: Disables Bit Stuff error interrupt<br>1: Enable Bit Stuff error interrupt                    |

| 28   | PidErr <sup>(2)</sup>     | R/W    | 0           | 0: Disables PID error interrupt<br>1: Enables PID error interrupt                               |

| 27   | CrcErr <sup>(2)</sup>     | R/W    | 0           | 0: Disables CRC error interrupt<br>1: Enables CRC error interrupt                               |

| 26   | DmaDne <sup>(1)</sup>     | R/W    | 0           | 0: Disables DMA Done interrupt<br>1: Enables DMA Done interrupt                                 |

| 25   | DmaErr <sup>(1)</sup>     | R/W    | 0           | 0: Disables DMA Error interrupt<br>1: Enables DMA Error interrupt                               |

| 24   | USBRsm                    | R/W    | 0           | 0: Disables USB Resume interrupt<br>1: Enables USB Resume interrupt                             |

| 23   | USBRst                    | R/W    | 0           | 0: Disables USB reset interrupt<br>1: Enables USB reset interrupt                               |

| 22   | USBSpnd                   | R/W    | 0           | 0: Disables USB Suspend interrupt<br>1: Enables USB Suspend interrupt                           |

| 21   | USBDsc                    | R/W    | 0           | 0: Disables USB Disconnect interrupt<br>1: Enables USB Disconnect interrupt                     |

| 20   | FIFOBufRdy                | R/W    | 0           | 0: Disables FIFIOBufRdy interrupt<br>1: Enables FIFIOBufRdy interrupt                           |

Table 2-16:

Interrupt Enable Register (C\_BASEADDR + 0x0110)

| Bits | Name        | Access | Reset Value | Description                                                                                                 |

|------|-------------|--------|-------------|-------------------------------------------------------------------------------------------------------------|

| 19   | FIFOBufFree | R/W    | 0           | 0: Disables FIFOBufFree interrupt<br>1: Enables FIFOBufFree interrupt                                       |

| 18   | SETUPPkt    | R/W    | 0           | 0: Disables Setup Packet received interrupt<br>1: Enables Setup Packet received interrupt                   |

| 17   | SOFPkt      | R/W    | 0           | 0: Disables Start of Frame received interrupt<br>1: Enables Start of Frame received interrupt               |

| 16   | HighSpd     | R/W    | 0           | 0: Disables core operates in High Speed interrupt<br>1: Enables core operates in High Speed interrupt       |

| 15   | Ep7ProcBuf1 | R/W    | 0           | 0: Disables endpoint 7, buffer 1 processed interrupt<br>1: Enables endpoint 7, buffer 1 processed interrupt |

| 14   | Ep6ProcBuf1 | R/W    | 0           | 0: Disables endpoint 6, buffer 1 processed interrupt<br>1: Enables endpoint 6, buffer 1 processed interrupt |

| 13   | Ep5ProcBuf1 | R/W    | 0           | 0: Disables endpoint 5, buffer 1 processed interrupt<br>1: Enables endpoint 5, buffer 1 processed interrupt |

| 12   | Ep4ProcBuf1 | R/W    | 0           | 0: Disables endpoint 4, buffer 1 processed interrupt<br>1: Enables endpoint 4, buffer 1 processed interrupt |

| 11   | Ep3ProcBuf1 | R/W    | 0           | 0: Disables endpoint 3, buffer 1 processed interrupt<br>1: Enables endpoint 3, buffer 1 processed interrupt |

| 10   | Ep2ProcBuf1 | R/W    | 0           | 0: Disables endpoint 2, buffer 1 processed interrupt<br>1: Enables endpoint 2, buffer 1 processed interrupt |

| 9    | Ep1ProcBuf1 | R/W    | 0           | 0: Disables endpoint 1, buffer 1 processed interrupt<br>1: Enables endpoint 1, buffer 1 processed interrupt |

| 8    | Reserved    | NA     | -           | Reserved                                                                                                    |

| 7    | Ep7ProcBuf0 | R/W    | 0           | 0: Disables endpoint 7, buffer 0 processed interrupt<br>1: Enables endpoint 7, buffer 0 processed interrupt |

| 6    | Ep6ProcBuf0 | R/W    | 0           | 0: Disables endpoint 6, buffer 0 processed interrupt<br>1: Enables endpoint 6, buffer 0 processed interrupt |

| 5    | Ep5ProcBuf0 | R/W    | 0           | 0: Disables endpoint 5, buffer 0 processed interrupt<br>1: Enables endpoint 5, buffer 0 processed interrupt |

| 4    | Ep4ProcBuf0 | R/W    | 0           | 0: Disables endpoint 4, buffer 0 processed interrupt<br>1: Enables endpoint 4, buffer 0 processed interrupt |

| 3    | Ep3ProcBuf0 | R/W    | 0           | 0: Disables endpoint 3, buffer 0 processed interrupt<br>1: Enables endpoint 3, buffer 0 processed interrupt |

| 2    | Ep2ProcBuf0 | R/W    | 0           | 0: Disables endpoint 2, buffer 0 processed interrupt<br>1: Enables endpoint 2, buffer 0 processed interrupt |

| 1    | Ep1ProcBuf0 | R/W    | 0           | 0: Disables endpoint 1, buffer 0 processed interrupt<br>1: Enables endpoint 1, buffer 0 processed interrupt |

| 0    | Ep0ProcBuf0 | R/W    | 0           | 0: Disables endpoint 0, buffer 0 processed interrupt<br>1: Enables endpoint 0, buffer 0 processed interrupt |

#### Notes:

1. This bit is undefined if the parameter C\_INCLUDE\_DMA = 0.

2. This bit is undefined if the parameter C\_INCLUDE\_USBERR\_LOGIC = 0.

## Buffer Ready Register (BRR)

The Buffer Ready Register (BRR) has a buffer ready bit corresponding to each buffer of each endpoint, as shown in Table 2-17. The firmware sets each bit when that buffer is ready for either USB IN or USB OUT traffic. Until that bit is set, an attempted IN or OUT to/from the buffer results in a NAK to the host. The ability of the buffer to handle an IN or OUT is determined by the EpOutIn bit in the Configuration and Status register of the corresponding endpoint. It should be noted per the USB 2.0 Specification, endpoint 0 has only one buffer that handles IN or OUT.

| Bits  | Name       | Access | Reset Value | Description                                                                                                |

|-------|------------|--------|-------------|------------------------------------------------------------------------------------------------------------|

| 31–16 | Reserved   | R      | 0           | Reserved for future use                                                                                    |

| 15    | Ep7Buf1Rdy | R/W    | 0           | 0: Endpoint 7, buffer 1 is not ready for SIE transfer<br>1: Endpoint 7, buffer 1 is ready for SIE transfer |

| 14    | Ep6Buf1Rdy | R/W    | 0           | 0: Endpoint 6, buffer 1 is not ready for SIE transfer<br>1: Endpoint 6, buffer 1 is ready for SIE transfer |

| 13    | Ep5Buf1Rdy | R/W    | 0           | 0: Endpoint 5, buffer 1 is not ready for SIE transfer<br>1: Endpoint 5, buffer 1 is ready for SIE transfer |

| 12    | Ep4Buf1Rdy | R/W    | 0           | 0: Endpoint 4, buffer 1 is not ready for SIE transfer<br>1: Endpoint 4, buffer 1 is ready for SIE transfer |

| 11    | Ep3Buf1Rdy | R/W    | 0           | 0: Endpoint 3, buffer 1 is not ready for SIE transfer<br>1: Endpoint 3, buffer 1 is ready for SIE transfer |

| 10    | Ep2Buf1Rdy | R/W    | 0           | 0: Endpoint 2, buffer 1 is not ready for SIE transfer<br>1: Endpoint 2, buffer 1 is ready for SIE transfer |

| 9     | Ep1Buf1Rdy | R/W    | 0           | 0: Endpoint 1, buffer 1 is not ready for SIE transfer<br>1: Endpoint 1, buffer 1 is ready for SIE transfer |

| 8     | Reserved   | NA     | -           | Reserved                                                                                                   |

| 7     | Ep7Buf0Rdy | R/W    | 0           | 0: Endpoint 7, buffer 0 is not ready for SIE transfer<br>1: Endpoint 7, buffer 0 is ready for SIE transfer |

| 6     | Ep6Buf0Rdy | R/W    | 0           | 0: Endpoint 6, buffer 0 is not ready for SIE transfer<br>1: Endpoint 6, buffer 0 is ready for SIE transfer |

| 5     | Ep5Buf0Rdy | R/W    | 0           | 0: Endpoint 5, buffer 0 is not ready for SIE transfer<br>1: Endpoint 5, buffer 0 is ready for SIE transfer |

| 4     | Ep4Buf0Rdy | R/W    | 0           | 0: Endpoint 4, buffer 0 is not ready for SIE transfer<br>1: Endpoint 4, buffer 0 is ready for SIE transfer |

| 3     | Ep3Buf0Rdy | R/W    | 0           | 0: Endpoint 3, buffer 0 is not ready for SIE transfer<br>1: Endpoint 3, buffer 0 is ready for SIE transfer |

| 2     | Ep2Buf0Rdy | R/W    | 0           | 0: Endpoint 2, buffer 0 is not ready for SIE transfer<br>1: Endpoint 2, buffer 0 is ready for SIE transfer |

| 1     | Ep1Buf0Rdy | R/W    | 0           | 0: Endpoint 1, buffer 0 is not ready for SIE transfer<br>1: Endpoint 1, buffer 0 is ready for SIE transfer |

| 0     | Ep0Buf0Rdy | R/W    | 0           | 0: Endpoint 0, buffer 0 is not ready for SIE transfer<br>1: Endpoint 0, buffer 0 is ready for SIE transfer |

Table 2-17:

Buffer Ready Register (C\_BASEADDR + 0x0114)

## Test Mode Register (TMR)

The Test Mode Register (TMR) described in Table 2-18 defines the different test modes in which the AXI USB 2.0 Device operates. The USB Implementors Forum, the organization that controls USB logo certification, requires all USB 2.0 devices that operate at High Speed support these test modes.

| Bits | Name     | Access | Reset Value | Description                                                                                                                             |

|------|----------|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 31–3 | Reserved | R      | 0           | Reserved for future use                                                                                                                 |

| 2–0  | TestMde  | R/W    | 0           | Value defines the test mode.<br>0x0: Normal Mode<br>0x1: Test Mode J<br>0x2: Test Mode K<br>0x3: Test Mode NAK<br>0x4: Test Mode Packet |

The AXI USB 2.0 Device provides test mode support to facilitate compliance testing.

Four test modes are supported:

- Test Mode J Core transmits a continuous chirp J and remains in this state until the time when it is reset.

- Test Mode K Core transmits a continuous chirp K and remains in this state until the time when it is reset.

- Test Mode NAK Core searches for any IN token with a valid crc5. If crc5 is valid, the core sends a NAK, otherwise it waits for the next valid IN token. The core remains in this state until it is reset.

- Test Mode Packet As specified by the USB 2.0 Specification, the core transmits a test

packet which is composed of a predefined sequence of bytes and is used for analog

testing of the USB in High Speed mode. The packet data is loaded into a predefined

sequence of locations in the DPRAM. This routine repeats continuously until the core is

reset.

## Error Count Register (ECR)

The Error Count Register (ECR) is described in Table 2-19. This register contains three counters each of 8-bit width. They are BitStuffErrCnt, PidErrCnt, and CrcErrCnt. When USB reset or read to this register is requested, all these counters are cleared and assigned to reset values. When the PHY detects seven consecutive ones on the bus (*bit stuff error condition*), the SIE increments BitStuffErrCnt by one and BitStufErr bit of Interrupt Status Register (ISR) is set.

Whenever four PID check bits are not complement to their respective packet identifier bits while receiving the packet, the SIE increments PidErrCnt by one and PidErr bit of Interrupt Status Register (ISR) is set. Whenever the received CRC does not match with the CRC calculated on the received packet (that is, for CRC5 while receiving token and for CRC16

www.xilinx.com

while receiving data), the SIE increments CrcErrCnt by one and CrcErr bit of Interrupt Status Register (ISR) is set.

| Bits  | Name           | Access | Reset Value | Description             |

|-------|----------------|--------|-------------|-------------------------|

| 31–24 | 31–24 Reserved |        | -           | Reserved                |

| 23–16 | BitStuffErrCnt | R      | 0x0         | Bit Stuff Error Counter |

| 15-8  | PidErrCnt      | R      | 0x0         | PID Error Counter       |

| 7–0   | CrcErrCnt      | R      | 0x0         | CRC Error Counter       |

Table 2-19:

Error Count Register (C\_BASEADDR + 0x011C) (1)(2)

Notes:

1. This register is read-only.

2. When any of the counters reach 255, they roll back and start counting from 0.

### **ULPI PHY Access Register (UPAR)**

The ULPI PHY Access Register (UPAR) shown in Table 2-20 defines the type of access (read or write) to the ULPI PHY registers.

Read – When type of access is configured as read, the user application:

- Writes the address of the PHY register into PHYReg Addr and sets the WriteNotRead bit to 0.

- Core asserts the busy bit of the ULPI PHY Access Register (UPAR) until a successful read is performed from the respective PHY register.

- SIE updates the PHY register read data into PHYRdWrData after a successful read from the PHY register.

- Core clears the busy bit of the ULPI PHY Access Register (UPAR) and sets the ULPIAccComp bit of the Interrupt Status Register (ISR).

Write – When the type of access is configured as write, the user application:

- Writes the address of the PHY register into PHYRegAddr and PHYRdWrData, and sets the WriteNotRead bit to 1.

- Core asserts the busy bit of the ULPI PHY Access Register (UPAR) until a successful write is performed on the respective PHY register.

- Core clears the busy bit of the ULPI PHY Access Register (UPAR) after a successful write to the PHY register and sets ULPIAccComp bit of the Interrupt Status Register (ISR).

| Bits  | Name           | Access | Reset<br>Value | Description                                                     |

|-------|----------------|--------|----------------|-----------------------------------------------------------------|

| 31    | busy           | R      | 0              | 0: SIE is not busy<br>1: SIE is busy                            |

| 30–16 | 30–16 Reserved |        | -              | Reserved                                                        |

| 15-8  | PHYRdWrData    | R/W    | 0x0            | PHY register read or write data                                 |

| 7     | 7 Reserved     |        | -              | Reserved                                                        |

| 6     | WriteNotRead   | R/W    | 0              | 0: SIE reads the PHY register<br>1: SIE writes the PHY register |

| 5–0   | 5–0 PHYRegAddr |        | 0x0            | PHY register address                                            |

#### Table 2-20: ULPI PHY Access Register (C\_BASEADDR + 0x0120) (1)(2)(3)

#### Notes:

1. The SIE performs the register access onto the ULPI PHY register when ULPI Bus is IDLE (for example, when there is no data exchange between the ULPI PHY and the SIE). If the ULPI Bus is busy with ongoing data transfer, the SIE waits for ULPI Bus IDLE to perform the ULPI PHY register access.

- 2. Unsuccessful writes to the ULPI PHY access register result when the busy bit is set to 1.

- 3. ULPI PHY register access is not supported without assertion of MstRdy bit of Control Register (CR).

### **DMA Software Reset Register (DSRR)**

The DMA Software Reset Register (DSRR) shown in Table 2-21 defines reset to the DMA modules by the AXI USB 2.0 Device core when C\_INCLUDE\_DMA is set to 1.

| Table 2-21: | <b>DMA Software Reset Register</b> (C_BASEADDR + 0x0200) |

|-------------|----------------------------------------------------------|

|-------------|----------------------------------------------------------|

| Bits | Name   | Access | Reset Value | Description                                                |

|------|--------|--------|-------------|------------------------------------------------------------|

| 31–0 | DmaRst | W      | NA          | A write of 0x0000000A causes the reset to the DMA modules. |

#### **DMA Control Register (DMACR)**

The DMA Control Register (DMACR) described in Table 2-22 defines the direction of the transfer as either Read or Write to DPRAM2. The EpBufSel bit determines whether the SIE side Buffer Ready status is updated by the hardware when the DMA is complete or by the firmware through the BRR register. If the EpBufSel bit is set to 1, the DMA Controller updates the Buffer Ready status to the SIE based on bits [16:31] of the register at the end of a successful DMA transfer only.

Table 2-22: **DMA Control Register** (C\_BASEADDR + 0x0204)

| Bits | Name                         | Access                       | Reset<br>Value | Description                                                              |

|------|------------------------------|------------------------------|----------------|--------------------------------------------------------------------------|

| 31   | Direction <sup>(1) (2)</sup> | R/W                          | 0              | 0: Write data into DPRAM2<br>1: Read data from DPRAM2                    |

| 30   | EpBufSel <sup>(3)</sup>      | pBufSel <sup>(3)</sup> R/W 0 |                | 0: Buffer Ready set by firmware<br>1: Buffer Ready set by DMA Controller |

| Table 2-22: DMA Control Register | er (C_BASEADDR + 0x0204) (Cont'd) |

|----------------------------------|-----------------------------------|

|----------------------------------|-----------------------------------|

| Bits  | Name       | Access | Reset<br>Value | Description                                                                                                                                                                                     |  |

|-------|------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 29–16 | Reserved   | NA     | -              | Reserved                                                                                                                                                                                        |  |

| 15    | Ep7Buf1Rdy | R/W    | 0              | <ul><li>0: Endpoint 7, buffer 1 not ready for SIE transfer after the DMA operation completes</li><li>1: Endpoint 7, buffer 1 ready for SIE transfer after the DMA operation completes</li></ul> |  |

| 14    | Ep6Buf1Rdy | R/W    | 0              | 0: Endpoint 6, buffer 1 not ready for SIE transfer after the DMA operation completes<br>1: Endpoint 6, buffer 1 ready for SIE transfer after the DMA operation completes                        |  |

| 13    | Ep5Buf1Rdy | R/W    | 0              | 0: Endpoint 5, buffer 1 not ready for SIE transfer after the DMA operation completes<br>1: Endpoint 5, buffer 1 ready for SIE transfer after the DMA operation completes                        |  |

| 12    | Ep4Buf1Rdy | R/W    | 0              | 0: Endpoint 4, buffer 1 not ready for SIE transfer after the DMA operation completes<br>1: Endpoint 4, buffer 1 ready for SIE transfer after the DMA operation completes                        |  |

| 11    | Ep3Buf1Rdy | R/W    | 0              | 0: Endpoint 3, buffer 1 not ready for SIE transfer after the DMA operation completes<br>1: Endpoint 3, buffer 1 ready for SIE transfer after the DMA operation completes                        |  |

| 10    | Ep2Buf1Rdy | R/W    | 0              | <ul> <li>0: Endpoint 2, buffer 1 not ready for SIE transfer after t DMA operation completes</li> <li>1: Endpoint 2, buffer 1 ready for SIE transfer after the E operation completes</li> </ul>  |  |

| 9     | Ep1Buf1Rdy | R/W    | 0              | 0: Endpoint 1, buffer 1 not ready for SIE transfer after the DMA operation completes<br>1: Endpoint 1, buffer 1 ready for SIE transfer after the DMA operation completes                        |  |

| 8     | Reserved   | NA     | -              | Reserved                                                                                                                                                                                        |  |

| 7     | Ep7Buf0Rdy | R/W    | 0              | 0: Endpoint 7, buffer 0 not ready for SIE transfer after the<br>DMA operation completes<br>1: Endpoint 7, buffer 0 ready for SIE transfer after the DMA<br>operation completes                  |  |

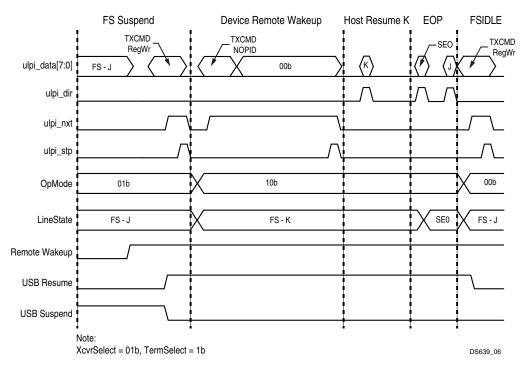

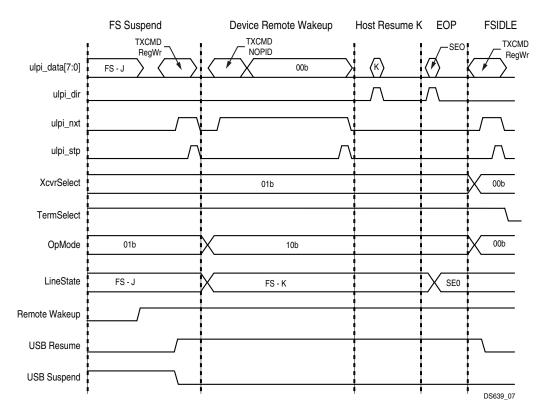

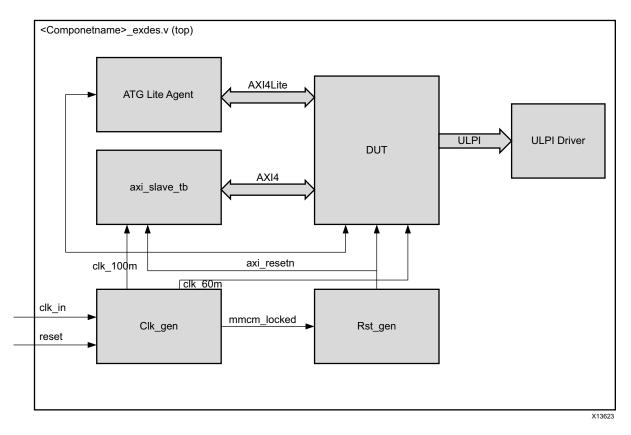

| 6     | Ep6Buf0Rdy | R/W    | 0              | 0: Endpoint 6, buffer 0 not ready for SIE transfer after the<br>DMA operation completes<br>1: Endpoint 6, buffer 0 ready for SIE transfer after the DMA<br>operation completes                  |  |