## Spartan-3E FPGA Family Data Sheet

DS312 December 14, 2018 Product Specification

## Module 1: Introduction and Ordering Information

### DS312 (v4.2) December 14, 2018

- Introduction

- Features

- Architectural Overview

- Package Marking

- Ordering Information

## Module 2: Functional Description

### DS312 (v4.2) December 14, 2018

- Input/Output Blocks (IOBs)

- Overview

- SelectIO™ Signal Standards

- Configurable Logic Block (CLB)

- Block RAM

- Dedicated Multipliers

- Digital Clock Manager (DCM)

- Clock Network

- Configuration

- Powering Spartan®-3E FPGAs

- Production Stepping

## Module 3: DC and Switching Characteristics

### DS312 (v4.2) December 14, 2018

- DC Electrical Characteristics

- Absolute Maximum Ratings

- Supply Voltage Specifications

- Recommended Operating Conditions

- DC Characteristics

- Switching Characteristics

- I/O Timing

- SLICE Timing

- DCM Timing

- Block RAM Timing

- Multiplier Timing

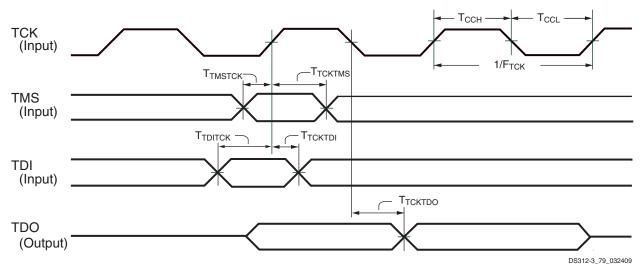

- Configuration and JTAG Timing

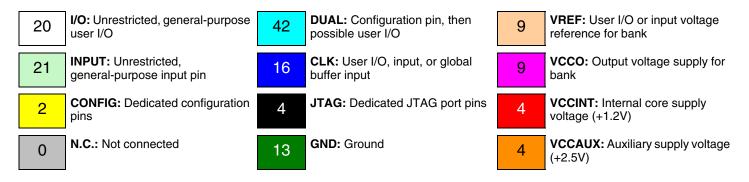

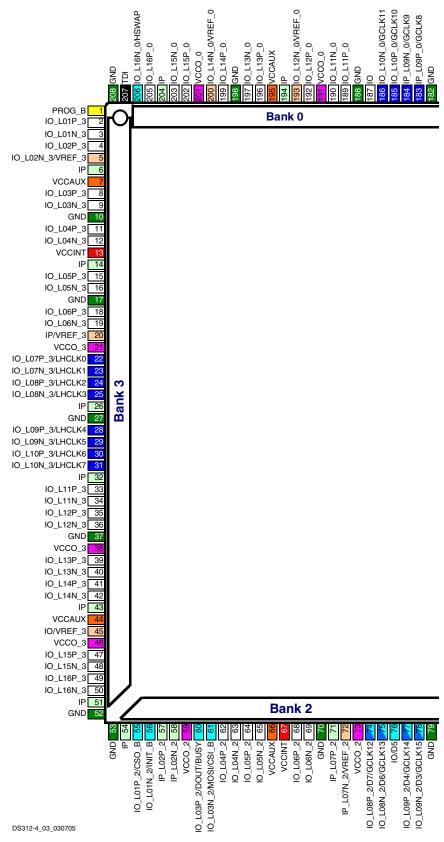

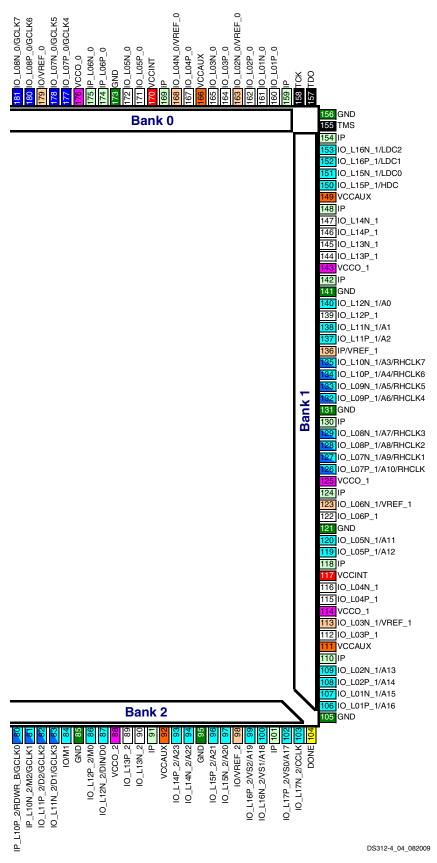

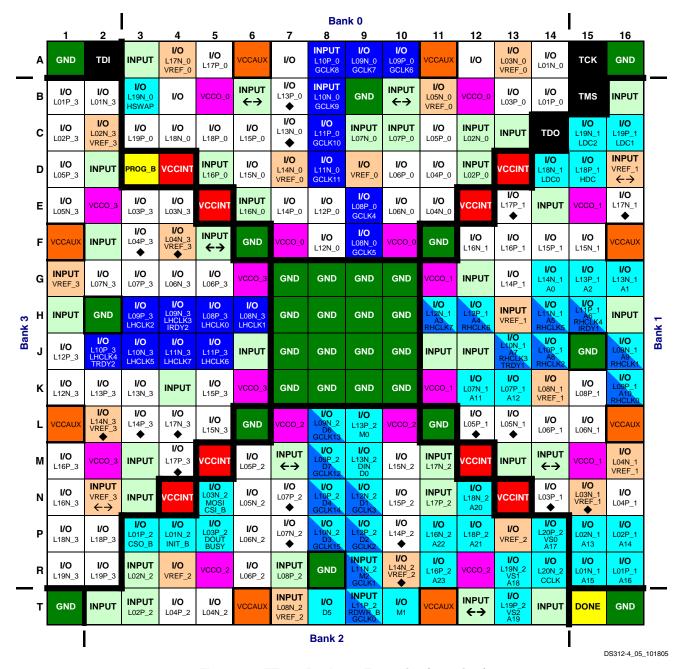

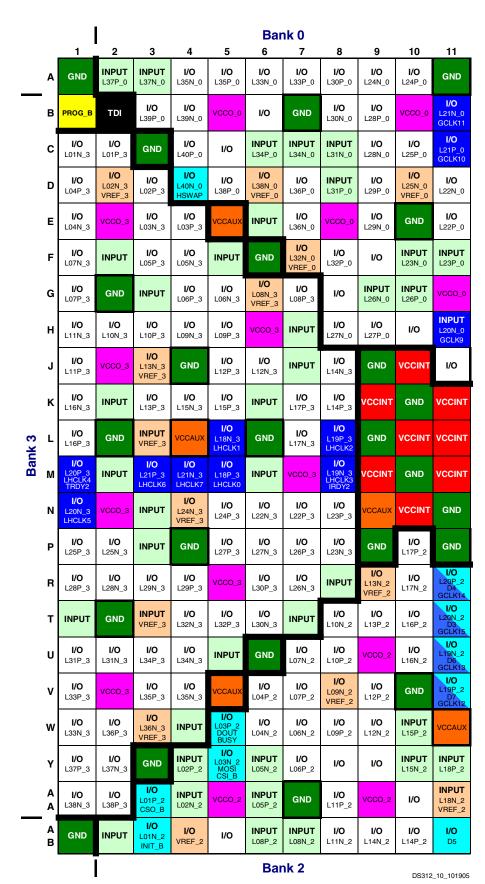

## Module 4: Pinout Descriptions

#### DS312 (v4.2) December 14, 2018

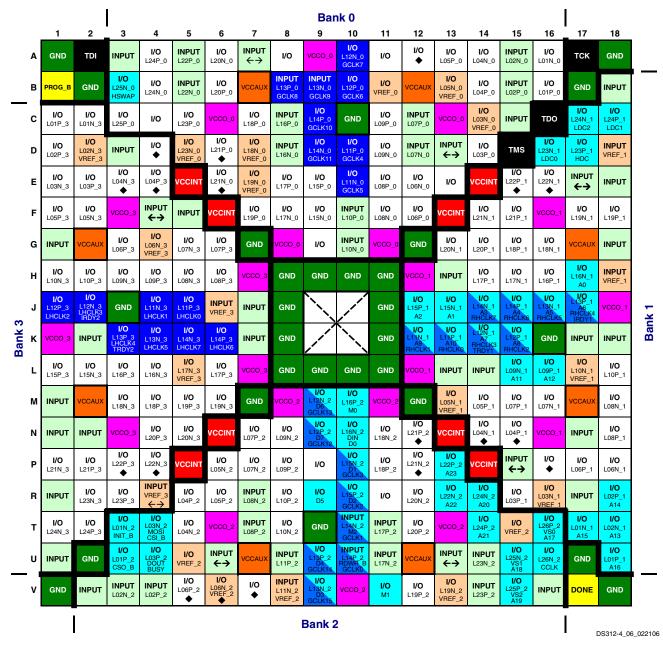

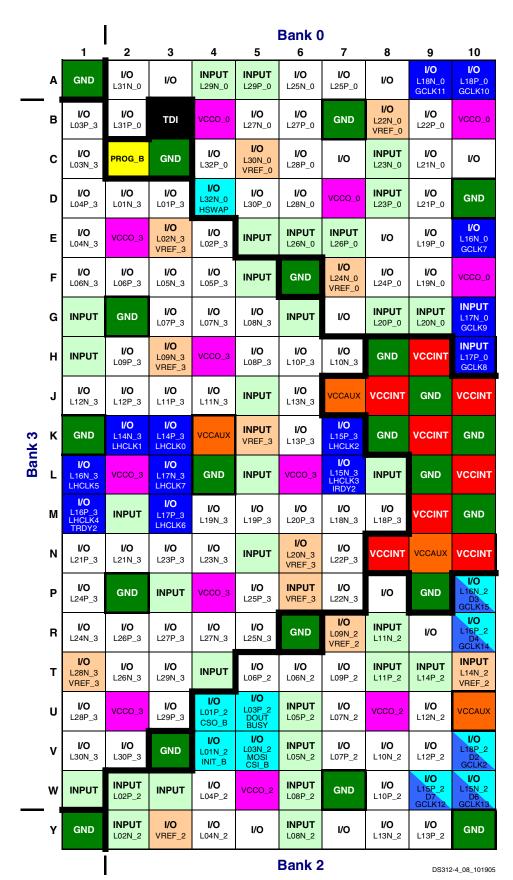

- Pin Descriptions

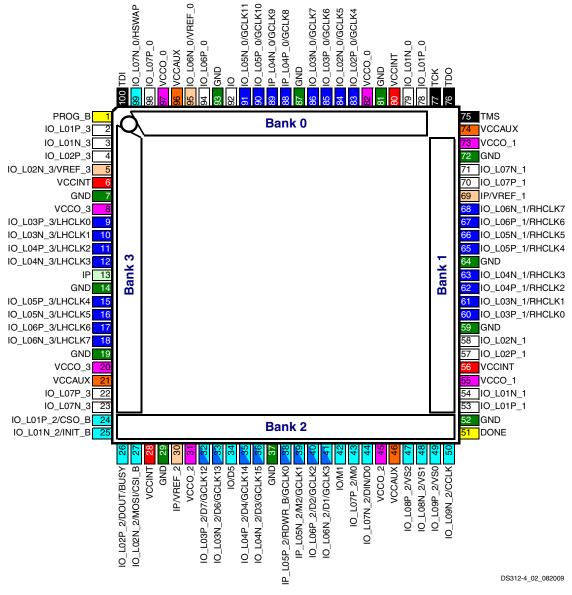

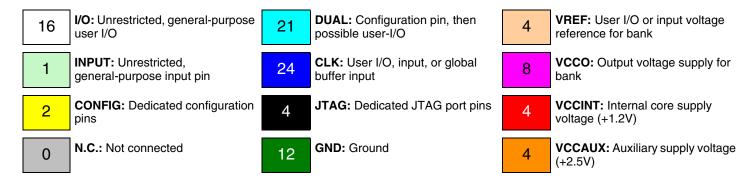

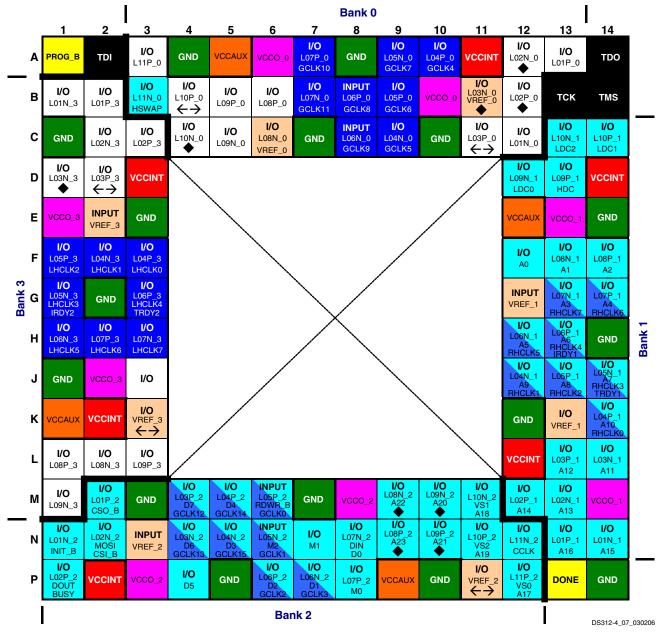

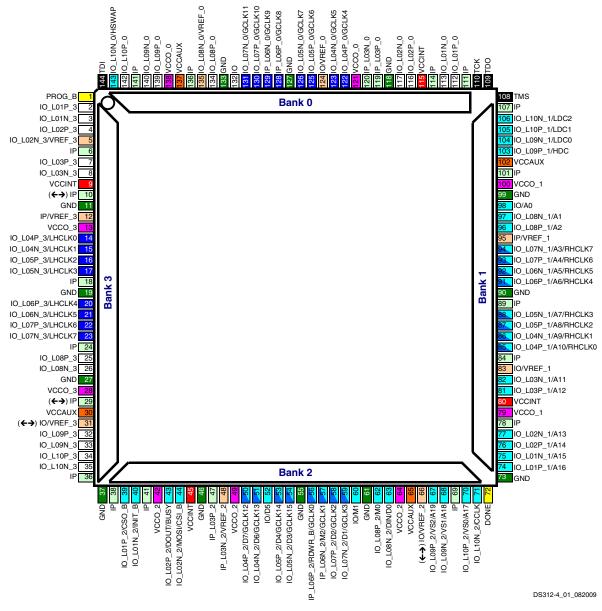

- Package Overview

- Pinout Tables

- Footprint Diagrams

# Spartan-3E FPGA Family: Introduction and Ordering Information

DS312 (v4.2) December 14, 2018

**Product Specification**

#### Introduction

The Spartan®-3E family of Field-Programmable Gate Arrays (FPGAs) is specifically designed to meet the needs of high volume, cost-sensitive consumer electronic applications. The five-member family offers densities ranging from 100,000 to 1.6 million system gates, as shown in Table 1.

The Spartan-3E family builds on the success of the earlier Spartan-3 family by increasing the amount of logic per I/O, significantly reducing the cost per logic cell. New features improve system performance and reduce the cost of configuration. These Spartan-3E FPGA enhancements, combined with advanced 90 nm process technology, deliver more functionality and bandwidth per dollar than was previously possible, setting new standards in the programmable logic industry.

Because of their exceptionally low cost, Spartan-3E FPGAs are ideally suited to a wide range of consumer electronics applications, including broadband access, home networking, display/projection, and digital television equipment.

The Spartan-3E family is a superior alternative to mask programmed ASICs. FPGAs avoid the high initial cost, the lengthy development cycles, and the inherent inflexibility of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary, an impossibility with ASICs.

#### **Features**

- Very low cost, high-performance logic solution for high-volume, consumer-oriented applications

- Proven advanced 90-nanometer process technology

- Multi-voltage, multi-standard SelectIO™ interface pins

- Up to 376 I/O pins or 156 differential signal pairs

- LVCMOS, LVTTL, HSTL, and SSTL single-ended signal standards

- 3.3V, 2.5V, 1.8V, 1.5V, and 1.2V signaling

- 622+ Mb/s data transfer rate per I/O

- True LVDS, RSDS, mini-LVDS, differential HSTL/SSTL differential I/O

- Enhanced Double Data Rate (DDR) support

- DDR SDRAM support up to 333 Mb/s

- · Abundant, flexible logic resources

- Densities up to 33,192 logic cells, including optional shift register or distributed RAM support

- Efficient wide multiplexers, wide logic

- Fast look-ahead carry logic

- Enhanced 18 x 18 multipliers with optional pipeline

- IEEE 1149.1/1532 JTAG programming/debug port

- Hierarchical SelectRAM™ memory architecture

- Up to 648 Kbits of fast block RAM

- Up to 231 Kbits of efficient distributed RAM

- Up to eight Digital Clock Managers (DCMs)

- Clock skew elimination (delay locked loop)

- Frequency synthesis, multiplication, division

- · High-resolution phase shifting

- Wide frequency range (5 MHz to over 300 MHz)

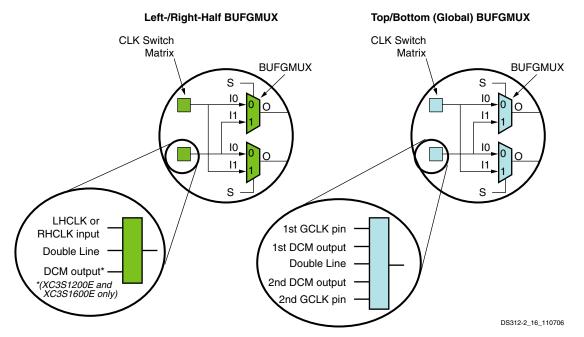

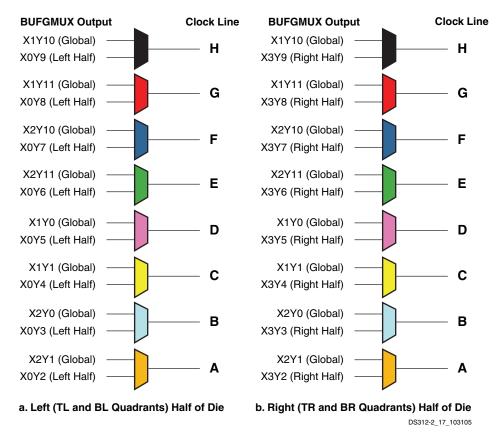

- Eight global clocks plus eight additional clocks per each half of device, plus abundant low-skew routing

- Configuration interface to industry-standard PROMs

- Low-cost, space-saving SPI serial Flash PROM

- x8 or x8/x16 parallel NOR Flash PROM

- Low-cost Xilinx® Platform Flash with JTAG

- Complete Xilinx ISE® and WebPACK™ software

- MicroBlaze<sup>™</sup> and PicoBlaze<sup>™</sup> embedded processor cores

- Fully compliant 32-/64-bit 33 MHz PCI support (66 MHz in some devices)

- Low-cost QFP and BGA packaging options

- Common footprints support easy density migration

- Pb-free packaging options

- XA Automotive version available

Table 1: Summary of Spartan-3E FPGA Attributes

| Device    | System | Equivalent  | (    | CLB Array<br>One CLB = Four Slices) |               |                 | Distributed             | Block<br>RAM        | Dedicated   | DCMs   | Maximum  | Maximum<br>Differential |  |

|-----------|--------|-------------|------|-------------------------------------|---------------|-----------------|-------------------------|---------------------|-------------|--------|----------|-------------------------|--|

| Device    | Gates  | Logic Cells | Rows | Columns                             | Total<br>CLBs | Total<br>Slices | RAM bits <sup>(1)</sup> | bits <sup>(1)</sup> | Multipliers | DCIVIS | User I/O | I/O Pairs               |  |

| XC3S100E  | 100K   | 2,160       | 22   | 16                                  | 240           | 960             | 15K                     | 72K                 | 4           | 2      | 108      | 40                      |  |

| XC3S250E  | 250K   | 5,508       | 34   | 26                                  | 612           | 2,448           | 38K                     | 216K                | 12          | 4      | 172      | 68                      |  |

| XC3S500E  | 500K   | 10,476      | 46   | 34                                  | 1,164         | 4,656           | 73K                     | 360K                | 20          | 4      | 232      | 92                      |  |

| XC3S1200E | 1200K  | 19,512      | 60   | 46                                  | 2,168         | 8,672           | 136K                    | 504K                | 28          | 8      | 304      | 124                     |  |

| XC3S1600E | 1600K  | 33,192      | 76   | 58                                  | 3,688         | 14,752          | 231K                    | 648K                | 36          | 8      | 376      | 156                     |  |

#### Notes:

1. By convention, one Kb is equivalent to 1,024 bits.

© Copyright 2005–2018 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

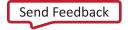

### **Architectural Overview**

The Spartan-3E family architecture consists of five fundamental programmable functional elements:

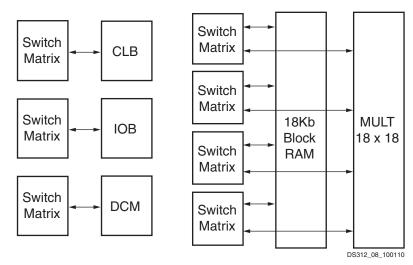

- Configurable Logic Blocks (CLBs) contain flexible Look-Up Tables (LUTs) that implement logic plus storage elements used as flip-flops or latches. CLBs perform a wide variety of logical functions as well as store data.

- Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3-state operation. Supports a variety of signal standards, including four high-performance differential standards. Double Data-Rate (DDR) registers are included.

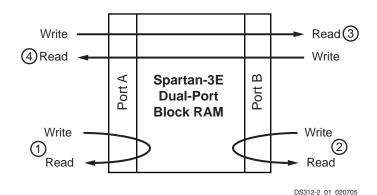

- Block RAM provides data storage in the form of 18-Kbit dual-port blocks.

- Multiplier Blocks accept two 18-bit binary numbers as inputs and calculate the product.

Digital Clock Manager (DCM) Blocks provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase-shifting clock signals.

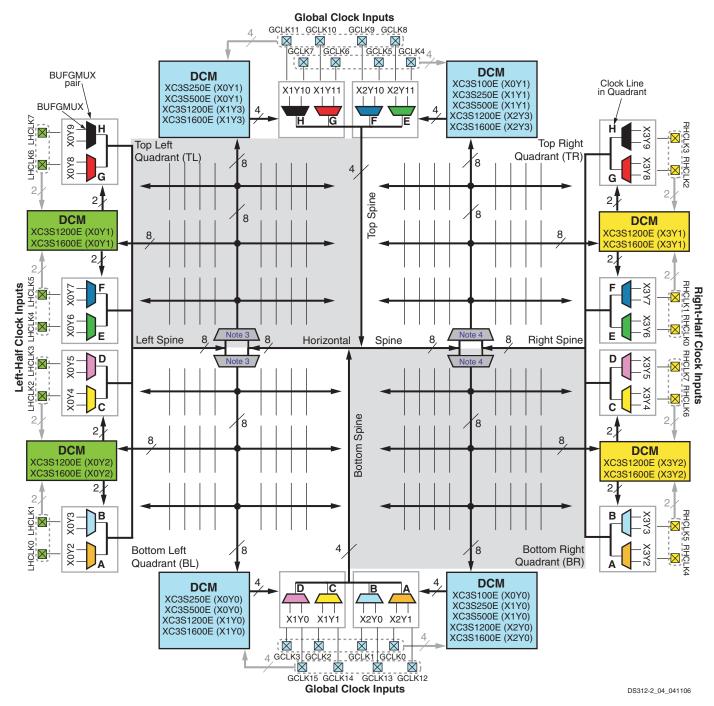

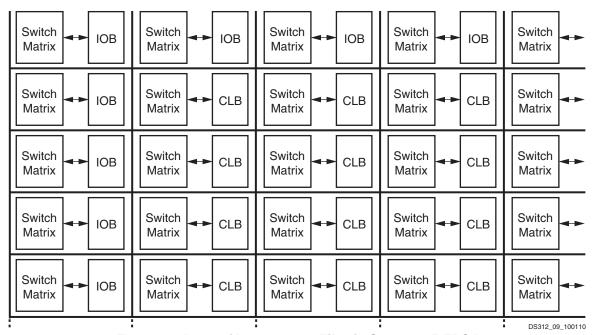

These elements are organized as shown in Figure 1. A ring of IOBs surrounds a regular array of CLBs. Each device has two columns of block RAM except for the XC3S100E, which has one column. Each RAM column consists of several 18-Kbit RAM blocks. Each block RAM is associated with a dedicated multiplier. The DCMs are positioned in the center with two at the top and two at the bottom of the device. The XC3S100E has only one DCM at the top and bottom, while the XC3S1200E and XC3S1600E add two DCMs in the middle of the left and right sides.

The Spartan-3E family features a rich network of traces that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

Figure 1: Spartan-3E Family Architecture

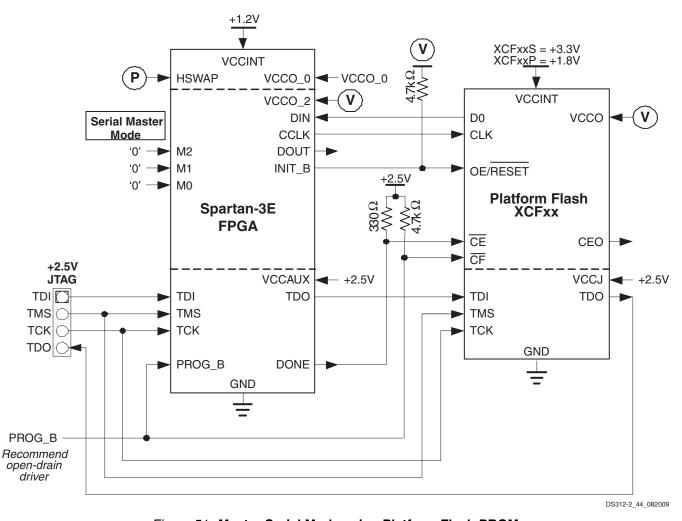

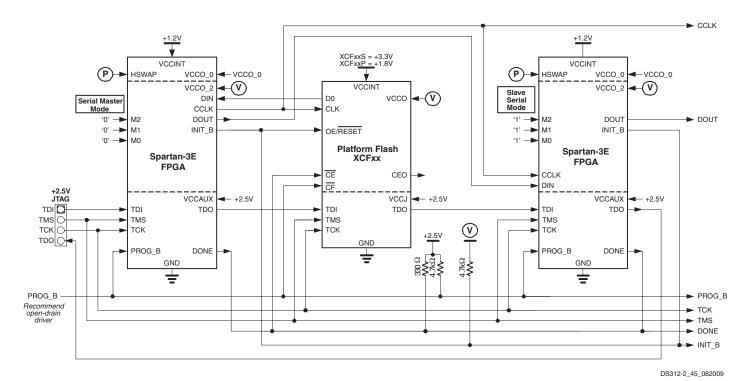

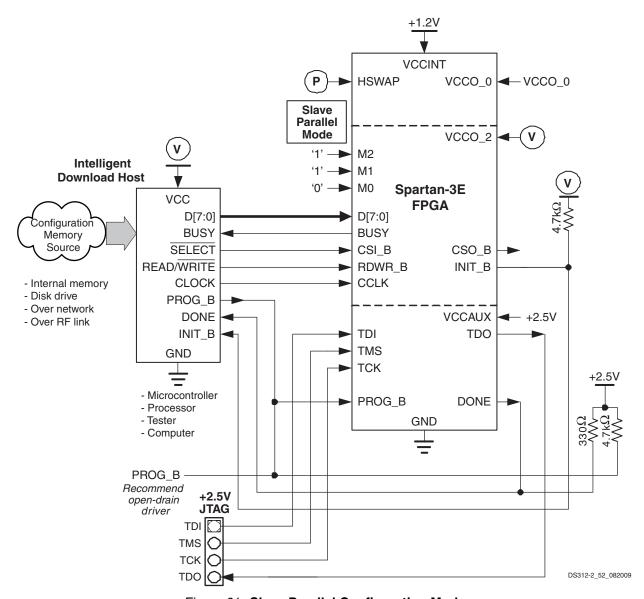

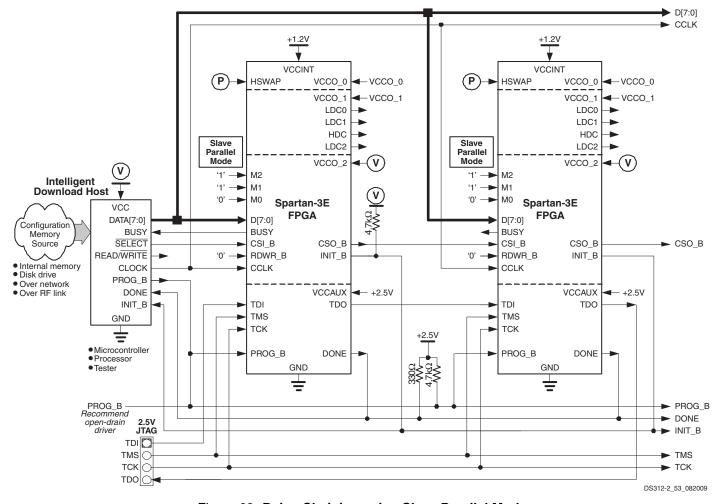

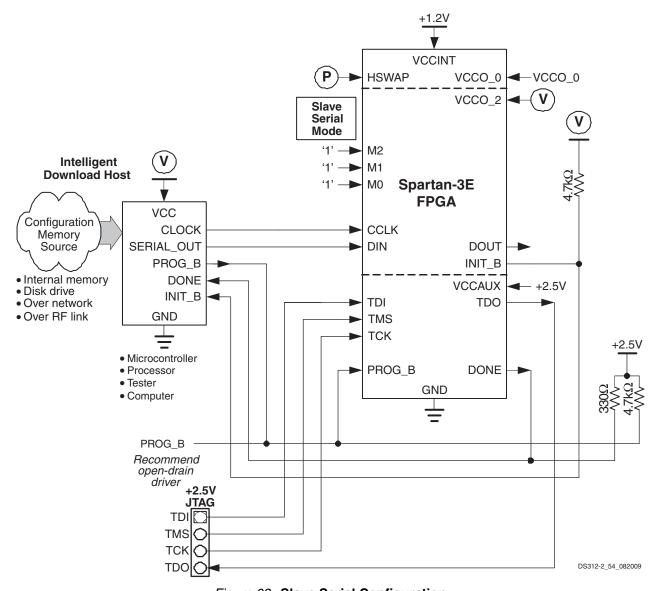

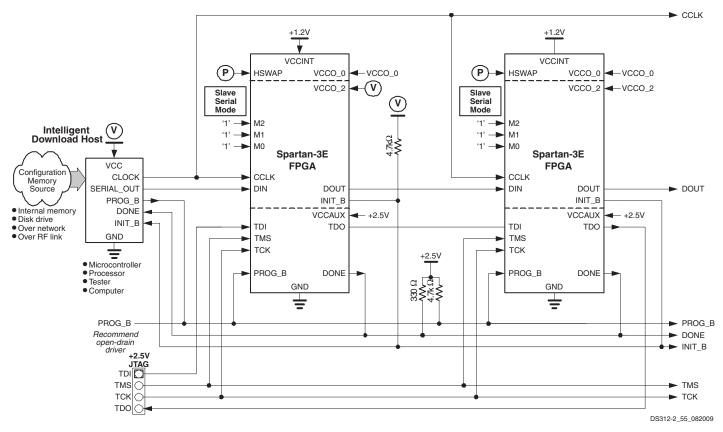

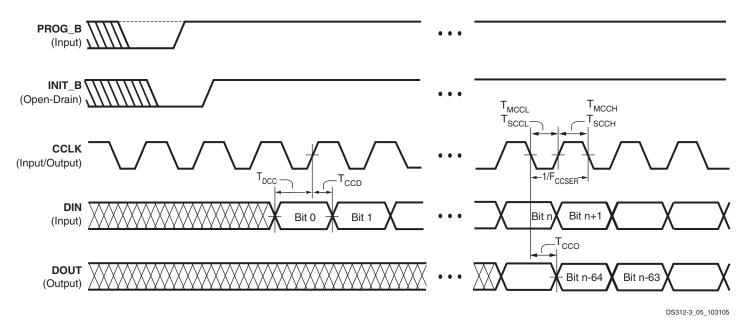

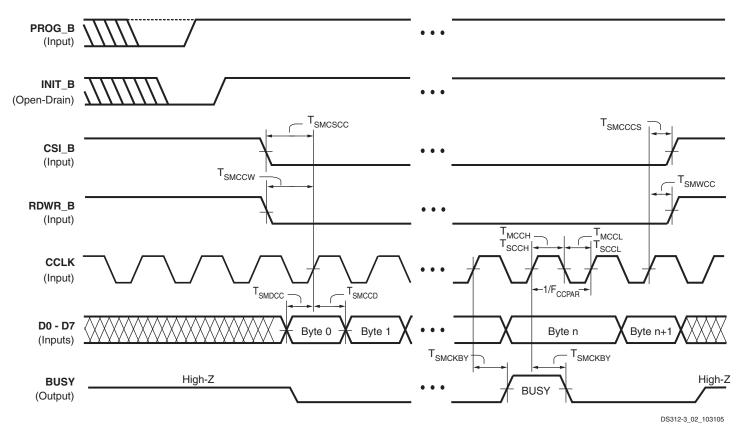

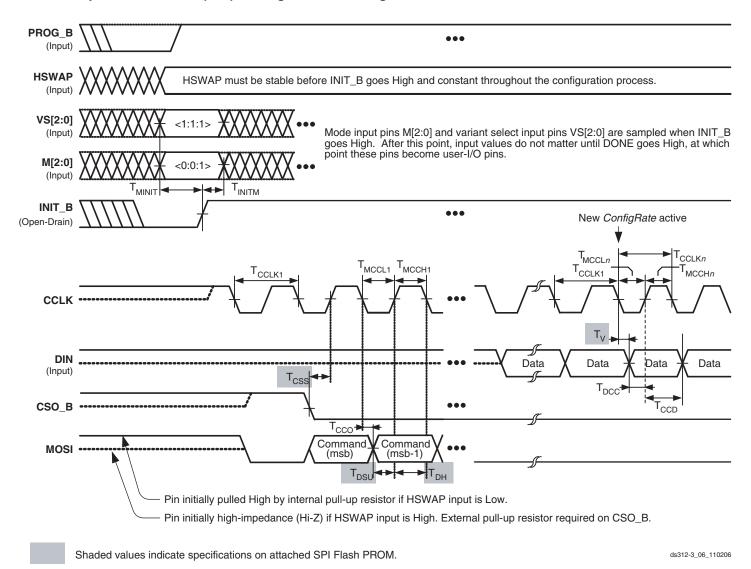

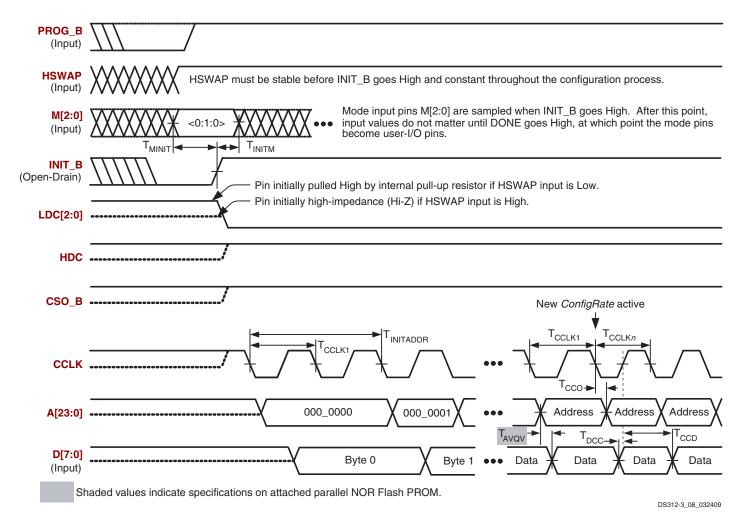

## Configuration

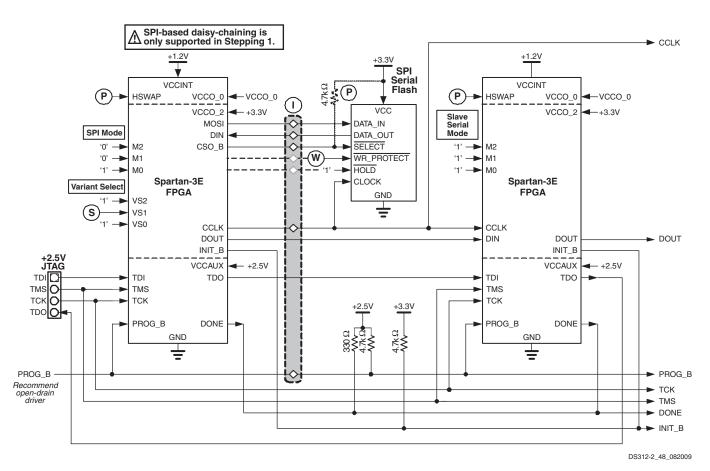

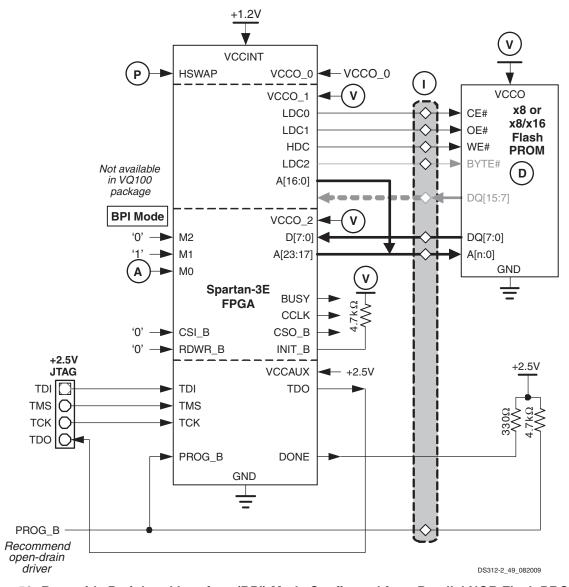

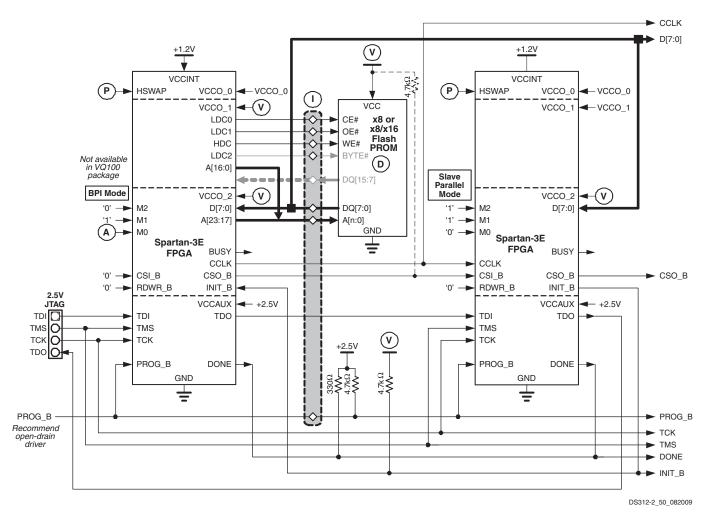

Spartan-3E FPGAs are programmed by loading configuration data into robust, reprogrammable, static CMOS configuration latches (CCLs) that collectively control all functional elements and routing resources. The FPGA's configuration data is stored externally in a PROM or some other non-volatile medium, either on or off the board. After applying power, the configuration data is written to the FPGA using any of seven different modes:

- Master Serial from a Xilinx Platform Flash PROM

- Serial Peripheral Interface (SPI) from an industry-standard SPI serial Flash

- Byte Peripheral Interface (BPI) Up or Down from an industry-standard x8 or x8/x16 parallel NOR Flash

- Slave Serial, typically downloaded from a processor

- Slave Parallel, typically downloaded from a processor

- Boundary Scan (JTAG), typically downloaded from a processor or system tester.

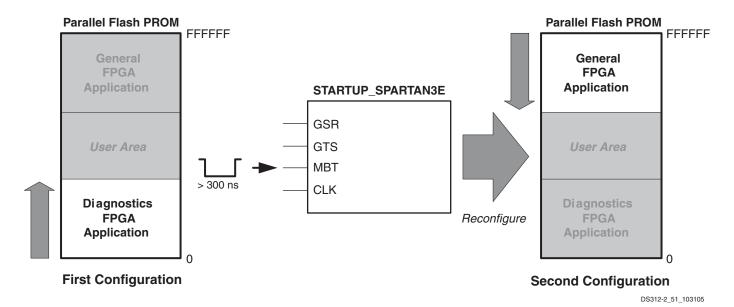

Furthermore, Spartan-3E FPGAs support MultiBoot configuration, allowing two or more FPGA configuration bitstreams to be stored in a single parallel NOR Flash. The FPGA application controls which configuration to load next and when to load it.

## I/O Capabilities

The Spartan-3E FPGA SelectIO interface supports many popular single-ended and differential standards. Table 2 shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination.

Spartan-3E FPGAs support the following single-ended standards:

- 3.3V low-voltage TTL (LVTTL)

- Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V, 1.5V, or 1.2V

- 3V PCI at 33 MHz, and in some devices, 66 MHz

- HSTL I and III at 1.8V, commonly used in memory applications

- SSTL I at 1.8V and 2.5V, commonly used for memory applications

Spartan-3E FPGAs support the following differential standards:

- LVDS

- Bus LVDS

- mini-LVDS

- RSDS

- Differential HSTL (1.8V, Types I and III)

- Differential SSTL (2.5V and 1.8V, Type I)

- 2.5V LVPECL inputs

Table 2: Available User I/Os and Differential (Diff) I/O Pairs

| Package                | VQ1<br>VQG                   |                      | CP <sup>0</sup> |                      | TQ:<br>TQG  |               | PQ:         | 208<br>3208   | FT256<br>FTG256 |               | FG320<br>FGG320 |                | FG400<br>FGG400 |                 | FG484<br>FGG484 |                 |

|------------------------|------------------------------|----------------------|-----------------|----------------------|-------------|---------------|-------------|---------------|-----------------|---------------|-----------------|----------------|-----------------|-----------------|-----------------|-----------------|

| Footprint<br>Size (mm) |                              |                      | 8               | 8 x 8 22 x 22        |             | ( 22          | 30.5 x 30.5 |               | 17 x 17         |               | 19 x 19         |                | 21 x 21         |                 | 23 x 23         |                 |

| Device                 | User                         | Diff                 | User            | Diff                 | User        | Diff          | User        | Diff          | User            | Diff          | User            | Diff           | User            | Diff            | User            | Diff            |

| XC3S100E               | <b>66<sup>(2)</sup></b> 9(7) | <b>30</b><br>(2)     | <b>83</b> (11)  | <b>35</b> <i>(2)</i> | 108<br>(28) | <b>40</b> (4) | -           | -             | -               | -             | -               | -              | -               | -               | -               | -               |

| XC3S250E               | <b>66</b> (7)                | <b>30</b> (2)        | <b>92</b> (7)   | <b>41</b> (2)        | 108<br>(28) | <b>40</b> (4) | 158<br>(32) | <b>65</b> (5) | <b>172</b> (40) | <b>68</b> (8) | -               | -              | -               | -               | -               | -               |

| XC3S500E               | <b>66</b> <sup>(3)</sup> (7) | <b>30</b> <i>(2)</i> | <b>92</b> (7)   | <b>41</b> <i>(2)</i> | -           | -             | 158<br>(32) | <b>65</b> (5) | 190<br>(41)     | <b>77</b> (8) | <b>232</b> (56) | <b>92</b> (12) | -               | -               | -               | -               |

| XC3S1200E              | -                            | -                    | -               | -                    | -           | -             | -           | -             | 190<br>(40)     | <b>77</b> (8) | <b>250</b> (56) | <b>99</b> (12) | <b>304</b> (72) | <b>124</b> (20) | -               | -               |

| XC3S1600E              | -                            | -                    | -               | -                    | -           | -             | -           | -             | -               | -             | <b>250</b> (56) | <b>99</b> (12) | <b>304</b> (72) | <b>124</b> (20) | <b>376</b> (82) | <b>156</b> (21) |

#### Notes:

- 1. All Spartan-3E devices provided in the same package are pin-compatible as further described in Module 4, Pinout Descriptions.

- 2. The number shown in **bold** indicates the maximum number of I/O and input-only pins. The number shown in (*italics*) indicates the number of input-only pins.

- The XC3S500E is available in the VQG100 Pb-free package and not the standard VQ100. The VQG100 and VQ100 pin-outs are identical

and general references to the VQ100 will apply to the XC3S500E.

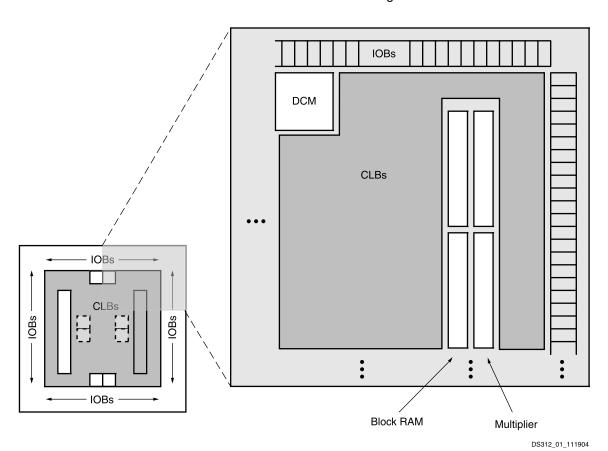

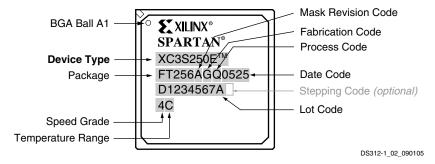

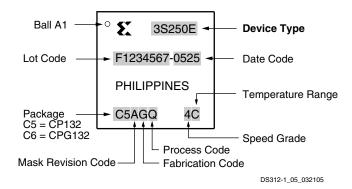

## **Package Marking**

Figure 2 provides a top marking example for Spartan-3E FPGAs in the quad-flat packages. Figure 3 shows the top marking for Spartan-3E FPGAs in BGA packages except the 132-ball chip-scale package (CP132 and CPG132). The markings for the BGA packages are nearly identical to those for the quad-flat packages, except that the marking is rotated with respect to the ball A1 indicator. Figure 4 shows the top marking for Spartan-3E FPGAs in the CP132 and CPG132 packages.

On the QFP and BGA packages, the optional numerical Stepping Code follows the Lot Code.

The "5C" and "4I" part combinations can have a dual mark of "5C/4I". Devices with a single mark are only guaranteed for the marked speed grade and temperature range. All "5C" and "4I" part combinations use the Stepping 1 production silicon.

Figure 2: Spartan-3E QFP Package Marking Example

Figure 3: Spartan-3E BGA Package Marking Example

Figure 4: Spartan-3E CP132 and CPG132 Package Marking Example

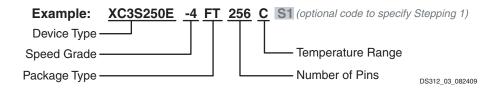

## **Ordering Information**

Spartan-3E FPGAs are available in both standard and Pb-free packaging options for all device/package combinations. All devices are available in Pb-free packages, which adds a 'G' character to the ordering code. All devices are available in either Commercial (C) or Industrial (I)

temperature ranges. Both the standard –4 and faster –5 speed grades are available for the Commercial temperature range. However, only the –4 speed grade is available for the Industrial temperature range. See Table 2 for valid device/package combinations.

| Device                  |    | Speed Grade                     |                 | Package Type / Number of Pins                    | ٦ | Temperature Range (T <sub>J</sub> ) |

|-------------------------|----|---------------------------------|-----------------|--------------------------------------------------|---|-------------------------------------|

| XC3S100E                | -4 | Standard Performance            | VQ100<br>VQG100 | 100-pin Very Thin Quad Flat Pack (VQFP)          | С | Commercial (0°C to 85°C)            |

| XC3S250E                | -5 | High Performance <sup>(1)</sup> | CP132<br>CPG132 | 132-ball Chip-Scale Package (CSP)                | I | Industrial (-40°C to 100°C)         |

| XC3S500E <sup>(2)</sup> |    |                                 | TQ144<br>TQG144 | 144-pin Thin Quad Flat Pack (TQFP)               |   |                                     |

| XC3S1200E               |    |                                 | PQ208<br>PQG208 | 208-pin Plastic Quad Flat Pack (PQFP)            |   |                                     |

| XC3S1600E               |    |                                 | FT256<br>FTG256 | 256-ball Fine-Pitch Thin Ball Grid Array (FTBGA) |   |                                     |

|                         |    |                                 | FG320<br>FGG320 | 320-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                     |

|                         |    |                                 | FG400<br>FGG400 | 400-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                     |

|                         |    |                                 | FG484<br>FGG484 | 484-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                     |

#### Notes:

- 1. The -5 speed grade is exclusively available in the Commercial temperature range.

- 2. The XC3S500E VQG100 is available only in the -4 Speed Grade.

- 3. See DS635 for the XA Automotive Spartan-3E FPGAs.

#### **Production Stepping**

The Spartan-3E FPGA family uses production stepping to indicate improved capabilities or enhanced features.

Stepping 1 is, by definition, a functional superset of Stepping 0. Furthermore, configuration bitstreams generated for any stepping are forward compatible. See Table 72 for additional details.

Xilinx has shipped both Stepping 0 and Stepping 1. Designs operating on the Stepping 0 devices perform similarly on a Stepping 1 device. Stepping 1 devices have been shipping since 2006. The faster speed grade (-5), Industrial (I grade), Automotive devices, and -4C devices with date codes 0901 (2009) and later, are always Stepping 1 devices. Only -4C devices have shipped as Stepping 0 devices.

To specify only the later stepping for the -4C, append an *S#* suffix to the standard ordering code, where # is the stepping number, as indicated in Table 3.

Table 3: Spartan-3E Optional Stepping Level Ordering

| Stepping<br>Number | Suffix Code | Status     |

|--------------------|-------------|------------|

| 0                  | None or S0  | Production |

| 1                  | S1          | Production |

The stepping level is optionally marked on the device using a single number character, as shown in Figure 2, Figure 3, and Figure 4.

## **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/01/2005 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                |

| 03/21/2005 | 1.1     | Added XC3S250E in CP132 package to Table 2. Corrected number of differential I/O pairs for CP132 package. Added package markings for QFP packages (Figure 2) and CP132/CPG132 packages (Figure 4).                                                                                                                                                                                                     |

| 11/23/2005 | 2.0     | Added differential HSTL and SSTL I/O standards. Updated Table 2 to indicate number of input-only pins. Added Production Stepping information, including example top marking diagrams.                                                                                                                                                                                                                  |

| 03/22/2006 | 3.0     | Upgraded data sheet status to Preliminary. Added XC3S100E in CP132 package and updated I/O counts for the XC3S1600E in FG320 package (Table 2). Added information about dual markings for – 5C and –4I product combinations to Package Marking.                                                                                                                                                        |

| 11/09/2006 | 3.4     | Added 66 MHz PCI support and links to the Xilinx PCI LogiCORE data sheet. Indicated that Stepping 1 parts are Production status. Promoted Module 1 to Production status. Synchronized all modules to v3.4.                                                                                                                                                                                             |

| 04/18/2008 | 3.7     | Added XC3S500E VQG100 package. Added reference to XA Automotive version. Updated links.                                                                                                                                                                                                                                                                                                                |

| 08/26/2009 | 3.8     | Added paragraph to Configuration indicating the device supports MultiBoot configuration. Added package sizes to Table 2. Described the speed grade and temperature range guarantee for devices having a single mark in paragraph 3 under Package Marking. Deleted Pb-Free Packaging example under Ordering Information. Revised information under Production Stepping. Revised description of Table 3. |

| 10/29/2012 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs.  Updated Table 2 footprint size of PQ208.                                                                                                                                                                                                                                                                                 |

| 07/19/2013 | 4.1     | Removed banner. This product IS recommended for new designs.                                                                                                                                                                                                                                                                                                                                           |

| 12/14/2018 | 4.2     | Updated for Lead-Frame Plating Composition Change For Legacy Eutectic Products (XCN18024).                                                                                                                                                                                                                                                                                                             |

### **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### **AUTOMOTIVE APPLICATIONS DISCLAIMER**

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

# Spartan-3E FPGA Family: Functional Description

DS312 (v4.2) December 14, 2018

**Product Specification**

## **Design Documentation Available**

The functionality of the Spartan®-3E FPGA family is now described and updated in the following documents. The topics covered in each guide are listed below.

- UG331: Spartan-3 Generation FPGA User Guide

- Clocking Resources

- Digital Clock Managers (DCMs)

- Block RAM

- Configurable Logic Blocks (CLBs)

- Distributed RAM

- SRL16 Shift Registers

- Carry and Arithmetic Logic

- I/O Resources

- Embedded Multiplier Blocks

- Programmable Interconnect

- ISE® Design Tools

- IP Cores

- Embedded Processing and Control Solutions

- Pin Types and Package Overview

- Package Drawings

- Powering FPGAs

- Power Management

- <u>UG332</u>: Spartan-3 Generation Configuration User Guide

- Configuration Overview

- Configuration Pins and Behavior

- Bitstream Sizes

- Detailed Descriptions by Mode

- Master Serial Mode using Xilinx® Platform Flash PROM

- Master SPI Mode using Commodity SPI Serial Flash PROM

- Master BPI Mode using Commodity Parallel NOR Flash PROM

- Slave Parallel (SelectMAP) using a Processor

- Slave Serial using a Processor

- JTAG Mode

- ISE iMPACT Programming Examples

- MultiBoot Reconfiguration

### **Xilinx Alerts**

Create a Xilinx user account and sign up to receive automatic e-mail notification whenever this data sheet or the associated user guides are updated.

#### Sign Up for Alerts on Xilinx.com

https://secure.xilinx.com/webreg/register.do ?group=myprofile&languageID=1

## **Spartan-3E FPGA Starter Kit**

For specific hardware examples, please see the Spartan-3E FPGA Starter Kit board web page, which has links to various design examples and the user guide.

- Spartan-3E FPGA Starter Kit Board page http://www.xilinx.com/s3estarter

- <u>UG230</u>: Spartan-3E FPGA Starter Kit User Guide

#### Introduction

As described in Architectural Overview, the Spartan-3E FPGA architecture consists of five fundamental functional elements:

- Input/Output Blocks (IOBs)

- Configurable Logic Block (CLB) and Slice Resources

- Block RAM

- Dedicated Multipliers

- Digital Clock Managers (DCMs)

The following sections provide detailed information on each of these functions. In addition, this section also describes the following functions:

- Clocking Infrastructure

- Interconnect

- Configuration

- Powering Spartan-3E FPGAs

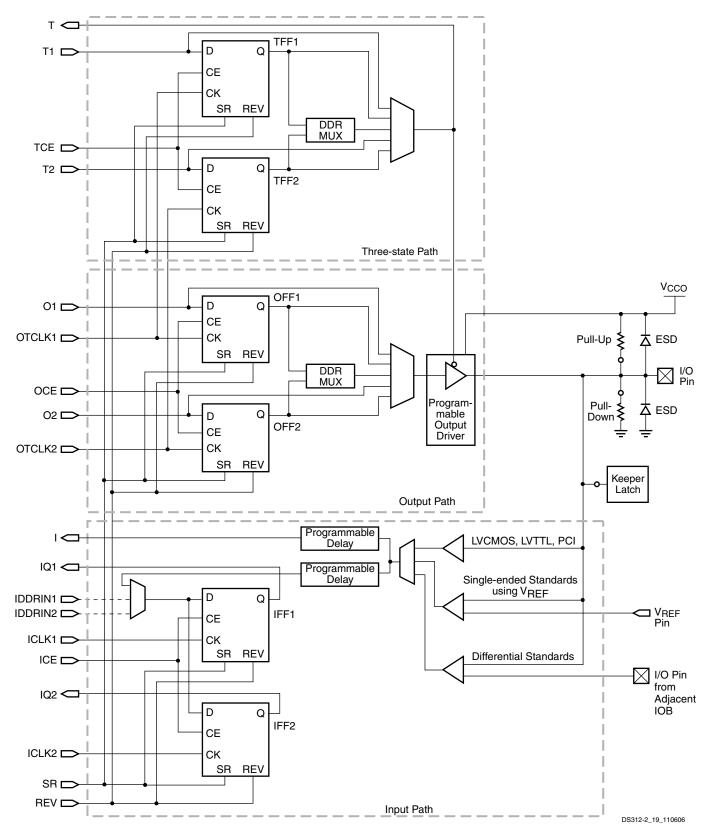

## Input/Output Blocks (IOBs)

For additional information, refer to the "Using I/O Resources" chapter in UG331.

### **IOB Overview**

The Input/Output Block (IOB) provides a programmable, unidirectional or bidirectional interface between a package pin and the FPGA's internal logic. The IOB is similar to that of the Spartan-3 family with the following differences:

- Input-only blocks are added

- Programmable input delays are added to all blocks

- DDR flip-flops can be shared between adjacent IOBs

The unidirectional input-only block has a subset of the full IOB capabilities. Thus there are no connections or logic for an output path. The following paragraphs assume that any reference to output functionality does not apply to the input-only blocks. The number of input-only blocks varies with device size, but is never more than 25% of the total IOB count.

Figure 5 is a simplified diagram of the IOB's internal structure. There are three main signal paths within the IOB: the output path, input path, and 3-state path. Each path has its own pair of storage elements that can act as either registers or latches. For more information, see Storage Element Functions. The three main signal paths are as follows:

The input path carries data from the pad, which is bonded to a package pin, through an optional programmable delay element directly to the I line. After the delay element, there are alternate routes through a

- pair of storage elements to the IQ1 and IQ2 lines. The IOB outputs I, IQ1, and IQ2 lead to the FPGA's internal logic. The delay element can be set to ensure a hold time of zero (see Input Delay Functions).

- The output path, starting with the O1 and O2 lines, carries data from the FPGA's internal logic through a multiplexer and then a three-state driver to the IOB pad. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements.

- The 3-state path determines when the output driver is high impedance. The T1 and T2 lines carry data from the FPGA's internal logic through a multiplexer to the output driver. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements.

- All signal paths entering the IOB, including those associated with the storage elements, have an inverter option. Any inverter placed on these paths is automatically absorbed into the IOB.

Figure 5: Simplified IOB Diagram

## **Input Delay Functions**

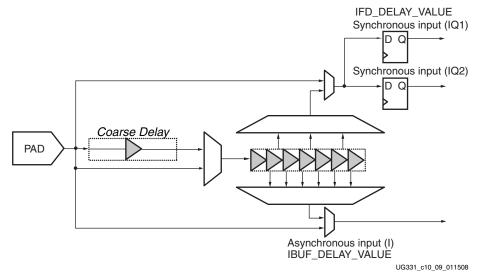

Each IOB has a programmable delay block that optionally delays the input signal. In Figure 6, the signal path has a coarse delay element that can be bypassed. The input signal then feeds a 6-tap delay line. The coarse and tap delays vary; refer to timing reports for specific delay values. All six taps are available via a multiplexer for use as an asynchronous input directly into the FPGA fabric. In this way, the delay is programmable in 12 steps. Three of the six taps are also available via a multiplexer to the D inputs of the synchronous storage elements. The delay inserted in the path to the storage element can be varied in six steps. The first, coarse delay element is common to both asynchronous and synchronous paths, and must be either used or not used for both paths.

The delay values are set up in the silicon once at configuration time—they are non-modifiable in device operation.

The primary use for the input delay element is to adjust the input delay path to ensure that there is no hold time requirement when using the input flip-flop(s) with a global clock. The default value is chosen automatically by the Xilinx software tools as the value depends on device size and the specific device edge where the flip-flop resides. The value set by the Xilinx ISE software is indicated in the Map

report generated by the implementation tools, and the resulting effects on input timing are reported using the Timing Analyzer tool.

If the design uses a DCM in the clock path, then the delay element can be safely set to zero because the Delay-Locked Loop (DLL) compensation automatically ensures that there is still no input hold time requirement.

Both asynchronous and synchronous values can be modified, which is useful where extra delay is required on clock or data inputs, for example, in interfaces to various types of RAM.

These delay values are defined through the IBUF\_DELAY\_VALUE and the IFD\_DELAY\_VALUE parameters. The default IBUF\_DELAY\_VALUE is 0, bypassing the delay elements for the asynchronous input. The user can set this parameter to 0-12. The default IFD\_DELAY\_VALUE is AUTO. IBUF\_DELAY\_VALUE and IFD\_DELAY\_VALUE are independent for each input. If the same input pin uses both registered and non-registered input paths, both parameters can be used, but they must both be in the same half of the total delay (both either bypassing or using the coarse delay element).

Figure 6: Programmable Fixed Input Delay Elements

## **Storage Element Functions**

There are three pairs of storage elements in each IOB, one pair for each of the three paths. It is possible to configure each of these storage elements as an edge-triggered D-type flip-flop (FD) or a level-sensitive latch (LD).

The storage-element pair on either the Output path or the Three-State path can be used together with a special multiplexer to produce Double-Data-Rate (DDR) transmission. This is accomplished by taking data

synchronized to the clock signal's rising edge and converting it to bits synchronized on both the rising and the falling edge. The combination of two registers and a multiplexer is referred to as a Double-Data-Rate D-type flip-flop (ODDR2).

Table 4 describes the signal paths associated with the storage element.

Table 4: Storage Element Signal Description

| Storage<br>Element<br>Signal | Description        | Function                                                                                                                                                                                                                                                                                                    |

|------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D                            | Data input         | Data at this input is stored on the active edge of CK and enabled by CE. For latch operation when the input is enabled, data passes directly to the output Q.                                                                                                                                               |

| Q                            | Data output        | The data on this output reflects the state of the storage element. For operation as a latch in transparent mode, Q mirrors the data at D.                                                                                                                                                                   |

| CK                           | Clock input        | Data is loaded into the storage element on this input's active edge with CE asserted.                                                                                                                                                                                                                       |

| CE                           | Clock Enable input | When asserted, this input enables CK. If not connected, CE defaults to the asserted state.                                                                                                                                                                                                                  |

| SR                           | Set/Reset input    | This input forces the storage element into the state specified by the SRHIGH/SRLOW attributes. The SYNC/ASYNC attribute setting determines if the SR input is synchronized to the clock or not. If both SR and REV are active at the same time, the storage element gets a value of 0.                      |

| REV                          | Reverse input      | This input is used together with SR. It forces the storage element into the state opposite from what SR does. The SYNC/ASYNC attribute setting determines whether the REV input is synchronized to the clock or not. If both SR and REV are active at the same time, the storage element gets a value of 0. |

As shown in Figure 5, the upper registers in both the output and three-state paths share a common clock. The OTCLK1 clock signal drives the CK clock inputs of the upper registers on the output and three-state paths. Similarly, OTCLK2 drives the CK inputs for the lower registers on the output and three-state paths. The upper and lower registers on the input path have independent clock lines: ICLK1 and ICLK2.

The OCE enable line controls the CE inputs of the upper and lower registers on the output path. Similarly, TCE controls the CE inputs for the register pair on the three-state path and ICE does the same for the register pair on the input path.

The Set/Reset (SR) line entering the IOB controls all six registers, as is the Reverse (REV) line.

In addition to the signal polarity controls described in IOB Overview, each storage element additionally supports the controls described in Table 5.

Table 5: Storage Element Options

| Option Switch | Function                                                                                                                                                                                                                                               | Specificity                                                                                                                                                                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FF/Latch      | Chooses between an edge-triggered flip-flop or a level-sensitive latch                                                                                                                                                                                 | Independent for each storage element                                                                                                                                                                                                             |

| SYNC/ASYNC    | Determines whether the SR set/reset control is synchronous or asynchronous                                                                                                                                                                             | Independent for each storage element                                                                                                                                                                                                             |

| SRHIGH/SRLOW  | Determines whether SR acts as a Set, which forces the storage element to a logic 1 (SRHIGH) or a Reset, which forces a logic 0 (SRLOW)                                                                                                                 | Independent for each storage element, except when using ODDR2. In the latter case, the selection for the upper element will apply to both elements.                                                                                              |

| INIT1/INIT0   | When Global Set/Reset (GSR) is asserted or after configuration this option specifies the initial state of the storage element, either set (INIT1) or reset (INIT0). By default, choosing SRLOW also selects INIT0; choosing SRHIGH also selects INIT1. | Independent for each storage element, except when using ODDR2, which uses two IOBs. In the ODDR2 case, selecting INIT0 for one IOBs applies to both elements within the IOB, although INIT1 could be selected for the elements in the other IOB. |

#### **Double-Data-Rate Transmission**

Double-Data-Rate (DDR) transmission describes the technique of synchronizing signals to both the rising and falling edges of the clock signal. Spartan-3E devices use register pairs in all three IOB paths to perform DDR operations.

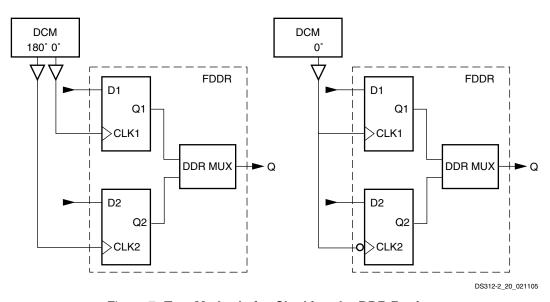

The pair of storage elements on the IOB's Output path (OFF1 and OFF2), used as registers, combine with a special multiplexer to form a DDR D-type flip-flop (ODDR2). This primitive permits DDR transmission where output data bits are synchronized to both the rising and falling edges of a clock. DDR operation requires two clock signals (usually 50% duty cycle), one the inverted form of the other. These signals trigger the two registers in alternating fashion, as shown in Figure 7. The Digital Clock Manager (DCM) generates the two clock signals by mirroring an incoming signal, and then shifting it 180 degrees. This approach ensures minimal skew between the two signals. Alternatively, the inverter inside the IOB can be used to invert the clock signal, thus only using one clock line and both rising and falling edges of that clock line as the two clocks for the DDR flip-flops.

The storage-element pair on the Three-State path (TFF1 and TFF2) also can be combined with a local multiplexer to form a DDR primitive. This permits synchronizing the output enable to both the rising and falling edges of a clock. This DDR operation is realized in the same way as for the output path.

The storage-element pair on the input path (IFF1 and IFF2) allows an I/O to receive a DDR signal. An incoming DDR clock signal triggers one register, and the inverted clock signal triggers the other register. The registers take turns capturing bits of the incoming DDR data signal. The primitive to allow this functionality is called IDDR2.

Aside from high bandwidth data transfers, DDR outputs also can be used to reproduce, or *mirror*, a clock signal on the output. This approach is used to transmit clock and data signals together (source synchronously). A similar approach is used to reproduce a clock signal at multiple outputs. The advantage for both approaches is that skew across the outputs is minimal.

Figure 7: Two Methods for Clocking the DDR Register

#### **Register Cascade Feature**

In the Spartan-3E family, one of the IOBs in a differential pair can cascade its input storage elements with those in the other IOB as part of a differential pair. This is intended to make DDR operation at high speed much simpler to implement. The new DDR connections that are available are shown in Figure 5 (dashed lines), and are only available for routing between IOBs and are not accessible to the FPGA fabric. Note that this feature is only available when using the differential I/O standards LVDS, RSDS, and MINI\_LVDS.

#### **IDDR2**

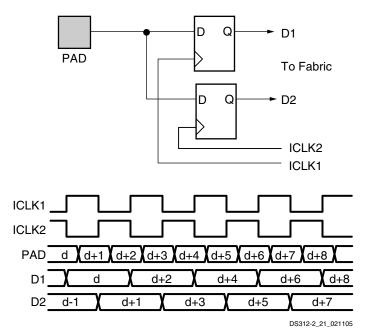

As a DDR input pair, the master IOB registers incoming data on the rising edge of ICLK1 (= D1) and the rising edge of ICLK2 (= D2), which is typically the same as the falling edge of ICLK1. This data is then transferred into the FPGA fabric. At some point, both signals must be brought into the same clock domain, typically ICLK1. This can be difficult at high frequencies because the available time is only one half of a clock cycle assuming a 50% duty cycle. See Figure 8 for a graphical illustration of this function.

Figure 8: Input DDR (without Cascade Feature)

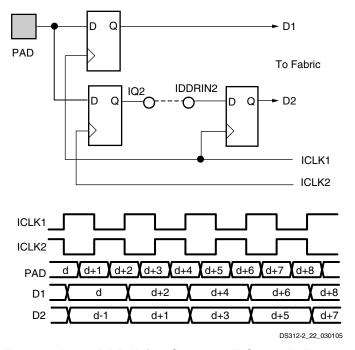

In the Spartan-3E device, the signal D2 can be cascaded into the storage element of the adjacent slave IOB. There it is re-registered to ICLK1, and only then fed to the FPGA fabric where it is now already in the same time domain as D1. Here, the FPGA fabric uses only the clock ICLK1 to process the received data. See Figure 9 for a graphical illustration of this function.

Figure 9: Input DDR Using Spartan-3E Cascade Feature

#### ODDR2

As a DDR output pair, the master IOB registers data coming from the FPGA fabric on the rising edge of OCLK1 (= D1)

and the rising edge of OCLK2 (= D2), which is typically the same as the falling edge of OCLK1. These two bits of data are multiplexed by the DDR mux and forwarded to the output pin. The D2 data signal must be re-synchronized from the OCLK1 clock domain to the OCLK2 domain using FPGA slice flip-flops. Placement is critical at high frequencies, because the time available is only one half a clock cycle. See Figure 10 for a graphical illustration of this function.

The C0 or C1 alignment feature of the ODDR2 flip-flop, originally introduced in the Spartan-3E FPGA family, is not recommended or supported in the ISE development software. The ODDR2 flip-flop without the alignment feature remains fully supported. Without the alignment feature, the ODDR2 feature behaves equivalent to the ODDR flip-flop on previous Xilinx FPGA families.

Figure 10: Output DDR

## **SelectIO Signal Standards**

The Spartan-3E I/Os feature inputs and outputs that support a wide range of I/O signaling standards (Table 6 and Table 7). The majority of the I/Os also can be used to form differential pairs to support any of the differential signaling standards (Table 7).

To define the I/O signaling standard in a design, set the IOSTANDARD attribute to the appropriate setting. Xilinx provides a variety of different methods for applying the IOSTANDARD for maximum flexibility. For a full description of different methods of applying attributes to control IOSTANDARD, refer to the Xilinx Software Manuals and Help.

Spartan-3E FPGAs provide additional input flexibility by allowing I/O standards to be mixed in different banks. For a particular  $V_{CCO}$  voltage, Table 6 and Table 7 list all of the

IOSTANDARDs that can be combined and if the IOSTANDARD is supported as an input only or can be used for both inputs and outputs.

Table 6: Single-Ended IOSTANDARD Bank Compatibility

|                            |                  | v <sub>cco</sub> s | Supply/Comp      | atibility        |                  | Input Req          | uirements                                          |

|----------------------------|------------------|--------------------|------------------|------------------|------------------|--------------------|----------------------------------------------------|

| Single-Ended<br>IOSTANDARD | 1.2V             | 1.5V               | 1.8V             | 2.5V             | 3.3V             | V <sub>REF</sub>   | Board<br>Termination<br>Voltage (V <sub>TT</sub> ) |

| LVTTL                      | -                | -                  | -                | -                | Input/<br>Output | N/R <sup>(1)</sup> | N/R                                                |

| LVCMOS33                   | -                | -                  | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| LVCMOS25                   | -                | -                  | -                | Input/<br>Output | Input            | N/R                | N/R                                                |

| LVCMOS18                   | -                | -                  | Input/<br>Output | Input            | Input            | N/R                | N/R                                                |

| LVCMOS15                   | -                | Input/<br>Output   | Input            | Input            | Input            | N/R                | N/R                                                |

| LVCMOS12                   | Input/<br>Output | Input              | Input            | Input            | Input            | N/R                | N/R                                                |

| PCl33_3                    | -                | -                  | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| PCI66_3                    | -                | -                  | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| HSTL_I_18                  | -                | -                  | Input/<br>Output | Input            | Input            | 0.9                | 0.9                                                |

| HSTL_III_18                | -                | -                  | Input/<br>Output | Input            | Input            | 1.1                | 1.8                                                |

| SSTL18_I                   | -                | -                  | Input/<br>Output | Input            | Input            | 0.9                | 0.9                                                |

| SSTL2_I                    | -                | -                  | -                | Input/<br>Output | Input            | 1.25               | 1.25                                               |

#### Notes:

1. N/R - Not required for input operation.

Table 7: Differential IOSTANDARD Bank Compatibility

| Differential     |                  | V <sub>CCO</sub> Supply                               |       |

|------------------|------------------|-------------------------------------------------------|-------|

| IOSTANDARD       | 1.8V             | 2.5V                                                  | 3.3V  |

| LVDS_25          | Input            | Input,<br>On-chip Differential Termination,<br>Output | Input |

| RSDS_25          | Input            | Input,<br>On-chip Differential Termination,<br>Output | Input |

| MINI_LVDS_25     | Input            | Input,<br>On-chip Differential Termination,<br>Output | Input |

| LVPECL_25        | Input            | Input                                                 | Input |

| BLVDS_25         | Input            | Input,<br>Output                                      | Input |

| DIFF_HSTL_I_18   | Input,<br>Output | Input                                                 | Input |

| DIFF_HSTL_III_18 | Input,<br>Output | Input                                                 | Input |

| DIFF_SSTL18_I    | Input,<br>Output | Input                                                 | Input |

| DIFF_SSTL2_I     | Input            | Input,<br>Output                                      | Input |

| Input<br>Requirements:<br>V <sub>REF</sub>           | Differential Bank<br>Restriction <sup>(1)</sup>                                        |

|------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                                      | Applies to Outputs<br>Only                                                             |

|                                                      | Applies to Outputs<br>Only                                                             |

|                                                      | Applies to Outputs<br>Only                                                             |

| V <sub>REF</sub> is not used for these I/O standards |                                                                                        |

|                                                      | No Differential Bank<br>Restriction<br>(other I/O bank<br>restrictions might<br>apply) |

#### Notes:

Each bank can support any two of the following: LVDS\_25 outputs, MINI\_LVDS\_25 outputs, RSDS\_25 outputs.

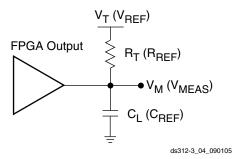

HSTL and SSTL inputs use the Reference Voltage ( $V_{REF}$ ) to bias the input-switching threshold. Once a configuration data file is loaded into the FPGA that calls for the I/Os of a given bank to use HSTL/SSTL, a few specifically reserved I/O pins on the same bank automatically convert to  $V_{REF}$  inputs. For banks that do not contain HSTL or SSTL,  $V_{REF}$  pins remain available for user I/Os or input pins.

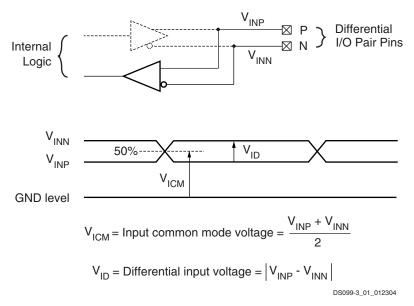

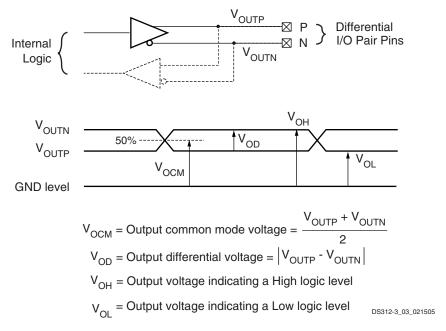

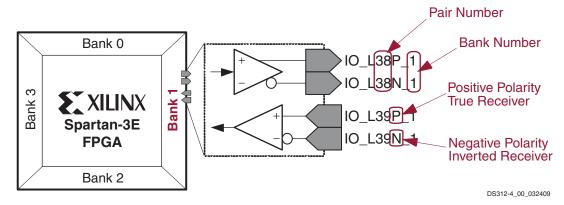

Differential standards employ a pair of signals, one the opposite polarity of the other. The noise canceling properties (for example, Common-Mode Rejection) of these standards permit exceptionally high data transfer rates. This subsection introduces the differential signaling capabilities of Spartan-3E devices.

Each device-package combination designates specific I/O pairs specially optimized to support differential standards. A unique *L-number*, part of the pin name, identifies the line-pairs associated with each bank (see Module 4, Pinout Descriptions). For each pair, the letters *P* and *N* designate the true and inverted lines, respectively. For example, the pin names IO\_L43P\_3 and IO\_L43N\_3 indicate the true and inverted lines comprising the line pair L43 on Bank 3.

$V_{CCO}$  provides current to the outputs and additionally powers the On-Chip Differential Termination.  $V_{CCO}$  must be 2.5V when using the On-Chip Differential Termination. The  $V_{RFF}$  lines are not required for differential operation.

To further understand how to combine multiple IOSTANDARDs within a bank, refer to IOBs Organized into Banks, page 19.

## **On-Chip Differential Termination**

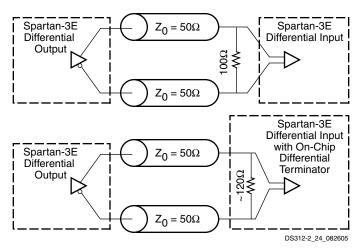

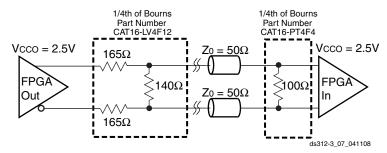

Spartan-3E devices provide an on-chip ~120 $\Omega$  differential termination across the input differential receiver terminals. The on-chip input differential termination in Spartan-3E devices potentially eliminates the external 100 $\Omega$  termination resistor commonly found in differential receiver circuits. Differential termination is used for LVDS, mini-LVDS, and RSDS as applications permit.

On-chip Differential Termination is available in banks with  $V_{CCO} = 2.5 V$  and is not supported on dedicated input pins. Set the DIFF\_TERM attribute to TRUE to enable Differential Termination on a differential I/O pin pair.

The DIFF\_TERM attribute uses the following syntax in the UCF file:

INST <I/O\_BUFFER\_INSTANTIATION\_NAME>

DIFF TERM = "<TRUE/FALSE>";

Figure 11: Differential Inputs and Outputs

## **Pull-Up and Pull-Down Resistors**

Pull-up and pull-down resistors inside each IOB optionally force a floating I/O or Input-only pin to a determined state. Pull-up and pull-down resistors are commonly applied to unused I/Os, inputs, and three-state outputs, but can be used on any I/O or Input-only pin. The pull-up resistor connects an IOB to  $V_{\rm CCO}$  through a resistor. The resistance value depends on the  $V_{\rm CCO}$  voltage (see Module 3, DC and Switching Characteristics for the specifications). The pull-down resistor similarly connects an IOB to ground with a resistor. The PULLUP and PULLDOWN attributes and library primitives turn on these optional resistors.

By default, PULLDOWN resistors terminate all unused I/O and Input-only pins. Unused I/O and Input-only pins can alternatively be set to PULLUP or FLOAT. To change the unused I/O Pad setting, set the Bitstream Generator (BitGen) option *UnusedPin* to PULLUP, PULLDOWN, or FLOAT. The *UnusedPin* option is accessed through the Properties for Generate Programming File in ISE. See Bitstream Generator (BitGen) Options.

During configuration a Low logic level on the HSWAP pin activates pull-up resistors on all I/O and Input-only pins not actively used in the selected configuration mode.

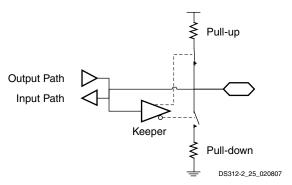

## Keeper Circuit

Each I/O has an optional keeper circuit (see Figure 12) that keeps bus lines from floating when not being actively driven. The KEEPER circuit retains the last logic level on a line after all drivers have been turned off. Apply the KEEPER attribute or use the KEEPER library primitive to use the KEEPER circuitry. Pull-up and pull-down resistors override the KEEPER settings.

Figure 12: Keeper Circuit

## **Slew Rate Control and Drive Strength**

Each IOB has a slew-rate control that sets the output switching edge-rate for LVCMOS and LVTTL outputs. The SLEW attribute controls the slew rate and can either be set to SLOW (default) or FAST.

Each LVCMOS and LVTTL output additionally supports up to six different drive current strengths as shown in Table 8. To adjust the drive strength for each output, the DRIVE attribute is set to the desired drive strength: 2, 4, 6, 8, 12, and 16. Unless otherwise specified in the FPGA application, the software default IOSTANDARD is LVCMOS25, SLOW slew rate, and 12 mA output drive.

Table 8: Programmable Output Drive Current

| IOSTANDARD | Output Drive Current (mA) |   |   |   |    |    |  |  |  |

|------------|---------------------------|---|---|---|----|----|--|--|--|

| IOSTANDARD | 2                         | 4 | 6 | 8 | 12 | 16 |  |  |  |

| LVTTL      | ~                         | ~ | ~ | ~ | ~  | ~  |  |  |  |

| LVCMOS33   | ~                         | ~ | ~ | ~ | ~  | ~  |  |  |  |

| LVCMOS25   | ~                         | ~ | ~ | ~ | ~  | -  |  |  |  |

| LVCMOS18   | ~                         | ~ | ~ | ~ | -  | -  |  |  |  |

| LVCMOS15   | ~                         | ~ | ~ | - | -  | -  |  |  |  |

| LVCMOS12   | •                         | - | - | - | -  | -  |  |  |  |

High output current drive strength and FAST output slew rates generally result in fastest I/O performance. However, these same settings generally also result in transmission line effects on the printed circuit board (PCB) for all but the shortest board traces. Each IOB has independent slew rate and drive strength controls. Use the slowest slew rate and lowest output drive current that meets the performance requirements for the end application.

Likewise, due to lead inductance, a given package supports a limited number of simultaneous switching outputs (SSOs) when using fast, high-drive outputs. Only use fast, high-drive outputs when required by the application.

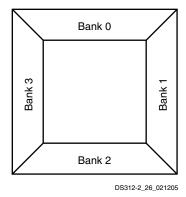

## **IOBs Organized into Banks**

The Spartan-3E architecture organizes IOBs into four I/O banks as shown in Figure 13. Each bank maintains separate  $V_{CCO}$  and  $V_{REF}$  supplies. The separate supplies allow each bank to independently set  $V_{CCO}$ . Similarly, the  $V_{REF}$  supplies can be set for each bank. Refer to Table 6 and Table 7 for  $V_{CCO}$  and  $V_{REF}$  requirements.

When working with Spartan-3E devices, most of the differential I/O standards are compatible and can be combined within any given bank. Each bank can support any two of the following differential standards: LVDS\_25 outputs, MINI\_LVDS\_25 outputs, and RSDS\_25 outputs. As an example, LVDS\_25 outputs, RSDS\_25 outputs, and any other differential inputs while using on-chip differential termination are a valid combination. A combination not allowed is a single bank with LVDS\_25 outputs, RSDS\_25 outputs, and MINI\_LVDS\_25 outputs.

Figure 13: Spartan-3E I/O Banks (top view)

## I/O Banking Rules

When assigning I/Os to banks, these  $V_{\mbox{\footnotesize{CCO}}}$  rules must be followed:

- 1. All  $V_{CCO}$  pins on the FPGA must be connected even if a bank is unused.

- 2. All V<sub>CCO</sub> lines associated within a bank must be set to the same voltage level.

- The V<sub>CCO</sub> levels used by all standards assigned to the I/Os of any given bank must agree. The Xilinx development software checks for this. Table 6 and Table 7 describe how different standards use the V<sub>CCO</sub> supply.

- 4. If a bank does not have any  $V_{CCO}$  requirements, connect  $V_{CCO}$  to an available voltage, such as 2.5V or 3.3V. Some configuration modes might place additional  $V_{CCO}$  requirements. Refer to Configuration for more information.

If any of the standards assigned to the Inputs of the bank use  $V_{\mbox{\scriptsize REF}}$ , then the following additional rules must be observed:

- 1. All V<sub>RFF</sub> pins must be connected within a bank.

- All V<sub>REF</sub> lines associated with the bank must be set to the same voltage level.

- The V<sub>REF</sub> levels used by all standards assigned to the Inputs of the bank must agree. The Xilinx development software checks for this. Table 6 describes how different standards use the V<sub>REF</sub> supply.

If  $V_{REF}$  is not required to bias the input switching thresholds, all associated  $V_{REF}$  pins within the bank can be used as user I/Os or input pins.

## **Package Footprint Compatibility**

Sometimes, applications outgrow the logic capacity of a specific Spartan-3E FPGA. Fortunately, the Spartan-3E family is designed so that multiple part types are available in pin-compatible package footprints, as described in Module 4, Pinout Descriptions. In some cases, there are subtle differences between devices available in the same footprint. These differences are outlined for each package, such as pins that are unconnected on one device but connected on another in the same package or pins that are dedicated inputs on one package but full I/O on another. When designing the printed circuit board (PCB), plan for potential future upgrades and package migration.

The Spartan-3E family is not pin-compatible with any previous Xilinx FPGA family.

## **Dedicated Inputs**

Dedicated Inputs are IOBs used only as inputs. Pin names designate a Dedicated Input if the name starts with IP, for example, IP or IP\_Lxxx\_x. Dedicated inputs retain the full functionality of the IOB for input functions with a single exception for differential inputs (IP\_Lxxx\_x). For the differential Dedicated Inputs, the on-chip differential termination is not available. To replace the on-chip differential termination, choose a differential pair that supports outputs (IO\_Lxxx\_x) or use an external  $100\Omega$  termination resistor on the board.

#### **ESD Protection**

Clamp diodes protect all device pads against damage from Electro-Static Discharge (ESD) as well as excessive voltage transients. Each I/O has two clamp diodes: one diode extends P-to-N from the pad to  $V_{\rm CCO}$  and a second diode extends N-to-P from the pad to GND. During operation, these diodes are normally biased in the off state. These clamp diodes are always connected to the pad, regardless of the signal standard selected. The presence of diodes limits the ability of Spartan-3E I/Os to tolerate high signal voltages. The  $V_{\rm IN}$  absolute maximum rating in Table 73 of Module 3, DC and Switching Characteristics specifies the voltage range that I/Os can tolerate.

## **Supply Voltages for the IOBs**

The IOBs are powered by three supplies:

- 1. The  $V_{\rm CCO}$  supplies, one for each of the FPGA's I/O banks, power the output drivers. The voltage on the  $V_{\rm CCO}$  pins determines the voltage swing of the output signal.

- 2. V<sub>CCINT</sub> is the main power supply for the FPGA's internal logic.

- V<sub>CCAUX</sub> is an auxiliary source of power, primarily to optimize the performance of various FPGA functions such as I/O switching.

## I/O and Input-Only Pin Behavior During Power-On, Configuration, and User Mode

In this section, all behavior described for I/O pins also applies to input-only pins and dual-purpose I/O pins that are not actively involved in the currently-selected configuration mode.

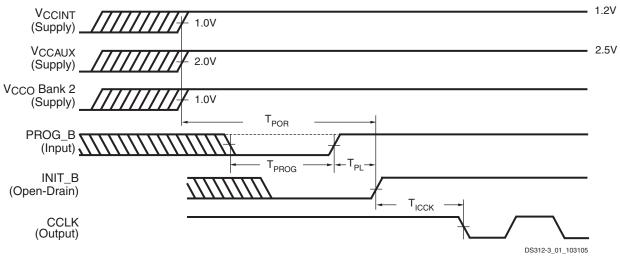

All I/O pins have ESD clamp diodes to their respective  $V_{CCO}$  supply and from GND, as shown in Figure 5. The  $V_{CCINT}$  (1.2V),  $V_{CCAUX}$  (2.5V), and  $V_{CCO}$  supplies can be applied in any order. Before the FPGA can start its configuration process,  $V_{CCINT}$ ,  $V_{CCO}$  Bank 2, and  $V_{CCAUX}$  must have reached their respective minimum recommended operating levels indicated in Table 74. At this time, all output drivers are in a high-impedance state.  $V_{CCO}$  Bank 2,  $V_{CCINT}$ , and  $V_{CCAUX}$  serve as inputs to the internal Power-On Reset circuit (POR).

A Low level applied to the HSWAP input enables pull-up resistors on user-I/O and input-only pins from power-on throughout configuration. A High level on HSWAP disables the pull-up resistors, allowing the I/Os to float. HSWAP contains an internal pull-up resistor and defaults to High if left floating. As soon as power is applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally asserts the Global Set-Reset (GSR), which asynchronously resets all IOB storage elements to a default Low state. Also see Pin Behavior During Configuration.

Upon the completion of initialization and the beginning of configuration, INIT\_B goes High, sampling the M0, M1, and M2 inputs to determine the configuration mode. Configuration data is then loaded into the FPGA. The I/O drivers remain in a high-impedance state (with or without pull-up resistors, as determined by the HSWAP input) throughout configuration.

At the end of configuration, the GSR net is released, placing the IOB registers in a Low state by default, unless the loaded design reverses the polarity of their respective SR inputs.

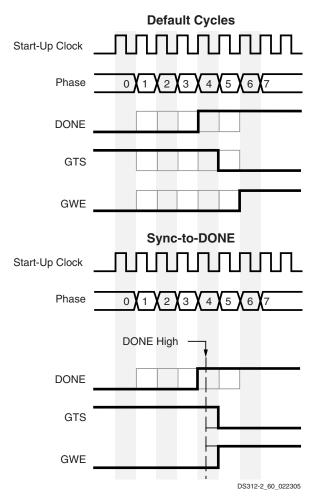

The Global Three State (GTS) net is released during Start-Up, marking the end of configuration and the

beginning of design operation in the User mode. After the GTS net is released, all user I/Os go active while all unused I/Os are pulled down (PULLDOWN). The designer can control how the unused I/Os are terminated after GTS is released by setting the Bitstream Generator (BitGen) option UnusedPin to PULLUP, PULLDOWN, or FLOAT.

One clock cycle later (default), the Global Write Enable (GWE) net is released allowing the RAM and registers to change states. Once in User mode, any pull-up resistors enabled by HSWAP revert to the user settings and HSWAP is available as a general-purpose I/O. For more information on PULLUP and PULLDOWN, see Pull-Up and Pull-Down Resistors.

## Behavior of Unused I/O Pins After Configuration

By default, the Xilinx ISE development software automatically configures all unused I/O pins as input pins with individual internal pull-down resistors to GND.

This default behavior is controlled by the *UnusedPin* bitstream generator (BitGen) option, as described in Table 69.

## JTAG Boundary-Scan Capability

All Spartan-3E IOBs support boundary-scan testing compatible with IEEE 1149.1/1532 standards. During boundary-scan operations such as EXTEST and HIGHZ the pull-down resistor is active. See JTAG Mode for more information on programming via JTAG.

## Configurable Logic Block (CLB) and Slice Resources

For additional information, refer to the "Using Configurable Logic Blocks (CLBs)" chapter in UG331.

#### **CLB Overview**

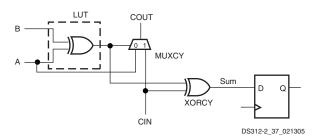

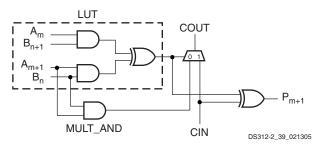

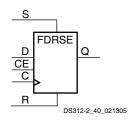

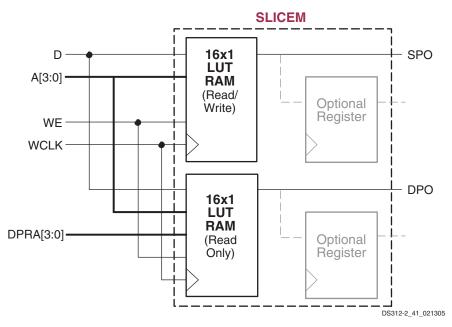

The Configurable Logic Blocks (CLBs) constitute the main logic resource for implementing synchronous as well as combinatorial circuits. Each CLB contains four slices, and each slice contains two Look-Up Tables (LUTs) to implement logic and two dedicated storage elements that can be used as flip-flops or latches. The LUTs can be used as a 16x1 memory (RAM16) or as a 16-bit shift register

(SRL16), and additional multiplexers and carry logic simplify wide logic and arithmetic functions. Most general-purpose logic in a design is automatically mapped to the slice resources in the CLBs. Each CLB is identical, and the Spartan-3E family CLB structure is identical to that for the Spartan-3 family.

## **CLB Array**

The CLBs are arranged in a regular array of rows and columns as shown in Figure 14.

Each density varies by the number of rows and columns of CLBs (see Table 9).

Figure 14: CLB Locations

Table 9: Spartan-3E CLB Resources

| Device    | CLB<br>Rows | CLB<br>Columns | CLB<br>Total <sup>(1)</sup> | Slices | LUTs /<br>Flip-Flops | Equivalent<br>Logic Cells | RAM16 /<br>SRL16 | Distributed<br>RAM Bits |

|-----------|-------------|----------------|-----------------------------|--------|----------------------|---------------------------|------------------|-------------------------|

| XC3S100E  | 22          | 16             | 240                         | 960    | 1,920                | 2,160                     | 960              | 15,360                  |

| XC3S250E  | 34          | 26             | 612                         | 2,448  | 4,896                | 5,508                     | 2,448            | 39,168                  |

| XC3S500E  | 46          | 34             | 1,164                       | 4,656  | 9,312                | 10,476                    | 4,656            | 74,496                  |

| XC3S1200E | 60          | 46             | 2,168                       | 8,672  | 17,344               | 19,512                    | 8,672            | 138,752                 |

| XC3S1600E | 76          | 58             | 3,688                       | 14,752 | 29,504               | 33,192                    | 14,752           | 236,032                 |

#### Notes:

The number of CLBs is less than the multiple of the rows and columns because the block RAM/multiplier blocks and the DCMs are embedded in the array (see Figure 1 in Module 1).

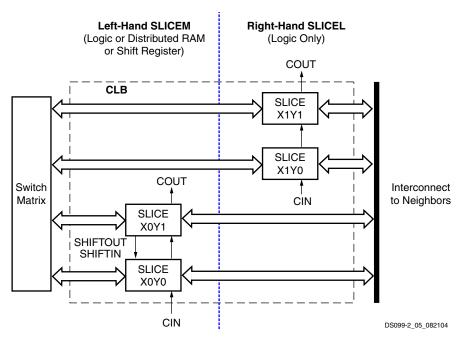

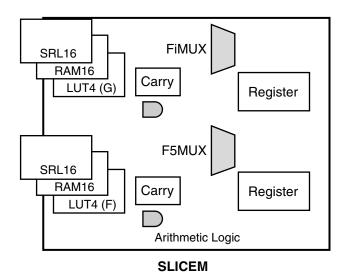

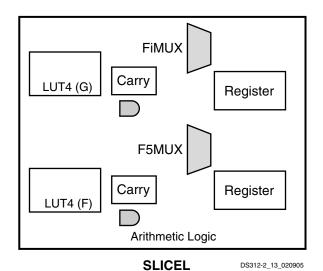

### **Slices**

Each CLB comprises four interconnected slices, as shown in Figure 16. These slices are grouped in pairs. Each pair is organized as a column with an independent carry chain. The left pair supports both logic and memory functions and its slices are called SLICEM. The right pair supports logic only and its slices are called SLICEL. Therefore half the

LUTs support both logic and memory (including both RAM16 and SRL16 shift registers) while half support logic only, and the two types alternate throughout the array columns. The SLICEL reduces the size of the CLB and lowers the cost of the device, and can also provide a performance advantage over the SLICEM.

### Notes:

- 1. Options to invert signal polarity as well as other options that enable lines for various functions are not shown.

- 2. The index i can be 6, 7, or 8, depending on the slice. The upper SLICEL has an F8MUX, and the upper SLICEM has an F7MUX. The lower SLICEL and SLICEM both have an F6MUX.

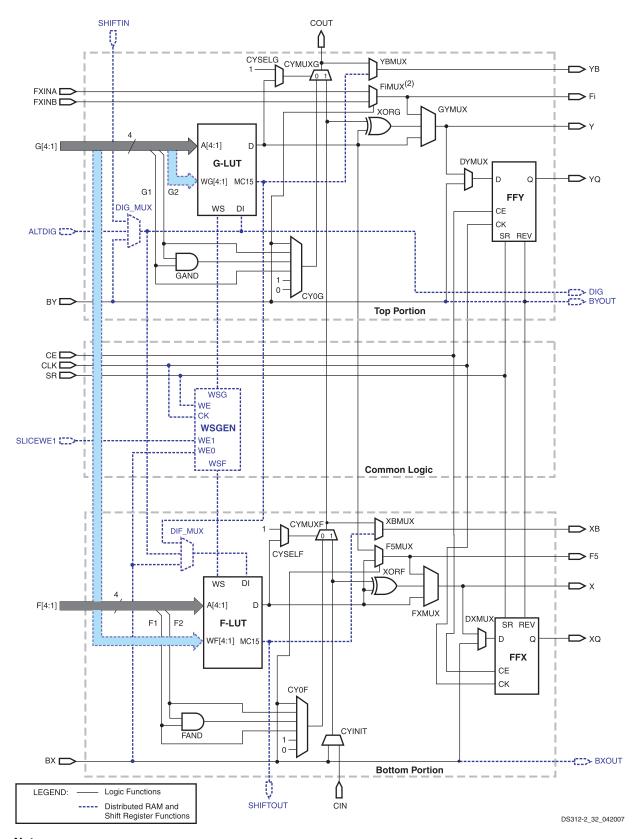

Figure 15: Simplified Diagram of the Left-Hand SLICEM

Figure 16: Arrangement of Slices within the CLB

#### Slice Location Designations

The Xilinx development software designates the location of a slice according to its X and Y coordinates, starting in the bottom left corner, as shown in Figure 14. The letter 'X' followed by a number identifies columns of slices, incrementing from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row, incrementing from the bottom of the die. Figure 16 shows the CLB located in the lower left-hand corner of the die. The SLICEM always has an even 'X' number, and the SLICEL always has an odd 'X' number.

#### Slice Overview

A slice includes two LUT function generators and two storage elements, along with additional logic, as shown in Figure 17.

Both SLICEM and SLICEL have the following elements in common to provide logic, arithmetic, and ROM functions:

- Two 4-input LUT function generators, F and G

- Two storage elements

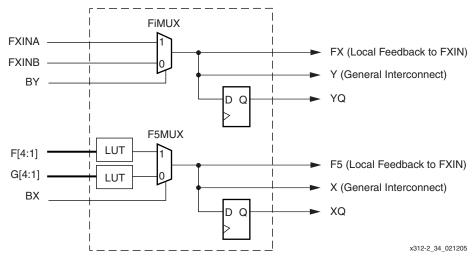

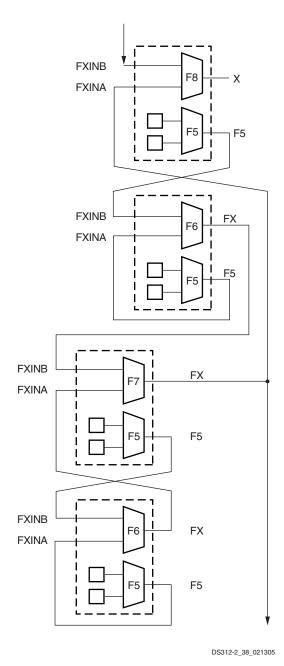

- Two wide-function multiplexers, F5MUX and FiMUX

- Carry and arithmetic logic

Figure 17: Resources in a Slice

The SLICEM pair supports two additional functions:

- Two 16x1 distributed RAM blocks, RAM16

- Two 16-bit shift registers, SRL16

Each of these elements is described in more detail in the following sections.

## **Logic Cells**

The combination of a LUT and a storage element is known as a "Logic Cell". The additional features in a slice, such as the wide multiplexers, carry logic, and arithmetic gates, add to the capacity of a slice, implementing logic that would otherwise require additional LUTs. Benchmarks have shown that the overall slice is equivalent to 2.25 simple logic cells. This calculation provides the equivalent logic cell count shown in Table 9.

#### Slice Details

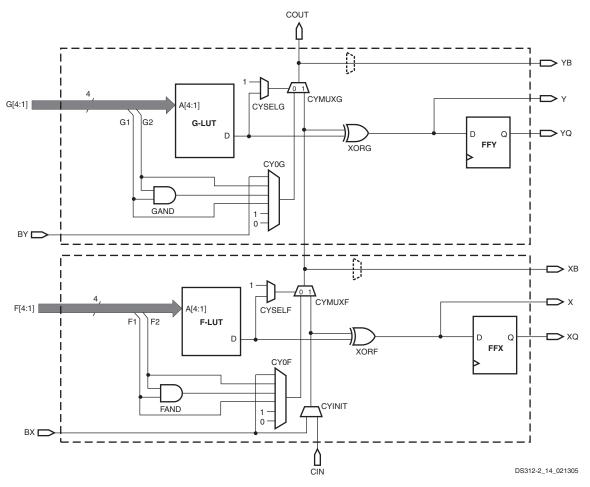

Figure 15 is a detailed diagram of the SLICEM. It represents a superset of the elements and connections to be found in all slices. The dashed and gray lines (blue when viewed in color) indicate the resources found only in the SLICEM and not in the SLICEL.

Each slice has two halves, which are differentiated as top and bottom to keep them distinct from the upper and lower slices in a CLB. The control inputs for the clock (CLK), Clock Enable (CE), Slice Write Enable (SLICEWE1), and Reset/Set (RS) are shared in common between the two halves.

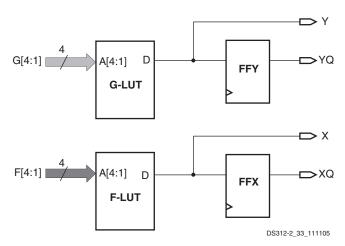

The LUTs located in the top and bottom portions of the slice are referred to as "G" and "F", respectively, or the "G-LUT" and the "F-LUT". The storage elements in the top and bottom portions of the slice are called FFY and FFX, respectively.

Each slice has two multiplexers with F5MUX in the bottom portion of the slice and FiMUX in the top portion. Depending on the slice, the FiMUX takes on the name F6MUX, F7MUX, or F8MUX, according to its position in the multiplexer chain. The lower SLICEL and SLICEM both have an F6MUX. The upper SLICEM has an F7MUX, and the upper SLICEL has an F8MUX.

The carry chain enters the bottom of the slice as CIN and exits at the top as COUT. Five multiplexers control the chain: CYINIT, CY0F, and CYMUXF in the bottom portion and CY0G and CYMUXG in the top portion. The dedicated arithmetic logic includes the exclusive-OR gates XORF and XORG (bottom and top portions of the slice, respectively) as well as the AND gates FAND and GAND (bottom and top portions, respectively).

See Table 10 for a description of all the slice input and output signals.

Table 10: Slice Inputs and Outputs

| Name     | Location        | Direction | Description                                                                                                                     |

|----------|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| F[4:1]   | SLICEL/M Bottom | Input     | F-LUT and FAND inputs                                                                                                           |

| G[4:1]   | SLICEL/M Top    | Input     | G-LUT and GAND inputs or Write Address (SLICEM)                                                                                 |

| BX       | SLICEL/M Bottom | Input     | Bypass to or output (SLICEM) or storage element, or control input to F5MUX, input to carry logic, or data input to RAM (SLICEM) |

| BY       | SLICEL/M Top    | Input     | Bypass to or output (SLICEM) or storage element, or control input to FiMUX, input to carry logic, or data input to RAM (SLICEM) |

| BXOUT    | SLICEM Bottom   | Output    | BX bypass output                                                                                                                |

| BYOUT    | SLICEM Top      | Output    | BY bypass output                                                                                                                |

| ALTDIG   | SLICEM Top      | Input     | Alternate data input to RAM                                                                                                     |

| DIG      | SLICEM Top      | Output    | ALTDIG or SHIFTIN bypass output                                                                                                 |

| SLICEWE1 | SLICEM Common   | Input     | RAM Write Enable                                                                                                                |

| F5       | SLICEL/M Bottom | Output    | Output from F5MUX; direct feedback to FiMUX                                                                                     |

| FXINA    | SLICEL/M Top    | Input     | Input to FiMUX; direct feedback from F5MUX or another FiMUX                                                                     |

| FXINB    | SLICEL/M Top    | Input     | Input to FiMUX; direct feedback from F5MUX or another FiMUX                                                                     |

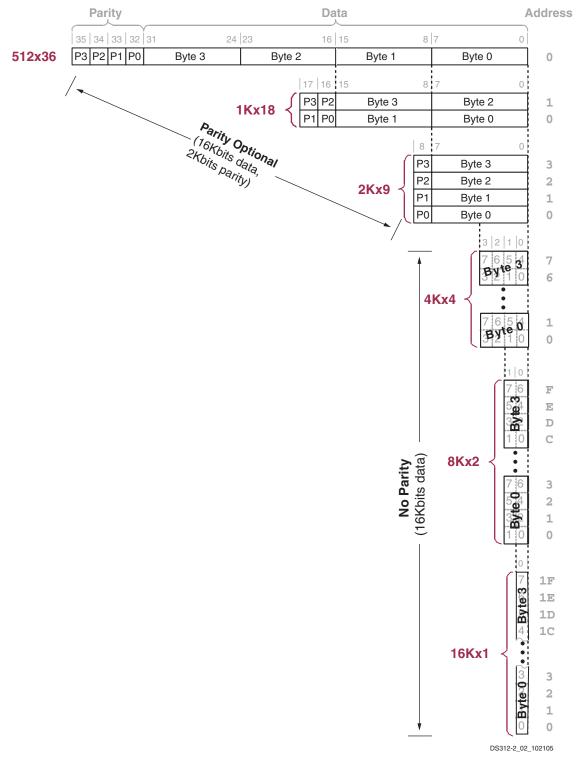

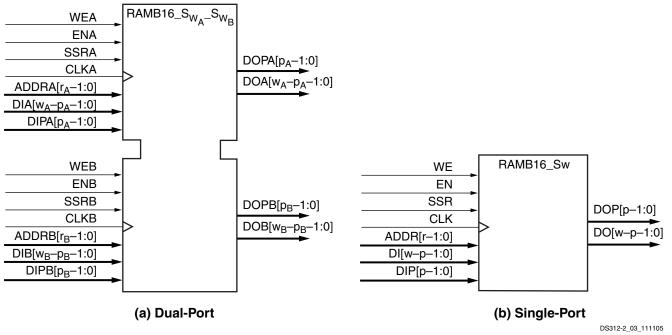

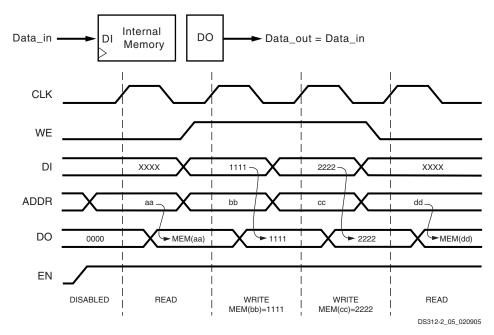

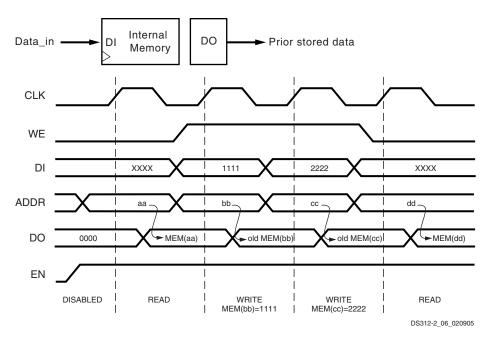

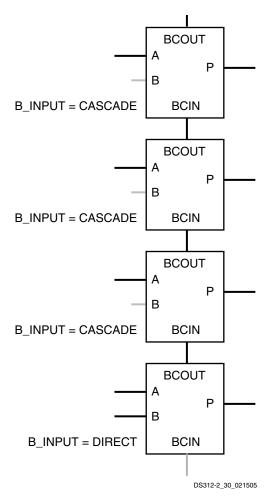

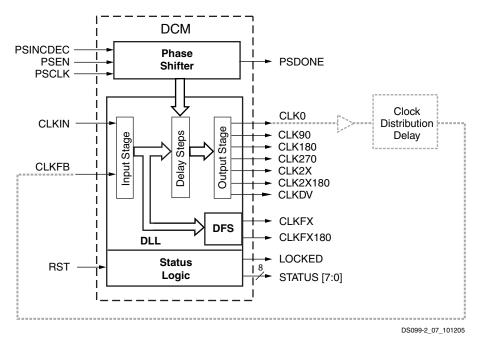

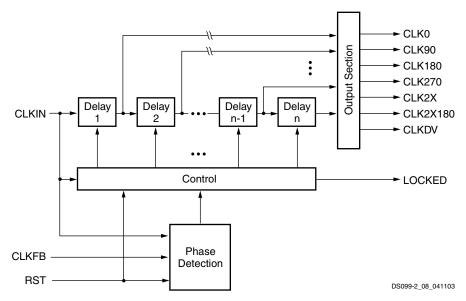

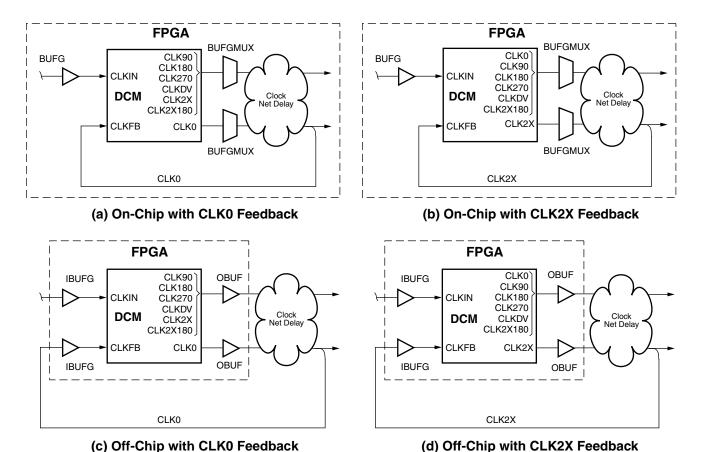

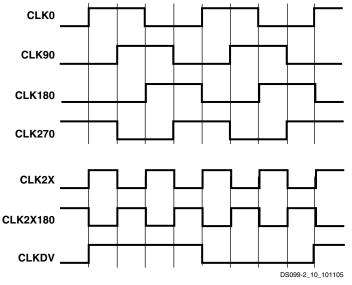

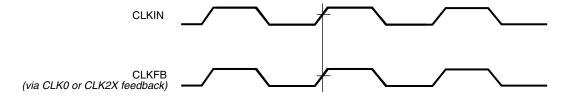

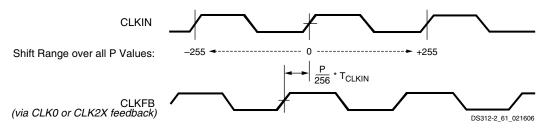

| Fi       | SLICEL/M Top    | Output    | Output from FiMUX; direct feedback to another FiMUX                                                                             |