High-Voltage Types(20-Volt Rating) XD4518 Dual BCD UP-Counter

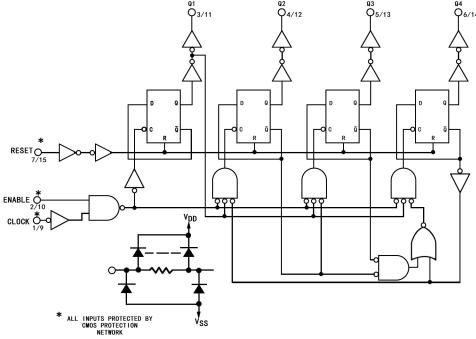

■ XD4518 Dual BCD Up-Counter nous 4-stage counters. The counter stages are D-type flip-flops having interchangeable CLOCK and ENABLE lines for incrementingon either the positive-going or negative-going transition. For single-unit operation the ENABLE input is maintained high and the counter advances on each positive\*going transition of the CLOCK. The counters are cleared by high levels on their RESET lines. The counter can be cascaded in the ripplemode by connecting Q4 to the enable input

#### Features:

- Medium speed operation 6-MHz typical clock frequency at 10 V

- Positive- or negative-edge teiggering

- Synchronous internal carry propagation

- 100% tested for quiescent current at 20 V

- Maximum input current of 1µA at 18 V over full package-temperature range: 100 nA at 18V and 25°C

- Noise margin(over full package-temperature range): 1 V at V<sub>DD</sub> = 5 V

2 V at V<sub>DD</sub> = 10V

2.5 V at V<sub>DD</sub> = 15V

- 5-V,10-V,and 15-V perametric ratings

- Standardized, symmetrical output characteristics

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard SPecifications fpr Description of 'b' Series CMOS Devices"

| MAXIMUM RATINGS, Absolute- Maximum Values:                                |

|---------------------------------------------------------------------------|

| DC SUPPLY-VOLTAGE RANGE, (V <sub>DD</sub> )                               |

| Voltages referenced to Vss Terminal)0.5V to +20V                          |

| INPUTVOLTAGE RANGE, ALL INPUTS                                            |

| DC INPUT CURRENT, ANY ONE INPUT                                           |

| POWER DISSIPATION PER PACKAGE (PD):                                       |

| ForT <sub>A</sub> = -55°C to +100°C                                       |

| ForT <sub>A</sub> = +100°C to +125°C DerateLinearity at 12mW/°C to 200mW  |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                  |

| FORTA = FULL PACKAGE-TEMPERATURE RANGE (All Package Types)                |

| OPERATING-TEMPERATURE RANGE (T <sub>A</sub> )                             |

| STORAGE TEMPERATURE RANGE (Tstg)65°C to +150°C                            |

| LEAD TEMPERATURE (DURING SOLDERING):                                      |

| At distance $1/16\pm 1/32$ inch $(1.59\pm 0.79$ mm) from case for 10s max |

| CLOCK | ENABLE | RESET | ACTION            |

|-------|--------|-------|-------------------|

| _     | 1      | 0     | Increment Counter |

| 0     | 7      | 0     | Increment Counter |

|       | Х      | 0     | No Change         |

| Х     | _      | 0     | No Change         |

| _     | 0      | 0     | No Change         |

| 1     | _      | 0     | No Change         |

| Х     | Х      | 0     | Q1 thru Q4 = 0    |

X = Don't Care 1 = High State 0 = Low State

#### Applications:

- Multistage synchronous counting

- Multistage ripple counting

- frequency dividers

#### TRUTH TABLE

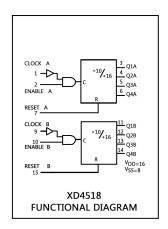

XD4518 TERMINAL ASSIGNMENT

#### STATIC ELECTRLCAL CHARACTERISTICS

| CHRACTER-                   | CON         | DITION | s        | LIMITS AT INDICATED TEMPERATURES(°C) |        |        |              | °C)    | UNITS             |       |            |  |

|-----------------------------|-------------|--------|----------|--------------------------------------|--------|--------|--------------|--------|-------------------|-------|------------|--|

| ISTIC                       | V0          | VIN    | $v_{DD}$ |                                      |        |        |              |        | +25               |       |            |  |

|                             | (V)         | (V)    | (V)      | -55                                  | -40    | +85    | +125         | Min    | Тур               | Max   |            |  |

|                             | ı           | 0, 5   | 5        | 5                                    | 5      | 150    | 150          | ı      | 0. 04             | 5     |            |  |

| Quiescent Device<br>Current | -           | 0, 10  | 10       | 10                                   | 10     | 300    | 300          | 1      | 0.04              | 10    | цA         |  |

| I DD Max.                   | -           | 0, 15  | 15       | 20                                   | 20     | 600    | 600          | -      | 0.04              | 20    | μА         |  |

|                             | -           | 0, 20  | 20       | 100                                  | 100    | 3000   | 3000         | -      | 0. 08             | 100   |            |  |

| Qutput Low                  | 0.4         | 0, 5   | 5        | 0.64                                 | 0. 61  | 0. 42  | 0. 36        | 0. 51  | 1                 | -     |            |  |

| (Sink)Current               | 0.5         | 0, 10  | 10       | 1. 6                                 | 1. 5   | 1. 1   | 0.9          | 1. 3   | 2. 6              | -     |            |  |

| ` loĽ Min.                  | 1.5         | 0, 15  | 15       | 4. 2                                 | 4      | 2. 8   | 2. 4         | 3. 4   | 6.8               | 1     |            |  |

| Qutput High                 | 4. 6        | 0, 5   | 5        | -0. 64                               | -0. 61 | -0. 42 | -0. 36       | -0. 51 | -1                | -     | mA         |  |

| (Source)                    | 2. 5        | 0, 5   | 5        | -2                                   | -1.8   | -1. 3  | <b>−1.15</b> | -1.6   | -3. 2             | ı     |            |  |

| Current,<br>IOH Min.        | 9.5         | 0, 10  | 10       | -1. 6                                | -1.5   | -1. 1  | -0. 9        | -1.3   | -2. 6             | -     |            |  |

| 'Un WIIII.                  | 13. 5       | 0, 15  | 15       | -4. 2                                | -4     | -2. 8  | -2. 4        | -3.4   | -6. 8             | -     |            |  |

| Output Voltage:             | -           | 0, 5   | 5        | 0.05                                 |        |        |              | -      | 0                 | 0.05  |            |  |

| Low-Level,                  | -           | 0, 10  | 10       | 0.05                                 |        |        |              | _      | 0                 | 0. 02 |            |  |

| V <sub>OL</sub> Max.        | -           | 0, 15  | 15       | 0.05                                 |        |        |              | ı      | 0                 | 0.02  | v          |  |

| Output Voltage:             | -           | 0, 5   | 5        | 4. 95                                |        |        |              | 4. 95  | 5                 | -     |            |  |

| High-Level,                 | -           | 0, 10  | 10       | 9.95                                 |        |        | 9.95         | 10     | -                 |       |            |  |

| V <sub>OH</sub> Min.        | _           | 0, 15  | 15       |                                      | 14. 95 |        |              | 14. 95 | 15                | _     |            |  |

| Lnput Low                   | 0. 5, 4. 5  | _      | 5        |                                      |        | 1.5    |              | _      | _                 | 1.5   |            |  |

| Voltage,                    | 1, 9        | _      | 10       |                                      |        | 3      |              | -      | -                 | 3     |            |  |

| V <sub>IL</sub> Max.        | 1. 5, 3. 5  | -      | 15       | 4                                    |        |        |              | _      | _                 | 4     |            |  |

| Input High<br>Voltage,      | 0. 5, 4. 5  | _      | 5        | 3.5                                  |        |        |              | 3.5    | _                 | _     | V          |  |

|                             | 1, 9        | _      | 10       |                                      |        | 7      |              | 7      | ı                 | _     |            |  |

| VIH Min.                    | 1. 5, 13. 5 | -      | 15       | 11                                   |        |        |              | 11     | -                 | -     |            |  |

| Input Current<br>IJN Max.   | _           | 0, 18  | 18       | ±0,1                                 | ±0.1   | ±1     | ±1           | _      | ±10 <sup>-5</sup> | ±01   | μ <b>A</b> |  |

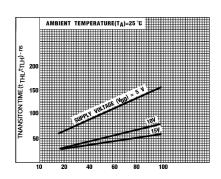

Typical transition time vs. load capacitance.

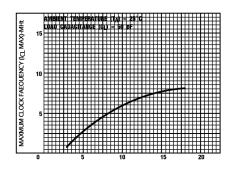

Typical maximum-clock-frequency vs. supply voltage.

#### DRAIN-TO-SOURCE VOLTAGE(VDS)-V

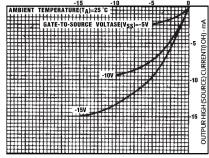

Minimum output high (source) current characterisitics.

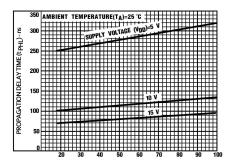

Typical propagation delay vs. load capacitance, clock or enable to output.

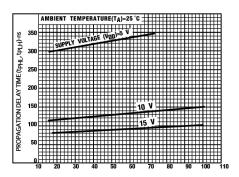

Typical propagation delay time vs. load capacitance, reset to output.

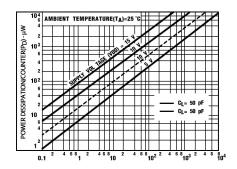

Typical power dissipation characteristics.

RECOMMENDED OPERATING CONDITIONS at TA =  $25\,^{\circ}$ C,Except as Noted. For maximum reliability,nominal operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                                     | VDD | LIN |     |            |

|--------------------------------------------------------------------|-----|-----|-----|------------|

| GRANAG IERISTIG                                                    | (V) | Min | Max | UNITS      |

| Supply-Voltage Range (For TA = Full Pack age<br>Temperature Range) |     | 3   | 18  | V          |

|                                                                    | 5   | 400 | -   |            |

| Enable pulse Width , <sup>t</sup> W .                              | 10  | 200 | -   | ns         |

|                                                                    | 15  | 140 | -   |            |

| Clock Pulse Width,¹W                                               | 5   | 200 | -   |            |

|                                                                    | 10  | 100 | -   | ns         |

|                                                                    | 15  | 70  | -   |            |

|                                                                    | 5   |     | 1.5 |            |

| Clock Input Frequency, fCL                                         | 10  | dc  | 3   | MHz        |

| mpar rroquency, en                                                 | 15  |     | 4   |            |

|                                                                    | 5   |     | 15  |            |

| Clock Rise or Fall Time,t <sub>f</sub> CL or t <sub>f</sub> CL:    | 10  | -   | 5   | μ <b>s</b> |

|                                                                    | 15  |     | 5   |            |

|                                                                    | 5   | 250 |     |            |

| Reset Pulse Width, <sup>t</sup> W                                  | 10  | 110 | -   | ns         |

|                                                                    | 15  | 80  |     |            |

### DYNAMIC ELECTRICAL CHARACTERISTICS at TA = 25 $^{\circ}C\colon$ Input $t_r,t_f{=}20$ ns, CL =50 pF, RL =200 K $\Omega$

|                                                           | TEST COND |                      |     |      |     |       |

|-----------------------------------------------------------|-----------|----------------------|-----|------|-----|-------|

| CHARACTERISTIC                                            |           | V <sub>DD</sub><br>V | Min | Тур  | Max | UNITS |

| December Dalay Time tout to U.                            |           | 5                    |     | 280  | 560 |       |

| Propagation Delay Time, tPHL, tPLH:                       |           | 10                   | -   | 115  | 230 |       |

| Clock or Enable to Qutput                                 |           | 15                   |     | 80   | 160 | ns    |

| Reset to Qutput                                           |           | 5                    |     | 330  | 650 | 115   |

|                                                           |           | 10                   | -   | 130  | 225 |       |

|                                                           |           | 15                   |     | 90   | 170 |       |

| Transition time, <sup>t</sup> THL <sup>t</sup> TLH        |           | 5                    |     | 100  | 200 |       |

|                                                           |           | 10                   | -   | 50   | 100 | ns    |

|                                                           |           | 15                   |     | 40   | 80  |       |

|                                                           |           | 5                    | 1.5 | 3    |     |       |

| Maximum Clock Input Frequency, <sup>f</sup> CL            |           | 10                   | 3   | 6    | -   | MHz   |

|                                                           |           | 15                   | 4   | 8    |     |       |

|                                                           |           | 5                    |     | 100  | 200 |       |

| Maximum Clock Pulse Width, <sup>t</sup> W                 |           | 10                   |     | 50   | 100 | ns    |

|                                                           |           | 15                   |     | 35   | 80  |       |

|                                                           |           | 5                    |     |      | 4.5 |       |

| Clock Rise or Fall Time <sup>t</sup> r or <sup>t</sup> f: |           | 10, 15               | -   | _ 15 | μs  |       |

|                                                           |           | 10, 15               |     |      | 5   |       |

|                                                           |           | 5                    |     | 125  | 250 |       |

| Minimum Reset Pulse Widtjh, <sup>t</sup> W                |           | 10                   | -   | 55   | 110 | ns    |

|                                                           |           | 15                   |     | 40   | 80  |       |

| Minimum Enable Pulse Widtjh, <sup>t</sup> W               |           | 5                    |     | 200  | 400 |       |

|                                                           |           | 10                   | -   | 100  | 200 | ns    |

|                                                           |           | 15                   |     | 70   | 140 |       |

| Input Capacitance,CIN                                     | Any Input |                      |     | 5    | 7.5 | pF    |

###

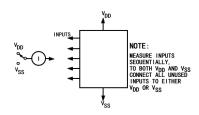

Dynamic power dissipartion

$t_r, t_f=20$  ns

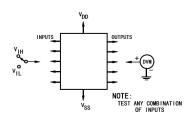

Input voltage.

Quiescent device current test circuit.

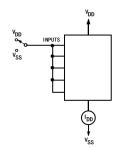

Input leakage-current test circuit

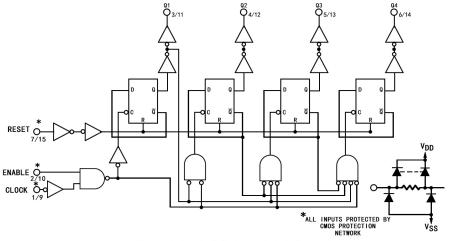

Decade counter (XD4518) logic diagram for one of two identical counters.

Binary counter (XD4518) logic diagram for one of two identical counters.

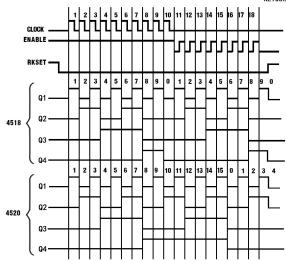

Timing diagrams for XD4518.

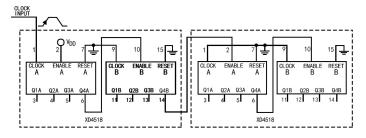

Ripple cascading of four counters with positive edge teiggering.

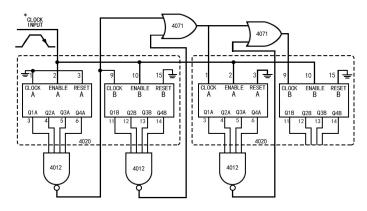

\* NOTE:

FOR SYNCHRONUS CCASCADING THE CLOCK TRANSITION

TIME SHOULD BE MADE LESS THAN OR EQUAL TO THE

SUN OF THE FIXED PROPAGATION DELAY AT 15pF AND

THE TRANSITION TIME OF THE OUTPUT DRIVES TAGE

FOR THE ESTIMATED CAPACITATIVE LOAD.

${\it Synchronous \ cascading \ of \ four \ binary \ counters \ with \ negative \ edge \ telggering.}$

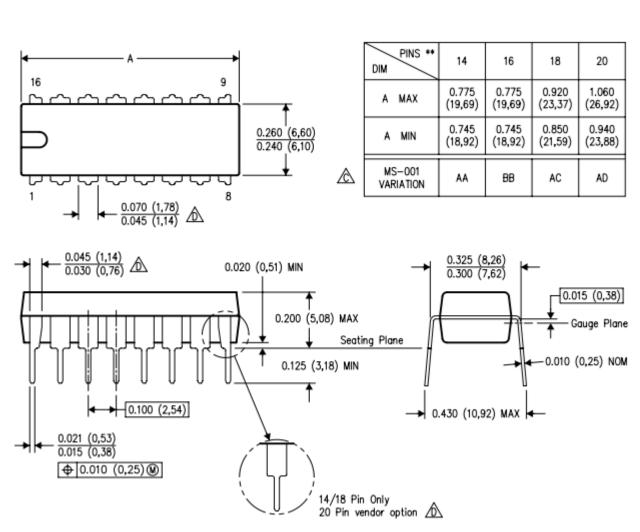

DIP

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Timers & Support Products category:

Click to view products by XINLUDA manufacturer:

Other Similar products are found below:

NLV14541BDR2G MIC1557YD5-TR Z84C3010AEG MIC1555YMU-TR NLV14541BDG MAX7375AXR365+T MIC1555YD5-TR

PT8A2515TAEX PT8A2514APE S-35710M01I-E8T3U LTC6992CDCB-2#TRMPBF SY87700ALZG LM555CM LMC555CM

FT8010UMX FTL11639UCX MAX809TEUR+ MAX7375AXR185+T MAX7375AXR105+T MAX3634ETM+ FTL75939UCX NA555S13 NB7N017MMNG NJM555D 82P33731ABAG TLC555MJG MAX7375AXR405+T Z84C3006PEG SA555S-13 MAX7375AXR805T

SY87701ALHG MCP130-475HI/TO S-1410G28-K8T2U4 VSC8115XYA-05-T VSC8115XYA-06-T LTC6992CS6-3#TRMPBF

NLV14541BDTR2G 636058D S-1410H30-K8T2U4 S-35710C01I-K8T2U S-35770E01I-K8T2U S-35720C01I-K8T2U S-35720C02IK8T2U S-35730C01I-K8T2U S-35740C01I-K8T2U ALD1502SAL ALD2502SBL ALD4501PEL ALD4501SEL ALD555PAL