- Parallel Inputs and Outputs

- Four Operating Modes:

Synchronous Parallel Load Right Shift Left Shift Do Nothing

- Positive Edge-Triggered Clocking

- Direct Overriding Clear

| TYPE    | TYPICAL<br>MAXIMUM<br>CLOCK<br>FREQUENCY | TYPICAL<br>POWER<br>DISSIPATION |

|---------|------------------------------------------|---------------------------------|

| 74LS194 | 36 MHz                                   | 75 mW                           |

## description

Thasa bidirectional shift registers are designed to incorporate virtually all of the features a system designer may want ina shift register. TM circuit contain\* 46 equivalent gates and features paraMI inputs, parallel outputs, right-shift and left-shift serial inputs, operMino-mode-control inputs, and a direct overriding clear line. The rtgister has four distinct modes of operation, namely:

Inhibit clock (do nothing)

Shift right (in the direction Qa toward Qd) Shift left On the direction Qq toward Qa) Parallol (broadside) load

Synchronoua parallel loading Is accomplished by applying the four bits of data and taking both mode control inputs, SO and SI, high. The 4ata are loaded into the associated fnp\*flops and appear at the outputs after ttw positivn transition of the clock input. During loading, sorial data flow is inhibited.

Shift right is accomplished synchronouBly with the rising edge of th® clock pulse when SO is high and S1 Is low. Serial data for this modB is entered at the shift-right data input. When SO Ia low and \$1 is high, data shifts left synchronously and now data ic entered at the shift-left serial input. Clocking of the shift register 询 inhibited when both mode control inputs are low. The mode controls of the XD74LS194 should be changed only whHe the clock input le high.

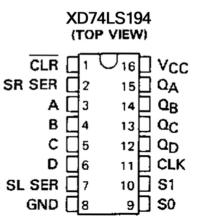

# XD74LS194 DIP-16

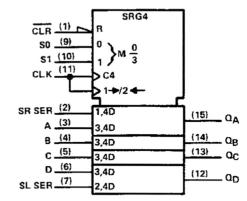

logic symbol<sup>†</sup>

|       | FUNCTION TABLE |    |        |      |       |   |      |     |     |                 |                 |                 |                 |   |

|-------|----------------|----|--------|------|-------|---|------|-----|-----|-----------------|-----------------|-----------------|-----------------|---|

|       | INPUTS         |    |        |      |       |   |      |     | OUT | PUTS            |                 |                 |                 |   |

|       | MO             | DE | 01.00% | SE   | IAL   |   | PARA | LLE | -   |                 | α <sub>B</sub>  | QC              | 0-              | Ι |

| CLEAR | S1             | SO | CLOCK  | LEFT | RIGHT | A | в    | С   | D   | QA              |                 |                 | QD              |   |

| L     | x              | x  | х      | X    | x     | X | х    | х   | x   | L               | L               | L               | Г               |   |

| н     | х              | х  | L      | x    | ×     | × | х    | х   | х   | QA0             | QB0             | $Q_{CO}$        | apo             |   |

| н     | н              | н  | t      | x    | x     | а | ь    | с   | d   | а               | b               | с               | d               |   |

| н     | L              | н  | †      | x    | H.    | × | х    | х   | ×   | н               | Q <sub>Ап</sub> | QBn             | QCn             | 1 |

| н     | L              | н  | 1      | x    | L     | X | х    | х   | х   | ι               | Q <sub>An</sub> | OBn             | QСп             |   |

| н     | н              | L  | †      | н    | ×     | × | х    | х   | х   | QBn             | Q <sub>Cn</sub> | Q <sub>Dn</sub> | н               |   |

| н     | н              | L  | 1      | L    | ×     | X | х    | х   | х   | QBn             | QCn             | Q <sub>Dп</sub> | L               |   |

| н     | L              | L  | ×      | ×    | x     | х | x    | х   | X   | Q <sub>A0</sub> | 0 <sub>80</sub> | a <sup>co</sup> | Q <sub>D0</sub> |   |

H = high level (steady state)

L = low level (steady state)

X = irrelevant (any input, incuding tean-sitions)

- t = transition from low to high level a,b,c,d = the level of steady-state input at

input A,B,C,orD,respectively. QAO, QBO, QCO, QDO = the level of QA, QB, QC, or QD,respectively,before the indicated steady-

state input conditions were established.

An. Bn. Cn. Dn = the level of A., B. C. respectively, before the most-recent 1 teansition of the clock.

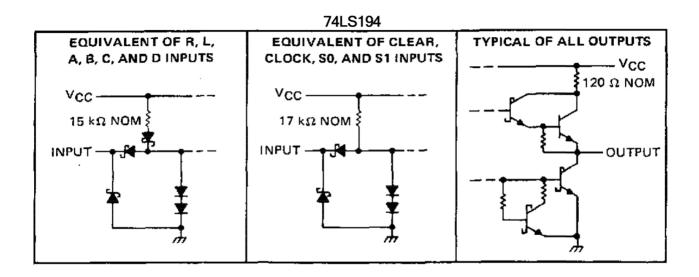

schematics of inputs and outputs

XD74LS194 DIP-16

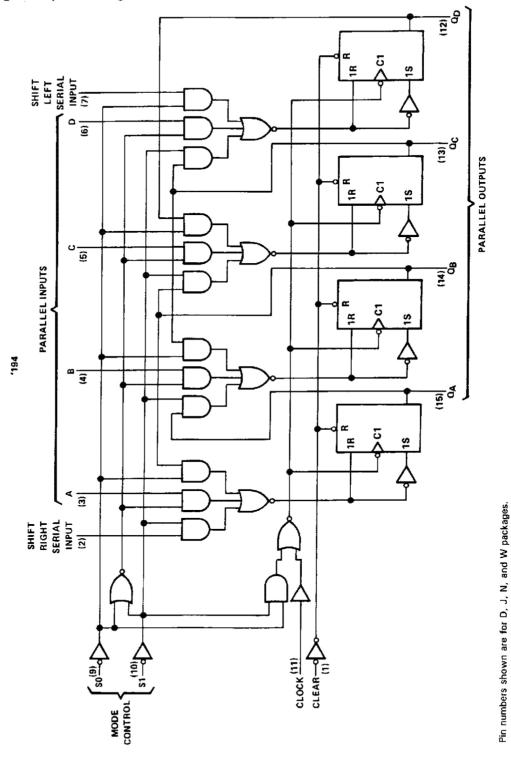

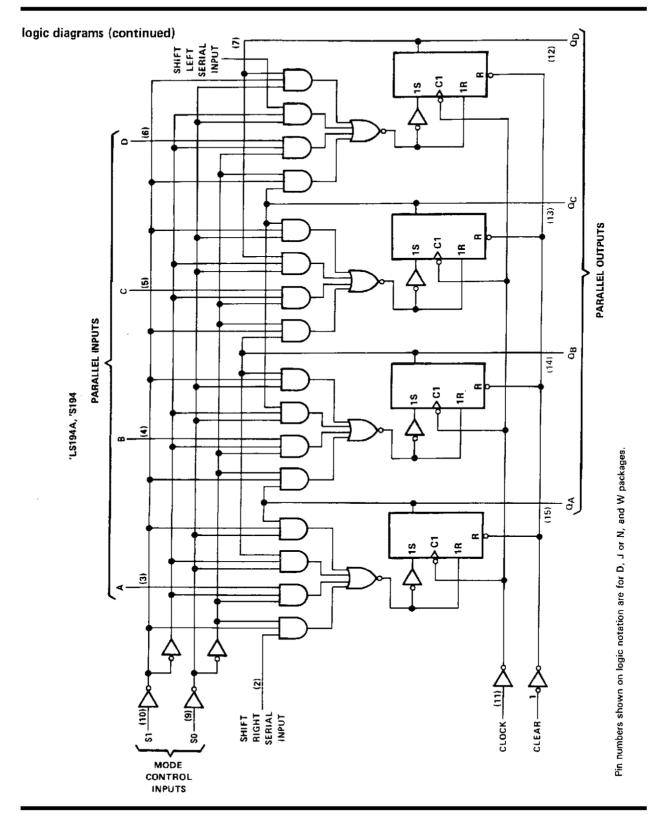

logic diagrams (positive logic)

3

XD74LS194 DIP-16

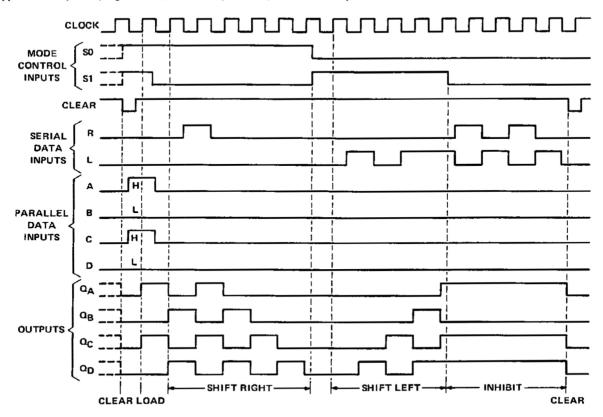

typical clear, load, right-shift, left-shift, inhibit, and clear sequences

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)    |                                       |

|-------------------------------------------------|---------------------------------------|

| Input voltage                                   | 7 V                                   |

| Operating free-air temperature range: XD74LS194 | $\cdot$ · · · · · · · · · 0°C to 70°C |

| Storage temperature range                       | $-65^{\circ}$ C to $150^{\circ}$ C    |

NOTE 1: Voltage values are with respect to network ground terminal.

### recommended operating conditions

|                                        |                          | X    | XD74LS164 |      |      |

|----------------------------------------|--------------------------|------|-----------|------|------|

|                                        |                          | MIN  | NOM       | MAX  | UNIT |

| Supply voltage, VCC                    |                          | 4.75 | 5         | 5.25 | V    |

| High-level output current, IOH         |                          |      |           | -400 | μA   |

| Low-level output current, IOL          |                          |      |           | 8    | mA   |

| Clock frequency, fclock                |                          | 0    |           | 25   | MHz  |

| Width of clock or clear pulse, tw      |                          | 20   |           |      | กร   |

|                                        | Mode control             | 30   |           |      | D5   |

| Setup time, t <sub>su</sub>            | Serial and parallel data | 20   |           |      | ns   |

|                                        | Clear inactive-state     | 25   |           |      | ns   |

| Hold time at any input, <sup>t</sup> h |                          | 0    |           |      | ns   |

| Operating free-air temperature, TA     |                          | 0    |           | 70   | °C   |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER |                                           | TEST CONDITIONS <sup>†</sup>                                    |                      |                        | XD74LS164 |      |      |      |

|-----------|-------------------------------------------|-----------------------------------------------------------------|----------------------|------------------------|-----------|------|------|------|

|           | PARAMETER                                 | TEST CONDITIONS.                                                |                      |                        | MIN       | TYP‡ | MAX  | UNIT |

| VIH       | High-level input voltage                  |                                                                 |                      |                        | 2         |      |      | V    |

| VIL       | Low-level input voltage                   |                                                                 |                      |                        |           |      | 0.8  | l v  |

| VI        | Input clamp voltage                       | V <sub>CC</sub> = MIN,                                          | lı ≈ –18 mA          | 1                      |           |      | -1.5 | - V  |

| ⊻он       | High-level output voltage                 | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = V <sub>IL</sub> max | ••••                 | μA                     | 2.7       | 3.5  |      | v    |

|           | Low-level output voltage                  | V <sub>CC</sub> = MIN,                                          | VIH = 2 V,           | IOL = 4 mA             |           | 0.25 | 0.4  | v    |

| VOL       |                                           | VIL = VIL max                                                   |                      | I <sub>OL</sub> = 8 mA |           | 0.35 | 0.5  | Ň    |

| 4         | Input current at<br>maximum input voltage | V <sub>CC</sub> = MAX,                                          | V <sub>1</sub> = 7 V |                        |           |      | 0.1  | mA   |

| Чн        | High-level input current                  | Vcc = MAX,                                                      | VI = 2.7 V           |                        |           |      | 20   | μA   |

| HL.       | Low-level input current                   | VCC = MAX,                                                      | Vi = 0.4 V           |                        |           |      | -0.4 | ΜA   |

| los       | Short-circuit output current §            | V <sub>CC</sub> = MAX                                           |                      |                        | -20       |      | -100 | mA   |

| lcc       | Supply current                            | VCC = MAX,                                                      | See Note 2           |                        |           | 15   | 23   | mΑ   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. <sup>†</sup>All surface under a set  $f_{1} = 5$  M,  $T_{2} = 25^{2}$ C

<sup>‡</sup>All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

Not more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second.

NOTE 2: With all outputs open, inputs A through D grounded, and 4.5 V applied to S0, S1, clear, and the serial inputs, I<sub>CC</sub> is tested with a momentary GND, then 4.5 V, applied to clock.

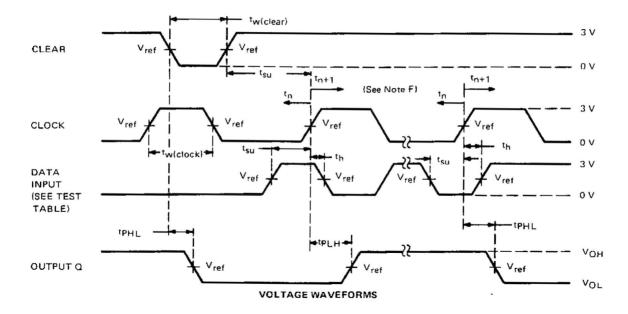

## switching characteristics, $V_{CC} = 5 V$ , $T_A = 25 °C$

|                  | PARAMETER                                                   | TEST CONDITIONS                     | MIN | ТҮР | MAX | UNIT |

|------------------|-------------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| fmax             | Maximum clock frequency                                     | 0 15 -5                             | 25  | 36  |     | MHz  |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level output from clear | $C_{L} = 15 \text{ pF},$            |     | 19  | 30  | ns   |

| <sup>t</sup> PLH | Propagation delay time, low-to-high level output from clock | $R_L = 2 k\Omega$ ,<br>See Figure 1 |     | 14  | 22  | វាន  |

| <b>tPHL</b>      | Propagation delay time, high-to-low level output from clock | See rigure i                        |     | 17  | 26  | ns   |

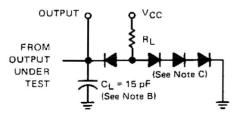

### PARAMETER MEASUREMENT INFORMATION

LOAD FOR OUTPUT UNDER TEST

OUTPUT TESTED DATA INPUT **S1** SO (SEE NOTE E) FOR TEST Δ 4.5 V 4.5 V QA at tn+1 4.5 V 4.5 V QR at tn+1 R Qc at tn+1 С 4.5 V 4.5 V 4.5 V 4.5 V QD at tn+1 п L Serial Input 4.5 V ٥v QA at tn+4 R Serial Input 0V 4.5V QD at tn+4

. TEST TABLE FOR SYNCHRONOUS INPUTS

NOTES: A. The clock pulse generator has the following characteristics: Zout $\approx$ 50  $\Omega$  and PRR $\leq$  1 MHz. For 'XD74LS194. tp $\leq$ 7ns and tp $\leq$ 7 ns. For XD74LS194, < 15ns and tf $\leq$ 6ns. For'XD74LS194. Ip $\leq$ 2.5 ns and tf $\leq$ 2.5 ns. When testing fmax. vary PRR. B. CL includes probe and iig capacitance.

- B. CL includes probe and jig capacita

- C. All diodes are 1N3064 or 1N916. .

- D. A clear pulse is appied prior to each test.

- E. For XD74LS194, Vref= 1.5 V:for XD74LS194. Vref- 1.3 V.

- F. Propagation delay times (tPLH and tPHL are measured at in+1. Proper shiting of data s vernfied at tn+a wit a tunctional tost.

- G. tn = bit time before clocking tr ansition.

- tn+1 = bit time attor ono clock ing transition.

- tn+4 = bit time atter four clocking transitions.

#### FIGURE 1-SWITCHING TIMES

## XD74LS194 DIP-16

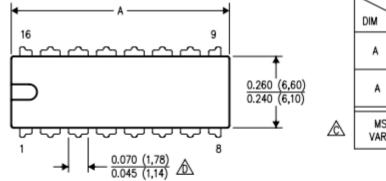

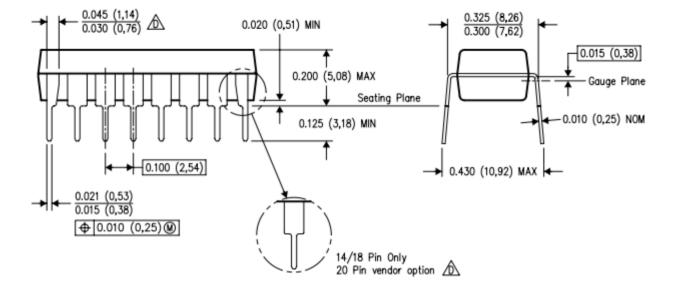

DIP

|   | PINS **<br>DIM      | 14               | 16               | 18               | 20               |

|---|---------------------|------------------|------------------|------------------|------------------|

|   | A MAX               | 0.775<br>(19,69) | 0.775<br>(19,69) | 0.920<br>(23,37) | 1.060<br>(26,92) |

|   | A MIN               | 0.745<br>(18,92) | 0.745<br>(18,92) | 0.850<br>(21,59) | 0.940<br>(23,88) |

| 2 | MS-001<br>VARIATION | AA               | BB               | AC               | AD               |

以上信息仅供参考. 如需帮助联系客服人员。谢谢 XINLUDA

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Counter Shift Registers category:

Click to view products by XINLUDA manufacturer:

Other Similar products are found below :

5962-8956101EA

MC10E446FNG

74HC195N

74HC4516N

74HCT182N

HEF4021BD

HEF4534BP

MC144111P

NLV74HC165ADTR2G

5962-9172201M2A

MC74HC597ADG

MC100EP142MNG

MC100EP016AMNG

5962-9172201MFA

MC74HC164BDR2G

TC74HC165AP(F)

74AHC164T14-13

MC74LV594ADR2G

NLV14094BDTR2G

NLV74HC595ADTG

MC74HC165AMNTWG

TPIC6C595PWG4

74VHC164MTCX

CD74HC195M96

CD4073BM96

CD4053BM96

MM74HC595MTCX

74HCT164T14-13

74HCT164S14-13

74HC4094D-Q100J

NLV14014BFELG

NLV74HC165ADR2G

NLV74HC589ADTR2G

NPIC6C595D-Q100,11

NPIC6C595PW,118

NPIC6C596ADJ

NPIC6C596APW-Q100J

NPIC6C596D-Q100,11

BU4094BCFV-E2

74HC164D14

74HC164T14-13

TPIC6C596PWRG4

STPIC6D595MTR

STP08CP05MTR

CD74HC123E

74HC164D.653

74HC165D.653

74HCT165D.652

74HCT164D.652

STPIC6D595MTR

STP08CP05MTR

CD74HC123E

74HC164D.653

74HC165D.653