# XD754410 DIP16

## 1 Features

- 1-A Output-Current Capability Per Driver

- Applications Include Half-H and Full-H Solenoid Drivers and Motor Drivers

- Designed for Positive-Supply Applications

- Wide Supply-Voltage Range of 4.5 V to 36 V

- TTL- and CMOS-Compatible High-Impedance

Diode-Clamped Inputs

- Separate Input-Logic Supply

- Thermal Shutdown

- Internal ESD Protection

- Input Hysteresis Improves Noise Immunity

- 3-State Outputs

- Minimized Power Dissipation

- Sink/Source Interlock Circuitry Prevents Simultaneous Conduction

- No Output Glitch During Power Up or Power Down

## 2 Applications

- Stepper Motor Drivers

- DC Motor Drivers

- Latching Relay Drivers

## 3 Description

The XD754410 is a quadruple high-current half-H driver designed to provide bidirectional drive currents up to 1 A at voltages from 4.5 V to 36 V. The device is designed to drive inductive loads such as relays, solenoids, DC and bipolar stepping motors, as well as other high-current/high-voltage loads in positive-supply applications.

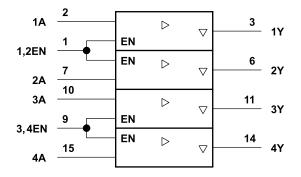

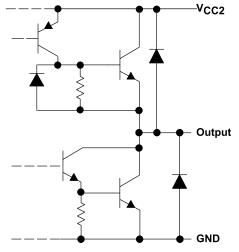

All inputs are compatible with TTL-and low-level CMOS logic. Each output (Y) is a complete totempole driver with a Darlington transistor sink and a pseudo-Darlington source. Drivers are enabled in pairs with drivers 1 and 2 enabled by 1,2EN and drivers 3 and 4 enabled by 3,4EN. When an enable input is high, the associated drivers are enabled and their outputs become active and in phase with their inputs. When the enable input is low, those drivers are disabled and their outputs are off and in a high-impedance state. With the proper data inputs, each pair of drivers form a full-H (or bridge) reversible drive suitable for solenoid or motor applications.

A separate supply voltage ( $V_{CC1}$ ) is provided for the logic input circuits to minimize device power dissipation. Supply voltage  $V_{CC2}$  is used for the output circuits.

The XD754410 is designed for operation from  $-40^{\circ}$ C to 85°C.

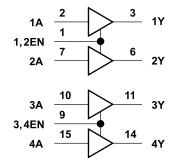

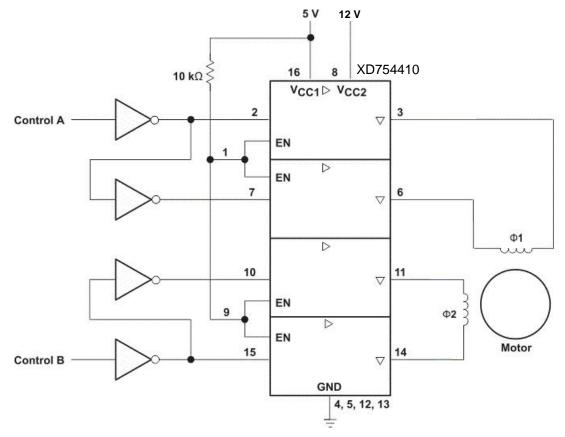

#### **4** Simplified Schematic

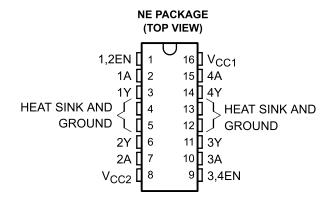

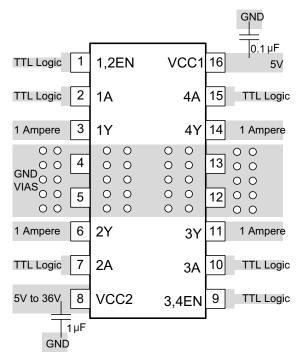

## 5 Pin Configuration and Functions

#### 6 Pin Functions

| PIN              |              | TYPE | DESCRIPTION                                                                                     |  |  |

|------------------|--------------|------|-------------------------------------------------------------------------------------------------|--|--|

| NAME             | NO.          | TIPE | DESCRIPTION                                                                                     |  |  |

| 1,2EN            | 1            | Ι    | Enable driver channels 1 and 2 (active high input)                                              |  |  |

| <1:4>A           | 2, 7, 10, 15 | Ι    | Driver inputs, non-inverting                                                                    |  |  |

| <1:4>Y           | 3, 6, 11, 14 | 0    | Driver outputs                                                                                  |  |  |

| GROUND           | 4, 5, 12, 13 | _    | Device ground and heat sink pin. Connect to circuit board ground plane with multiple solid vias |  |  |

| V <sub>CC2</sub> | 8            | —    | Power VCC for drivers 4.5V to 36V                                                               |  |  |

| 3,4EN            | 9            | I    | Enable driver channels 3 and 4 (active high input)                                              |  |  |

| V <sub>CC1</sub> | 16           | _    | 5V supply for internal logic translation                                                        |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                  |                                                                                           | MIN  | MAX                  | UNIT |

|------------------|-------------------------------------------------------------------------------------------|------|----------------------|------|

| V <sub>CC1</sub> | Output supply voltage range                                                               | -0.5 | 36                   | V    |

| V <sub>CC2</sub> | Output supply voltage range                                                               | -0.5 | 36                   | V    |

| VI               | Input voltage                                                                             | -0.5 | 36                   | V    |

| Vo               | Output voltage range                                                                      | -3   | V <sub>CC2</sub> + 3 | V    |

| I <sub>P</sub>   | Peak output current                                                                       |      | ±2                   | А    |

| I <sub>O</sub>   | Continuous output current                                                                 |      | ±1                   | А    |

| PD               | Continuous total power dissipation at (or below) 25°C free-air temperature <sup>(3)</sup> |      | 2075                 | mW   |

| T <sub>A</sub>   | Operating free-air temperature range                                                      | -40  | 85                   | °C   |

| TJ               | Operating virtual junction temperature range                                              | -40  | 150                  | °C   |

| T <sub>stg</sub> | Storage temperature range                                                                 |      | 260                  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network GND.

(3) For operation above 25°C free-air temperature, derate linearly at the rate of 16.6 mW/°C. To avoid exceeding the design maximum virtual junction temperature, these ratings should not be exceeded. Due to variations in individual device electrical characteristics and thermal resistance, the built-in thermal overload protection can be activated at power levels slightly above or below the rated dissipation.

## 7.2 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                        | MIN                 | MAX | UNIT |

|------------------|----------------------------------------|---------------------|-----|------|

| V <sub>CC1</sub> | Logic supply voltage                   | 4.5                 | 5.5 | V    |

| V <sub>CC2</sub> | Output supply voltage                  | 4.5                 | 36  | V    |

| V <sub>IH</sub>  | High-level input voltage               | 2                   | 5.5 | V    |

| V <sub>IL</sub>  | Low-level input voltage                | -0.3 <sup>(1)</sup> | 0.8 | V    |

| TJ               | Operating virtual junction temperature | -40                 | 125 | °C   |

| T <sub>A</sub>   | Operating free-air temperature         | -40                 | 85  | °C   |

(1) The algebraic convention, in which the least positive (most negative) limit is designated as minimum, is used in this data sheet for logic voltage levels.

#### 7.3 Thermal Information

|                                                         | XD754410 |      |  |

|---------------------------------------------------------|----------|------|--|

| THERMAL METRIC <sup>(1)</sup>                           | NE       | UNIT |  |

|                                                         | 16 PINS  |      |  |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance | 60       | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 7.4 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                         | TE                      | EST CONDITIONS                | MIN                    | TYP                    | MAX                    | UNIT |  |

|----------------------|-----------------------------------|-------------------------|-------------------------------|------------------------|------------------------|------------------------|------|--|

| V <sub>IK</sub>      | Input clamp voltage               | I <sub>I</sub> = -12 m. | A                             |                        | -0.9                   | -1.5                   | V    |  |

|                      |                                   | I <sub>OH</sub> = -0.5  | A                             | V <sub>CC2</sub> – 1.5 | V <sub>CC2</sub> – 1.1 |                        | V    |  |

| V <sub>OH</sub>      | High-level output voltage         | I <sub>OH</sub> = -1 A  | l l                           | V <sub>CC2</sub> – 2   |                        |                        |      |  |

|                      |                                   | I <sub>OH</sub> = -1 A  | λ, Τ <sub>J</sub> = 25°C      | V <sub>CC2</sub> – 1.8 | V <sub>CC2</sub> – 1.4 |                        |      |  |

|                      |                                   | $I_{OL} = 0.5 A$        | A                             |                        | 1                      | 1.4                    |      |  |

| V <sub>OL</sub>      | Low-level output voltage          | I <sub>OL</sub> = 1 A   |                               |                        |                        | 2                      | V    |  |

|                      |                                   | I <sub>OL</sub> = 1 A,  | T <sub>J</sub> = 25°C         |                        | 1.2                    | 1.8                    |      |  |

|                      |                                   | I <sub>OK</sub> = -0.5  | A                             |                        | V <sub>CC2</sub> + 1.4 | V <sub>CC2</sub> + 2   | V    |  |

| V <sub>ОКН</sub>     | High-level output clamp voltage   | I <sub>OK</sub> = 1 A   |                               |                        | V <sub>CC2</sub> + 1.9 | V <sub>CC2</sub> + 2.5 | V    |  |

|                      |                                   | I <sub>OK</sub> = 0.5 A |                               |                        | -1.1                   | -2                     | V    |  |

| V <sub>OKL</sub>     | KL Low-level output clamp voltage |                         | I <sub>OK</sub> = -1 A        |                        | -1.3                   | -2.5                   | V    |  |

|                      | Off-state high-impedance-state    | $V_{O} = V_{CC2}$       |                               |                        |                        | 500                    |      |  |

| I <sub>OZ(off)</sub> | output current                    | $V_{O} = 0$             | V <sub>O</sub> = 0            |                        | -500                   |                        | μA   |  |

| I <sub>IH</sub>      | High-level input current          | V <sub>I</sub> = 5.5 V  |                               |                        |                        | 10                     | μA   |  |

| I <sub>IL</sub>      | Low-level input current           | $V_{I} = 0$             |                               |                        |                        | -10                    | μA   |  |

|                      | Output supply current             |                         | All outputs at high level     |                        |                        | 38                     |      |  |

| I <sub>CC1</sub>     |                                   | I <sub>O</sub> = 0      | All outputs at low level      |                        | -                      |                        | mA   |  |

| 1001                 |                                   | 10 - 0                  | all outputs at high impedance |                        | 25                     |                        |      |  |

| I <sub>CC2</sub>     | Output supply current             |                         | All outputs at high level     |                        |                        | 33                     |      |  |

|                      |                                   | I <sub>O</sub> = 0      | All outputs at low level      | 20                     |                        | 20                     | nA   |  |

|                      |                                   | 10 - 0                  | All outputs at high impedance |                        |                        | 5                      | ΠA   |  |

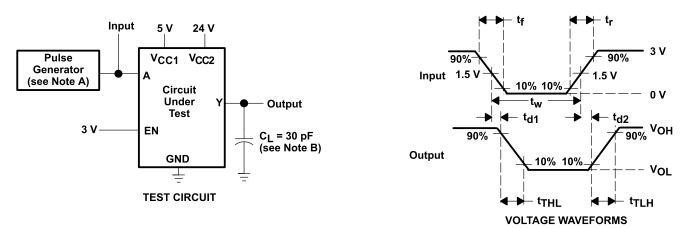

## 7.5 Switching Characteristics

over operating free-air temperature range (unless otherwise noted),  $V_{CC1} = 5 V$ ,  $V_{CC2} = 24 V$ ,  $C_L = 30 pF$ ,  $T_A = 25^{\circ}C$

|                   | PARAMETER                                            | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------|------------------------------------------------------|-----------------|-----|-----|-----|------|

| t <sub>d1</sub>   | Delay time, high-to-low-level output<br>from A input |                 |     | 400 |     | ns   |

| t <sub>d2</sub>   | Delay time, low-to-high-level output from A input    |                 | 800 |     |     | ns   |

| t <sub>TLH</sub>  | Transition time, low-to-high-level output            | See Figure 3    | 300 |     |     | ns   |

| t <sub>THL</sub>  | Transition time, high-to-low-level output            |                 |     | 300 |     | ns   |

| t <sub>en1</sub>  | Enable time to the high level                        |                 |     | 700 |     | ns   |

| t <sub>en2</sub>  | Enable time to the low level                         | See Figure 4    |     | 400 |     | ns   |

| t <sub>dis1</sub> | Disable time from the high level                     | See Figure 4    |     | 900 |     | ns   |

| t <sub>dis2</sub> | Disable time from the low level                      |                 |     | 600 |     | ns   |

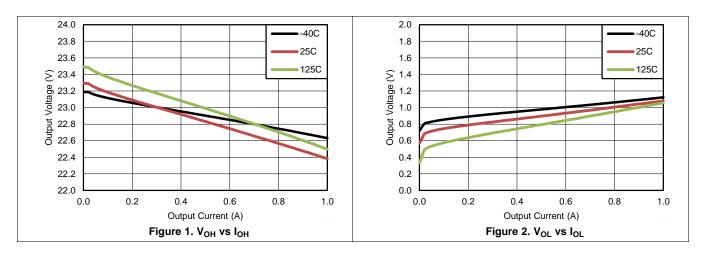

## 7.6 Typical Characteristics

$V_{CC1} = 5 \text{ V}, V_{CC2} = 24 \text{ V}$

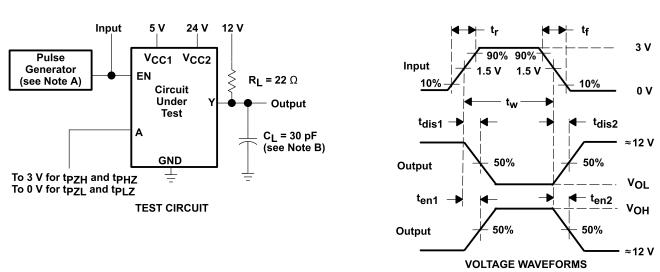

## 8 Parameter Measurement Information

- A. The pulse generator has the following characteristics:  $t_r \le 10$  ns,  $t_f \le 10$  ns,  $t_w = 10 \mu$ s,  $P_{RR} = 5$  kHz,  $Z_O = 50 \Omega$

- B. C<sub>L</sub> includes probe and jig capacitance.

#### Figure 3. Test Circuit and Switching Times from Data Inputs

- A. The pulse generator has the following characteristics:  $t_r \le 10$  ns,  $t_f \le 10$  ns,  $t_w = 10$  µs,  $P_{RR} = 5$  kHz,  $Z_O = 50$   $\Omega$

- B.  $C_L$  includes probe and jig capacitance.

## Figure 4. Test Circuit and Switching Times from Enable Inputs

## 9 Detailed Description

#### 9.1 Overview

The XD754410 is a quadruple high-current half-H driver designed to provide bidirectional drive currents up to 1 A at voltages from 4.5 V to 36 V. The device is designed to drive inductive loads such as relays, solenoids, DC and bipolar stepping motors, as well as other high-current/high-voltage loads in positive-supply applications. All inputs are compatible with TTL and low-level CMOS logic. Each output (Y) is a complete totem-pole driver with a Darlington transistor sink and a pseudo-Darlington source. Drivers are enabled in pairs with drivers 1 and 2 enabled by 1,2EN and drivers 3 and 4 enabled by 3,4EN. When an enable input is high, the associated drivers are enabled and their outputs become active and in phase with their inputs. When the enable input is low, those drivers are disabled and their outputs are off and in a high-impedance state. With the proper data inputs, each pair of drivers form a full-H (or bridge) reversible drive suitable for solenoid or motor applications.

A separate supply voltage ( $V_{CC1}$ ) is provided for the logic input circuits to minimize device power dissipation. Supply voltage  $V_{CC2}$  is used for the output circuits. The XD754410 is designed for operation from -40°C to 85°C.

#### 9.2 Functional Block Diagram

#### 9.3 Feature Description

#### 9.3.1 High Current, High Voltage Outputs

Four high current and high voltage outputs feature clamp diodes for inductive load driving.

Figure 5. Typical of All Outputs

#### **Feature Description (continued)**

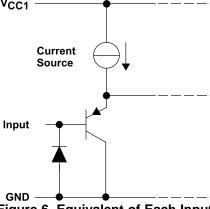

#### 9.3.2 TTL Compatible Inputs

Data inputs and enable inputs are compatible with TTL. 3.3-V CMOS logic is also acceptable, however open or high impedance input voltage can approach  $V_{CC1}$  voltage. VCC1

Figure 6. Equivalent of Each Input

#### 9.4 Device Functional Modes

| INPU | TS <sup>(2)</sup> | OUTPUTS |  |  |

|------|-------------------|---------|--|--|

| Α    | EN                | Y       |  |  |

| Н    | Н                 | Н       |  |  |

| L    | Н                 | L       |  |  |

| Х    | L                 | Z       |  |  |

(1) H = high-level

L = low-level

X = irrelevant

Z = high-impedance (off)

(2) In the thermal shutdown mode, the output is in a high-impedance state regardless of the input levels.

## **10** Application and Implementation

### **10.1** Application Information

Provide a 5-V supply to  $V_{CC1}$  and valid logic input levels to data and enable inputs.  $V_{CC2}$  must be connected to a power supply capable of suppling the needed current and voltage demand for the loads connected to the outputs.

#### **10.2 Typical Application**

Figure 7. Typical Application Schematic

#### 10.2.1 Design Requirements

The design techniques in the following sections may be used for applications which fall within the following requirements.

- 4.5-V minimum and 36-V maximum V<sub>CC2</sub> voltage

- 1000-mA or less output current per channel

- 5-V supply with 10% tolerance or less

- TTL compatible logic inputs

## **Typical Application (continued)**

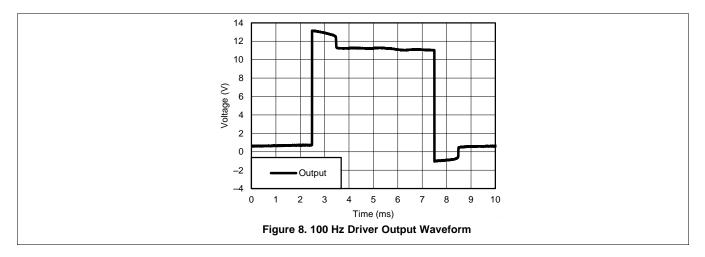

## 10.2.2 Application Curves

Driver output voltage waveform with a two phase stepper motor; 12-V 20- $\Omega$  coils.

## **11 Power Supply Recommendations**

$V_{CC1}$  is 5 V ± 0.5 V and  $V_{CC2}$  can be same supply as  $V_{CC1}$  or a higher voltage supply with peak voltage up to 36 V. Bypass capacitors of 0.1 uF or greater should be used at  $V_{CC1}$  and  $V_{CC2}$  pins. There are no power up or power down supply sequence order requirements.

## 12.2 Layout Example

Figure 9. Layout Diagram

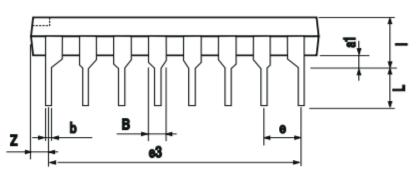

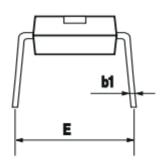

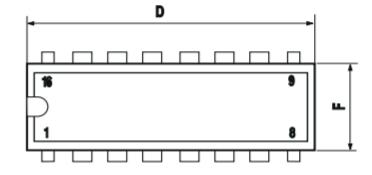

## XD754410 DIP16

| DIM. | mm   |       |      | inch  |       |       |  |

|------|------|-------|------|-------|-------|-------|--|

|      | MIN. | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |  |

| a1   | 0.51 |       |      | 0.020 |       |       |  |

| в    | 0.85 |       | 1.40 | 0.033 |       | 0.055 |  |

| b    |      | 0.50  |      |       | 0.020 |       |  |

| b1   | 0.38 |       | 0.50 | 0.015 |       | 0.020 |  |

| D    |      |       | 20.0 |       |       | 0.787 |  |

| Е    |      | 8.80  |      |       | 0.346 |       |  |

| е    |      | 2.54  |      |       | 0.100 |       |  |

| e3   |      | 17.78 |      |       | 0.700 |       |  |

| F    |      |       | 7.10 |       |       | 0.280 |  |

| I.   |      |       | 5.10 |       |       | 0.201 |  |

| L    |      | 3.30  |      |       | 0.130 |       |  |

| Z    |      |       | 1.27 |       |       | 0.050 |  |

以上信息仅供参考.如需帮助联系客服人员。谢谢 XINLUDA

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Motor/Motion/Ignition Controllers & Drivers category:

Click to view products by XINLUDA manufacturer:

Other Similar products are found below :

LV8133JA-ZH LV8169MUTBG LV8774Q-AH LV8860PV-TLM-H MC33931EKR2 FSB50250UTD FSB50550TB2 FSBF15CH60BTH FSBS10CH60T MP6507GR-P MP6508GF MSVCPM2-63-12 MSVGW45-14-2 MSVGW54-14-5 NTE7043 CAT3211MUTAG LA6245P-CL-TLM-E LA6245P-TLM-E LA6565VR-TLM-E LB11650-E LB1694N-E LB1837M-TLM-E LB1845DAZ-XE LC898111AXB-MH LC898300XA-MH SS30-TE-L-E STK531-345A-E STK581U3A0D-E STK58AUNP0D-E STK621-068C-E STK621-140C STK621-728S-E STK625-728-E STK672-400B-E STK672-432AN-E STK672-432BN-E STK672-440AN-E STK672-442AN-E AMIS30621AUA FSB50550ASE 26700 LV8161MUTAG LV8281VR-TLM-H LV8702V-TLM-H LV8734VZ-TLM-H LV8773Z-E LV8807QA-MH MC33932EK MCP8024T-H/MP TND027MP-AZ