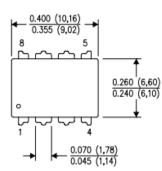

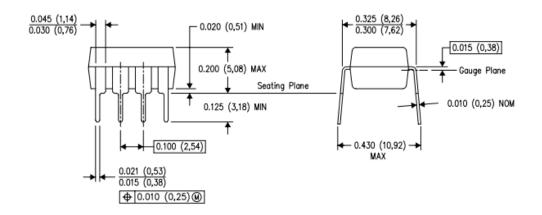

## XD1881 DIP-8 XL1881 SOP-8

### FEATURES

- AC Coupled Composite Input Signal

- >10 kΩ Input Resistance

- <10 mA Power Supply Drain Current

- Composite Sync and Vertical Outputs

- Odd/Even Field Output

- Burst Gate/Back Porch Output

- Horizontal Scan Rates to 150 kHz

- Edge Triggered Vertical Output

- Default Triggered Vertical Output for Nonstandard Video Signal (Video Games-Home Computers)

### DESCRIPTION

The 1881 Video sync separator extracts timing information including composite and vertical sync, burst/back porch timing, and odd/even field information from standard negative going sync NTSC, PAL <sup>(1)</sup> and SECAM video signals with amplitude from 0.5V to 2V p-p. The integrated circuit is also capable of providing sync separation for non-standard, faster horizontal rate video signals. The vertical output is produced on the rising edge of the first serration in the vertical sync period. A default vertical output is produced after a time delay if the rising edge mentioned above does not occur within the externally set delay period, such as might be the case for a non-standard video signal.

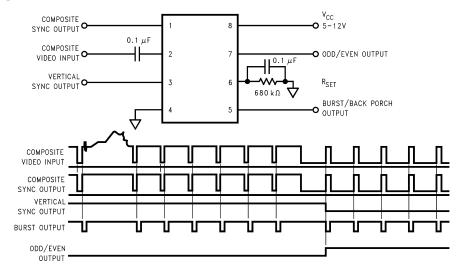

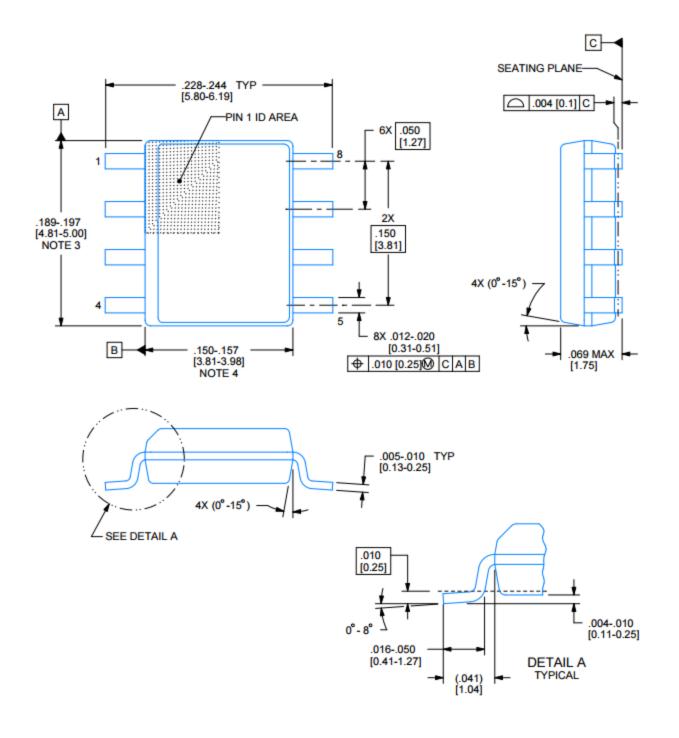

### **Connection Diagram**

### Absolute Maximum Ratings (1)(2)

| Supply Voltage                     |                                                                                        |                       | 13.2V           |  |  |

|------------------------------------|----------------------------------------------------------------------------------------|-----------------------|-----------------|--|--|

| Input Voltage                      | 3 V <sub>P-P</sub> (V <sub>CC</sub> = 5V)<br>6 V <sub>P-P</sub> (V <sub>CC</sub> ≥ 8V) |                       |                 |  |  |

| Output Sink Currents; Pi           | ns, 1, 3, 5                                                                            |                       | 5 mA            |  |  |

| Output Sink Current; Pin 7         |                                                                                        |                       | 2 mA            |  |  |

| Package Dissipation <sup>(3)</sup> |                                                                                        |                       | 1100 mW         |  |  |

| Storage Temperature Range          |                                                                                        |                       | −65°C to +150°C |  |  |

| ESD Susceptibility <sup>(4)</sup>  |                                                                                        |                       | 2 kV            |  |  |

| ESD Susceptibility <sup>(5)</sup>  |                                                                                        |                       | 200 V           |  |  |

| Soldering Information              | PDIP Package (10 sec.)                                                                 |                       | 260°C           |  |  |

|                                    | SOIC Package                                                                           | Vapor Phase (60 sec.) | 215°C           |  |  |

|                                    |                                                                                        | Infrared (15 sec.)    | 220°C           |  |  |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed.

(2) For operation in ambient temperatures above 25°C, the device must be derated based on a 150°C maximum junction temperature and a package thermal resistance of 110°C/W, junction to ambient.

(3) ESD susceptibility test uses the "human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor".

(4) Machine Model, 220 pF – 240 pF discharged through all pins.

### **Electrical Characteristics 1881**

| $V_{CC} = 5V$ : $R_{SET} = 680 \text{ kG}$ | $T_{A} = 0^{\circ}C$ to +70°C k | ov correlation with 100% | % electrical testing at T <sub>A</sub> =25 | °C |

|--------------------------------------------|---------------------------------|--------------------------|--------------------------------------------|----|

|                                            |                                 |                          |                                            |    |

| Parameter                              |                                            | Conditions                      | Min         | Тур <sup>(1)</sup> | Max      | Units |

|----------------------------------------|--------------------------------------------|---------------------------------|-------------|--------------------|----------|-------|

| Supply Current                         | Outputs at<br>Logic 1                      | $V_{CC} = 5V$<br>$V_{CC} = 12V$ |             | 5.2<br>5.5         | 10<br>12 | mA    |

| DC Input Voltage                       | Pin 2                                      |                                 | 1.3         | 1.5                | 1.8      | V     |

| Input Threshold Voltage                | (2)                                        |                                 | 55          | 70                 | 85       | mV    |

| Input Discharge Current                | Pin 2; V <sub>IN</sub> = 2V                |                                 | 6           | 11                 | 16       | μA    |

| Input Clamp Charge Current             | Pin 2; V <sub>IN</sub> = 1V                |                                 | 0.2         | 0.8                |          | mA    |

| R <sub>SET</sub> Pin Reference Voltage | Pin 6; <sup>(3)</sup>                      |                                 | 1.10        | 1.22               | 1.35     | V     |

| Composite Sync. & Vertical<br>Outputs  | I <sub>OUT</sub> = 40 μA;<br>Logic 1       | $V_{CC} = 5V$<br>$V_{CC} = 12V$ | 4.0<br>11.0 | 4.5                |          | V     |

|                                        | I <sub>OUT</sub> = 1.6 mA<br>Logic 1       | $V_{CC} = 5V$<br>$V_{CC} = 12V$ | 2.4<br>10.0 | 3.6                |          | V     |

| Burst Gate & Odd/Even Outputs          | I <sub>OUT</sub> = 40 μA;<br>Logic 1       | $V_{CC} = 5V$<br>$V_{CC} = 12V$ | 4.0<br>11.0 | 4.5                |          | V     |

| Composite Sync. Output                 | I <sub>OUT</sub> = −1.6 mA; Logic 0; Pin 1 |                                 |             | 0.2                | 0.8      | V     |

| Vertical Sync. Output                  | I <sub>OUT</sub> = −1.6 mA; Logic 0; Pin 3 |                                 |             | 0.2                | 0.8      | V     |

| Burst Gate Output                      | I <sub>OUT</sub> = −1.6 mA; Logic 0; Pin 5 |                                 |             | 0.2                | 0.8      | V     |

| Odd/Even Output                        | I <sub>OUT</sub> = −1.6 mA; Logic 0; Pin 7 |                                 |             | 0.2                | 0.8      | V     |

| Vertical Sync Width                    |                                            |                                 | 190         | 230                | 300      | μs    |

| Burst Gate Width                       | 2.7 k $\Omega$ from Pin 5 to $V_{CC}$      |                                 | 2.5         | 4                  | 4.7      | μs    |

| Vertical Default Time                  | (4)                                        |                                 | 32          | 65                 | 90       | μs    |

(1) Typicals are at  $T_J = 25^{\circ}C$  and represent the most likely parametric norm.

(2) Relative difference between the input clamp voltage and the minimum input voltage which produces a horizontal output pulse.

(3) Careful attention should be made to prevent parasitic capacitance coupling from any output pin (Pins 1, 3, 5 and 7) to the R<sub>SET</sub> pin (Pin 6).

(4) Delay time between the start of vertical sync (at input) and the vertical output pulse.

100

500

12

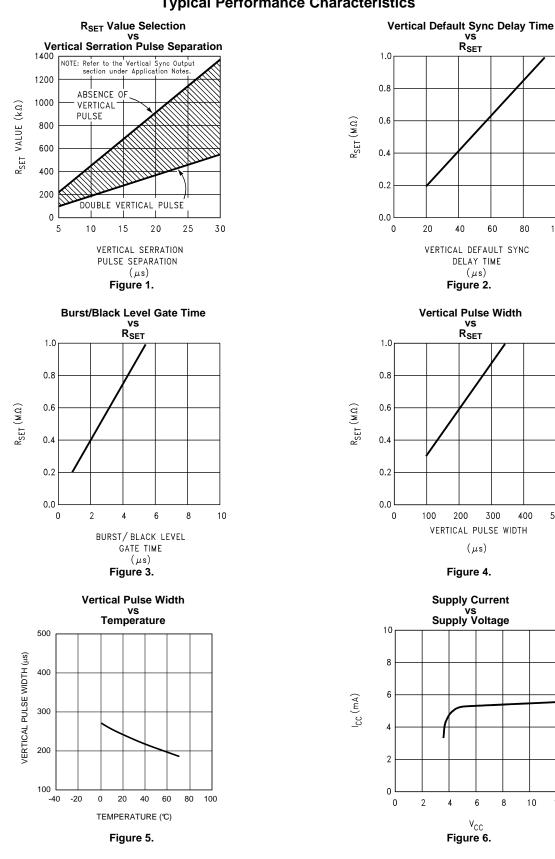

### **Typical Performance Characteristics**

## XD1881 DIP-8 XL1881 SOP-8

Instead of using the vertical serration pulse separation, use the actual pulse width of the vertical sync period, or 64 µs in this example. This graph is linear, meaning that a value as large as 2.7 M $\Omega$  can be used for R<sub>SET</sub> (twice the value as the maximum at 30 µs). Due to leakage currents it is advisable to keep the value of R<sub>SET</sub> under 2.0 M $\Omega$ . In this example a value of 1.0 M $\Omega$  is selected, well above the minimum of 680 k $\Omega$ . With this value for R<sub>SET</sub> the pulse width of the vertical sync output pulse of the 1881 is about 340 µs.

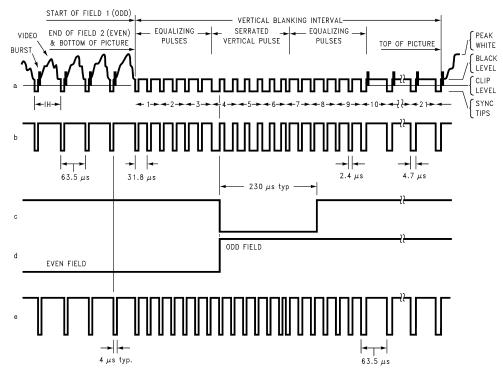

Figure 7. (a) Composite Video; (b) Composite Sync; (c) Vertical Output Pulse; (d) Odd/Even Field Index; (e) Burst Gate/Back Porch Clamp

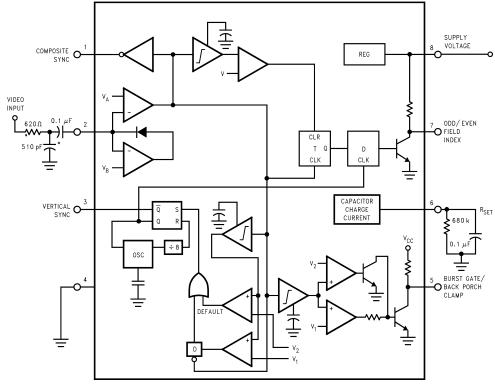

# XD1881 DIP-8 XL1881 SOP-8

\*Components Optional, See Text

Figure 8.

### **ODD/EVEN FIELD PULSE**

An unusual feature of 1881 is an output level from Pin 7 that identifies the video field present at the input to the 1881. This can be useful in frame memory storage applications or in extracting test signals that occur in alternate fields. For a composite video signal that is interlaced, one of the two fields that make up each video frame or picture must have a half horizontal scan line period at the end of the vertical scan—i.e., at the bottom of the picture. This is called the "odd field" or "even field". The "even field" or "field 2" has a complete horizontal scan line at the end of the field. An odd field starts on the leading edge of the first equalizing pulse, whereas the even field starts on the leading edge of the second equalizing pulse of the vertical retrace interval. Figure 8(a) shows the end of the even field and the start of the odd field.

To detect the odd/even fields the 1881 again integrates the composite sync waveform (Figure 8). A capacitor is charged during the period between sync pulses and discharged when the sync pulse is present. The period between normal horizontal sync pulses is enough to allow the capacitor voltage to reach a threshold level of a comparator that clears a flip-flop which is also being clocked by the sync waveform. When the vertical interval is reached, the shorter integration time between equalizing pulses prevents this threshold from being reached and the Q output of the flip-flop is toggled with each equalizing pulse. Since the half line period at the end of the odd field will have the same effect as an equalizing pulse period, the Q output will have a different polarity on successive fields. Thus by comparing the Q polarity with the vertical output pulse, an odd/even field index is generated. Pin 7 remains low during the even field and high during the odd field.

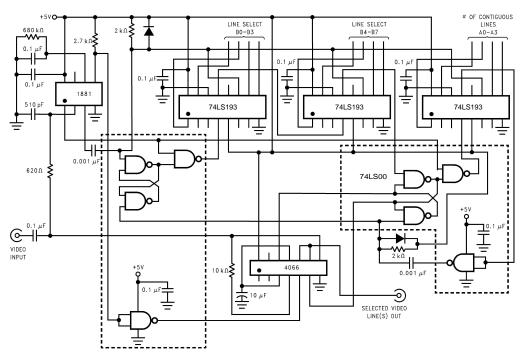

#### MULTIPLE CONTIGUOUS VIDEO LINE SELECTOR WITH BLACK LEVEL RESTORATION

The circuit in Figure 10 will select a number of adjoining lines starting with the line selected as in the previous example. Additional counters can be added as described previously for either higher starting line numbers or an increased number of contiguous output lines. The back porch pulse output of the 1881 is used to gate the video input's black level through a low pass filter (10 k $\Omega$ , 10  $\mu$ F) providing black level restoration at the video output when the output selected line(s) is not being gated through.

### **Typical Applications**

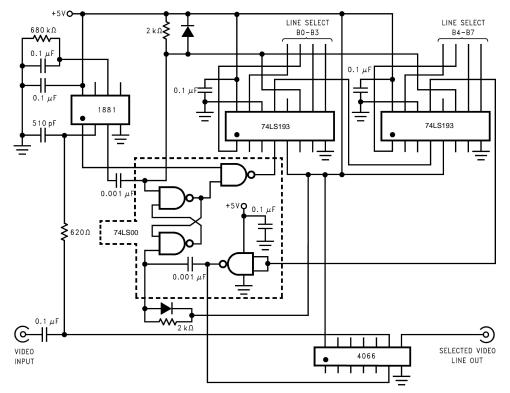

Figure 9. Video Line Selector

Figure 10. Multiple Contiguous Video Line Selector with Black Level Restoration

以上信息仅供参考.如需帮助联系客服人员。谢谢 XINLUDA

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Audio DSPs category:

Click to view products by XINLUDA manufacturer:

Other Similar products are found below :

E-TDA7377A TDA7716N BR281W31A101V1G LC823425-12G1-LR-H TDA7419N R3910-CFAB-E1B HMC474MP86ETR AMIS30660CANH6G B300W35A102XYG MAX9892ERT+T MAX9892ELTT SB3229-E1 NJW1157BFC2 ZL38060LDG1 SB3231-E1 HMC1022-SX SA3229-E1-T LC75056PE-H TDA7729 NJW1195AV WM5102ECS/R CI1103 WM5102ECS/R 100-CG1820 CS48L10-CNZ CS48L10-CNZR CS47024C-CQZ CS48L10-CWZR CS48L11-CNZ HMC618LP3ETR HMC604LP3ETR HMC5622LS7TR HMC288MS8ETR HMC240A STA323W13TR BU9408KS2 DSPB56725AF TAS3204PAGR ADAU1467WBCPZ300 ADAU1463WBCPZ300 BD37514FS-E2 ADAU1463WBCPZ150 NJM2294V-TE1 LC823450TA-2H NJM2537V-TE1 TWL1103TPBSQ1 LC823450XDTBG HMC-AUH312-SX ADAV4622BSTZ ADXL372BCCZ-RL7