# XD3846 DIP-16 XL3846 SOP-16

# **1** Features

- Automatic Feedforward Compensation

- Programmable Pulse-by-Pulse Current Limiting

- Automatic Symmetry Correction in Push-Pull Configuration

- Enhanced Load Response Characteristics

- Parallel Operation Capability for Modular Power Systems

- Differential Current Sense Amplifier with Wide Common Mode Range

- Double-Pulse Suppression

- 500-mA (Peak) Totem-pole Outputs

- ±1% Band Gap Reference

- Undervoltage Lockout

- Soft-Start Capability

- Shutdown Terminal

- 500-kHz Operation

# 2 Applications

- Telecommunication Power Converters

- Industrial Power Converters

# **3** Description

The 1846/7 family of control devices provides all of the necessary features to implement fixedfrequency, current-mode control schemes while maintaining a minimum external parts count. The superior performance of this technique can be measured in improved line regulation, enhanced load response characteristics, and a simpler, easier-todesign control loop. Topological advantages include inherent pulse-by-pulse current limiting capability, automatic symmetry correction for push-pull converters, and the ability to parallel *power modules* while maintaining equal current sharing.

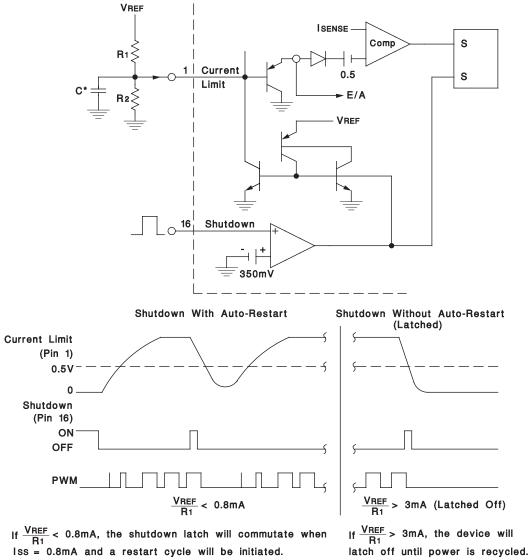

Protection circuitry includes built-in undervoltage lockout and programmable current limit, in addition to soft-start capability. A shutdown function is also available, which can initiate either a complete shutdown with automatic restart or latch the supply off.

Other features include fully-latched operation, doublepulse suppression, deadline adjust capability, and a  $\pm 1\%$  trimmed band gap reference.

The 1846 features low outputs in the OFF state, while the 3846 features high outputs in the OFF state.

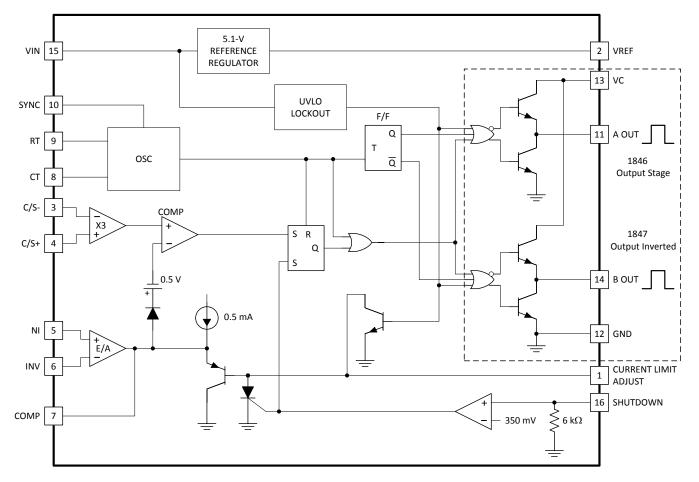

**4** Block Diagram

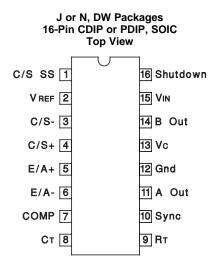

# 5 Pin Configuration and Functions

### **Pin Functions**

| PIN           |                  |                 |     |                                                                         |  |

|---------------|------------------|-----------------|-----|-------------------------------------------------------------------------|--|

| DIL, SOIC NO. | PLCC, LCC<br>NO. | NAME            | I/O | DESCRIPTION                                                             |  |

| 1             | 2                | C/S SS          | Ι   | Current limit/soft-start programming                                    |  |

| 2             | 3                | $V_{REF}$       | 0   | 5.1-V reference voltage output                                          |  |

| 3             | 4                | C/S –           | Ι   | Current sense comparator inverting input                                |  |

| 4             | 5                | C/S +           | Ι   | Current sense comparator non-inverting input                            |  |

| 5             | 7                | E/A +           | Ι   | Error amplifier inverting input                                         |  |

| 6             | 8                | E/A –           | Ι   | Error amplifier inverting input                                         |  |

| 7             | 9                | COMP            | I/O | Error amplifier output and input to the PWM comparator                  |  |

| 8             | 10               | CT              | Ι   | Oscillator frequency programming capacitor pin                          |  |

| 9             | 12               | C <sub>R</sub>  | Ι   | Oscillator frequency programming resistor pin                           |  |

| 10            | 13               | Sync            | I/O | Synchronization out from master controller or input of slave controller |  |

| 11            | 14               | A Out           | 0   | PWM drive signal output A, Pin11 and P14 are complementary              |  |

| 12            | 15               | GND             | G   | All signals are referenced to this node                                 |  |

| 13            | 17               | V <sub>C</sub>  | Ι   | Bias supply input for output stage                                      |  |

| 14            | 18               | B Out           | 0   | PWM drive signal output B, Pin11 and P14 are complementary              |  |

| 15            | 19               | V <sub>IN</sub> | Ι   | Bias supply input                                                       |  |

| 16            | 20               | Shutdown        | Ι   | External shutdown signal input                                          |  |

| _             | 1, 6, 11, 16     | N/C             |     |                                                                         |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                              | MIN  | MAX              | UNIT |

|----------------------------------------------|------|------------------|------|

| Supply Voltage (Pin 15)                      |      | 40               | V    |

| Collector Supply Voltage (Pin 13)            |      | 40               | V    |

| Output Current, Source or Sink (Pins 11, 14) |      | 500              | mA   |

| Analog Inputs (Pins 3, 4, 5, 6, 16)          | -0.3 | +V <sub>IN</sub> | V    |

| Reference Output Current (Pin 2)             |      | -30              | mA   |

| Sync Output Current (Pin 10)                 |      | -5               | mA   |

| Error Amplifier Output Current (Pin 7)       |      | -5               | mA   |

| Soft Start Sink Current (Pin 1)              |      | 50               | mA   |

| Oscillator Charging Current (Pin 9)          |      | 5                | mA   |

| Power Dissipation at $T_A = 25^{\circ}C$     |      | 1000             | mW   |

| Power Dissipation at $T_C = 25^{\circ}C$     |      | 2000             | mW   |

| Storage temperature, T <sub>stg</sub>        | -65  | 150              | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|    |      |                         |                                                                                       | VALUE | UNIT |

|----|------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|    |      |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±2500 |      |

| V( | ESD) | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±1500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                    | MIN | NOM | MAX | UNIT |

|------------------------------------|-----|-----|-----|------|

| VREF terminal external capacitance | 1   |     | 2.2 | μF   |

### 6.4 Thermal Information

|                       |                                              | 38                        | 3846                      |      |  |  |

|-----------------------|----------------------------------------------|---------------------------|---------------------------|------|--|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | N or DW (PDIP or<br>SOIC) | J or DW (CDIP or<br>SOIC) | UNIT |  |  |

|                       |                                              | 16 PINS                   | 16 PINS                   |      |  |  |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 41.8                      | 73.1                      | °C/W |  |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 28.5                      | 34.2                      | °C/W |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 21.8                      | 38.0                      | °C/W |  |  |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 13.0                      | 7.7                       | °C/W |  |  |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 21.7                      | 37.4                      | °C/W |  |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A                       | N/A                       | °C/W |  |  |

# 6.5 Electrical Characteristics

$\label{eq:T_A} \begin{array}{l} T_A = -55^\circ C \mbox{ to } +125^\circ C \mbox{ for 1846/7}; -40^\circ C \mbox{ to } +85^\circ C \mbox{ for the 2846/7}; \mbox{ and } 0^\circ C \mbox{ to } +70^\circ C \mbox{ for the 3846}; \mbox{ } V_{IN} = 15 \mbox{ V}, \\ R_T = 10k, \mbox{ } C_T = 4.7 \mbox{ nF}, \mbox{ } T_A = T_J \mbox{ (unless otherwise noted)} \end{array}$

| PARAMETER                    | TEST CONDITIONS                                                                                                                   | 1846/7<br>2846/7 |      |                       | XD/XL3846 |      |                       | UNIT  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----------------------|-----------|------|-----------------------|-------|

|                              |                                                                                                                                   | MIN              | TYP  | MAX                   | MIN       | TYP  | MAX                   |       |

| REFERENCE                    | i i                                                                                                                               |                  |      |                       |           |      |                       |       |

| Output Voltage               | $T_{J} = 25^{\circ}C, I_{O} = 1 \text{ mA}$                                                                                       | 5.05             | 5.10 | 5.15                  | 5.00      | 5.10 | 5.20                  | V     |

| Line Regulation              | $V_{IN} = 8 V$ to 40 V                                                                                                            |                  | 5    | 20                    |           | 5    | 20                    | mV    |

| Load Regulation              | $I_L = 1 \text{ mA to } 10 \text{ mA}$                                                                                            |                  | 3    | 15                    |           | 3    | 15                    | mV    |

| Temperature Stability        | Over Operating<br>Range, <sup>(1)</sup>                                                                                           |                  | 0.4  |                       |           | 0.4  |                       | mV/°C |

| Total Output Variation       | Line, Load, and<br>Temperature <sup>(1)</sup>                                                                                     | 5.00             |      | 5.20                  | 4.95      |      | 5.25                  | V     |

| Output Noise Voltage         | 10 Hz $\leq$ f $\leq$ 10 kHz, T <sub>J</sub><br>= 25°C <sup>(1)</sup>                                                             |                  | 100  |                       |           | 100  |                       | μV    |

| Long Term Stability          | $T_J = 125^{\circ}C, 1000$<br>Hrs <sup>(1)</sup>                                                                                  |                  | 5    |                       |           | 5    |                       | mV    |

| Short Circuit Output Current | V <sub>REF</sub> = 0 V                                                                                                            | -10              | -45  |                       | -10       | -45  |                       | mA    |

| OSCILLATOR                   |                                                                                                                                   |                  |      |                       |           |      |                       |       |

| Initial Accuracy             | $T_J = 25^{\circ}C$                                                                                                               | 39               | 43   | 47                    | 39        | 43   | 47                    | kHz   |

| Voltage Stability            | V <sub>IN</sub> =8 V to 40 V                                                                                                      |                  | -1%  | 2%                    |           | -1%  | 2%                    |       |

| Temperature Stability        | Over Operating<br>Range <sup>(1)</sup>                                                                                            |                  | -1%  |                       |           | -1%  |                       |       |

| Sync Output High Level       |                                                                                                                                   | 3.9              | 4.35 |                       | 3.9       | 4.35 |                       | V     |

| Sync Output Low Level        |                                                                                                                                   |                  | 2.3  | 2.5                   |           | 2.3  | 2.5                   | V     |

| Sync Input High Level        | Pin 8 = 0 V                                                                                                                       | 3.9              |      |                       | 3.9       |      |                       | V     |

| Sync Input Low Level         | Pin 8 = 0 V                                                                                                                       |                  |      | 2.5                   |           |      | 2.5                   | V     |

| Sync Input Current           | Sync Voltage = $3.9 \text{ V}$ ,<br>Pin 8 = $0 \text{ V}$                                                                         |                  | 1.3  | 1.5                   |           | 1.3  | 1.5                   | mA    |

| ERROR AMPLIFIER              |                                                                                                                                   |                  |      |                       |           |      |                       |       |

| Input Offset Voltage         |                                                                                                                                   |                  | 0.5  | 5                     |           | 0.5  | 10                    | mV    |

| Input Bias Current           |                                                                                                                                   |                  | -0.6 | -1                    |           | -0.6 | -2                    | μA    |

| Input Offset Current         |                                                                                                                                   |                  | 40   | 250                   |           | 40   | 250                   | nA    |

| Common Mode Range            | $V_{IN} = 8 V \text{ to } 40 V$                                                                                                   | 0                |      | V <sub>IN</sub> - 2 V | 0         |      | V <sub>IN</sub> - 2 V | V     |

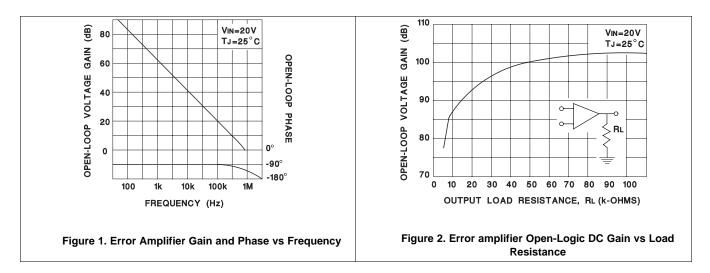

| Open Loop Voltage Gain       | $\Delta V_{O}$ = 1.2 to 3 V, V <sub>CM</sub><br>= 2 V                                                                             | 80               | 105  |                       | 80        | 105  |                       | dB    |

| Unity Gain Bandwidth         | $T_{J} = 25^{\circ}C^{(1)}$                                                                                                       | 0.7              | 1.0  |                       | 0.7       | 1.0  |                       | MHz   |

| CMRR                         | $V_{CM} = 0 V$ to 38 V,<br>$V_{IN} = 40 V$                                                                                        | 75               | 100  |                       | 75        | 100  |                       | dB    |

| PSRR                         | $V_{IN} = 8 V \text{ to } 40 V$                                                                                                   | 80               | 105  |                       | 80        | 105  |                       | dB    |

| Output Sink Current          | $\label{eq:VID} \begin{array}{l} V_{\text{ID}} = -15 \text{ mV to } -5 \text{ V}, \\ V_{\text{PIN7}} = 1.2 \text{ V} \end{array}$ | 2                | 6    |                       | 2         | 6    |                       | mA    |

| Output Source Current        | $V_{\text{ID}} = 15 \text{ mV to -5 V}, \\ V_{\text{PIN7}} = 2.5 \text{ V}$                                                       | -0.4             | -0.5 |                       | -0.4      | -0.5 |                       | mA    |

| High Level Output Voltage    | R <sub>L</sub> = (Pin 7) 15 kΩ                                                                                                    | 4.3              | 4.6  |                       | 4.3       | 4.6  |                       | V     |

| Low Level Output Voltage     | R <sub>L</sub> = (Pin 7) 15 kΩ                                                                                                    |                  | 0.7  | 1                     |           | 0.7  | 1                     | V     |

| CURRENT SENSE AMPLIFIE       | R                                                                                                                                 |                  |      | <u>.</u>              |           |      |                       |       |

| Amplifier Gain               | V <sub>PIN 3</sub> = 0 V, Pin 1<br>Open <sup>(2)</sup> , <sup>(3)</sup>                                                           | 2.5              | 2.75 | 3.0                   | 2.5       | 2.75 | 3.0                   | V     |

These parameters, although ensured over the recommended operating conditions, are not 100% tested in production.

Parameter measured at trip point of latch with VPIN 5 = VREF, VPIN 6 = 0 V.

Amplifier gain defined as: G = ΔV<sub>PIN7</sub> / ΔV<sub>PIN4</sub>; V<sub>PIN4</sub> = 0 to 1.0 V

### **Electrical Characteristics (continued)**

$T_A = -55^{\circ}C$  to +125°C for 1846/7; -40°C to +85°C for the 2846/7; and 0°C to +70°C for the 3846;  $V_{IN} = 15 V$ ,  $R_T$ =10k,  $C_T$ =4.7 nF,  $T_A$ = $T_J$  (unless otherwise noted)

| PARAMETER                                                                      | TEST CONDITIONS                                                                  | 1846/7<br>2846/7   |                    |                    | XD/XL3846 |      |                    | UNIT |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------|--------------------|--------------------|-----------|------|--------------------|------|

|                                                                                |                                                                                  | MIN                | TYP                | MAX                | MIN       | ТҮР  | MAX                | -    |

| Maximum Differential Input<br>Signal (V <sub>PIN 4</sub> -V <sub>PIN 3</sub> ) | Pin 1 Open <sup>(2)</sup> ; R <sub>L</sub><br>(Pin 7) = 15 kW                    | 1.1                | 1.2                |                    | 1.1       | 1.2  |                    | V    |

| Input Offset Voltage                                                           | $V_{PIN 1} = 0.5 V, Pin 7 Open^{(2)}$                                            |                    | 5                  | 25                 |           | 5    | 25                 | mV   |

| CMRR                                                                           | $V_{CM} = 1 V \text{ to } 12 V$                                                  | 60                 | 83                 |                    | 60        | 83   |                    | dB   |

| PSRR                                                                           | $V_{IN} = 8 V \text{ to } 40 V$                                                  | 60                 | 84                 |                    | 60        | 84   |                    | dB   |

| Input Bias Current                                                             | $V_{PIN 1} = 0.5 V$ , Pin 7<br>Open <sup>(2)</sup>                               |                    | -2.5               | -10                |           | -2.5 | -10                | μA   |

| Input Offset Current                                                           | $V_{PIN 1} = 0.5 V$ , Pin 7<br>Open <sup>(2)</sup>                               |                    | 0.08               | 1                  |           | 0.08 | 1                  | μA   |

| Input Common Mode Range                                                        |                                                                                  | 0                  |                    | V <sub>IN</sub> -3 | 0         |      | V <sub>IN</sub> -3 | V    |

| Delay to Outputs                                                               | $T_{\rm J} = 25^{\circ}C^{(1)}$                                                  |                    | 200                | 500                |           | 200  | 500                | ns   |

| CURRENT LIMIT ADJUST                                                           |                                                                                  |                    |                    |                    |           |      |                    |      |

| Current Limit Offset                                                           | V <sub>PIN 3</sub> = 0 V, V <sub>PIN 4</sub> =<br>0 V, Pin 7 Open <sup>(2)</sup> | 0.45               | 0.5                | 0.55               | 0.45      | 0.5  | 0.55               | V    |

| Input Bias Current                                                             | $V_{PIN 5} = V_{REF}, V_{PIN 6}$ $= 0 V$                                         |                    | -10                | -30                |           | -10  | -30                | μA   |

| SHUTDOWN TERMINAL                                                              |                                                                                  |                    |                    |                    |           |      |                    |      |

| Threshold Voltage                                                              |                                                                                  | 250                | 350                | 400                | 250       | 350  | 400                | mV   |

| Input Voltage Range                                                            |                                                                                  | 0                  |                    | V <sub>IN</sub>    | 0         |      | V <sub>IN</sub>    | V    |

| Minimum Latching Current (I <sub>PIN1</sub> )                                  |                                                                                  | <sup>(4)</sup> 3.0 | 1.5                |                    | 3.0       | 1.5  |                    | mA   |

| Maximum Latching Current (I <sub>PIN1</sub> )                                  |                                                                                  |                    | <sup>(5)</sup> 1.5 | 0.8                |           | 1.5  | 0.8                | mA   |

| Delay to Outputs                                                               | $T_{J} = 25^{\circ}C^{(1)}$                                                      |                    | 300                | 600                |           | 300  | 600                | ns   |

| OUTPUT                                                                         |                                                                                  |                    |                    |                    |           |      |                    |      |

| Collector-Emitter Voltage                                                      |                                                                                  | 40                 |                    |                    | 40        |      |                    | V    |

| Collector Leakage Current                                                      | $V_{\rm C} = 40 \ V^{(6)}$                                                       |                    |                    | 200                |           |      | 200                | μA   |

|                                                                                | I <sub>SINK</sub> = 20 mA                                                        |                    | 0.1                | 0.4                |           | 0.1  | 0.4                | v    |

| Output Low Level                                                               | I <sub>SINK</sub> = 100 mA                                                       |                    | 0.4                | 2.1                |           | 0.4  | 2.1                | v    |

| Output High Level                                                              | I <sub>SOURCE</sub> = 20 mA                                                      | 13                 | 13.5               |                    | 13        | 13.5 |                    | v    |

| Output high Level                                                              | I <sub>SOURCE</sub> = 100 mA                                                     | 12                 | 13.5               |                    | 12        | 13.5 |                    | v    |

| Rise Time                                                                      | $C_{L} = 1 \text{ nF}, T_{J} = 25^{\circ}C$                                      |                    | 50                 | 300                |           | 50   | 300                | ns   |

| Fall Time                                                                      | $C_{L} = 1 \text{ nF}, T_{J} = 25^{\circ}C$                                      |                    | 50                 | 300                |           | 50   | 300                | ns   |

| UNDERVOLTAGE LOCKOUT                                                           | r                                                                                |                    |                    |                    |           |      |                    |      |

| Start-Up Threshold                                                             |                                                                                  |                    | 7.7                | 8.0                |           | 7.7  | 8.0                | V    |

| Threshold Hysteresis                                                           |                                                                                  |                    | 0.75               |                    |           | 0.75 |                    | V    |

| TOTAL STANDBY CURRENT                                                          | г                                                                                |                    |                    |                    |           |      |                    |      |

| Supply Current                                                                 |                                                                                  |                    | 17                 | 21                 |           | 17   | 21                 | mA   |

Current into Pin 1 ensured to latch circuit in shutdown state. (4)

(5) Current into Pin 1 ensured not to latch circuit in shutdown state.

(6) Applies to 1846/2846/3846 only due to polarity of outputs.

# 6.6 Typical Characteristics

# 7 Detailed Description

# 7.1 Overview

The 3846 family of control devices provides the necessary features to implement off-line or DC-to-DC fixedfrequency, current-mode control schemes with a minimal external parts count. Internally implemented circuits include under-voltage lockout featuring start-up current less than 1 mA, a precision reference trimmed for accuracy at the error amplifier input, logic to insure latched operation, a PWM comparator which also provides current limit control, and a totem pole output stage designed to source or sink high-peak current. The output stage, suitable for driving either N-Channel MOSFETs or bipolar transistor switches, is low in the off state.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

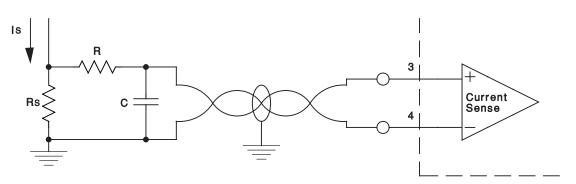

# 7.3.1 Current Sense Amplifier

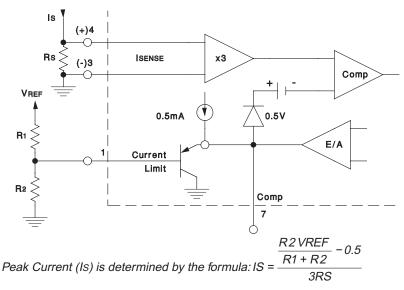

The current sense amplifier may be used in a variety of ways to sense peak switch current for comparison with an error voltage. Referring to *Functional Block Diagram*, maximum swing on the inverting input of the PWM comparator is limited to approximately 3.5 V by the internal regulated supply. Accordingly, for a fixed gain of 3, maximum differential voltages must be kept below 1.2 V at the current sense inputs.

### Feature Description (continued)

A small RC filter may be required in some applications to reduce switch transients. Differential input allows remote, noise free sensing.

#### Figure 3. Current Sense Amplifier Connection

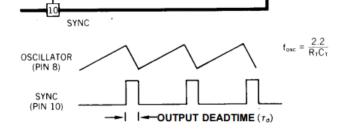

### 7.3.2 Oscillator

By implementing the oscillator using all NPN transistors, the 3846 achieves excellent temperature stability and waveform clarity at frequencies in excess of 1 MHz.

Referring to Figure 4, an external resistor  $R_T$  is used to generate a constant current into a capacitor  $C_T$  to produce a linear sawtooth waveform. Oscillator frequency may be approximated by selecting  $R_T$  and  $C_T$  such that:

$$f_{OSC} = \frac{2\pi L}{R_T C_T}$$

(1)

Figure 4. Oscillator Circuit

# 8 Application and Implementation

# 8.1 Application Information

The 3846 family of control devices provides all of the necessary features to implement fixed frequency, current mode control schemes while maintaining a minimum external parts count. The superior performance of this technique can be measured in improved line regulation, enhanced load response characteristics, and a simpler, easier to design control loop. Topological advantages include inherent pulse-by-pulse current limiting capability, automatic symmetry correction for push-pull converters. Protection circuitry includes undervoltage lockout and programmable current limit in addition to soft-start capability. A shutdown function is also available which initiates either a complete shutdown with automatic restart or latch the supply off.

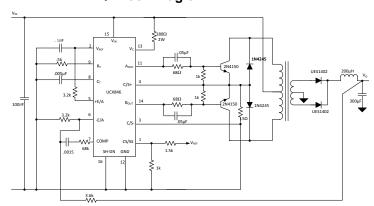

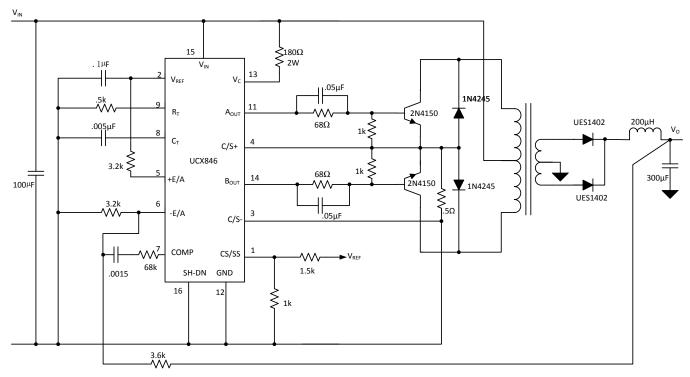

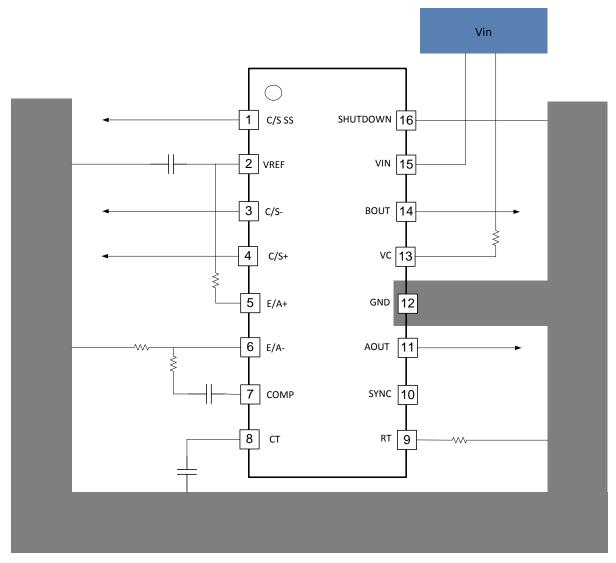

# 8.2 Typical Application

Figure 5. Typical Application Diagram

# 8.2.1 Design Requirements

Table 1 shows the design parameters for this application.

### **Table 1. Design Parameters**

| DESIGN PARAMETER                       | TARGET VALUE |

|----------------------------------------|--------------|

| Typical efficiency                     | 85%          |

| Switching frequency                    | 880 kHz      |

| Pulse by pulse current limit threshold | 1 A          |

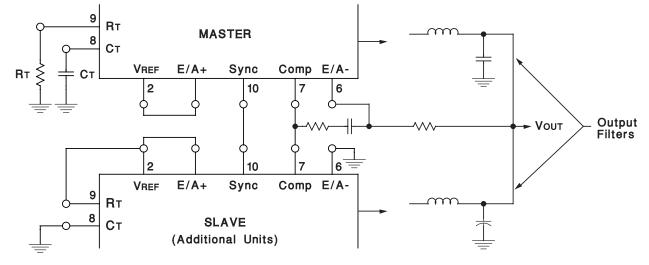

### 8.2.2 Detailed Design Procedure

This section details the design procedure based on the design requirements.

# 8.2.2.1 Design Switching Frequency

Output deadtime is determined by the external capacitor, C<sub>T</sub>, according to the formula:

$$Td(\mu s) = 145 C_{T}(\mu F) \left| \frac{ID}{ID - \frac{3.6}{RT(k\Omega)}} \right|$$

where

• ID = Oscillator discharge current at 25°C; typically is 7.5.

For large values of  $R_T$ : rd (µs ) ≈145CT (µF).

Oscillator frequency is approximated by the formula:

$$fT(kHz) \approx \frac{2.2}{\left(R_T(k\Omega) \times C_T(\mu F)\right)}$$

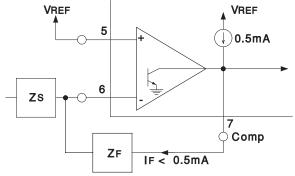

### 8.2.2.2 Error Amplifier Output Configuration

### Figure 6. Error Amplifier Output Configuration

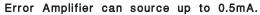

### 8.2.2.3 Parallel Operation Configuration

Slaving allows parallel operation of two or more units with equal current sharing.

Figure 8. Pulse by Pulse Current Limiting

### 8.2.2.5 Soft-Start and Shutdown, Restart Function Design

Figure 9. Soft-Start and Shutdown, Restart Functions

# 9 Layout

### 9.1 Layout Guidelines

- Place a low ESR and ESL decoupling capacitor C<sub>REF</sub> in the 1-μF to 2.2-μF range, preferably ceramic, from VREF pin to GND.

- The EA+ is a non-inverting input, the EA- is an inverting input and the COMP is the output of the error amplifier. Place resistor and capacitor series network between EA+ pin and COMP pin, and reduce the trace of resistor and capacitor series network as much as possible.

- Place a low ESR and ESL capacitor C<sub>T</sub>, preferably ceramic, from CT pin to GND, and place C<sub>T</sub> close to 3846 as much as possible.

- Place a resistor  $R_T$  from RT pin to GND, and place  $R_T$  close to UCx846/7 as much as possible.

### 9.2 Layout Example

Figure 10. 3846 Layout Example

以上信息仅供参考.如需帮助联系客服人员。谢谢 XINLUDA

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by XINLUDA manufacturer:

Other Similar products are found below :

LV5065VB-TLM-H LV5066V-TLM-H LV5725JAZ-AH 633888R MP2908AGF AZ7500EP-E1 NCP1012AP133G NCP1217P133G NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP1587GDR2G NCP6153MNTWG NCP81005MNTWG NCP81101BMNTXG NCP81205MNTXG HV9123NG-G-M934 IR35207MTRPBF ISL6367HIRZ CAT874-80ULGT3 SJ6522AG SJE6600 TLE63893GV50XUMA1 IR35215MTRPBF SG3845DM NCP1216P133G NCP1236DD65R2G NCP1247BD100R2G NCP1250BP65G NCP4202MNR2G NCP4204MNTXG NCP6132AMNR2G NCP81141MNTXG NCP81142MNTXG NCP81172MNTXG NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UC3845ADM UBA2051C IR35201MTRPBF MAX8778ETJ+ MAX17500AAUB+T MAX17411GTM+T MAX16933ATIR/V+ NCP1010AP130G NCP1063AD100R2G NCP1216AP133G NCP1217AP100G