# XD4558 DIP8 / XL4558 SOP8

#### 1 Features

- · Continuous Short-Circuit Protection

- Wide Common-Mode and Differential Voltage Ranges

- No Frequency Compensation Required

- Low Power Consumption

- No Latch-Up

- Unity-Gain Bandwidth: 3 MHz Typ

- · Gain and Phase Match Between Amplifiers

- Low Noise: 8 nV/√Hz Typ at 1 kHz

## 2 Applications

- DVD Recorders and Players

- Pro Audio Mixers

## 3 Description

The XDXL/4558 device is a dual general-purpose operational amplifier, with each half electrically similar to the  $\mu$ A741, except that offset null capability is not provided.

The high common-mode input voltage range and the absence of latch-up make this amplifier ideal for voltage-follower applications. The device is short-circuit protected, and the internal frequency compensation ensures stability without external components.

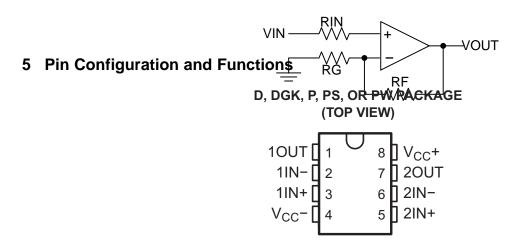

#### 4 Noninverting Amplifier Schematic

#### **Pin Functions**

| I III I Unicions  |     |      |                    |  |  |  |  |  |

|-------------------|-----|------|--------------------|--|--|--|--|--|

| PIN               |     | TYPE | DESCRIPTION        |  |  |  |  |  |

| NAME              | NO. | ITPE | DESCRIPTION        |  |  |  |  |  |

| 1IN+              | 3   | 1    | Noninverting input |  |  |  |  |  |

| 1IN-              | 2   | I    | Inverting Input    |  |  |  |  |  |

| 1OUT              | 1   | 0    | Output             |  |  |  |  |  |

| 2IN+              | 5   | I    | Noninverting input |  |  |  |  |  |

| 2IN-              | 6   | I    | Inverting Input    |  |  |  |  |  |

| 2OUT              | 7   | 0    | Output             |  |  |  |  |  |

| V <sub>CC</sub> + | 8   | _    | Positive Supply    |  |  |  |  |  |

| V <sub>CC</sub> - | 4   | _    | Negative Supply    |  |  |  |  |  |

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                   |                                                                         | MIN | MAX      | UNIT |

|-------------------|-------------------------------------------------------------------------|-----|----------|------|

| $V_{CC+}$         | Cumply yeltogo (2)                                                      |     |          | V    |

| V <sub>CC</sub> - | Supply voltage (2)                                                      |     | -18      | V    |

| $V_{\text{ID}}$   | Differential input voltage <sup>(3)</sup>                               |     | ±30      | ٧    |

| VI                | Input voltage (any input) (2)(4)                                        |     | ±15      | V    |

|                   | Duration of output short circuit to ground, one amplifier at a time (5) |     | Unlimite | ed   |

| $T_{J}$           | Operating virtual junction temperature                                  |     | 150      | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values, unless otherwise noted, are with respect to the midpoint between V<sub>CC+</sub> and V<sub>CC-</sub>

- Differential voltages are at IN+ with respect to IN-.

- (4) The magnitude of the input voltage must never exceed the magnitude of the supply voltage or 15 V, whichever is less.

- (5) Temperature and/or supply voltages must be limited to ensure that the dissipation rating is not exceeded.

## 6.2 Handling Ratings

|                    |                           |                                                         | MIN | MAX  | UNIT |

|--------------------|---------------------------|---------------------------------------------------------|-----|------|------|

| T <sub>stg</sub>   | Storage temperature range |                                                         | -65 | 150  | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | 0   | 500  | V    |

|                    |                           | Charged device model (CDM), per AEC Q100-011 (2)        | 0   | 1000 |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- 2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

|                |                                |            |     |    | UNIT |

|----------------|--------------------------------|------------|-----|----|------|

| $V_{CC+}$      | Cupply voltage                 |            | 5   | 15 | \/   |

| $V_{CC-}$      | Supply voltage                 | <b>-</b> 5 | -15 | V  |      |

| T <sub>A</sub> | Operating free cir temperature | XD4558     | 0   | 70 | °C   |

|                | Operating free-air temperature | XL4558     | -40 | 85 | 10   |

#### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                        | XDXL/4558 |     |    |    |     |      |

|-------------------------------|----------------------------------------|-----------|-----|----|----|-----|------|

|                               |                                        | D         | DGK | Р  | PS | PW  | UNIT |

|                               |                                        | 8 PINS    |     |    |    |     |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance | 97        | 172 | 85 | 95 | 149 | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

at specified free-air temperature,  $V_{CC+}$  = 15 V,  $V_{CC-}$  = -15 V

|                  | PARAMETER                                       |                                             | TEST<br>CONDITIONS <sup>(1)</sup>                                               | T <sub>A</sub> (2) | MIN | TYP | MAX | UNIT               |

|------------------|-------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------|--------------------|-----|-----|-----|--------------------|

| \/               | Input offset voltage                            |                                             | V 0                                                                             | 25°C               |     | 0.5 | 6   | mV                 |

| $V_{IO}$         |                                                 |                                             | $V_O = 0$                                                                       | Full range         |     |     | 7.5 | IIIV               |

|                  | Lead off and assessed                           |                                             | ., .                                                                            | 25°C               |     | 5   | 200 | •                  |

| I <sub>IO</sub>  | Input offset current                            |                                             | $V_O = 0$                                                                       | Full range         |     |     | 300 | nA                 |

|                  | Input bias current                              |                                             | V <sub>O</sub> = 0                                                              | 25°C               |     | 150 | 500 | nΛ                 |

| I <sub>IB</sub>  | input bias current                              |                                             | V <sub>O</sub> = 0                                                              | Full range         |     |     | 800 | nA                 |

| $V_{ICR}$        | Common-mode input voltage ra                    | ange                                        |                                                                                 | 25°C               | ±12 | ±14 |     | V                  |

|                  |                                                 |                                             | $R_L = 10 \text{ k}\Omega$                                                      | 25°C               | ±12 | ±14 |     |                    |

| $V_{OM}$         | Maximum output voltage swing                    | J                                           | B - 2 kO                                                                        | 25°C               | ±10 | ±13 |     | V                  |

|                  |                                                 |                                             | $R_L = 2 k\Omega$                                                               | Full range         | ±10 |     |     |                    |

| ٨                | Large-signal differential voltage amplification |                                             | $R_L \ge 2 k\Omega$ ,                                                           | 25°C               | 20  | 300 |     | V/mV               |

| $A_{VD}$         | Large-signal differential voltage               | $V_0 = \pm 10 \text{ V}$                    | Full range                                                                      | 15                 |     |     |     |                    |

| B <sub>1</sub>   | Unity-gain bandwidth                            |                                             |                                                                                 | 25°C               |     | 3   |     | MHz                |

| r <sub>i</sub>   | Input resistance                                |                                             |                                                                                 | 25°C               | 0.3 | 5   |     | ΜΩ                 |

| CMRR             | Common-mode rejection ratio                     |                                             |                                                                                 | 25°C               | 70  | 90  |     | dB                 |

| $k_{\text{SVS}}$ | Supply-voltage sensitivity ( $\Delta V_{IG}$    | <sub>O</sub> /ΔV <sub>CC</sub> )            | $V_{CC} = \pm 15 \text{ V}$ to $\pm 9 \text{ V}$                                | 25°C               |     | 30  | 150 | μV/V               |

| $V_n$            | Equivalent input noise voltage                  | (closed loop)                               | $A_{VD} = 100,$ $R_S = 100 \ \Omega,$ $f = 1 \ \text{Hz},$ $BW = 1 \ \text{Hz}$ | 25°C               | 8   |     |     | nV/√ <del>Hz</del> |

|                  |                                                 |                                             | V <sub>O</sub> = 0,<br>No load                                                  | 25°C               |     | 2.5 | 5.6 |                    |

| I <sub>CC</sub>  | Supply current (both amplifiers                 | )                                           |                                                                                 | T <sub>A</sub> min |     | 3   | 6.6 | mA                 |

|                  |                                                 |                                             | 140 1000                                                                        | T <sub>A</sub> max |     | 2.3 | 5   |                    |

|                  |                                                 |                                             |                                                                                 | 25°C               |     | 75  | 170 |                    |

| $P_{D}$          | Total power dissipation (both a                 | mplifiers)                                  | V <sub>O</sub> = 0,<br>No load                                                  | T <sub>A</sub> min |     | 90  | 200 | mW                 |

|                  |                                                 |                                             | 140 1040                                                                        | T <sub>A</sub> max |     | 70  | 150 | 1                  |

| \/ \/\           | Cracatally attacasetics                         | Open loop                                   | $R_S = 1 k\Omega$                                                               | 0500               |     | 85  |     | 40                 |

| $V_{O1}/V_{O2}$  | Crosstalk attenuation                           | Crosstalk attenuation A <sub>VD</sub> = 100 |                                                                                 | 25°C               |     | 105 |     | dB                 |

<sup>(1)</sup> All characteristics are measured under open-loop conditions with zero common-mode input voltage, unless otherwise specified.

(2) Full range is 0°C to 70°C for XD4558 and -40°C to 85°C for XL4558

## 6.6 Operating Characteristics

$V_{CC+}$  = 15 V,  $V_{CC-}$  = -15 V,  $T_A$  = 25°C

| PARAMETER      |                         | TEST CONDITIONS        |                     |                          | MIN | TYP  | MAX | UNIT |

|----------------|-------------------------|------------------------|---------------------|--------------------------|-----|------|-----|------|

| t <sub>r</sub> | Rise time               | $V_I = 20 \text{ mV},$ | $R_L = 2 k\Omega$ , | $C_{L} = 100 \text{ pF}$ |     | 0.13 |     | ns   |

|                | Overshoot               | $V_I = 20 \text{ mV},$ | $R_L = 2 k\Omega$ , | $C_{L} = 100 \text{ pF}$ |     | 5%   |     |      |

| SR             | Slew rate at unity gain | $V_{I} = 10 V,$        | $R_L = 2 k\Omega$ , | $C_{L} = 100 \text{ pF}$ | 1.1 | 1.7  |     | V/µs |

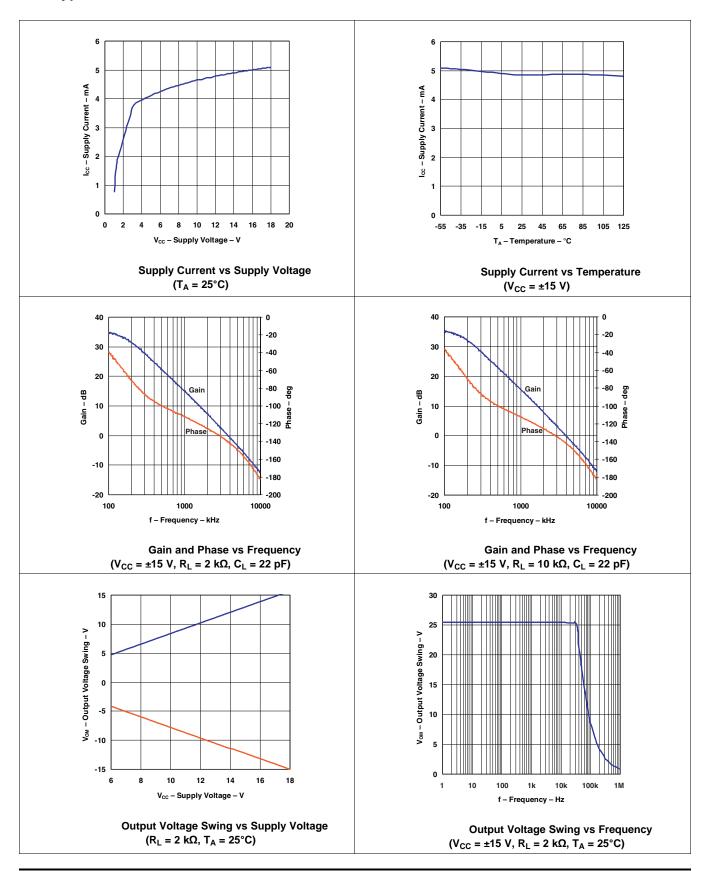

## 6.7 Typical Characteristics

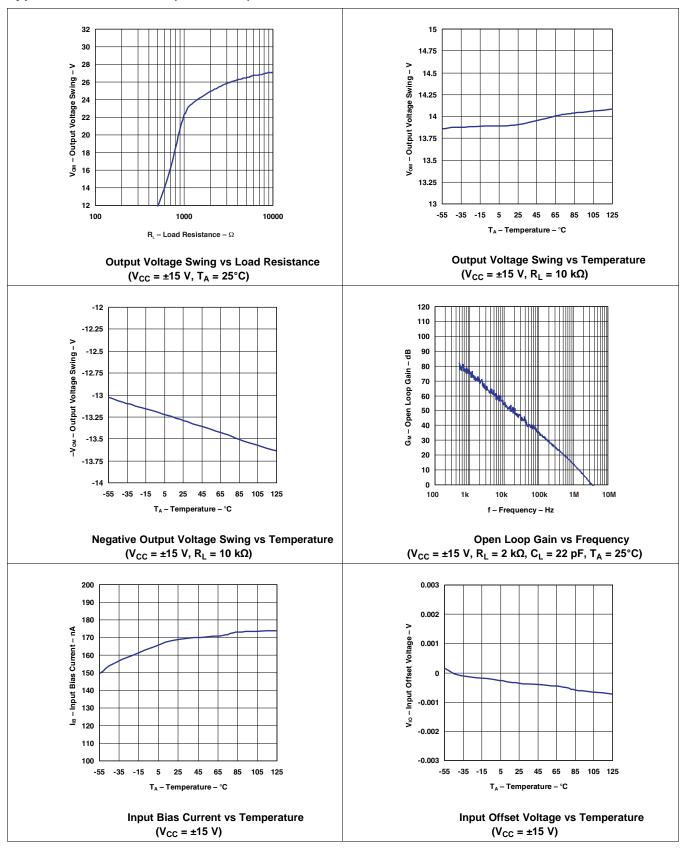

## **Typical Characteristics (continued)**

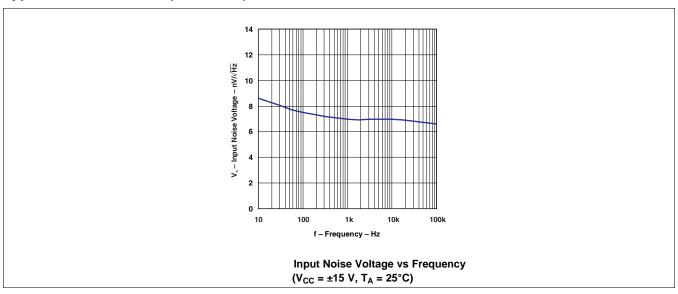

# **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

The XDXL/4558 device is a dual general-purpose operational amplifier, with each half electrically similar to the µA741, except that offset null capability is not provided.

The high common-mode input voltage range and the absence of latch-up make this amplifier ideal for voltage-follower applications. The device is short-circuit protected, and the internal frequency compensation ensures stability without external components.

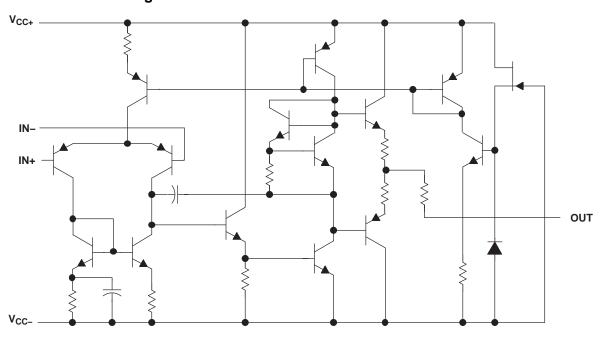

#### 7.2 Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 Unity-Gain Bandwidth

The unity-gain bandwidth is the frequency up to which an amplifier with a unity gain may be operated without greatly distorting the signal. The XDXL/4558 device has a 3-MHz unity-gain bandwidth.

#### 7.3.2 Common-Mode Rejection Ratio

The common-mode rejection ratio (CMRR) of an amplifier is a measure of how well the device rejects unwanted input signals common to both input leads. It is found by taking the ratio of the change in input offset voltage to the change in the input voltage, then converting to decibels. Ideally the CMRR is infinite, but in practice, amplifiers are designed to have it as high as possible. The CMRR of the XDXL/4558device is 90 dB.

#### 7.3.3 Slew Rate

The slew rate is the rate at which an operational amplifier can change its output when there is a change on the input. The XDXL/4558 device has a 1.7 V/µs slew rate.

#### 7.4 Device Functional Modes

The XDXL/4558 device is powered on when the supply is connected. Each of these devices can be operated as a single supply operational amplifier or dual supply amplifier depending on the application.

## 8 Application and Implementation

## 8.1 Typical Application

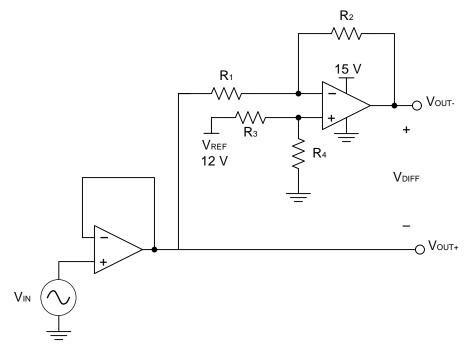

Some applications require differential signals. Figure 14 shows a simple circuit to convert a single-ended input of 2 V to 10 V into differential output of  $\pm 8$  V on a single 15-V supply. The output range is intentionally limited to maximize linearity. The circuit is composed of two amplifiers. One amplifier acts as a buffer and creates a voltage,  $V_{OUT+}$ . The second amplifier inverts the input and adds a reference voltage to generate  $V_{OUT-}$ . Both  $V_{OUT+}$  and  $V_{OUT-}$  range from 2 V to 10 V. The difference,  $V_{DIFF}$ , is the difference between  $V_{OUT+}$  and  $V_{OUT-}$ .

Schematic for Single-Ended Input to Differential Output Conversion

## **Typical Application (continued)**

#### 8.1.1 Design Requirements

The design requirements are as follows:

Supply voltage: 15 V

Reference voltage: 12V

Input: 2 V to 10 V

Output differential: ±8 V

#### 8.1.2 Detailed Design Procedure

The circuit in Figure 14 takes a single-ended input signal,  $V_{IN}$ , and generates two output signals,  $V_{OUT+}$  and  $V_{OUT-}$  using two amplifiers and a reference voltage,  $V_{REF}$ .  $V_{OUT+}$  is the output of the first amplifier and is a buffered version of the input signal,  $V_{IN}$  (see Equation 1).  $V_{OUT-}$  is the output of the second amplifier which uses  $V_{REF}$  to add an offset voltage to  $V_{IN}$  and feedback to add inverting gain. The transfer function for  $V_{OUT-}$  is Equation 2.

$$V_{OUT+} = V_{IN} \tag{1}$$

$$V_{\text{OUT-}} = V_{\text{REF}} \times \left(\frac{R_4}{R_3 + R_4}\right) \times \left(1 + \frac{R_2}{R_1}\right) - V_{\text{IN}} \times \frac{R_2}{R_1}$$

(2)

The differential output signal,  $V_{DIFF}$ , is the difference between the two single-ended output signals,  $V_{OUT+}$  and  $V_{OUT-}$ . Equation 3 shows the transfer function for  $V_{DIFF}$ . By applying the conditions that  $R_1 = R_2$  and  $R_3 = R_4$ , the transfer function is simplified into Equation 6. Using this configuration, the maximum input signal is equal to the reference voltage and the maximum output of each amplifier is equal to the  $V_{REF}$ . The differential output range is  $2 \times V_{REF}$ . Furthermore, the common mode voltage will be one half of  $V_{REF}$  (see Equation 7).

$$V_{DIFF} = V_{OUT+} - V_{OUT-} = V_{IN} \times \left(1 + \frac{R_2}{R_1}\right) - V_{REF} \times \left(\frac{R_4}{R_3 + R_4}\right) \left(1 + \frac{R_2}{R_1}\right)$$

(3)

$$V_{OUT+} = V_{IN} \tag{4}$$

$$V_{OUT-} = V_{REF} - V_{IN}$$

(5)

$$V_{DIFF} = 2xV_{IN} - V_{REF}$$

(6)

$$V_{cm} = \left(\frac{V_{OUT+} + V_{OUT-}}{2}\right) = \frac{1}{2}V_{REF}$$

(7)

#### 8.1.2.1 Amplifier Selection

Linearity over the input range is key for good dc accuracy. The common mode input range and the output swing limitations determine the linearity. In general, an amplifier with rail-to-rail input and output swing is required. Bandwidth is a key concern for this design. Because XDXL/4558 has a bandwidth of 3 MHz, this circuit will only be able to process signals with frequencies of less than 3 MHz.

#### 8.1.2.2 Passive Component Selection

Because the transfer function of  $V_{OUT-}$  is heavily reliant on resistors ( $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ ), use resistors with low tolerances to maximize performance and minimize error. This design used resistors with resistance values of 36 k $\Omega$  with tolerances measured to be within 2%. But, if the noise of the system is a key parameter, the user can select smaller resistance values (6 k $\Omega$  or lower) to keep the overall system noise low. This ensures that the noise from the resistors is lower than the amplifier noise.

## **Typical Application (continued)**

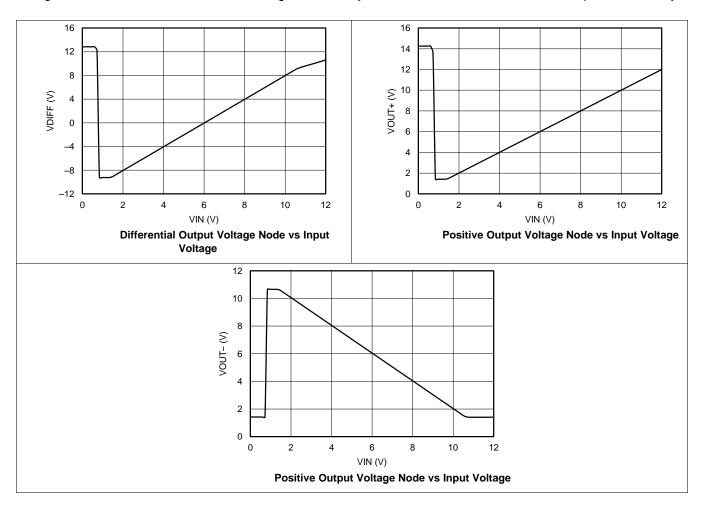

## 8.1.3 Application Curves

The measured transfer functions in Figure 15, Figure 16, and Figure 17 were generated by sweeping the input voltage from 0 V to 12 V. However, this design should only be used between 2 V and 10 V for optimum linearity.

## 9 Layout

## 9.1 Layout Guidelines

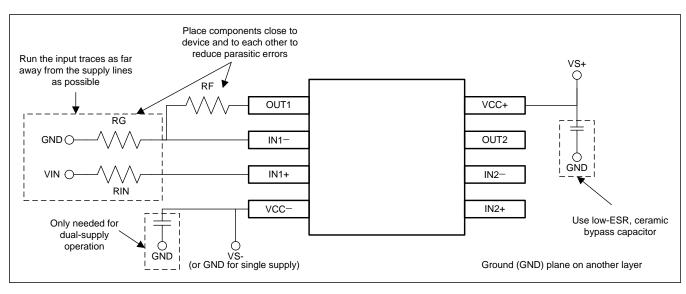

For best operational performance of the device, use good PCB layout practices, including:

- Noise can propagate into analog circuitry through the power pins of the circuit as a whole and the operational

amplifier. Bypass capacitors are used to reduce the coupled noise by providing low impedance power

sources local to the analog circuitry.

- Connect low-ESR, 0.1-µF ceramic bypass capacitors between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable for single supply applications.

- Separate grounding for analog and digital portions of circuitry is one of the simplest and most-effective

methods of noise suppression. One or more layers on multilayer PCBs are usually devoted to ground planes.

A ground plane helps distribute heat and reduces EMI noise pickup. Make sure to physically separate digital

and analog grounds, paying attention to the flow of the ground current. For more detailed information, refer to

Circuit Board Layout Techniques, (SLOA089).

- To reduce parasitic coupling, run the input traces as far away from the supply or output traces as possible. If

it is not possible to keep them separate, it is much better to cross the sensitive trace perpendicular as

opposed to in parallel with the noisy trace.

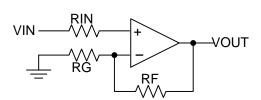

- Place the external components as close to the device as possible. Keeping RF and RG close to the inverting input minimizes parasitic capacitance, as shown in *Layout Example*.

- Keep the length of input traces as short as possible. Always remember that the input traces are the most sensitive part of the circuit.

- Consider a driven, low-impedance guard ring around the critical traces. A guard ring can significantly reduce leakage currents from nearby traces that are at different potentials.

## 9.2 Layout Example

#### **Operational Amplifier Schematic for Noninverting Configuration**

**Operational Amplifier Board Layout for Noninverting Configuration**

以上信息仅供参考. 如需帮助联系客服人员。谢谢 XINLUDA

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Operational Amplifiers - Op Amps category:

Click to view products by XINLUDA manufacturer:

Other Similar products are found below:

OPA2991IDSGR OPA607IDCKT 007614D 633773R 635798C 635801A 702115D 709228FB 741528D NCV33072ADR2G

SC2902DTBR2G SC2903DR2G SC2903VDR2G LM258AYDT LM358SNG 430227FB 430228DB 460932C AZV831KTR-G1 409256CB

430232AB LM2904DR2GH LM358YDT LT1678IS8 042225DB 058184EB 070530X SC224DR2G SC239DR2G SC2902DG

SCYA5230DR2G 714228XB 714846BB 873836HB MIC918YC5-TR TS912BIYDT NCS2004MUTAG NCV33202DMR2G

M38510/13101BPA NTE925 SC2904DR2G SC358DR2G LM358EDR2G AZV358MTR-G1 AP4310AUMTR-AG1 HA1630D02MMEL-E

NJM358CG-TE2 HA1630S01LPEL-E LM324AWPT HA1630Q06TELL-E