### 1. General description

The 8574A/PT provides general-purpose remote I/O expansion via the two-wire bidirectional I<sup>2</sup>C-bus (serial clock (SCL), serial data (SDA)).

The devices consist of eight quasi-bidirectional ports, 100 kHz I<sup>2</sup>C-bus interface, three hardware address inputs and interrupt output operating between 2.5 V and 6 V. The quasi-bidirectional port can be independently assigned as an input to monitor interrupt status or keypads, or as an output to activate indicator devices such as LEDs. System master can read from the input port or write to the output port through a single register.

The low current consumption of 2.5  $\mu$ A (typical, static) is great for mobile applications and the latched output ports directly drive LEDs.

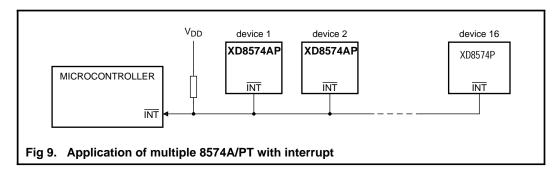

The 8574A/PT are identical, except for the different fixed portion of the slave address. The three hardware address pins allow eight of each device to be on the same I<sup>2</sup>C-bus, so there can be up to 16 of these I/O expanders 8574A/PT together on the same I<sup>2</sup>C-bus, supporting up to 128 I/Os (for example, 128 LEDs).

The active LOW open-drain interrupt output ( $\overline{INT}$ ) can be connected to the interrupt logic of the microcontroller and is activated when any input state differs from its corresponding input port register state. It is used to indicate to the microcontroller that an input state has changed and the device needs to be interrogated without the microcontroller continuously polling the input register via the I<sup>2</sup>C-bus.

The internal Power-On Reset (POR) initializes the I/Os as inputs with a weak internal pull-up 100  $\mu$ A current source.

### 2. Features and benefits

- I<sup>2</sup>C-bus to parallel port expander

- 100 kHz I<sup>2</sup>C-bus interface (Standard-mode I<sup>2</sup>C-bus)

- Operating supply voltage 2.5 V to 6 V with non-overvoltage tolerant I/O held to V<sub>DD</sub> with 100 μA current source

- 8-bit remote I/O pins that default to inputs at power-up

- Latched outputs directly drive LEDs

- Total package sink capability of 80 mA

- Active LOW open-drain interrupt output

- Eight programmable slave addresses using three address pins

- Low standby current (2.5 μA typical)

- -40 °C to +85 °C operation

- ESD protection exceeds 2000 V HBM per JESD22-A114 and 1000 V CDM per

- Latch-up testing is done to JEDEC standard JESD78 which exceeds 100 mA

- Packages offered: DIP16, SOP16

### 3. Applications

- LED signs and displays

- Servers

- Key pads

- Industrial control

- Medical equipment

- PLC

- Cellular telephones

- Mobile devices

- Gaming machines

- Instrumentation and test measurement

### 4. Ordering options

#### Table 1.Ordering options

| Type number | Package | Packing method                                  | Temperature range                             |

|-------------|---------|-------------------------------------------------|-----------------------------------------------|

| XD8574P     | DIP16   | Standard marking<br>* IC's tube - DSC bulk pack | $T_{amb} = -40 \text{ °C to +85 °C}$          |

| XD8574AP    | DIP16   | Standard marking<br>* IC's tube - DSC bulk pack | $T_{amb} = -40 \text{ °C to } +85 \text{ °C}$ |

| XL8574T     | SO16    | Standard marking<br>* tube dry pack             | $T_{amb} = -40 \text{ °C to } +85 \text{ °C}$ |

|             | SO16    | Reel 13" Q1/T1<br>*standard mark SMD dry pack   | $T_{amb} = -40 \text{ °C to } +85 \text{ °C}$ |

| XL8574AT    | SO16    | Standard marking<br>* tube dry pack             | $T_{amb} = -40 \text{ °C to } +85 \text{ °C}$ |

|             | SO16    | Reel 13" Q1/T1<br>*standard mark SMD dry pack   | $T_{amb} = -40 \text{ °C to } +85 \text{ °C}$ |

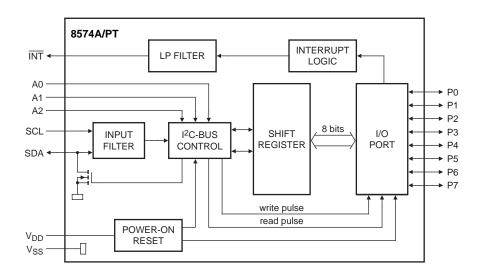

### 5. Block diagram

#### Fig 1. Block diagram

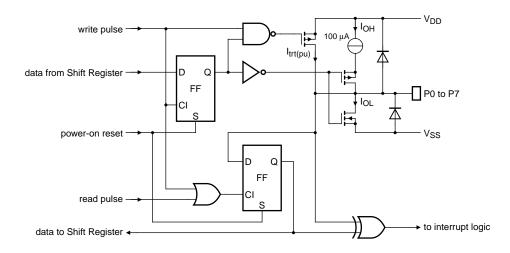

Fig 2. Simplified schematic diagram of P0 to P7

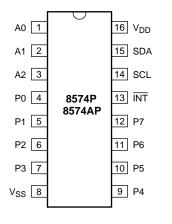

## 6. Pinning information

### 6.1 Pinning

| A0 1<br>A1 2<br>A2 3<br>P0 4<br>P1 5<br>P2 6<br>P3 7<br>Vss 8 | 8574T<br>8574AT | 16 V <sub>DD</sub><br>15 SDA<br>14 SCL<br>13 INT<br>12 P7<br>11 P6<br>10 P5<br>9 P4 |

|---------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------|

|                                                               |                 |                                                                                     |

#### Fig 3. Pin configuration for DIP16 Fig 4. Pin configuration for SO16

### 6.2 Pin description

| Table 2.        | Pin description | ı            |                               |

|-----------------|-----------------|--------------|-------------------------------|

| Symbol          | Pin             |              | Description                   |

|                 | DIP16, SO16     |              | 7                             |

| A0              | 1               | 6            | address input 0               |

| A1              | 2               | 7            | address input 1               |

| A2              | 3               | 9            | address input 2               |

| P0              | 4               | 10           | quasi-bidirectional I/O 0     |

| P1              | 5               | 11           | quasi-bidirectional I/O 1     |

| P2              | 6               | 12           | quasi-bidirectional I/O 2     |

| P3              | 7               | 14           | quasi-bidirectional I/O 3     |

| V <sub>SS</sub> | 8               | 15           | supply ground                 |

| P4              | 9               | 16           | quasi-bidirectional I/O 4     |

| P5              | 10              | 17           | quasi-bidirectional I/O 5     |

| P6              | 11              | 19           | quasi-bidirectional I/O 6     |

| P7              | 12              | 20           | quasi-bidirectional I/O 7     |

| INT             | 13              | 1            | interrupt output (active LOW) |

| SCL             | 14              | 2            | serial clock line             |

| SDA             | 15              | 4            | serial data line              |

| V <sub>DD</sub> | 16              | 5            | supply voltage                |

| n.c.            | -               | 3, 8, 13, 18 | not connected                 |

## 7. Functional description

Refer to Figure 1 "Block diagram".

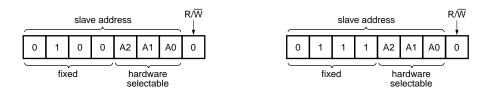

#### 7.1 Device address

Following a START condition, the bus master must send the address of the slave it is accessing and the operation it wants to perform (read or write). The address format of the 8574A/PT is shown in Figure5. Slave address pins A2, A1 and A0 are held HIGH or LOW to choose one of eight slave addresses. To conserve power, no internal pull-up resistors are incorporated on A2, A1 or A0, so they must be externally held HIGH or LOW. The address pins (A2, A1, A0) can connect to V<sub>DD</sub> or V<sub>SS</sub> directly or through resistors.

a. XD8574AP

b.XD8574P

#### Fig 5. 8574A/PT slave addresses

The last bit of the first byte defines the operation to be performed. When set to logic 1 a read is selected, while a logic 0 selects a write operation (write operation is shown in Figure 5).

#### 7.1.1 Address maps

The 8574A/PT are functionally the same, but have a different fixed portion (A6 to A3) of the slave address. This allows eight of the XD8574AP and eight of the XD8574P to be on the same I  $^{2}$ C-bus without address conflict.

| Pin c           | onnec           | tivity          |    |    | Addr | ess c | of PC | F857 | 4  |     | Address b | oyte value | 7-bit                                         |

|-----------------|-----------------|-----------------|----|----|------|-------|-------|------|----|-----|-----------|------------|-----------------------------------------------|

| A2              | A1              | A0              | A6 | A5 | A4   | A3    | A2    | A1   | A0 | R/W | Write     | Read       | hexadecimal<br>address <u></u><br>without R/W |

| V <sub>SS</sub> | V <sub>SS</sub> | $V_{SS}$        | 0  | 1  | 0    | 0     | 0     | 0    | 0  | -   | 40h       | 41h        | 20h                                           |

| $V_{SS}$        | $V_{\text{SS}}$ | $V_{DD}$        | 0  | 1  | 0    | 0     | 0     | 0    | 1  | -   | 42h       | 43h        | 21h                                           |

| $V_{SS}$        | $V_{DD}$        | $V_{SS}$        | 0  | 1  | 0    | 0     | 0     | 1    | 0  | -   | 44h       | 45h        | 22h                                           |

| $V_{SS}$        | $V_{DD}$        | $V_{DD}$        | 0  | 1  | 0    | 0     | 0     | 1    | 1  | -   | 46h       | 47h        | 23h                                           |

| $V_{DD}$        | $V_{\text{SS}}$ | $V_{\text{SS}}$ | 0  | 1  | 0    | 0     | 1     | 0    | 0  | -   | 48h       | 49h        | 24h                                           |

| $V_{DD}$        | $V_{\text{SS}}$ | $V_{\text{DD}}$ | 0  | 1  | 0    | 0     | 1     | 0    | 1  | -   | 4Ah       | 4Bh        | 25h                                           |

| $V_{DD}$        | $V_{DD}$        | $V_{SS}$        | 0  | 1  | 0    | 0     | 1     | 1    | 0  | -   | 4Ch       | 4Dh        | 26h                                           |

| $V_{\text{DD}}$ | $V_{DD}$        | $V_{DD}$        | 0  | 1  | 0    | 0     | 1     | 1    | 1  | -   | 4Eh       | 4Fh        | 27h                                           |

Table 3. 8574A/PT address map

| Pin c           | onnec           | tivity          |    | A  | Addre | ess of |    |    |    | 7-bit |       |      |                                       |

|-----------------|-----------------|-----------------|----|----|-------|--------|----|----|----|-------|-------|------|---------------------------------------|

| A2              | A1              | A0              | A6 | A5 | A4    | A3     | A2 | A1 | A0 | R/W   | Write | Read | hexadecimal<br>address<br>without R/W |

| $V_{\text{SS}}$ | V <sub>SS</sub> | V <sub>SS</sub> | 0  | 1  | 1     | 1      | 0  | 0  | 0  | -     | 70h   | 71h  | 38h                                   |

| $V_{\text{SS}}$ | $V_{SS}$        | $V_{DD}$        | 0  | 1  | 1     | 1      | 0  | 0  | 1  | -     | 72h   | 73h  | 39h                                   |

| $V_{\text{SS}}$ | $V_{\text{DD}}$ | $V_{\text{SS}}$ | 0  | 1  | 1     | 1      | 0  | 1  | 0  | -     | 74h   | 75h  | 3Ah                                   |

| $V_{\text{SS}}$ | $V_{DD}$        | $V_{DD}$        | 0  | 1  | 1     | 1      | 0  | 1  | 1  | -     | 76h   | 77h  | 3Bh                                   |

| $V_{DD}$        | $V_{SS}$        | $V_{SS}$        | 0  | 1  | 1     | 1      | 1  | 0  | 0  | -     | 78h   | 79h  | 3Ch                                   |

| $V_{DD}$        | $V_{SS}$        | $V_{DD}$        | 0  | 1  | 1     | 1      | 1  | 0  | 1  | -     | 7Ah   | 7Bh  | 3Dh                                   |

| $V_{DD}$        | $V_{DD}$        | $V_{SS}$        | 0  | 1  | 1     | 1      | 1  | 1  | 0  | -     | 7Ch   | 7Dh  | 3Eh                                   |

| $V_{DD}$        | $V_{DD}$        | $V_{DD}$        | 0  | 1  | 1     | 1      | 1  | 1  | 1  | -     | 7Eh   | 7Fh  | 3Fh                                   |

Table 4. 8574A/PT address map

### 8. I/O programming

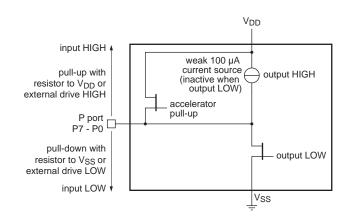

### 8.1 Quasi-bidirectional I/Os

A quasi-bidirectional I/O is an input or output port without using a direction control register. Whenever the master reads the register, the value returned to master depends on the actual voltage or status of the pin. At power on, all the ports are HIGH with a weak 100  $\mu$ A internal pull-up to V<sub>DD</sub>, but can be driven LOW by an internal transistor, or an external signal. The I/O ports are entirely independent of each other, but each I/O octal is controlled by the same read or write data byte.

Advantages of the quasi-bidirectional I/O over totem pole I/O include:

- Better for driving LEDs since the p-channel (transistor to V<sub>DD</sub>) is small, which saves die size and therefore cost. LED drive only requires an internal transistor to ground, while the LED is connected to V<sub>DD</sub> through a current-limiting resistor. Totem pole I/O have both n-channel and p-channel transistors, which allow solid HIGH and LOW output levels without a pull-up resistor — good for logic levels.

- Simpler architecture only a single register and the I/O can be both input and output at the same time. Totem pole I/O have a direction register that specifies the port pin direction and it is always in that configuration unless the direction is explicitly changed.

- Does not require a command byte. The simplicity of one register (no need for the pointer register or, technically, the command byte) is an advantage in some embedded systems where every byte counts because of memory or bandwidth limitations.

There is only one register to control four possibilities of the port pin: Input HIGH, input LOW, output HIGH, or output LOW.

**Input HIGH:** The master needs to write 1 to the register to set the port as an input mode if the device is not in the default power-on condition. The master reads the register to check the input status. If the external source pulls the port pin up to  $V_{DD}$  or drives logic 1, then the master will read the value of 1.

**Input LOW:** The master needs to write 1 to the register to set the port to input mode if the device is not in the default power-on condition. The master reads the register to check the input status. If the external source pulls the port pin down to  $V_{SS}$  or drives logic 0, which sinks the weak 100  $\mu$ A current source, then the master will read the value of 0.

**Output HIGH:** The master writes 1 to the register. There is an additional 'accelerator' or strong pull-up current when the master sets the port HIGH. The additional strong pull-up is only active during the HIGH time of the acknowledge clock cycle. This accelerator current helps the port's 100  $\mu$ A current source make a faster rising edge into a heavily loaded output, but only at the start of the acknowledge clock cycle to avoid bus contention if an external signal is pulling the port LOW to V<sub>SS</sub>/driving the port with logic 0 at the same time. After the half clock cycle there is only the 100  $\mu$ A current source to hold the port HIGH.

**Output LOW:** The master writes 0 to the register. There is a strong current sink transistor that holds the port pin LOW. A large current may flow into the port, which could potentially damage the part if the master writes a 0 to the register and an external source is pulling the port HIGH at the same time.

#### Fig 6. Simple quasi-bidirectional I/O

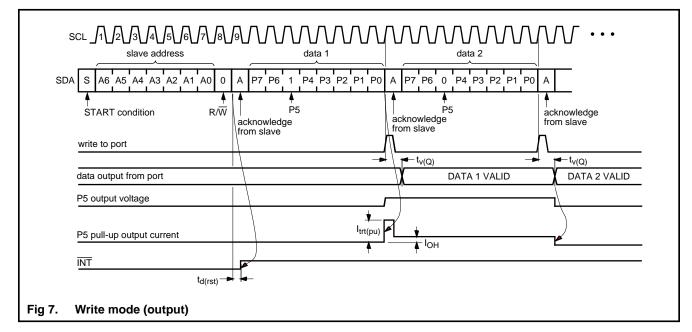

### 8.2 Writing to the port (Output mode)

The master (microcontroller) sends the START condition and slave address setting the last bit of the address byte to logic 0 for the write mode. The 8574A/PT acknowledges and the master then sends the data byte for P7 to P0 to the port register. As the clock line goes HIGH, the 8-bit data is presented on the port lines after it has been acknowledged by the 8574A/PT. If a LOW is written, the strong pull-down turns on and stays on. If a HIGH is written, the strong pull-up turns on for  $\frac{1}{2}$  of the clock cycle, then the line is held HIGH by the weak current source. The master can then send a STOP or ReSTART condition or continue sending data. The number of data bytes that can be sent successively is not limited and the previous data is overwritten every time a data byte has been sent and acknowledged.

Ensure a logic 1 is written for any port that is being used as an input to ensure the strong external pull-down is turned off.

Simple code WRITE mode:

<S> <slave address + write> <ACK> <data out> <ACK> <data out> <ACK> ... <data out> <ACK> <P>

Remark: Bold type = generated by slave device.

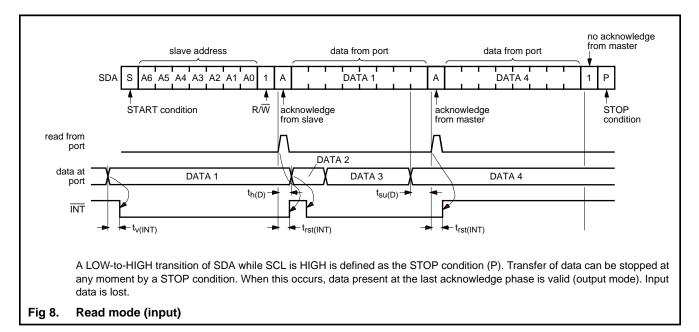

#### 8.3 Reading from a port (Input mode)

The port must have been previously written to logic 1, which is the condition after power-on reset. To enter the Read mode the master (microcontroller) addresses the slave device and sets the last bit of the address byte to logic 1 (address byte read). The slave will acknowledge and then send the data byte to the master. The master will NACK and then send the STOP condition or ACK and read the input register again.

The read of any pin being used as an output will indicate HIGH or LOW depending on the actual state of the pin.

If the data on the input port changes faster than the master can read, this data may be lost. The DATA 2 and DATA3 are lost because these data did not meet the setup time and hold time (see Figure 8).

Simple code for Read mode:

<S> <slave address + read> <**ACK**> <**data in**> <ACK> ... <**data in**> <ACK> <**data in**> <ACK> <**data in**> <NACK> <P>

**Remark:** Bold type = generated by slave device.

#### 8.4 Power-on reset

When power is applied to V<sub>DD</sub>, an internal Power-On Reset (POR) holds the 8574A/PT in a reset condition until V<sub>DD</sub> has reached V<sub>POR</sub>. At that point, the reset condition is released and the 8574A/PT registers and I <sup>2</sup>C-bus/SMBus state machine will initialize to their default states of all I/Os to inputs with weak current source to V<sub>DD</sub>. Thereafter V<sub>DD</sub> must be lowered below V<sub>POR</sub> and back up to the operation voltage for power-on reset cycle.

### 8.5 Interrupt output (INT)

The 8574A/PT provides an open-drain output (INT) which can be fed to a corresponding input of the microcontroller (see Figure 9). As soon as a port input is changed, the INT will be active (LOW) and notify the microcontroller.

An interrupt is generated at any rising or falling edge of the port inputs. After time  $t_{\nu(Q)},$  the signal  $\overline{\text{INT}}$  is valid.

The interrupt will reset to HIGH when data on the port is changed to the original setting or data is read or written by the master.

In the Write mode, the interrupt may be reset (HIGH) on the rising edge of the acknowledge bit of the address byte and also on the rising edge of the write to port pulse. The interrupt will always be reset (HIGH) on the falling edge of the write to port pulse (see <u>Figure 7</u>).

The interrupt is reset (HIGH) in the Read mode on the rising edge of the read from port pulse (see Figure8).

During the interrupt reset, any I/O change close to the read or write pulse may not generate an interrupt, or the interrupt will have a very short pulse. After the interrupt is reset, any change in I/Os will be detected and transmitted as an INT.

At power-on reset all ports are in Input mode and the initial state of the ports is HIGH, therefore, for any port pin that is pulled LOW or driven LOW by external source, the interrupt output will be active (output LOW).

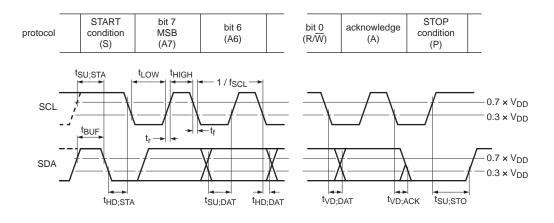

## 9. Characteristics of the l<sup>2</sup>C-bus

The I<sup>2</sup>C-bus is for 2-way, 2-wire communication between different ICs or modules. The two wires are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

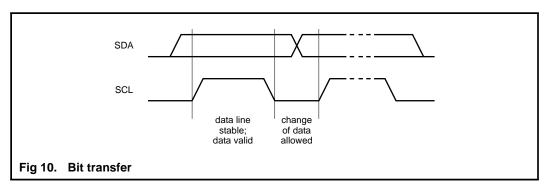

### 9.1 Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals (see <u>Figure10</u>).

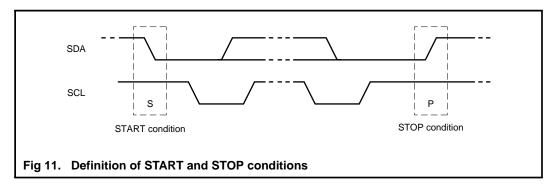

#### 9.1.1 START and STOP conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P) (see Figure 11).

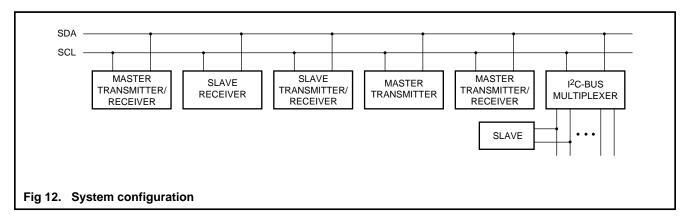

### 9.2 System configuration

A device generating a message is a 'transmitter'; a device receiving is the 'receiver'. The device that controls the message is the 'master' and the devices which are controlled by the master are the 'slaves' (see Figure 12).

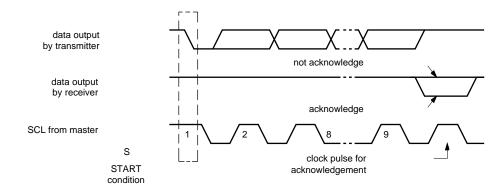

#### 9.3 Acknowledge

The number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit (see <u>Figure 13</u>). The acknowledge bit is an active LOW level (generated by the receiving device) that indicates to the transmitter that the data transfer was successful.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that wants to issue an acknowledge bit has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge bit related clock pulse; set-up and hold times must be taken into account.

A master receiver must signal an end of data to the transmitter by **not** generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

Fig 13. Acknowledgement on the I<sup>2</sup>C-bus

## 10. Application design-in information

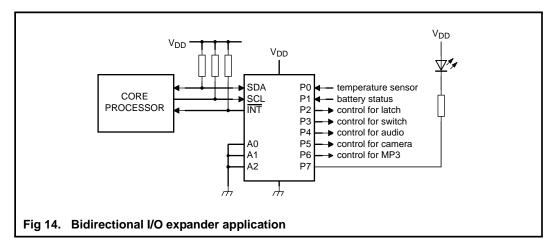

#### 10.1 Bidirectional I/O expander applications

In the 8-bit I/O expander application shown in <u>Figure 14</u>, P0 and P1 are inputs, and P2 to P7 are outputs. When used in this configuration, during a write, **the input (P0 and P1) must be written as HIGH so the external devices fully control the input ports**. The desired HIGH or LOW logic levels may be written to the ports used as outputs (P2 to P7). If 10  $\mu$ A internal output HIGH is not enough current source, the port needs external pull-up resistor. During a read, the logic levels of the external devices driving the input ports (P0 and P1) and the previous written logic level to the output ports (P2 to P7) will be read.

The GPIO also has an interrupt line ( $\overline{INT}$ ) that can be connected to the interrupt logic of the microcontroller. By sending an interrupt signal on this line, the remote I/O informs the microprocessor that there has been a change of data on its ports without having to communicate via the I<sup>2</sup>C-bus.

### 10.2 How to read and write to I/O expander (example)

In the application example of 8574A/PT shown in <u>Figure 14</u>, the microcontroller wants to control the P3 switch ON and the P7 LED ON when the temperature sensor P0 changes.

1. When the system power on:

Core Processor needs to issue an initial command to set P0 and P1 as inputs and P[7:2] as outputs with value 1010 00 (LED off, MP3 off, camera on, audio off, switch off and latch off).

2. Operation:

When the temperature changes above the threshold, the temperature sensor signal will toggle from HIGH to LOW. The INT will be activated and notifies the 'core processor' that there have been changes on the input pins. Read the input register. If P0 = 0 (temperature sensor has changed), then turn on LED and turn on switch.

3. Software code:

```

//System Power on

// write to 8574A/PT with data 1010 0011b to set P[7:2] outputs and P[1:0] inputs

<S> <0100 0000> <ACK> <1010 0011> <ACK> <P>//Initial setting for 9574

```

```

while (INT == 1); //Monitor the interrupt pin. If INT = 1 do nothing

//When INT = 0 then read input ports

<S> <slave address read> <ACK> <1010 0010> <NACK> <P> //Read 8574A/PT data

If (P0 == 0) //Temperature sensor activated

{

// write to 8574A/PT with data 0010 1011b to turn on LED (P7), on Switch (P3)

and keep P[1:0] as input ports.

<S> <0100 0000> <ACK> <0010 1011> <ACK> <P> // Write to 8574A/PT

}

```

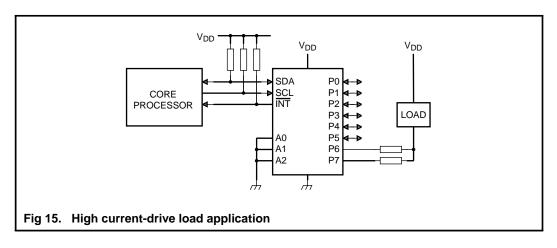

### 10.3 High current-drive load applications

The GPIO has a minimum guaranteed sinking current of 10 mA per bit at 5 V. In applications requiring additional drive, two port pins may be connected together to sink up to 20 mA current. Both bits must then always be turned on or off together. Up to five pins can be connected together to drive 80 mA, which is the device recommended total limit. Each pin needs its own limiting resistor as shown in <u>Figure 15</u> to prevent damage to the device should all ports not be turned on at the same time.

#### 10.4 Migration path

NXP offers newer, more capable drop-in replacements for the 8574A/PT in newer space-saving packages.

| Table 5. | Migration path |

|----------|----------------|

|----------|----------------|

| Type number | I <sup>2</sup> C-bus<br>frequency | Voltage range  | Number o<br>addresse<br>per devic | s   | Rese | t Total package<br>sink current |

|-------------|-----------------------------------|----------------|-----------------------------------|-----|------|---------------------------------|

| 8574A/PT    | 100 kHz                           | 2.5 V to 6 V   | 8                                 | yes | no   | 80 mA                           |

| 8574A/PT    | 400 kHz                           | 2.3 V to 5.5 V | 8                                 | yes | no   | 200 mA                          |

| 9674/74A    | 1 MHz Fm+                         | 2.3 V to 5.5 V | 64                                | yes | no   | 200 mA                          |

## 11. Limiting values

| Table 6.<br>In accorda | Limiting values<br>nce with the Absolute Maximum R | ating System (IE | EC 60134).     |                       |      |

|------------------------|----------------------------------------------------|------------------|----------------|-----------------------|------|

| Symbol                 | Parameter                                          | Conditions       | Min            | Max                   | Unit |

| V <sub>DD</sub>        | supply voltage                                     | •                | -0.5           | +7                    | V    |

| I <sub>DD</sub>        | supply current                                     |                  | -              | ±100                  | mA   |

| I <sub>SS</sub>        | ground supply current                              |                  | -              | ±100                  | mA   |

| VI                     | input voltage                                      |                  | $V_{SS} - 0.5$ | V <sub>DD</sub> + 0.5 | V    |

| l <sub>l</sub>         | input current                                      |                  | -              | ±20                   | mA   |

| l <sub>O</sub>         | output current                                     |                  | -              | ±25                   | mA   |

| P <sub>tot</sub>       | total power dissipation                            |                  | -              | 400                   | mW   |

| P/out                  | power dissipation per output                       |                  | -              | 100                   | mW   |

| T <sub>j(max)</sub>    | maximum junction temperature                       |                  | -              | 125                   | °C   |

| T <sub>stg</sub>       | storage temperature                                |                  | -65            | +150                  | °C   |

| T <sub>amb</sub>       | ambient temperature                                | operating        | -40            | +85                   | °C   |

## 12. Thermal characteristics

#### Table 7.Thermal characteristics

| Symbol               | Parameter                        | Conditions     | Тур | Unit |

|----------------------|----------------------------------|----------------|-----|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction | SO16 package   | 115 | °C/W |

|                      | to ambient                       | SSOP20 package | 136 | °C/W |

## 13. Static characteristics

#### Table 8. Static characteristics

$V_{DD}$  = 2.5 V to 6 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 °C to +85 °C; unless otherwise specified.

| Symbol                | Parameter                                              | Conditions                                                                                            | Min         | Тур | Max                   | Unit |

|-----------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------|-----|-----------------------|------|

| Supply                | •                                                      | •                                                                                                     |             | •   | •                     |      |

| V <sub>DD</sub>       | supply voltage                                         |                                                                                                       | 2.5         | -   | 6.0                   | V    |

| I <sub>DD</sub>       | supply current                                         | operating mode; $V_{DD} = 6 V$ ; no load;<br>$V_I = V_{DD}$ or $V_{SS}$ ; $f_{SCL} = 100 \text{ kHz}$ | -           | 40  | 100                   | μA   |

| I <sub>stb</sub>      | standby current                                        | standby mode; $V_{DD}$ = 6 V; no load; $V_I = V_{DD}$ or $V_{SS}$                                     | -           | 2.5 | 10                    | μA   |

| V <sub>POR</sub>      | power-on reset voltage                                 | $V_{DD}$ = 6 V; no load; $V_{I}$ = $V_{DD}$ or $V_{SS}$                                               | [1] _       | 1.3 | 2.4                   | V    |

| Input SCL             | _; input/output SDA                                    |                                                                                                       |             |     |                       |      |

| V <sub>IL</sub>       | LOW-level input voltage                                |                                                                                                       | -0.5        | -   | +0.3V <sub>DD</sub>   | V    |

| V <sub>IH</sub>       | HIGH-level input voltage                               |                                                                                                       | $0.7V_{DD}$ | -   | V <sub>DD</sub> + 0.5 | V    |

| I <sub>OL</sub>       | LOW-level output current                               | $V_{OL} = 0.4 V$                                                                                      | 3           | -   | -                     | mA   |

| IL                    | leakage current                                        | $V_{I} = V_{DD} \text{ or } V_{SS}$                                                                   | -1          | -   | +1                    | μΑ   |

| Ci                    | input capacitance                                      | $V_I = V_{SS}$                                                                                        | -           | -   | 7                     | pF   |

| I/Os; P0 to           | o P7                                                   |                                                                                                       |             |     |                       |      |

| V <sub>IL</sub>       | LOW-level input voltage                                |                                                                                                       | -0.5        | -   | +0.3V <sub>DD</sub>   | V    |

| V <sub>IH</sub>       | HIGH-level input voltage                               |                                                                                                       | $0.7V_{DD}$ | -   | V <sub>DD</sub> + 0.5 | V    |

| I <sub>IHL(max)</sub> | maximum allowed input current through protection diode | $V_{I} \geq V_{DD} \text{ or } V_{I} \leq V_{SS}$                                                     | -           | -   | ±400                  | μA   |

| I <sub>OL</sub>       | LOW-level output current                               | V <sub>OL</sub> = 1 V; V <sub>DD</sub> = 5 V                                                          | 10          | 25  | -                     | mA   |

| I <sub>OH</sub>       | HIGH-level output current                              | $V_{OH} = V_{SS}$                                                                                     | 30          | -   | 300                   | μΑ   |

| I <sub>trt(pu)</sub>  | transient boosted pull-up current                      | HIGH during acknowledge (see <u>Figure7</u> ); $V_{OH} = V_{SS}$ ; $V_{DD} = 2.5 V$                   | -           | -1  | -                     | mA   |

| Ci                    | input capacitance                                      |                                                                                                       | -           | -   | 10                    | pF   |

| Co                    | output capacitance                                     |                                                                                                       | -           | -   | 10                    | pF   |

| Interrupt             | INT (see <u>Figure7</u> )                              |                                                                                                       |             |     |                       |      |

| I <sub>OL</sub>       | LOW-level output current                               | $V_{OL} = 0.4 V$                                                                                      | 1.6         | -   | -                     | mA   |

| ΙL                    | leakage current                                        | $V_{I} = V_{DD} \text{ or } V_{SS}$                                                                   | -1          | -   | +1                    | μΑ   |

| Select inp            | outs A0, A1, A2                                        |                                                                                                       |             |     |                       |      |

| V <sub>IL</sub>       | LOW-level input voltage                                |                                                                                                       | -0.5        | -   | +0.3V <sub>DD</sub>   | V    |

| V <sub>IH</sub>       | HIGH-level input voltage                               |                                                                                                       | $0.7V_{DD}$ | -   | V <sub>DD</sub> + 0.5 | V    |

| ILI                   | input leakage current                                  | pin at $V_{DD}$ or $V_{SS}$                                                                           | -250        | -   | +250                  | nA   |

[1] The power-on reset circuit resets the  $I^2$ C-bus logic at  $V_{DD} < V_{POR}$  and sets all I/Os to logic 1 (with current source to  $V_{DD}$ ).

### 14. Dynamic characteristics

#### Table 9. Dynamic characteristics

$V_{DD} = 2.5 \text{ V}$  to 6 V;  $V_{SS} = 0 \text{ V}$ ;  $T_{amb} = -40 \text{ °C}$  to +85 °C; unless otherwise specified.

| Symbol                | Parameter                                        | Conditions                                                 | Min | Тур | Max | Unit |

|-----------------------|--------------------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

| l²C-bus ti            | ming <sup>[1]</sup> (see <u>Figure 16</u> )      |                                                            |     |     | -   |      |

| f <sub>SCL</sub>      | SCL clock frequency                              |                                                            | -   | -   | 100 | kHz  |

| t <sub>BUF</sub>      | bus free time between a STOP and START condition |                                                            | 4.7 | -   | -   | μs   |

| t <sub>HD;STA</sub>   | hold time (repeated) START condition             |                                                            | 4   | -   | -   | μS   |

| t <sub>SU;STA</sub>   | set-up time for a repeated START condition       |                                                            | 4.7 | -   | -   | μS   |

| t <sub>su;sто</sub>   | set-up time for STOP condition                   |                                                            | 4   | -   | -   | μS   |

| t <sub>HD;DAT</sub>   | data hold time                                   |                                                            | 0   | -   | -   | ns   |

| t <sub>VD;DAT</sub>   | data valid time                                  |                                                            | -   | -   | 3.4 | μS   |

| t <sub>SU;DAT</sub>   | data set-up time                                 |                                                            | 250 | -   | -   | ns   |

| t <sub>LOW</sub>      | LOW period of the SCL clock                      |                                                            | 4.7 | -   | -   | μS   |

| t <sub>HIGH</sub>     | HIGH period of the SCL clock                     |                                                            | 4   | -   | -   | μS   |

| t <sub>r</sub>        | rise time of both SDA and SCL signals            |                                                            | -   | -   | 1   | μS   |

| t <sub>f</sub>        | fall time of both SDA and SCL signals            |                                                            | -   | -   | 0.3 | μS   |

| Port timiı            | ng (see <u>Figure7</u> and <u>Figure8</u> )      |                                                            |     |     |     |      |

| t <sub>v(Q)</sub>     | data output valid time                           | $C_L \le 100 \text{ pF}$                                   | -   | -   | 4   | μS   |

| t <sub>su(D)</sub>    | data input set-up time                           | $C_L \le 100 \text{ pF}$                                   | 0   | -   | -   | μS   |

| t <sub>h(D)</sub>     | data input hold time                             | $C_L \le 100 \text{ pF}$                                   | 4   | -   | -   | μS   |

| Interrupt             | INT timing (see Figure8 )                        |                                                            |     |     |     |      |

| v(INT)                | valid time on pin INT                            | from port to $\overline{INT}$ ;<br>C <sub>L</sub> ≤ 100 pF | -   | -   | 4   | μS   |

| t <sub>rst(INT)</sub> | reset time on pin INT                            | from SCL to INT;<br>$C_L \le 100 \text{ pF}$               | -   | -   | 4   | μS   |

[1] All the timing values are valid within the operating supply voltage and ambient temperature range and refer to  $V_{IL}$  and  $V_{IH}$  with an input voltage swing of  $V_{SS}$  to  $V_{DD}$ .

Rise and fall times refer to  $V_{\text{IL}}$  and  $V_{\text{IH}}.$

#### Fig 16. I<sup>2</sup>C-bus timing diagram

以上信息仅供参考. 如需帮助联系客服人员。谢谢 XINLUDA

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - I/O Expanders category:

Click to view products by XINLUDA manufacturer:

Other Similar products are found below :

PCA9654EDR2G LA79200V-TLM-E LC709006V-E LC709006V-TLM-E NLVPCA9535EDTR2G MAX7329AWE+T MAX7313ATG+T MAX7310AUET MAX7301ATL+T MAX7317ATE+T MAX7310AEE+T MAX7318AUG+T TC7SPN334L6X,LF(S MAX7300ATL+T MAX7312ATG+T MAX7317AEE+T MAX7320ATE+T MAX7321ATE+T PI4IOE5V6408ZTAEX MAX7319AEE+T MAX7301AAI+T MAX7312AWG+T PCAL6416AEX1Z PI4IOE5V9554LEX MAX7322ATE+T CLCS82C55AZ PI4IOE5V9555LEX XP8255 PI4IOE5V6534Q2ZLWEX MCP23009T-E/SS MCP25055-IP MCP23S18T-E/MJ MD82C59A/B TMC424 DS90C385AMT PCA9539AHF,128 PCAL9554BPWJ MCP23017T-E/ML MAX7319AEE+ MAX7311AWG MAX7311ATG+T MAX7301ATL+ MAX7301AAX+ MAX7300ATL+ MAX7323AEE MAX7314ATG+ MAX7311AUG+T MAX7306AUB+ MAX7301ANI MAX1608EEE+