XLV358D SOP-8 XLV358-MS MSOP-8 XBV321-5 SOT23-5 XLV324 SOP-14

#### **FEATURES**

- (For V<sup>+</sup> = 5V and V<sup>-</sup> = 0V, unless otherwise specified)

- XBV321-5, V358, and XLV324 are available in Automotive AEC-Q100 Grade 1 & 3 versions

- Guaranteed 2.7V and 5V performance

- No crossover distortion

- Industrial temperature range -40°C to +125°C

- Gain-bandwidth product 1 MHz

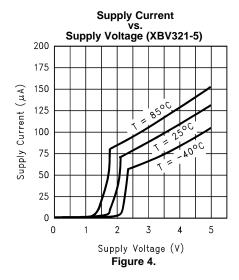

- Low supply current

- XBV321-5 130 μA

- V358 210 μA

- XLV324 410 μA

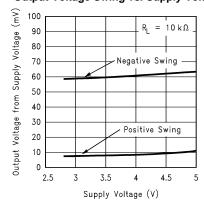

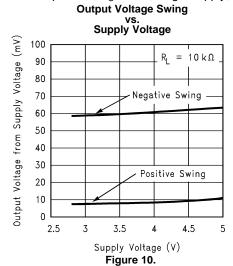

- Rail-to-rail output swing @ 10 k $\Omega$  V<sup>+</sup>- 10 mV & V<sup>-</sup>+ 65 mV

- V<sub>CM</sub> Range -0.2V to V<sup>+</sup>- 0.8V

### **APPLICATIONS**

- Active filters

- General purpose low voltage applications

- · General purpose portable devices

### **DESCRIPTION**

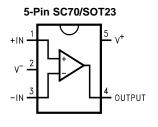

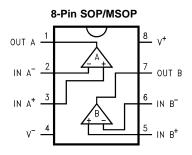

The V358/XLV324 are low voltage (2.7V to 5.5V) versions of the dual and quad commodity op amps V358/XLV324 (5V to 30V). The XBV321-5 is the single channel version. The XBV321-5/V358 /XLV324 are the most cost effective solutions for applications where low voltage operation, space efficiency, and low price are important. They offer specifications that meet or exceed the familiar V358/XLV324. The XBV321-5/V358/XLV324 have rail-to-rail output swing capability and the input common-mode voltage range includes ground. They all exhibit excellent speed to power ratio, achieving 1 MHz of bandwidth and 1 V/μs slew rate with low supply current.

The XBV321-5 is available in the space saving 5-Pin SC70, which is approximately half the size of the 5-Pin SOT23. The small package saves space on PC boards and enables the design of small portable electronic devices. It also allows the designer to place the device closer to the signal source to reduce noise pickup and increase signal integrity.

The XBV321-5/V358/XLV324-N have bipolar input and output stages for improved noise performance and higher output current drive.

#### Output Voltage Swing vs. Supply Voltage

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1)(2)

| ESD Tolerance (3)                                |                          |

|--------------------------------------------------|--------------------------|

| Human Body Model                                 |                          |

| V358/XLV324                                      | 2000V                    |

| XBV321-5                                         | 900V                     |

| Machine Model                                    | 100V                     |

| Differential Input Voltage                       | ±Supply Voltage          |

| Input Voltage                                    | −0.3V to +Supply Voltage |

| Supply Voltage (V <sup>+</sup> –V <sup>-</sup> ) | 5.5V                     |

| Output Short Circuit to V +                      | (4)                      |

| Output Short Circuit to V -                      | (5)                      |

| Soldering Information                            |                          |

| Infrared or Convection (30 sec)                  | 260°C                    |

| Storage Temp. Range                              | −65°C to 150°C           |

| Junction Temperature (6)                         | 150°C                    |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

- (2) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC)Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC

- (3) Shorting output to V<sup>+</sup> will adversely affect reliability.

- (4) Shorting output to V-will adversely affect reliability.

- (5) The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>D</sub> = (T<sub>J(MAX)</sub> T<sub>A</sub>)/ θ<sub>JA</sub>. All numbers apply for packages soldered directly onto a PC Board.

Operating Ratings (1)

| Supply Voltage                                       | 2.7V to 5.5V    |

|------------------------------------------------------|-----------------|

| Temperature Range (2)                                |                 |

| XBV321-5/V358/XLV324                                 | −40°C to +125°C |

| Thermal Resistance (θ <sub>JA</sub> ) <sup>(3)</sup> |                 |

| 5-pin SC70                                           | 478°C/W         |

| 5-pin SOT23                                          | 265°C/W         |

| 8-Pin SOP                                            | 190°C/W         |

| 8-Pin MSOP                                           | 235°C/W         |

| 14-Pin SOP                                           | 145°C/W         |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

- (2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

- (3) All numbers are typical, and apply for packages soldered directly onto a PC board in still air.

#### 2.7V DC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 2.7V$ ,  $V^- = 0V$ ,  $V_{CM} = 1.0V$ ,  $V_O = V^+/2$  and  $R_L > 1$  M $\Omega$ .

| Symbol            | Parameter                          | Conditions                                          | Min<br>(1) | <b>Typ</b> (2)     | Max<br>(1) | Units |

|-------------------|------------------------------------|-----------------------------------------------------|------------|--------------------|------------|-------|

| V <sub>OS</sub>   | Input Offset Voltage               |                                                     |            | 1.7                | 7          | mV    |

| TCV <sub>OS</sub> | Input Offset Voltage Average Drift |                                                     |            | 5                  |            | μV/°C |

| I <sub>B</sub>    | Input Bias Current                 |                                                     |            | 11                 | 250        | nA    |

| Ios               | Input Offset Current               |                                                     |            | 5                  | 50         | nA    |

| CMRR              | Common Mode Rejection Ratio        | 0V ≤ V <sub>CM</sub> ≤ 1.7V                         | 50         | 63                 |            | dB    |

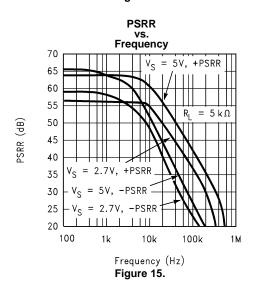

| PSRR              | Power Supply Rejection Ratio       | $2.7V \le V^+ \le 5V$ $V_O = 1V$                    | 50         | 60                 |            | dB    |

| V <sub>CM</sub>   | Input Common-Mode Voltage Range    | For CMRR ≥ 50 dB                                    | 0          | -0.2               |            | V     |

|                   |                                    |                                                     |            | 1.9                | 1.7        | V     |

| Vo                | Output Swing                       | $R_L = 10 \text{ k}\Omega \text{ to } 1.35\text{V}$ | V+ -100    | V <sup>+</sup> −10 |            | mV    |

|                   |                                    |                                                     |            | 60                 | 180        | mV    |

| Is                | Supply Current                     | XBV321-5                                            |            | 80                 | 170        | μΑ    |

|                   |                                    | V358<br>Both amplifiers                             |            | 140                | 340        | μA    |

|                   |                                    | XLV324<br>All four amplifiers                       |            | 260                | 680        | μA    |

(1) All limits are guaranteed by testing or statistical analysis.

(2) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

### 2.7V AC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for T  $_J$  = 25°C, V<sup>+</sup> = 2.7V, V<sup>-</sup> = 0V, V<sub>CM</sub> = 1.0V, V<sub>O</sub> = V<sup>+</sup>/2 and R<sub>L</sub> > 1 M $\Omega$ .

| Symbol         | Parameter                    | Conditions              | <b>Min</b> (1) | Typ  | Max<br>(1) | Units     |

|----------------|------------------------------|-------------------------|----------------|------|------------|-----------|

| GBWP           | Gain-Bandwidth Product       | C <sub>L</sub> = 200 pF |                | 1    |            | MHz       |

| $\Phi_{m}$     | Phase Margin                 |                         |                | 60   |            | Deg       |

| G <sub>m</sub> | Gain Margin                  |                         |                | 10   |            | dB        |

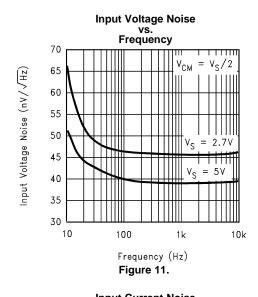

| e <sub>n</sub> | Input-Referred Voltage Noise | f = 1 kHz               |                | 46   |            | nV<br>√Hz |

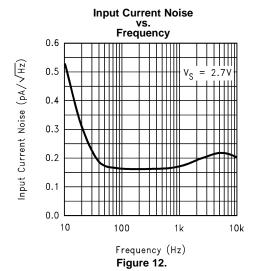

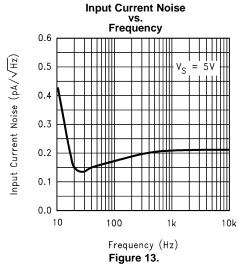

| i <sub>n</sub> | Input-Referred Current Noise | f = 1 kHz               |                | 0.17 |            | pA<br>√Hz |

(1) All limits are guaranteed by testing or statistical analysis.

(2) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

### **5V DC Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for T  $_J$  = 25°C, V<sup>+</sup> = 5V, V<sup>-</sup> = 0V, V $_{CM}$  = 2.0V, V $_O$  = V<sup>+</sup>/2 and R  $_L$  > 1 M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                          | Conditions                                                             | Min<br>(1)                                          | <b>Typ</b> (2)      | <b>Max</b> (1)     | Units |

|-------------------|------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------|---------------------|--------------------|-------|

| V <sub>OS</sub>   | Input Offset Voltage               |                                                                        |                                                     | 1.7                 | 7<br><b>9</b>      | mV    |

| TCV <sub>OS</sub> | Input Offset Voltage Average Drift |                                                                        |                                                     | 5                   |                    | μV/°C |

| I <sub>B</sub>    | Input Bias Current                 |                                                                        |                                                     | 15                  | 250<br><b>500</b>  | nA    |

| I <sub>OS</sub>   | Input Offset Current               |                                                                        |                                                     | 5                   | 50<br><b>150</b>   | nA    |

| CMRR              | Common Mode Rejection Ratio        | $0V \le V_{CM} \le 4V$                                                 | 50                                                  | 65                  |                    | dB    |

| PSRR              | Power Supply Rejection Ratio       | $2.7V \le V^+ \le 5V$<br>$V_O = 1V, V_{CM} = 1V$                       | 50                                                  | 60                  |                    | dB    |

| V <sub>CM</sub>   | Input Common-Mode Voltage Range    | For CMRR ≥ 50 dB                                                       | 0                                                   | -0.2                |                    | V     |

|                   |                                    |                                                                        |                                                     | 4.2                 | 4                  | V     |

| A <sub>V</sub>    | Large Signal Voltage Gain          | $R_L = 2 k\Omega$                                                      | 15<br><b>10</b>                                     | 100                 |                    | V/mV  |

| Vo                | Output Swing                       | $R_L = 2 k\Omega$ to 2.5V                                              | V <sup>+</sup> - 300<br>V <sup>+</sup> - <b>400</b> | V <sup>+</sup> -40  |                    | >/    |

|                   |                                    | $R_L = 2 k\Omega$ to 2.5V                                              |                                                     | 120                 | 300<br><b>400</b>  | mV    |

|                   |                                    | $R_L = 10 \text{ k}\Omega \text{ to } 2.5 \text{V}$                    | V <sup>+</sup> - 100<br>V <sup>+</sup> - <b>200</b> | V <sup>+</sup> - 10 |                    |       |

|                   |                                    | $R_L = 2 \text{ k}\Omega \text{ to } 2.5\text{V}, 125^{\circ}\text{C}$ |                                                     | 65                  | 180<br><b>280</b>  | mV    |

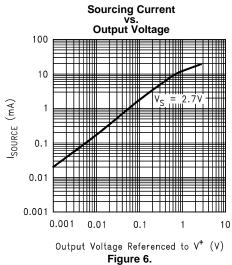

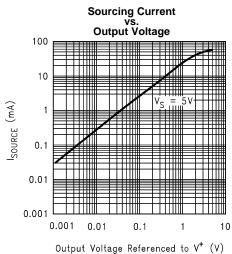

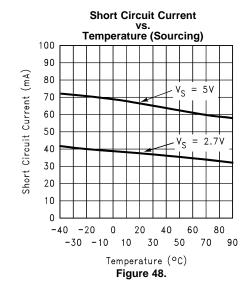

| lo                | Output Short Circuit Current       | Sourcing, V <sub>O</sub> = 0V                                          | 5                                                   | 60                  |                    | A     |

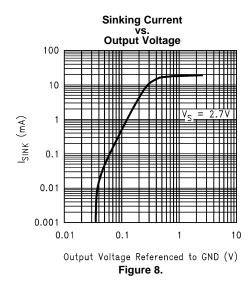

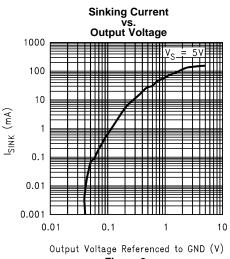

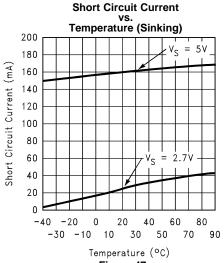

|                   |                                    | Sinking, V <sub>O</sub> = 5V                                           | 10                                                  | 160                 |                    | mA    |

| I <sub>S</sub>    | Supply Current                     | XBV321-5                                                               |                                                     | 130                 | 250<br><b>350</b>  |       |

|                   |                                    | V358 (both amps)                                                       |                                                     | 210                 | 440<br><b>615</b>  | μA    |

|                   |                                    | XLV324 (all four amps)                                                 |                                                     | 410                 | 830<br><b>1160</b> |       |

<sup>(1)</sup> All limits are guaranteed by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

<sup>(3)</sup>  $R_L$  is connected to  $V^-$ . The output voltage is  $0.5V \le V_0 \le 4.5V$ .

#### **5V AC Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = 2.0V$ ,  $V_O = V^+/2$  and R  $_L > 1$  M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                    | Conditions              | Min<br>(1) | <b>Typ</b> (2) | Max<br>(1) | Units     |

|----------------|------------------------------|-------------------------|------------|----------------|------------|-----------|

| SR             | Slew Rate                    | (3)                     |            | 1              |            | V/µs      |

| GBWP           | Gain-Bandwidth Product       | C <sub>L</sub> = 200 pF |            | 1              |            | MHz       |

| Φ <sub>m</sub> | Phase Margin                 |                         |            | 60             |            | Deg       |

| G <sub>m</sub> | Gain Margin                  |                         |            | 10             |            | dB        |

| e <sub>n</sub> | Input-Referred Voltage Noise | f = 1 kHz               |            | 39             |            | nV<br>√Hz |

| i <sub>n</sub> | Input-Referred Current Noise | f = 1 kHz               |            | 0.21           |            | pA<br>√Hz |

- (1) All limits are guaranteed by testing or statistical analysis.

- (2) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

- (3) Connected as voltage follower with 3V step input. Number specified is the slower of the positive and negative slew rates.

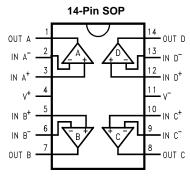

#### **CONNECTION DIAGRAM**

Figure 1. Top View

Figure 2. Top View

Figure 3. Top View

Devices with an asterisk (\*) are future products. Please contact the factory for availability.

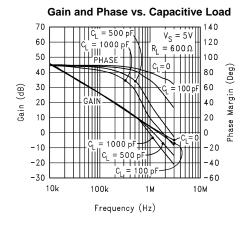

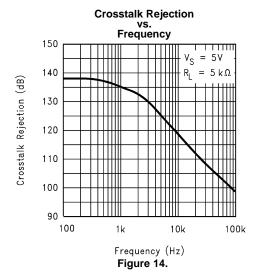

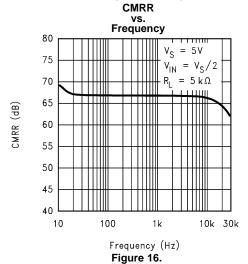

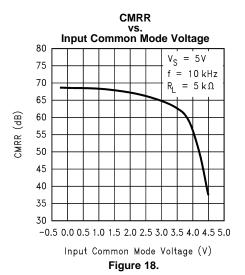

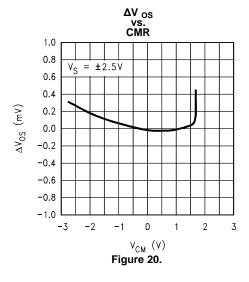

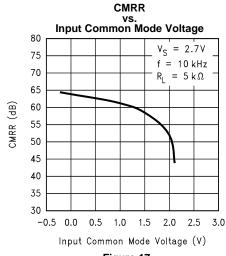

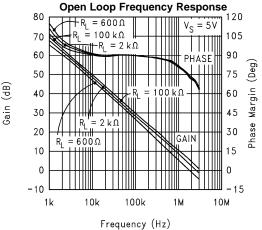

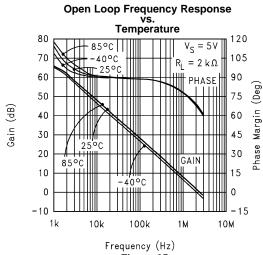

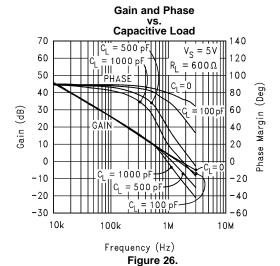

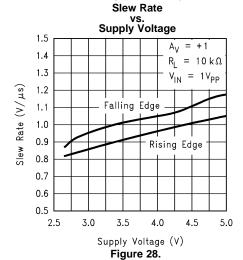

### **Typical Performance Characteristics**

Unless otherwise specified,  $V_S = +5V$ , single supply,  $T_A = 25$ °C.

Figure 7.

Unless otherwise specified,  $V_S = +5V$ , single supply,  $T_A = 25$ °C.

Unless otherwise specified,  $V_S = +5V$ , single supply,  $T_A = 25$ °C.

Figure 17.

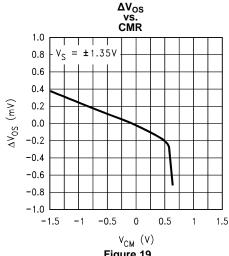

Figure 19.

Unless otherwise specified,  $V_S = +5V$ , single supply,  $T_A = 25$ °C.

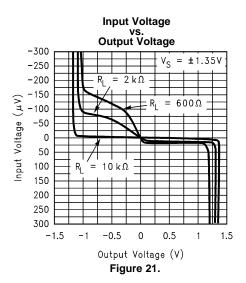

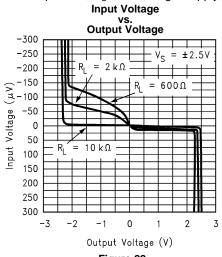

Figure 22.

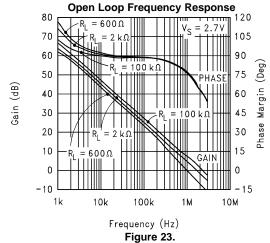

Figure 24.

Figure 25.

**Gain and Phase** vs. Capacitive Load 70 = 500 pF 60 50 40 30 20 10 0 -10 -20 -30 10k 100k 1 M 10M Frequency (Hz)

Figure 27.

Unless otherwise specified,  $V_S$  = +5V, single supply,  $T_A$  = 25°C.

TIME  $(1 \mu s/div)$ Figure 30.

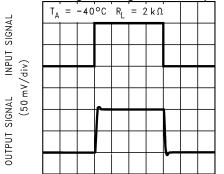

### Non-Inverting Small Signal Pulse Response

TIME (1  $\mu$ s/div) **Figure 32.**

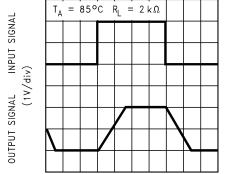

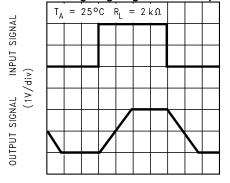

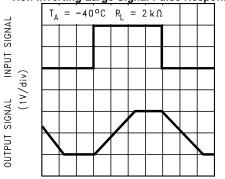

### Non-Inverting Large Signal Pulse Response

TIME (1  $\mu$ s/div) **Figure 29.**

### Non-Inverting Large Signal Pulse Response

TIME (1  $\mu$ s/div) **Figure 31.**

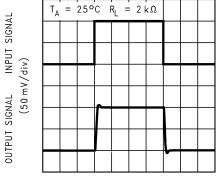

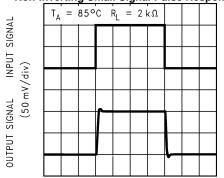

### Non-Inverting Small Signal Pulse Response

TIME (1  $\mu$ s/div) **Figure 33.**

Unless otherwise specified,  $V_S = +5V$ , single supply,  $T_A = 25$ °C.

TIME  $(1 \mu s/div)$ Figure 34.

TIME (1  $\mu$ s/div) **Figure 36.**

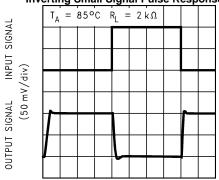

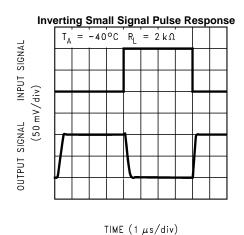

### Inverting Small Signal Pulse Response

TIME  $(1 \mu s/div)$ Figure 38.

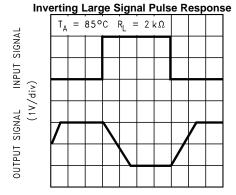

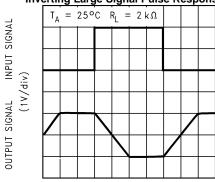

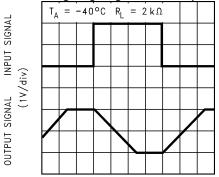

### Inverting Large Signal Pulse Response

TIME (1  $\mu$ s/div) **Figure 35.**

### Inverting Large Signal Pulse Response

TIME  $(1 \mu s/div)$ Figure 37.

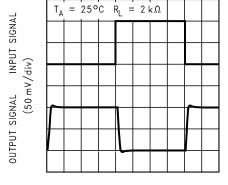

### **Inverting Small Signal Pulse Response**

TIME (1  $\mu$ s/div) **Figure 39.**

Unless otherwise specified,  $V_S = +5V$ , single supply,  $T_A = 25$ °C.

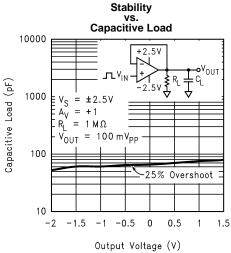

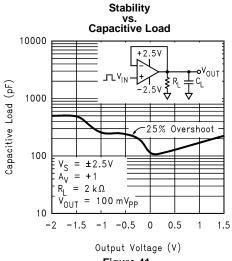

Figure 40.

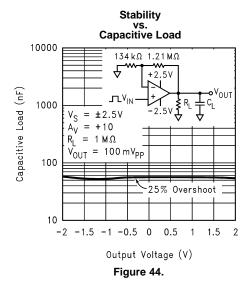

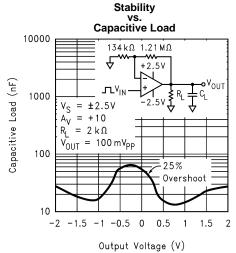

Figure 42.

Figure 41.

Figure 43.

12

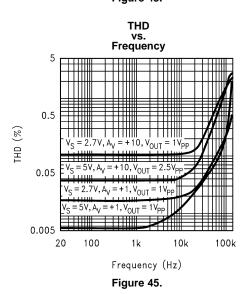

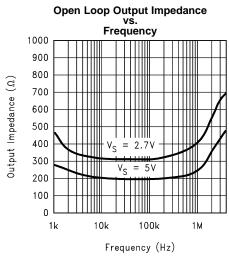

Unless otherwise specified,  $V_S = +5V$ , single supply,  $T_A = 25$ °C.

Figure 46.

Figure 47.

13

#### APPLICATION INFORMATION

#### BENEFITS OF THE XBV321-5/V358/XLV324

#### Size

The small footprints of the XBV321-5/V358/XLV324 packages save space on printed circuit boards, and enable the design of smaller electronic products, such as cellular phones, pagers, or other portable systems. The low profile of the XBV321-5/V358/XLV324 make them possible to use in PCMCIA type III cards.

### Signal Integrity

Signals can pick up noise between the signal source and the amplifier. By using a physically smaller amplifier package, the XBV321-5/V358/XLV324 can be placed closer to the signal source, reducing noise pickup and increasing signal integrity.

### **Simplified Board Layout**

These products help you to avoid using long PC traces in your PC board layout. This means that no additional components, such as capacitors and resistors, are needed to filter out the unwanted signals due to the interference between the long PC traces.

### **Low Supply Current**

These devices will help you to maximize battery life. They are ideal for battery powered systems.

### Rail-to-Rail Output

Rail-to-rail output swing provides maximum possible dynamic range at the output. This is particularly important when operating on low supply voltages.

#### **Input Includes Ground**

Allows direct sensing near GND in single supply operation.

Protection should be provided to prevent the input voltages from going negative more than -0.3V (at 25°C). An input clamp diode with a resistor to the IC input terminal can be used.

### **Ease of Use and Crossover Distortion**

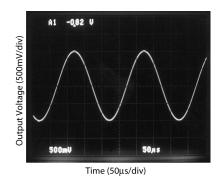

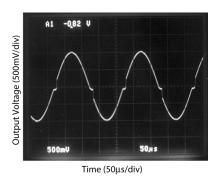

The XBV321-5/V358/XLV324 offer specifications similar to the familiar XL324. In addition, the new XBV321-5/V358/XLV324 effectively eliminate the output crossover distortion. The scope photos in Figure 49 and Figure 50 compare the output swing of the XLV324 and the XL324 in a voltage follower configuration, with  $V_S = \pm 2.5V$  and  $R_L$  (= 2 k $\Omega$ ) connected to GND. It is apparent that the crossover distortion has been eliminated in the new XLV324.

Figure 49. Output Swing of XLV324

Figure 50. Output Swing of XL324

#### **CAPACITIVE LOAD TOLERANCE**

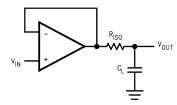

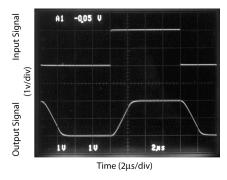

The XBV321-5/V358/XLV324 can directly drive 200 pF in unity-gain without oscillation. The unity-gain follower is the most sensitive configuration to capacitive loading. Direct capacitive loading reduces the phase margin of amplifiers. The combination of the amplifier's output impedance and the capacitive load induces phase lag. This results in either an underdamped pulse response or oscillation. To drive a heavier capacitive load, the circuit in Figure 51 can be used.

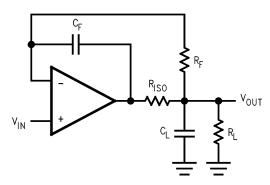

Figure 51. Indirectly Driving a Capacitive Load Using Resistive Isolation

In Figure 51 , the isolation resistor  $R_{ISO}$  and the load capacitor  $C_L$  form a pole to increase stability by adding more phase margin to the overall system. The desired performance depends on the value of  $R_{ISO}$ . The bigger the  $R_{ISO}$  resistor value, the more stable  $V_{OUT}$  will be. Figure 52 is an output waveform of Figure 51 using 620 $\Omega$  for  $R_{ISO}$  and 510 pF for  $C_L$ .

Figure 52. Pulse Response of the XLV324 Circuit in Figure 51

The circuit in Figure 53 is an improvement to the one in Figure 51 because it provides DC accuracy as well as AC stability. If there were a load resistor in Figure 51, the output would be voltage divided by  $R_{\rm ISO}$  and the load resistor. Instead, in Figure 53,  $R_{\rm F}$  provides the DC accuracy by using feed-forward techniques to connect  $V_{\rm IN}$  to  $R_{\rm L}$ . Caution is needed in choosing the value of  $R_{\rm F}$  due to the input bias current of XBV321-5/V358/XLV324  $C_{\rm F}$  and  $R_{\rm ISO}$  serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier's inverting input, thereby preserving phase margin in the overall feedback loop. Increased capacitive drive is possible by increasing the value of  $C_{\rm F}$ . This in turn will slow down the pulse response.

Figure 53. Indirectly Driving A Capacitive Load with DC Accuracy

#### INPUT BIAS CURRENT CANCELLATION

The XBV321-5/V358/XLV324 family has a bipolar input stage. The typical input bias current of XBV321-5/V358/ XLV324 is 15 nA with 5V supply. Thus a 100 k $\Omega$  input resistor will cause 1.5 mV of error voltage. By balancing the resistor values at both inverting and non-inverting inputs, the error caused by the amplifier's input bias current will be reduced. The circuit in Figure 54 shows how to cancel the error caused by input bias current.

Figure 54. Cancelling the Error Caused by Input Bias Current

#### TYPICAL SINGLE-SUPPLY APPLICATION CIRCUITS

### **Difference Amplifier**

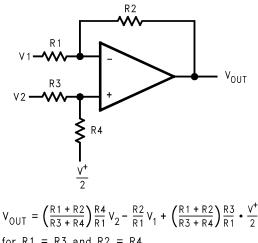

The difference amplifier allows the subtraction of two voltages or, as a special case, the cancellation of a signal common to two inputs. It is useful as a computational amplifier, in making a differential to single-ended conversion or in rejecting a common mode signal.

$$\begin{aligned} & V_{OUT} = \left(\frac{R1 + R2}{R3 + R4}\right) \frac{R4}{R1} V_2 - \frac{R2}{R1} V_1 + \left(\frac{R1 + R2}{R3 + R4}\right) \frac{R3}{R1} \cdot \frac{V_1}{2} \\ & \text{for R1} = R3 \text{ and } R2 = R4 \\ & V_{OUT} = \frac{R2}{R1} \left(V_2 - V_1\right) + \frac{V_1^+}{2} \end{aligned}$$

Figure 55. Difference Amplifier

#### **Instrumentation Circuits**

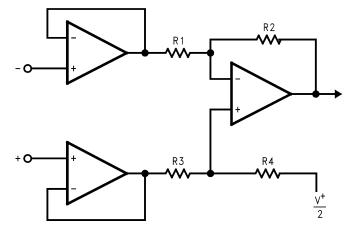

The input impedance of the previous difference amplifier is set by the resistors R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, and R<sub>4</sub>. To eliminate the problems of low input impedance, one way is to use a voltage follower ahead of each input as shown in the following two instrumentation amplifiers.

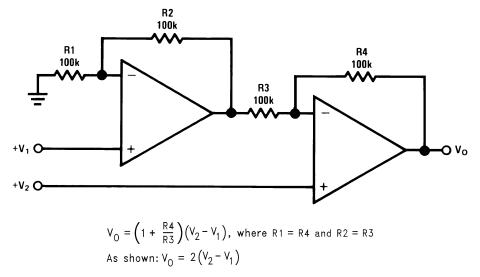

#### Three-Op-Amp Instrumentation Amplifier

The quad XLV324 can be used to build a three-op-amp instrumentation amplifier as shown in Figure 56.

Figure 56. Three-Op-Amp Instrumentation Amplifier

The first stage of this instrumentation amplifier is a differential-input, differential-output amplifier, with two voltage followers. These two voltage followers assure that the input impedance is over 100 M $\Omega$ . The gain of this instrumentation amplifier is set by the ratio of R<sub>2</sub>/R<sub>1</sub>. R<sub>3</sub> should equal R<sub>1</sub>, and R<sub>4</sub> equal R<sub>2</sub>. Matching of R<sub>3</sub> to R<sub>1</sub> and R<sub>4</sub> to R<sub>2</sub> affects the CMRR. For good CMRR over temperature, low drift resistors should be used. Making R<sub>4</sub> slightly smaller than R2 and adding a trim pot equal to twice the difference between R2 and R4 will allow the CMRR to be adjusted for optimum performance.

#### Two-Op-Amp Instrumentation Amplifier

A two-op-amp instrumentation amplifier can also be used to make a high-input-impedance DC differential amplifier (Figure 57). As in the three-op-amp circuit, this instrumentation amplifier requires precise resistor matching for good CMRR. R<sub>4</sub> should equal R<sub>1</sub> and, R<sub>3</sub> should equal R<sub>2</sub>.

Figure 57. Two-Op-Amp Instrumentation Amplifier

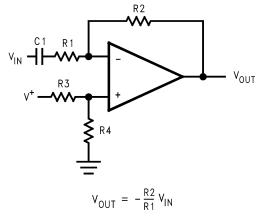

#### Single-Supply Inverting Amplifier

There may be cases where the input signal going into the amplifier is negative. Because the amplifier is operating in single supply voltage, a voltage divider using  $R_3$  and  $R_4$  is implemented to bias the amplifier so the input signal is within the input common-mode voltage range of the amplifier. The capacitor  $C_1$  is placed between the inverting input and resistor  $R_1$  to block the DC signal going into the AC signal source,  $V_{IN}$ . The values of  $R_1$  and  $C_1$  affect the cutoff frequency, fc =  $1/2\pi R_1 C_1$ .

As a result, the output signal is centered around mid-supply (if the voltage divider provides  $V^+/2$  at the non-inverting input). The output can swing to both rails, maximizing the signal-to-noise ratio in a low voltage system.

Figure 58. Single-Supply Inverting Amplifier

#### **ACTIVE FILTER**

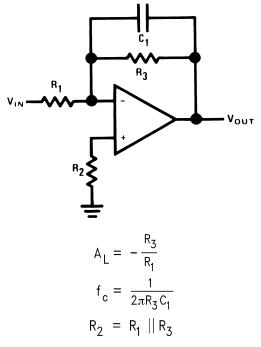

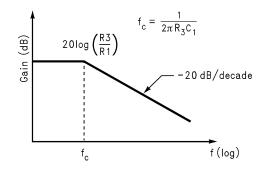

#### Simple Low-Pass Active Filter

The simple low-pass filter is shown in Figure 59. Its low-frequency gain ( $\omega \to 0$ ) is defined by  $-R_3/R_1$ . This allows low-frequency gains other than unity to be obtained. The filter has a -20 dB/decade roll-off after its corner frequency fc.  $R_2$  should be chosen equal to the parallel combination of  $R_1$  and  $R_3$  to minimize errors due to bias current. The frequency response of the filter is shown in Figure 60.

Figure 59. Simple Low-Pass Active Filter

Figure 60. Frequency Response of Simple Low-Pass Active Filter in Figure 11

Note that the single-op-amp active filters are used in the applications that require low quality factor,  $Q \le 10$ , low frequency ( $\le 5$  kHz), and low gain ( $\le 10$ ), or a small value for the product of gain times  $Q \le 100$ ). The op amp should have an open loop voltage gain at the highest frequency of interest at least 50 times larger than the gain of the filter at this frequency. In addition, the selected op amp should have a slew rate that meets the following requirement:

Slew Rate

$$\geq 0.5 \times (\omega_H V_{OPP}) \times 10^{-6} V/\mu sec$$

(1)

where  $\omega_H$  is the highest frequency of interest, and  $V_{OPP}$  is the output peak-to-peak voltage.

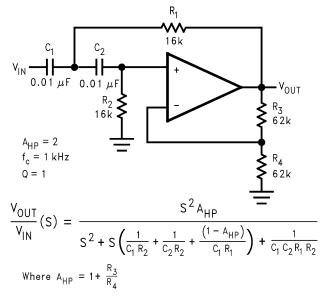

#### Sallen-Key 2nd-Order Active Low-Pass Filter

The Sallen-Key 2nd-order active low-pass filter is illustrated in Figure 61. The DC gain of the filter is expressed as

$$A_{LP} = \frac{R_3}{R_4} + 1 \tag{2}$$

Its transfer function is

$$\frac{V_{OUT}}{V_{IN}}(S) = \frac{\frac{1}{C_1 C_2 R_1 R_2} A_{LP}}{S^2 + S\left(\frac{1}{C_1 R_1} + \frac{1}{C_1 R_2} + \frac{1}{C_2 R_2} - \frac{A_{LP}}{C_2 R_2}\right) + \frac{1}{C_1 C_2 R_1 R_2}}$$

$$\frac{C1}{0.01 \mu F}$$

$$V_{IN}$$

$$\frac{R1}{16k}$$

$$C2$$

$$0.01 \mu F$$

$$C3$$

$$A_{LP} = 2$$

$$Q = 1$$

$$f_c = 1 kHz$$

Figure 61. Sallen-Key 2nd-Order Active Low-Pass Filter

The following paragraphs explain how to select values for  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$ ,  $C_1$ , and  $C_2$  for given filter requirements, such as  $A_{LP}$ , Q, and  $f_c$ .

The standard form for a 2nd-order low pass filter is

$$\frac{V_{OUT}}{V_{IN}}(S) = \frac{A_{LP} \omega_c^2}{S^2 + (\frac{\omega_c}{Q})S + \omega_c^2}$$

(4)

where

Q: Pole Quality Factor

$\omega_C$ : Corner Frequency

A comparison between Equation 3 and Equation 4 yields

$$\omega_{\rm c}^2 = \frac{1}{C_1 C_2 R_1 R_2} \tag{5}$$

$$\frac{\omega_{\rm C}}{Q} = \frac{1}{C_1 R_1} + \frac{1}{C_1 R_2} + \frac{1}{C_2 R_2} - \frac{A_{\rm LP}}{C_2 R_2}$$

(6)

To reduce the required calculations in filter design, it is convenient to introduce normalization into the components and design parameters. To normalize, let  $\omega_C = \omega_n = 1$  rad/s, and  $C_1 = C_2 = C_n = 1$ F, and substitute these values into Equation 5 and Equation 6. From Equation 5, we obtain

$$R_1 = \frac{1}{R_2} \tag{7}$$

From Equation 6, we obtain

$$R_2 = \frac{1 \pm \sqrt{1 - 4Q^2(2 - A_{LP})}}{2Q}$$

(8)

For minimum DC offset,  $V^+ = V^-$ , the resistor values at both inverting and non-inverting inputs should be equal, which means

$$R_1 + R_2 = \frac{R_3 R_4}{R_3 + R_4} \tag{9}$$

XLV358D SOP-8 XLV358-MS MSOP-8 XBV321-5 SOT23-5 XLV324 SOP-14

From Equation 2 and Equation 9, we obtain

$$R_3 = (R_1 + R_2)A_{LP} \tag{10}$$

$$R_4 = \left(\frac{A_{LP}}{A_{LP}-1}\right) (R_1 + R_2) \tag{11}$$

The values of C<sub>1</sub> and C<sub>2</sub> are normally close to or equal to

$$C = \frac{10}{f_c} \mu F \tag{12}$$

As a design example:

Require:  $A_{LP} = 2$ , Q = 1, fc = 1 kHz

Start by selecting C<sub>1</sub> and C<sub>2</sub>. Choose a standard value that is close to

$$C = \frac{10}{f_c} \mu F \tag{13}$$

$$C_1 = C_2 = \frac{10}{1 \times 10^3} \,\mu\text{F} = 0.01 \,\mu\text{F}$$

(14)

From Equation 7 Equation 8 Equation 10 Equation 11,

$$R_1 = 1\Omega \tag{15}$$

$$R_2 = 1\Omega \tag{16}$$

$$R_3 = 4\Omega \tag{17}$$

$$R_4 = 4\Omega \tag{18}$$

The above resistor values are normalized values with  $\omega_n = 1$  rad/s and  $C_1 = C_2 = C_n = 1$ F. To scale the normalized cutoff frequency and resistances to the real values, two scaling factors are introduced, frequency scaling factor ( $k_f$ ) and impedance scaling factor ( $k_m$ ).

$$k_f = \frac{\omega_c}{\omega_n} = \frac{2\pi \times 1 \times 10^3}{1} = 2\pi \times 10^3$$

$$k_m k_f = \frac{Cn}{C1}$$

$$k_{\rm m} = 1.59 \times 10^4$$

(19)

Scaled values:

$$R_2 = R_1 = 15.9 \text{ k}\Omega$$

(20)

$$R_3 = R_4 = 63.6 \text{ k}\Omega$$

(21)

$$C_1 = C_2 = 0.01 \,\mu\text{F}$$

(22)

An adjustment to the scaling may be made in order to have realistic values for resistors and capacitors. The actual value used for each component is shown in the circuit.

#### 2nd-Order High Pass Filter

A 2nd-order high pass filter can be built by simply interchanging those frequency selective components ( $R_1$ ,  $R_2$ ,  $C_1$ ,  $C_2$ ) in the Sallen-Key 2nd-order active low pass filter. As shown in Figure 62, resistors become capacitors, and capacitors become resistors. The resulted high pass filter has the same corner frequency and the same maximum gain as the previous 2nd-order low pass filter if the same components are chosen.

Figure 62. Sallen-Key 2nd-Order Active High-Pass Filter

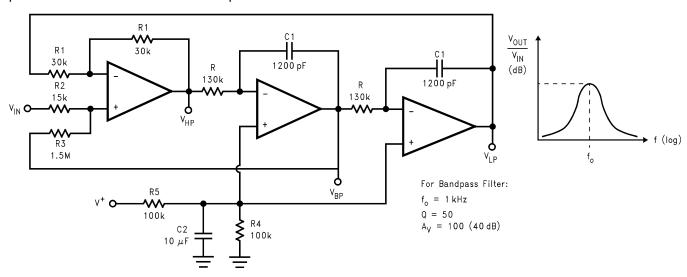

#### State Variable Filter

A state variable filter requires three op amps. One convenient way to build state variable filters is with a quad op amp, such as the XLV324 (Figure 63).

This circuit can simultaneously represent a low-pass filter, high-pass filter, and bandpass filter at three different outputs. The equations for these functions are listed below. It is also called "Bi-Quad" active filter as it can produce a transfer function which is quadratic in both numerator and denominator.

Figure 63. State Variable Active Filter

(23)

$$V_{LP} = \left(\frac{2R_3}{R_2 + R_3}\right) \frac{\frac{1}{R^2 c^2}}{S^2 + \frac{1}{\left(\frac{R_2 + R_3}{2R_2}\right) RC} S + \frac{1}{R^2 c^2}} V_{IN}$$

$$V_{HP} = \left(\frac{2R_3}{R_2 + R_3}\right) \frac{S^2}{S^2 + \left(\frac{1}{\frac{R_2 + R_3}{2R_2}}\right) RC} S + \frac{1}{R^2 C^2} V_{IN}$$

$$V_{BP} = \left(\frac{2R_3}{R_2 + R_3}\right) \frac{\left(\frac{1}{RC}\right)S}{S^2 + \frac{1}{\left(\frac{R_2 + R_3}{2R_2}\right)RC}S + \frac{1}{R^2C^2}} V_{IN}$$

where for all three filters,

$$Q = \frac{R_2 + R_3}{2R_2} \tag{24}$$

$$\omega_0 = \frac{1}{RC}$$

(resonant frequency) (25)

A design example for a bandpass filter is shown below:

Assume the system design requires a bandpass filter with  $f_0 = 1$  kHz and Q = 50. What needs to be calculated are capacitor and resistor values.

First choose convenient values for C<sub>1</sub>, R<sub>1</sub> and R<sub>2</sub>:

$$C_1 = 1200 \text{ pF}$$

(26)

$$2R_2 = R_1 = 30 \text{ k}\Omega \tag{27}$$

Then from Equation 24,

$$R_3 = R_2(2Q-1)$$

$R_3 = 15 k\Omega \times (2 \times 50-1)$

$= 1.5 M\Omega$  (28)

From Equation 25,

$$R = \frac{1}{\omega_0 C_1}$$

$$R = \frac{1}{(2\pi x 10^3)(1.2 \times 10^{-9})}$$

$$= 132.7 \text{ k}\Omega$$

(29)

From the above calculated values, the midband gain is  $H_0 = R_3/R_2 = 100$  (40 dB). The nearest 5% standard values have been added to Figure 63.

#### PULSE GENERATORS AND OSCILLATORS

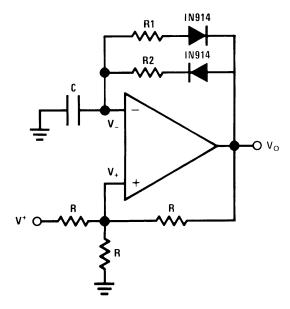

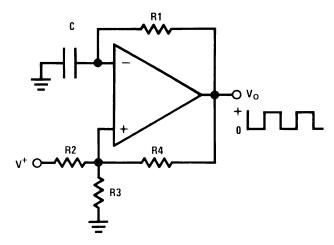

A pulse generator is shown in Figure 64. Two diodes have been used to separate the charge and discharge paths to capacitor C.

Figure 64. Pulse Generator

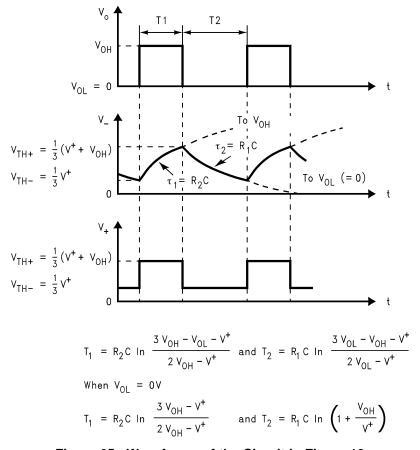

When the output voltage  $V_O$  is first at its high,  $V_{OH}$ , the capacitor C is charged toward  $V_{OH}$  through  $R_2$ . The voltage across C rises exponentially with a time constant  $\tau=R_2C$ , and this voltage is applied to the inverting input of the op amp. Meanwhile, the voltage at the non-inverting input is set at the positive threshold voltage  $(V_{TH+})$  of the generator. The capacitor voltage continually increases until it reaches  $V_{TH+}$ , at which point the output of the generator will switch to its low,  $V_{OL}$  which 0V is in this case. The voltage at the non-inverting input is switched to the negative threshold voltage  $(V_{TH-})$  of the generator. The capacitor then starts to discharge toward  $V_{OL}$  exponentially through  $R_1$ , with a time constant  $\tau=R_1C$ . When the capacitor voltage reaches  $V_{TH-}$ , the output of the pulse generator switches to  $V_{OH}$ . The capacitor starts to charge, and the cycle repeats itself.

Figure 65. Waveforms of the Circuit in Figure 16

As shown in the waveforms in Figure 65, the pulse width  $(T_1)$  is set by  $R_2$ , C and  $V_{OH}$ , and the time between pulses  $(T_2)$  is set by  $R_1$ , C and  $V_{OL}$ . This pulse generator can be made to have different frequencies and pulse width by selecting different capacitor value and resistor values.

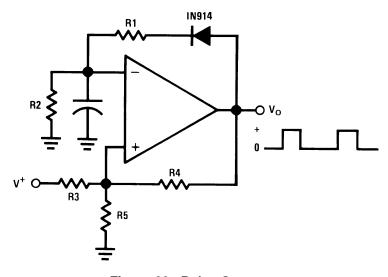

Figure 66 shows another pulse generator, with separate charge and discharge paths. The capacitor is charged through  $R_1$  and is discharged through  $R_2$ .

Figure 66. Pulse Generator

Figure 67 is a squarewave generator with the same path for charging and discharging the capacitor.

Figure 67. Squarewave Generator

#### **CURRENT SOURCE AND SINK**

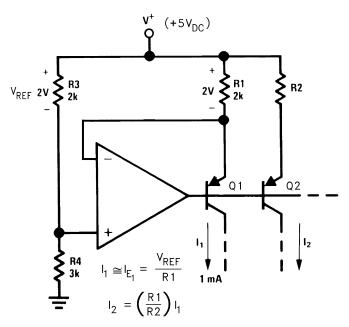

The XBV321-5/V358/XLV324 can be used in feedback loops which regulate the current in external PNP transistors to provide current sources or in external NPN transistors to provide current sinks.

#### **Fixed Current Source**

A multiple fixed current source is shown in Figure 68. A voltage ( $V_{REF} = 2V$ ) is established across resistor  $R_3$  by the voltage divider ( $R_3$  and  $R_4$ ). Negative feedback is used to cause the voltage drop across  $R_1$  to be equal to  $V_{REF}$ . This controls the emitter current of transistor  $Q_1$  and if we neglect the base current of  $Q_1$  and  $Q_2$ , essentially this same current is available out of the collector of  $Q_1$ .

Large input resistors can be used to reduce current loss and a Darlington connection can be used to reduce errors due to the  $\beta$  of  $Q_1$ .

The resistor,  $R_2$ , can be used to scale the collector current of  $Q_2$  either above or below the 1 mA reference value.

Figure 68. Fixed Current Source

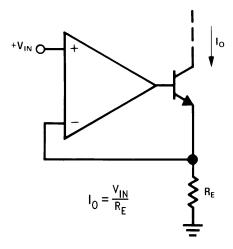

### **High Compliance Current Sink**

A current sink circuit is shown in Figure 69. The circuit requires only one resistor (R<sub>E</sub>) and supplies an output current which is directly proportional to this resistor value.

Figure 69. High Compliance Current Sink

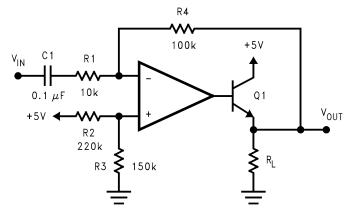

### **POWER AMPLIFIER**

A power amplifier is illustrated in Figure 70. This circuit can provide a higher output current because a transistor follower is added to the output of the op amp.

Figure 70. Power Amplifier

### **LED DRIVER**

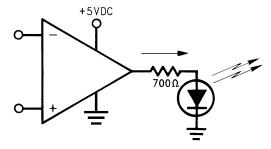

The XBV321-5/V358/XLV324 can be used to drive an LED as shown in Figure 71.

Figure 71. LED Driver

XLV358D SOP-8 XLV358-MS MSOP-8 XBV321-5 SOT23-5 XLV324 SOP-14

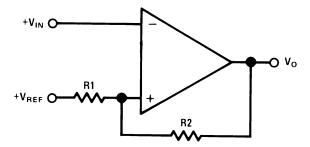

#### **COMPARATOR WITH HYSTERESIS**

The XBV321-5/V358/XLV324 can be used as a low power comparator. Figure 72 shows a comparator with hysteresis. The hysteresis is determined by the ratio of the two resistors.

$$V_{TH+} = V_{REF}/(1+R_1/R_2)+V_{OH}/(1+R_2/R_1)$$

(30)

$$V_{TH-} = V_{REF}/(1+R_1/R_2)+V_{OL}/(1+R_2/R_1)$$

(31)

$$V_{H} = (V_{OH} - V_{OL})/(1 + R_{2}/R_{1})$$

(32)

#### where

$V_{TH+}$ : Positive Threshold Voltage  $V_{TH-}$ : Negative Threshold Voltage

V<sub>OH</sub>: Output Voltage at High V<sub>OL</sub>: Output Voltage at Low

V<sub>H</sub>: Hysteresis Voltage

Since XBV321-5/V358/XLV324 have rail-to-rail output, the ( $V_{OH-}V_{OL}$ ) is equal to  $V_S$ , which is the supply voltage.

$$V_{H} = V_{S}/(1 + R_{2}/R_{1}) \tag{33}$$

Figure 72. Comparator with Hysteresis

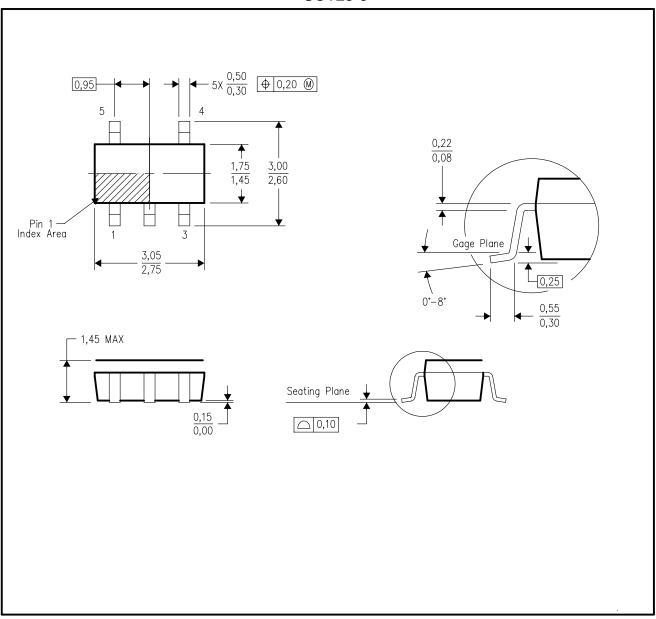

### SOT23-5

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- C. Body dimensions do not include mold fla D. Falls within JEDEC MO—178 Variation AA.

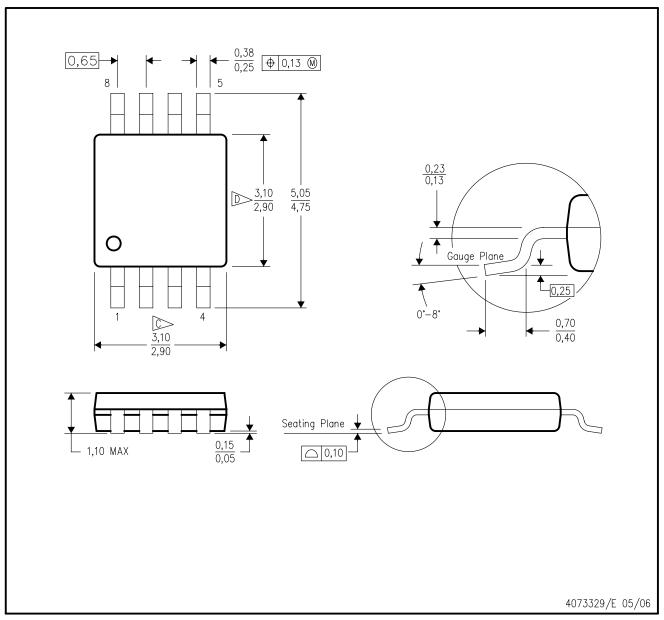

### MSOP-8

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

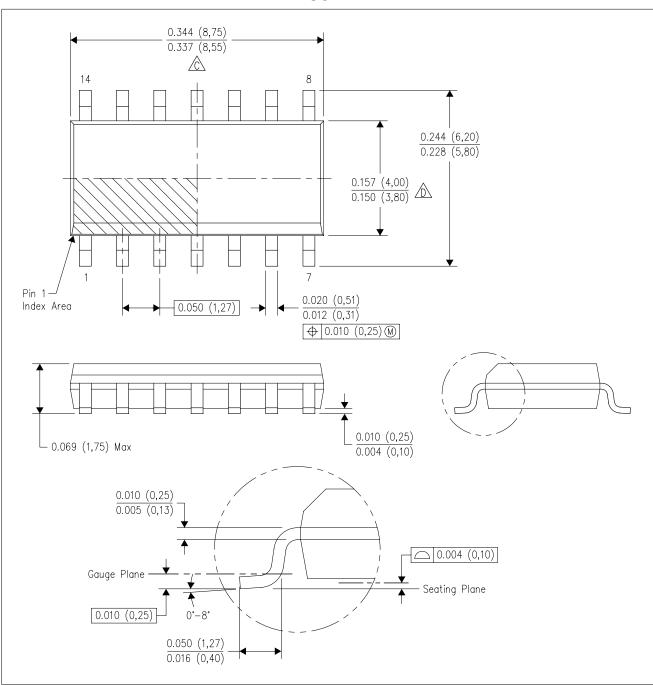

### SOP-14

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AB.

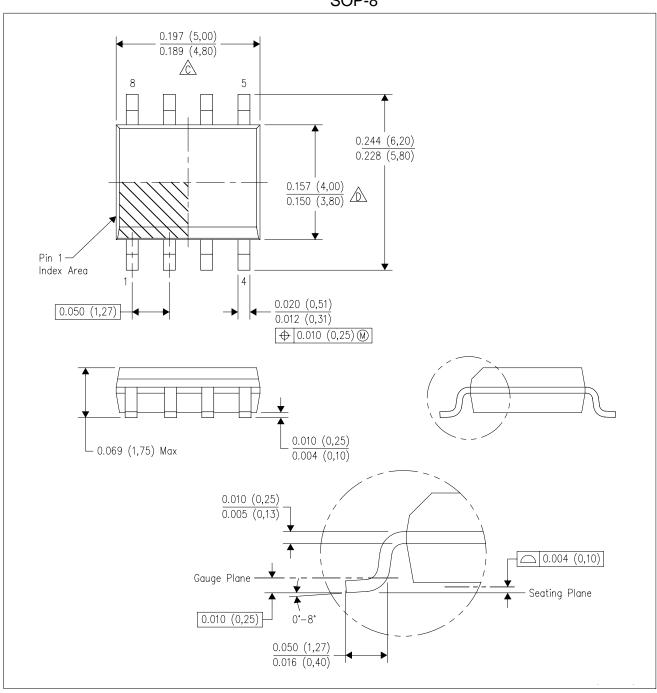

### SOP-8

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Operational Amplifiers - Op Amps category:

Click to view products by XINLUDA manufacturer:

Other Similar products are found below:

OPA2991IDSGR OPA607IDCKT 007614D 633773R 635798C 635801A 702115D 709228FB 741528D NCV33072ADR2G

SC2902DTBR2G SC2903DR2G SC2903VDR2G LM258AYDT LM358SNG 430227FB 430228DB 460932C AZV831KTR-G1 409256CB

430232AB LM2904DR2GH LM358YDT LT1678IS8 042225DB 058184EB 070530X SC224DR2G SC239DR2G SC2902DG

SCYA5230DR2G 714228XB 714846BB 873836HB MIC918YC5-TR TS912BIYDT NCS2004MUTAG NCV33202DMR2G

M38510/13101BPA NTE925 SC2904DR2G SC358DR2G LM358EDR2G AZV358MTR-G1 AP4310AUMTR-AG1 HA1630D02MMEL-E

NJM358CG-TE2 HA1630S01LPEL-E LM324AWPT HA1630Q06TELL-E