2Gb (256M x 8) NAND flash + 2Gb(64M x 32) Low Power DDR2 SDRAM

# NAND MCP Specification 2Gb (256M x 8) NAND flash + 2Gb (64M x 32) Low Power DDR2 SDRAM

深圳市芯天下技术有限公司 XTX Technology Limited

Tel: (86 755) 28229862 Fax: (86 755) 28229847

Web Site: http://www.xtxtech.com/ Technical Contact: fae@xtxtech.com

\* Information furnished is believed to be accurate and reliable. However, XTX Technology Limited assumes no responsibility for the consequences of use of such information or for any infringement of patents of other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of XTX Technology Limited. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. XTX Technology Limited products are not authorized for use as critical components in life support devices or systems without express written approval of XTX Technology Limited. The XTX logo is a registered trademark of XTX Technology Limited. All other names are the property of their respective own.

# **Revision History:**

| Rev. | Date       | Changes                                 | Remark      |

|------|------------|-----------------------------------------|-------------|

| A1.0 | 2018/8/14  | Initial release                         | Preliminary |

| A1.1 | 2018/8/15  | Modify Plane size of NAND feature       | Preliminary |

| A1.2 | 2018/8/17  | Correct CK_t of NAND to CE#             | Preliminary |

| A1.3 | 2018/8/24  | Correct several diagrams                | Preliminary |

| A1.4 | 2019/3/24  | Correct several inaccurate descriptions | Preliminary |

| A1.5 | 2019/12/10 | Correct the unclear description         | Revise      |

# Introduction

XTX nMCP is a Multi-Chip Packaged memory which combines NAND flash memory and LPDDR2 (Low Power Double Data Rate) SDRAM. The NAND flash memory provides the most cost-effective solution for the non-volatile solid state mass storage market, while the LPDDR2 is an excellent solution for large volatile but fast storage applications such as random/temporary data access.

XTX nMCP is suitable for use in data memory of portable electronic devices to reduce its square size and power consumption at the same time. The NAND flash memory and LPDDR2 SDRAM in it could be operated individually .

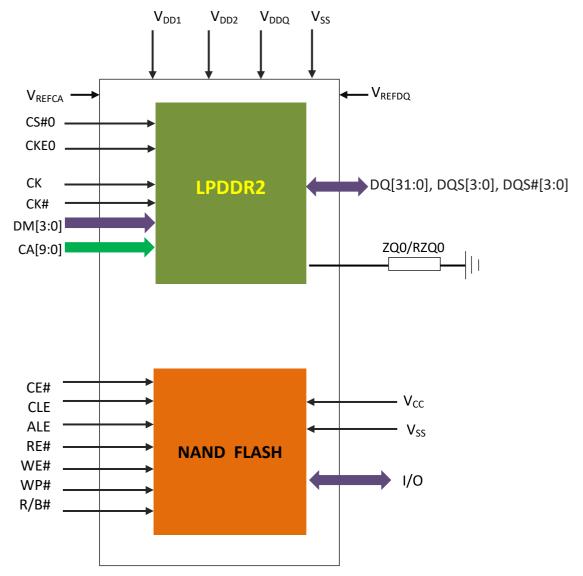

# **MCP Block Diagram**

## < NAND flash >

- Single Level per Cell (SLC) Technology

- **ECC requirement: 8bit/544Bytes**

- Power Supply Voltage Voltage range: 1.7V ~ 1.95V

#### > Organization

Page size: x8 (2048 + 128) bytes; 128- bytes spare area Block size: x8 (128k + 8k) bytes Plane size: 1024 Blocks per Plane 2008 block (min) ~2048 block (max)

#### > Modes

Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy , Multi Page Program, Multi Block Erase, Multi Page Copy, Multi Page Read

#### Access time

Cell array to register: 25µs (max) Serial Read Cycle: 25 ns (min) (CL=30pF)

#### Program/Erase time

Auto Page Program: 300 µs /page (typ.) Auto Block Erase: 3.5 ms/block( typ.)

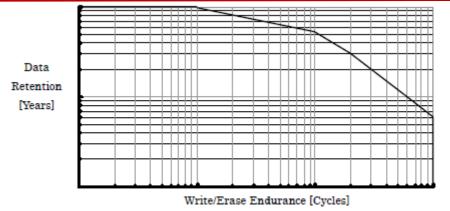

#### Reliability

10 Year Data retention (Typ)

# <LPDDR2>

# Specifications

- Density: 2G bits

- Organization

- × 32 bits: 8M words × 32 bits × 8 banks

- Power supply

- VDD1 = 1.70V to 1.95V

- VDD2, VDDCA, VDDQ = 1.14V to 1.30V

- Clock frequency: 533/466/400/333/266/200/166Mhz(max.)

- 2KB page size

- Row address: R0 to R13

- Column address:C0 to C8 (× 32 bits)

- Eight internal banks for concurrent operation

- Interface: LVCMOS

- Burst lengths (BL): 4, 8, 16

- Burst type (BT)

- Sequential (4, 8, 16)

- Interleave (4, 8)

- Read latency (RL): 3, 4, 5, 6, 7, 8

- Write latency (WL): 1, 2, 3, 4

- Pre-charge: auto pre-charge option for each

burst access

- Programmable driver strength

- Refresh: auto-refresh, self-refresh

- Refresh cycles: 16384 cycles/64ms

- Average refresh period: 3.9us

# **Features**

- DLL is not implemented

- Low power consumption

- JEDEC LPDDR2-S4B compliance

- Partial Array Self-Refresh (PASR)

Bank Masking

- Auto Temperature Compensated Self- Refresh (ATCSR) by built-in temperature sensor

- Deep power-down mode

- Double-data-rate architecture; two data transfers per one clock cycle

- The high-speed data transfer is realized by the 4 bits pre-fetch pipelined architecture

- Differential clock inputs (CK and /CK)

- Commands entered on both rising and falling CK edge; data and data mask referenced to both edges of DQS

- Data mask (DM) for write data

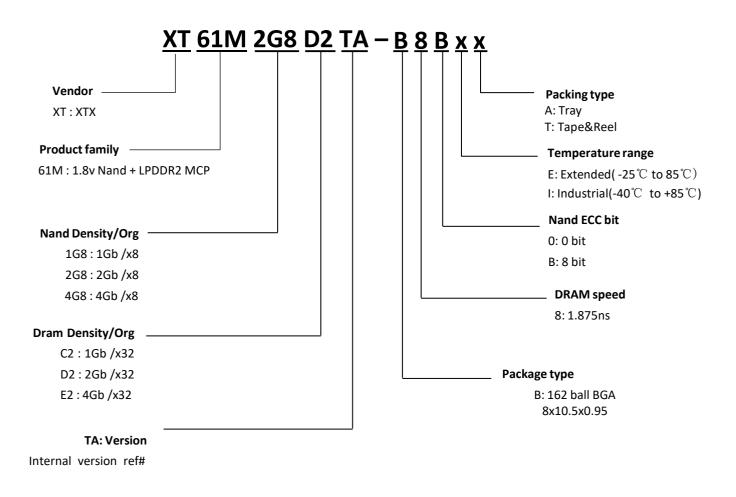

# **Ordering information**

|                    | NAND Flash     |       | Mobile DDR2                     | SDRAM    |                             | Operation            |  |

|--------------------|----------------|-------|---------------------------------|----------|-----------------------------|----------------------|--|

| Product ID         | Configuration  | Speed | Configuration                   | Speed    | Package                     | Temperature<br>Range |  |

| XT61M2G8D2TA-B8BEA | 2Gb (256M X 8) | 25ns  | 2Gb (8 Banks X<br>8M X 32 bits) | 1066Mbps | 162 ball BGA<br>8x10.5x0.95 | Extended             |  |

| XT61M2G8D2TA-B8BET | 2Gb (256M X 8) | 25ns  | 2Gb (8 Banks X<br>8M X 32 bits) | 1066Mbps | 162 ball BGA<br>8x10.5x0.95 | Extended             |  |

| XT61M2G8D2TA-B8BIA | 2Gb (256M X 8) | 25ns  | 2Gb (8 Banks X<br>8M X 32 bits) | 1066Mbps | 162 ball BGA<br>8x10.5x0.95 | Industrial           |  |

| XT61M2G8D2TA-B8BIT | 2Gb (256M X 8) | 25ns  | 2Gb (8 Banks X<br>8M X 32 bits) | 1066Mbps | 162 ball BGA<br>8x10.5x0.95 | Industrial           |  |

# Part number description

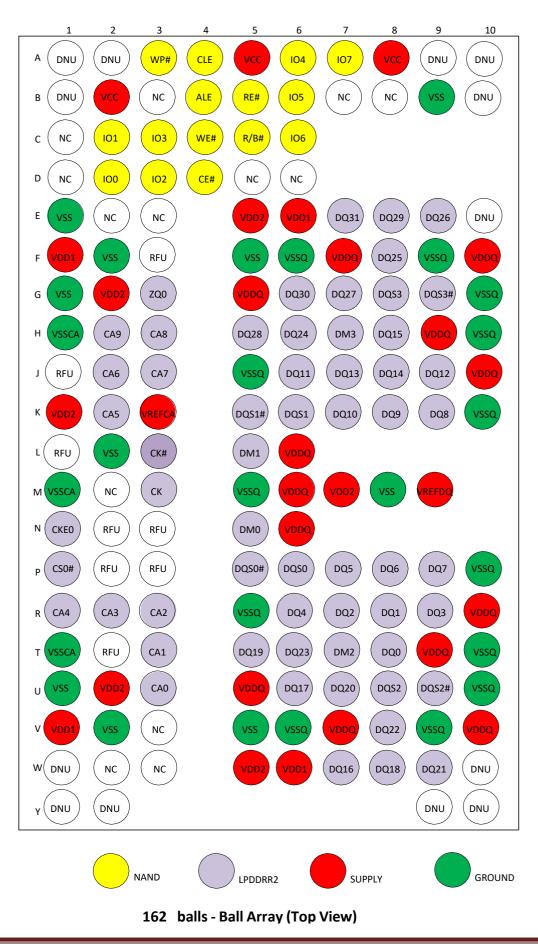

# **Pin Assignments**

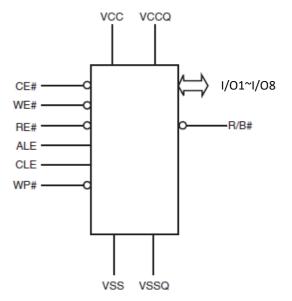

# Pin description

| Pin Name  | Туре         | Function                                                                                                                                                                              |

|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |              | NAND                                                                                                                                                                                  |

| VCC       | Supply       | Supply Voltage: The VCC supplies the power for all the operations (Read, Program, Erase).<br>An internal lock circuit ,prevents the insertion of Commands when VCC is less than VLKO. |

| VSS       | Supply       | Ground                                                                                                                                                                                |

| I/00-I/07 | Input/output | Data input/outputs: address inputs, or command inputs                                                                                                                                 |

| ALE       | Input        | Address Latch Enable: This input activates the latching of the I/O inputs inside the Address Register on the                                                                          |

| CLE       | Input        | Command Latch Enable: This input activates the latching of the I/O inputs inside the Command Register on                                                                              |

| CE#       | Input        | Chip Enable: This input controls the selection of the device. When the device is not busy CE# low selects                                                                             |

| RE#       | Input        | Read Enable: The RE# input is the serial data-out control, and when active drives the data onto the I/O bus.                                                                          |

| WE#       | Input        | Write Enable: This input latches Command, Address and Data. The I/O inputs are latched on the rising edge                                                                             |

| WP#       | Input        | Write Protect: The WP# pin, when low, provides hardware protection against undesired data modification                                                                                |

| R / B#    | Output       | Ready Busy: The Ready/Busy output is an Open Drain pin that signals the state of the memory.                                                                                          |

|                   |                | LP DDR2 SDRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

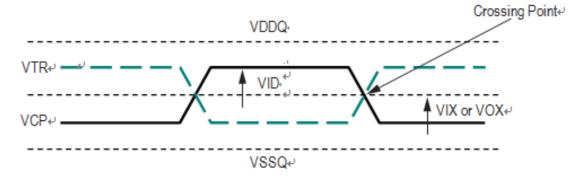

| СК, СК#           | Input          | Clock: CK and are differential clock inputs. All Double Data Rate (DDR) CA inputs are sampled<br>on both positive and negative edge of CK. Single Data Rate (SDR) inputs, CK# and CKE, are<br>sampled at the positive Clock edge. Clock is defined as the differential pair, CK and CK#.<br>The positive Clock edge .<br>Clock Enable: CKE high activates, and CKE low deactivates internal clock signals, and device<br>Input buffers and output drivers. Power saving modes are entered and exited through CKE<br>transitions. |

| CA0 – CA9         | Input          | Command/Address Inputs: Unidirectional command/address bus inputs. Provide the command and address inputs according to the command truth table. CA is considered part of the command code.                                                                                                                                                                                                                                                                                                                                       |

| DQ0-DQ31          | Input / Output | Data Bus: Bi-directional Input / Output data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DM0-DM3           | Input          | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS. Although DM pins are input-only, the DM loading matched the DQ and DQS. DM0 corresponds to the data on DQ0-DQ7, DM1 corresponds to the data on DQ8-DQ15, DM2, corresponds to the data on DQ16-DQ23, and DM3 corresponds to the data on DQ24-DQ31.                                                                            |

| DQS0~3<br>DQS#0~3 | Input / Output | Data Strobe (Bi-directional, Differential): The data strobe is bi-directional (used for read and write data) and Differential DQS ,t is output with read data and input with write data. DQS is edge-aligned to read data, and centered with write data.                                                                                                                                                                                                                                                                         |

| ZQ0               | Input          | Reference Pin for Output Drive Strength Calibration. External impedance (240-ohm): this signal is used to calibrate the device output impedance.                                                                                                                                                                                                                                                                                                                                                                                 |

| СКЕО              | Input          | Clock Enable: CKE high activates, and CKE low deactivates internal clock signals, and device<br>input buffers and output drivers. Power saving modes are entered and exited through CKE<br>transitions. CKE is considered part of the command code. CKE is sampled at the positive<br>Clock edge.                                                                                                                                                                                                                                |

| CS0#              | Input          | CS# enables (registered LOW) and disables (registered HIGH) the command decoder. All commands are masked when CS# is registered HIGH. CS# provides for external bank selection on systems with multiple banks. CS# is considered part of the command code.                                                                                                                                                                                                                                                                       |

| VDD1              | Supply         | VDD1: LPDDR2 power supply 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD2              | Supply         | VDD2: LPDDR2 power supply 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDDCA             | Supply         | VDDCA: LPDDR2 CA power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VDDQ              | Supply         | VDDQ: LPDDR2 I/O power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VREFCA            | Supply         | VREFCA: LPDDR2 reference for CA pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VREFDQ            | Supply         | VREFDQ: LPDDR2 reference for DQ pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VSSCA             | Supply         | VSSCA: LPDDR2 I/O ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VSSQ              | Supply         | VSSQ: LPDDR2 I/O ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### NOTES:

**DNU** – Do not use: Must be grounded or left floating.

NC – No connect: Not internally connected.

**RFU** – Reserved for future use.

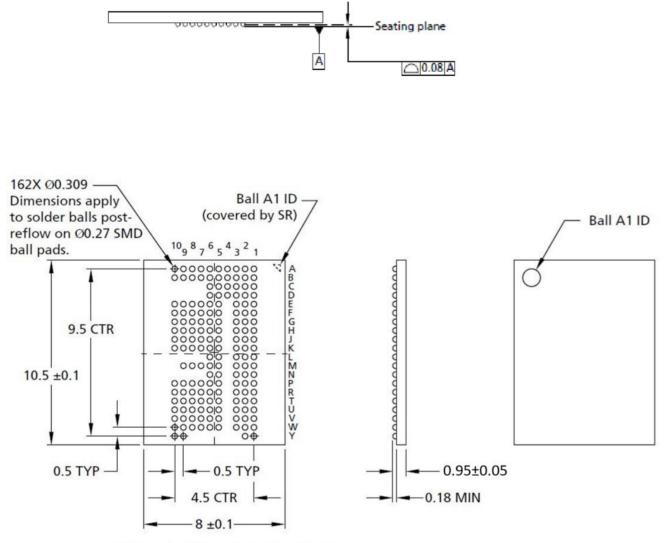

Package Dimension 8x10.5 package

Notes: 1. All dimensions are in millimeters.

# Content

| 1.NANC | ) Flash I        | Vlemory                                                                       | 13 |

|--------|------------------|-------------------------------------------------------------------------------|----|

| 1.1.   | Genera           | Description                                                                   | 14 |

| 1.2.   | Logic Di         | agram                                                                         | 14 |

| 1.3.   | Block D          | iagram                                                                        | 15 |

| 1.4.   | Array O          | rganization                                                                   | 16 |

| 1.5.   | Address          |                                                                               | 16 |

| 1.6.   | Absolut          | e Maximum Ratings                                                             | 17 |

| 1.7.   | Capacit          | ance *(Ta = 25°C, f = 1 MHz)                                                  | 17 |

|        |                  | ocks                                                                          |    |

|        |                  | nended DC Operating Conditions                                                |    |

|        |                  | racteristics (Ta = -40 to $85^{\circ}$ , VCC = 1.7 to 1.95V )                 |    |

|        |                  | Conditions                                                                    |    |

|        |                  | nming and Erasing Characteristics                                             |    |

|        | -                | itput                                                                         |    |

|        |                  | election                                                                      |    |

|        |                  | Operation                                                                     |    |

|        |                  | Diagrams                                                                      |    |

|        | -                | tion Notes and Comments                                                       |    |

|        |                  |                                                                               |    |

| •      |                  | DR2 SDRAM Part                                                                |    |

|        |                  | Description                                                                   |    |

| 2.2    |                  | al Specifications:                                                            |    |

|        | 2.2.1            | Absolute Maximum Ratings                                                      |    |

|        | 2.2.2            | Operating Temperature Condition                                               |    |

|        | 2.2.3<br>2.2.4   | Recommended DC Operating Conditions                                           |    |

|        | 2.2.4            | AC and DC Input Measurement Levels<br>DC Characteristics 1                    |    |

|        | 2.2.5            | Advanced Data Retention Current (Self - refresh current)                      |    |

|        | 2.2.0            | DC Characteristics 2                                                          |    |

|        | 2.2.8            | DC Characteristics 3                                                          |    |

|        | 2.2.9            | Pin Capacitance                                                               |    |

|        | 2.2.10           | Refresh Requirement Parameters (2Gb)                                          | 83 |

|        | 2.2.11           | AC Characteristics                                                            | 84 |

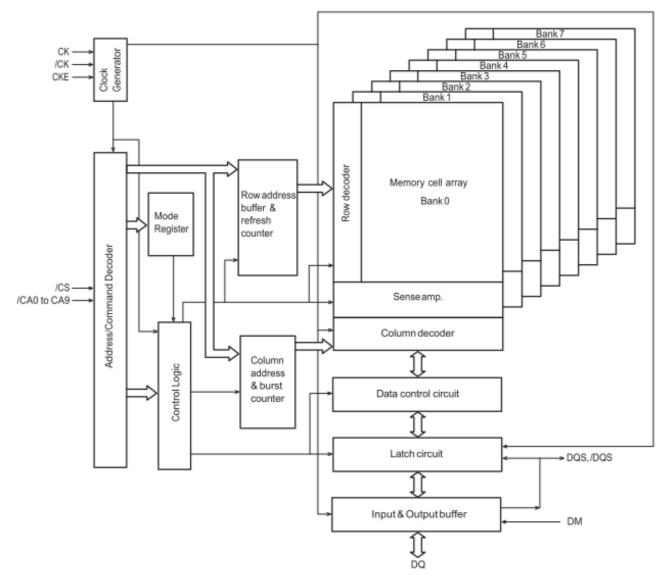

| 2.3    | Block Di         | agram                                                                         | 89 |

| 2.4    | Pin Fun          | ction                                                                         | 89 |

|        | 2.4.1            | CK, /CK (input pins)                                                          |    |

|        | 2.4.2            | /CS (input pin)                                                               |    |

|        | 2.4.3            | CAO to CA9 (input pins)                                                       |    |

|        | 2.4.4            | [Addressing Table]                                                            |    |

|        | 2.4.5            | [Bank Numbering and BA Input Table]                                           |    |

|        | 2.4.6            | CKE (input pin)                                                               |    |

|        | 2.4.7            | DQ0 to DQ15 (x16), DQ0 to DQ31 (x32) - (input/output pins)                    |    |

|        | 2.4.8<br>2.4.9   | DQSx, /DQSx (input/ output pins, where x = 0 to 3)<br>DM0 to DM3 (input pins) |    |

|        | 2.4.9            | [DM truth table]                                                              |    |

|        | 2.4.10           | [DQS and DM Correspondence Table]                                             |    |

|        | 2.4.12           | VDD1, VSS, VSS2, VDDCA, VSSCA, VDDQ, VSSQ (power supply)                      |    |

| 2.4    |                  | nd Operation                                                                  |    |

|        | 2.4.1            | Command Truth Table                                                           |    |

|        | 2.4.2            | Register Commands [MRR/MRW]                                                   | 93 |

|        | 2.4.3            | Refresh Commands [REF]                                                        | 93 |

|        | 2.4.4            | Active Command [ACT]                                                          |    |

|        | 2.4.5            | Read/Write Commands [READ/WRIT]                                               |    |

|        | 2.4.6            | Precharge Commands [PRE]                                                      |    |

|        | 2.4.7            | Burst Terminate Command [BST]                                                 |    |

|        | 2.4.8            | Power - down and Deep Power Down [PDEN/DPDEN]                                 |    |

|        | 2.4.9            | Exit Command [PDEX, DPDX, SELFX]                                              |    |

|        | 2.4.10<br>2.4.11 | No Operation Command [NOP]<br>CKE Truth Table                                 |    |

| 2 ⊑    |                  |                                                                               |    |

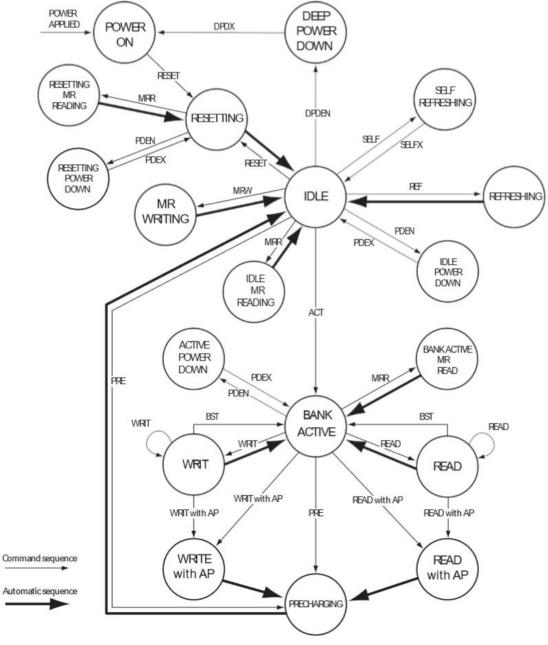

|        | -                | ed State Diagram                                                              |    |

| 2.6    | •                | on of the LPDDR2 RAM                                                          |    |

|        | 2.6.1            | LPDDR2 RAM Power - On and Initialization Sequence                             | 96 |

# 2Gb (256M x 8) NAND flash + 2Gb(64M x 32) Low Power DDR2 SDRAM

| 2.6.2  | Programming the Mode Register                             | 97  |

|--------|-----------------------------------------------------------|-----|

| 2.6.3  | Bank Activate Command [ACT]                               |     |

| 2.6.4  | Read and Write Access Modes                               |     |

| 2.6.5  | Burst Mode Operation                                      |     |

| 2.6.6  | Burst Read Command [READ]                                 |     |

| 2.6.7  | Burst Write Command [WRIT]                                |     |

| 2.6.8  | Write Data Mask                                           |     |

| 2.6.9  | Precharge Command [PRE]                                   |     |

| 2.6.10 | Burst Read Operation Followed by Precharge                |     |

| 2.6.11 | Burst Write Operation Followed by Precharge               |     |

| 2.6.12 | Auto Precharge Operation                                  |     |

| 2.6.13 | Burst Read with Auto Precharge                            |     |

| 2.6.14 | Burst Write with Auto Precharge                           |     |

| 2.6.15 | The Burst Terminate [BST]                                 |     |

| 2.6.16 | Refresh Command [REF]                                     |     |

| 2.6.17 | Self - Refresh [SELF]                                     |     |

| 2.6.18 | Mode Register Read Command                                |     |

| 2.6.19 | Mode Register Write Command                               | 110 |

| 2.6.20 | Power - Down [PDEN]                                       | 110 |

| 2.6.21 | Deep Power - Down [DPDEN]                                 | 111 |

| 2.6.22 | Input Clock Stop and Frequency Change during Power - Down |     |

| 2.6.23 | Clock Stop                                                |     |

| 2.6.24 | No Operation Command [NOP]                                |     |

| 2.6.25 | Deselect Command [DESL]                                   |     |

|        |                                                           |     |

# **1.NAND Flash Memory**

## **1.1. General Description**

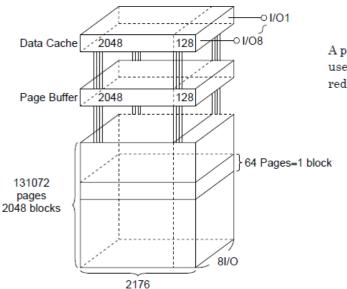

The NAND is a single 1.8v 2Gbit NAND Electrically Erasable and Programmable Read-Only Memory (NAND E2PROM) organized as (2048 + 128) bytes × 64 pages × 2048 blocks. The device has two 2176-byte static registers which allow program and read data to be transferred between the register and the memory cell array in 2176-byte increments. The Erase operation is implemented in a single block unit (128 Kbytes + 8 Kbytes: 2176 bytes × 64 pages).

The NAND is a serial-type memory device which utilizes the I/O pins for both address and data input/output as well as for command inputs. The Erase and Program operations are automatically executed making the device most suitable for applications such as solid-state file storage, voice recording, image file memory for still cameras and other systems which require high-density non-volatile memory data storage.

## 1.2. Logic Diagram

# 1.3. Block Diagram

# 1.4. Array Organization

#### Schematic Cell Layout and Address Assignment

The Program operation works on page units while the Erase operation works on block units.

A page consists of 2176 bytes in which 2048 bytes are used for main memory storage and 128 bytes are for redundancy or for other uses.

1 page = 2176 bytes

1 block = 2176 bytes × 64 pages = (128K + 8K) bytes Capacity = 2176 bytes × 64pages × 2048 blocks

An address is read in via the I/O port over five consecutive clock cycles, as shown in Table 1.

## 1.5. Addressing

|              | I/O8 | I/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 |

|--------------|------|------|------|------|------|------|------|------|

| First cycle  | CA7  | CA6  | CA5  | CA4  | CA3  | CA2  | CA1  | CA0  |

| Second cycle | L    | L    | L    | L    | CA11 | CA10 | CA9  | CA8  |

| Third cycle  | PA7  | PA6  | PA5  | PA4  | PA3  | PA2  | PA1  | PA0  |

| Fourth cycle | PA15 | PA14 | PA13 | PA12 | PA11 | PA10 | PA9  | PA8  |

| Fifth cycle  | L    | L    | L    | L    | L    | L    | L    | PA16 |

CA0 to CA11: Column address PA0 to PA16: Page address PA6 to PA16: Block address PA0 to PA5: NAND address in block

# **1.6.** Absolute Maximum Ratings

| SYMBOL              | RATING                       | VALUE                                   | UNIT |

|---------------------|------------------------------|-----------------------------------------|------|

| V <sub>CC</sub>     | Power Supply Voltage         | -0.6 to 2.5                             | V    |

| V <sub>IN</sub>     | Input Voltage                | -0.6 to 2.5                             | V    |

| V <sub>I/O</sub>    | Input /Output Voltage        | –0.6 to V <sub>CC</sub> + 0.3 (≤ 2.5 V) | V    |

| PD                  | Power Dissipation            | 0.3                                     | W    |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s) | 260                                     | °C   |

| T <sub>STG</sub>    | Storage Temperature          | -55 to 150                              | °C   |

| T <sub>OPR</sub>    | Operating Temperature        | -40 to 85                               | °C   |

# 1.7. Capacitance \*(Ta = 25°C, f = 1 MHz)

| SYMB0L           | PARAMETER | CONDITION              | MIN | MAX | UNIT |

|------------------|-----------|------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input     | VIN = 0 V              | _   | 10  | pF   |

| C <sub>OUT</sub> | Output    | V <sub>OUT</sub> = 0 V |     | 10  | pF   |

\* This parameter is periodically sampled and is not tested for every device.

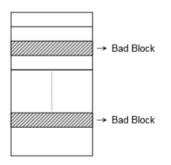

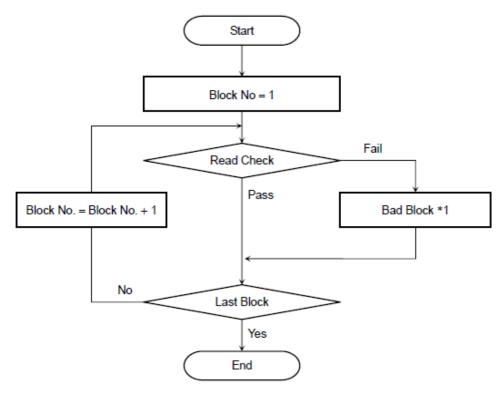

## 1.8. Valid Blocks

| SYMBOL          | PARAMETER              | MIN  | TYP. | MAX  | UNIT   |

|-----------------|------------------------|------|------|------|--------|

| N <sub>VB</sub> | Number of Valid Blocks | 2008 | _    | 2048 | Blocks |

NOTE: The device occasionally contains unusable blocks. Refer to Application Note (13) toward the end of this document.

The first block (Block 0) is guaranteed to be a valid block at the time of shipment.

The specification for the minimum number of valid blocks is applicable over lifetime.

The number of valid blocks is on the basis of single plane operations, and this may be decreased with two plane operations.

# 1.9. Recommended DC Operating Conditions

| SYMBOL          | PARAMETER                | MIN       | TYP. | МАХ                   | UNIT |

|-----------------|--------------------------|-----------|------|-----------------------|------|

| V <sub>CC</sub> | Power Supply Voltage     | 1.7       | _    | 1.95                  | V    |

| VIH             | High Level input Voltage | Vcc x 0.8 | _    | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> | Low Level Input Voltage  | -0.3*     | _    | Vcc x 0.2             | V    |

\* -2 V (pulse width lower than 20 ns)

# 1.10. DC Characteristics (Ta = -40 to 85 $^\circ C$ , VCC = 1.7 to 1.95V )

| SYMBOL                     | PARAMETER                   | CONDITION                                                       | MIN       | TYP. | MAX | UNIT |

|----------------------------|-----------------------------|-----------------------------------------------------------------|-----------|------|-----|------|

| ۱ <sub>IL</sub>            | Input Leakage Current       | V <sub>IN</sub> = 0 V to V <sub>CC</sub>                        | —         | _    | ±10 | μA   |

| ILO                        | Output Leakage Current      | V <sub>OUT</sub> = 0 V to V <sub>CC</sub>                       | _         |      | ±10 | μA   |

| I <sub>CCO1</sub>          | Serial Read Current         | $CE\# = VIL$ , $I_{OUT} = 0$ mA, tcycle = 25 ns                 | _         | _    | 30  | mA   |

| I <sub>CCO2</sub>          | Programming Current         | _                                                               | _         | _    | 30  | mA   |

| I <sub>CCO3</sub>          | Erasing Current             | —                                                               | _         |      | 30  | mA   |

| I <sub>CCS</sub>           | Standby Current             | $CE\# = V_{CC}-0.2 \text{ V}, \text{WP}\# = 0 \text{ V/V}_{CC}$ | —         |      | 50  | μA   |

| V <sub>OH</sub>            | High Level Output Voltage   | Iон = -0.1 mA                                                   | Vcc – 0.2 | _    | _   | V    |

| V <sub>OL</sub>            | Low Level Output Voltage    | I <sub>OL</sub> = 0.1 mA                                        | _         | _    | 0.2 | V    |

| I <sub>OL</sub><br>(RY/BY) | Output current of RY/BY pin | V <sub>OL</sub> = 0.2 V                                         | _         | 4    | _   | mA   |

# AC CHARACTERISTICS AND RECOMMENDED OPERATING

| YMBOL             | PARAMETER                                             | MIN      | МАХ        | UNIT |

|-------------------|-------------------------------------------------------|----------|------------|------|

| t <sub>CLS</sub>  | CLE Setup Time                                        | 12       | _          | ns   |

| <sup>t</sup> CLH  | CLE Hold Time                                         | 5        | —          | ns   |

| t <sub>CS</sub>   | CE# Setup Time                                        | 20       | —          | ns   |

| t <sub>CH</sub>   | CE# Hold Time                                         | 5        | —          | ns   |

| t <sub>WP</sub>   | Write Pulse Width                                     | 12       | —          | ns   |

| t <sub>ALS</sub>  | ALE Setup Time                                        | 12       | —          | ns   |

| t <sub>ALH</sub>  | ALE Hold Time                                         | 5        | —          | ns   |

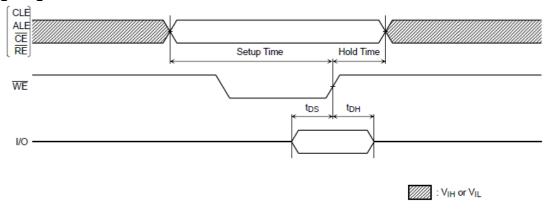

| t <sub>DS</sub>   | Data Setup Time                                       | 12       | —          | ns   |

| t <sub>DH</sub>   | Data Hold Time                                        | 5        | —          | ns   |

| t <sub>WC</sub>   | Write Cycle Time                                      | 25       | —          | ns   |

| twн               | WE# High Hold Time                                    | 10       | —          | ns   |

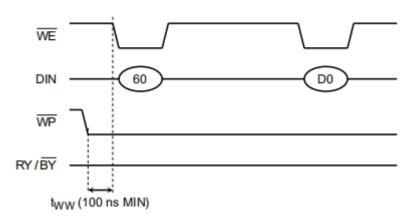

| tww               | WP# High to WE# Low                                   | 100      | —          | ns   |

| t <sub>RR</sub>   | Ready to RE# Falling Edge                             | 20       | —          | ns   |

| t <sub>RW</sub>   | Ready to WE# Falling Edge                             | 20       | —          | ns   |

| t <sub>RP</sub>   | Read Pulse Width                                      | 12       | —          | ns   |

| t <sub>RC</sub>   | Read Cycle Time                                       | 25       | —          | ns   |

| t <sub>REA</sub>  | RE# Access Time                                       | —        | 20         | ns   |

| tCEA              | CE# Access Time                                       | _        | 25         | ns   |

| tCLR              | CLE Low to RE# Low                                    | 10       | —          | ns   |

| t <sub>AR</sub>   | ALE Low to RE# Low                                    | 10       | _          | ns   |

| t <sub>RHOH</sub> | RE# High to Output Hold Time                          | 25       | _          | ns   |

| t <sub>RLOH</sub> | RE# Low to Output Hold Time                           | 5        | —          | ns   |

| t <sub>RHZ</sub>  | RE# High to Output High Impedance                     | —        | 60         | ns   |

| t <sub>CHZ</sub>  | CE# High to Output High Impedance                     | _        | 20         | ns   |

| tCSD              | CE# High to ALE or CLE Don't Care                     | 0        | —          | ns   |

| t <sub>REH</sub>  | RE# High Hold Time                                    | 10       | —          | ns   |

| t <sub>IR</sub>   | Output-High-impedance-to- RE# Falling Edge            | 0        | —          | ns   |

| t <sub>RHW</sub>  | RE# High to WE# Low                                   | 30       | —          | ns   |

| tWHC              | WE# High to CE# Low                                   | 30       | —          | ns   |

| <sup>t</sup> WHR  | WE# High to RE# Low                                   | 60       | —          | ns   |

| tR                | Memory Cell Array to Starting Address                 | —        | 25         | μs   |

| tDCBSYR1          | Data Cache Busy in Read Cache (following 31h and 3Fh) | _        | 25         | μs   |

| tDCBSYR2          | Data Cache Busy in Page Copy (following 3Ah)          | <u> </u> | 30         | μs   |

| t <sub>WB</sub>   | WE# High to Busy                                      | _        | 100        | ns   |

| t <sub>RST</sub>  | Device Reset Time (Ready/Read/Program/Erase)          |          | 5/5/10/500 | μs   |

\*1: tCLS and tALS can not be shorter than tWP \*2: tCS should be longer than tWP + 8ns.

# **1.11. AC Test Conditions**

| PARAMETER                      | CONDITION                      |  |  |  |  |

|--------------------------------|--------------------------------|--|--|--|--|

| FARAMETER                      | V <sub>CC</sub> : 1.7 to 1.95V |  |  |  |  |

| Input level                    | V <sub>CC</sub> – 0.2 V, 0.2 V |  |  |  |  |

| Input pulse rise and fall time | 3 ns                           |  |  |  |  |

| Input comparison level         | Vcc / 2                        |  |  |  |  |

| Output data comparison level   | Vcc / 2                        |  |  |  |  |

| Output load                    | C <sub>L</sub> (30 pF) + 1 TTL |  |  |  |  |

Note: Busy to ready time depends on the pull-up resistor tied to the RY/BY# pin.

## 1.12. Programming and Erasing Characteristics

#### (Ta = -40 to 85°C, V<sub>CC</sub> = 1.7 to 1.95V)

| SYMBOL               | PARAMETER                                           | MIN | TYP. | MAX | UNIT | NOTES |

|----------------------|-----------------------------------------------------|-----|------|-----|------|-------|

| t <sub>PROG</sub>    | Average Programming Time                            | _   | 300  | 700 | μs   |       |

| t <sub>DCBSYW1</sub> | Data Cache Busy Time in Write Cache (following 11h) | _   | _    | 10  | μs   |       |

| t <sub>DCBSYW2</sub> | Data Cache Busy Time in Write Cache (following 15h) |     |      | 700 | μs   | (2)   |

| Ν                    | Number of Partial Program Cycles in the Same Page   | _   | _    | 4   |      | (1)   |

| t <sub>BERASE</sub>  | Block Erasing Time                                  |     | 3.5  | 10  | ms   |       |

(1) Refer to Application Note (12) toward the end of this document.

(2) tDCBSYW2 depends on the timing between internal programming time and data in time.

# 1.13. Data Output

When tREH is long, output buffers are disabled by /RE=High, and the hold time of data output depend on tRHOH (25ns MIN). On this condition, waveforms look like normal serial read mode.

When tREH is short, output buffers are not disabled by /RE=High, and the hold time of data output depend on tRLOH (5ns MIN). On this condition, output buffers are disabled by the rising edge of CLE, ALE, /CE or falling edge of /WE, and waveforms look like Extended Data Output Mode.

## 1.14. Mode Selection

The operation modes such as Program, Erase, Read and Reset are controlled by command operations shown in Table 3. Address input, command input and data input/output are controlled by the CLE, ALE, /CE, /WE, /RE and /WP signals as shown in Table 2.

## Table 2. Logic Table

|                        | CLE | ALE | CE | WE     | RE     | WP <sup>*1</sup>    |

|------------------------|-----|-----|----|--------|--------|---------------------|

| Command Input          | Н   | L   | L  |        | н      | *                   |

| Data Input             | L   | L   | L  |        | н      | н                   |

| Address input          | L   | н   | L  |        | н      | *                   |

| Serial Data Output     | L   | L   | L  | н      | ₹      | *                   |

| During Program (Busy)  | *   | *   | *  | *      | *      | н                   |

| During Erase (Busy)    | *   | *   | *  | *      | *      | н                   |

| During Dand (Busy)     | *   | *   | н  | *      | *      | *                   |

| During Read (Busy)     | *   | *   | L  | H (*2) | H (*2) | *                   |

| Program, Erase Inhibit | *   | *   | *  | *      | *      | L                   |

| Standby                | *   | *   | Н  | *      | *      | 0 V/V <sub>CC</sub> |

H: VIH, L: VIL, \*: VIH or VIL

1. \*1: Refer to Application Note (10) toward the end of this document regarding the WP signal when Program or Erase Inhibit

2. \*2 :If CE is low during read busy, WE and RE must be held High to avoid unintended command/address input to the device or read to device. Reset or Status Read command can be input during Read Busy.

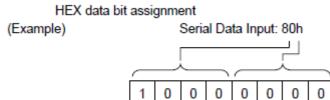

# Table 3. Command table (HEX)

|                                                         | First Cycle | Second Cycle | Acceptable while Busy |

|---------------------------------------------------------|-------------|--------------|-----------------------|

| Serial Data Input                                       | 80          | —            |                       |

| Read                                                    | 00          | 30           |                       |

| Column Address Change in Serial Data Output             | 05          | E0           |                       |

| Read with Data Cache                                    | 31          | _            |                       |

| Read Start for Last Page in Read Cycle with Data Cache  | 3F          | —            |                       |

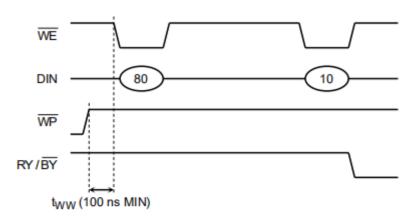

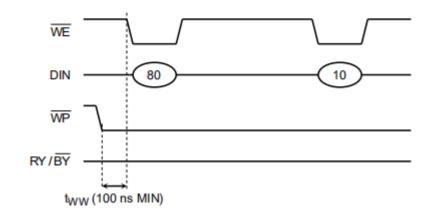

| Auto Page Program                                       | 80          | 10           |                       |

| Column Address Change in Serial Data Input              | 85          | _            |                       |

| Auto Program with Data Cache                            | 80          | 15           |                       |

|                                                         | 80          | 11           |                       |

| Multi Page Program                                      | 81          | 15           |                       |

|                                                         | 81          | 10           |                       |

| Read for Page Copy (2) with Data Out                    | 00          | ЗA           |                       |

| Auto Program with Data Cache during Page Copy (2)       | 8C          | 15           |                       |

| Auto Program for last page during Page Copy (2)         | 8C          | 10           |                       |

| Auto Block Erase                                        | 60          | D0           |                       |

| ID Read                                                 | 90          | —            |                       |

| Status Read                                             | 70          | —            | 0                     |

| Status Read for Multi-Page Program or Multi Block Erase | 71          | _            | ٥                     |

| Reset                                                   | FF          | —            | ٥                     |

# Table 4. Read mode operation states

|                 | CLE | ALE | CE | WE | RE | I/O1 to I/O8   | Power  |

|-----------------|-----|-----|----|----|----|----------------|--------|

| Output select   | L   | L   | L  | н  | L  | Data output    | Active |

| Output Deselect | L   | L   | L  | Н  | Н  | High impedance | Active |

5 4 3

2 1/01

6

H: VIH, L: VIL

## **1.15.** Device Operation

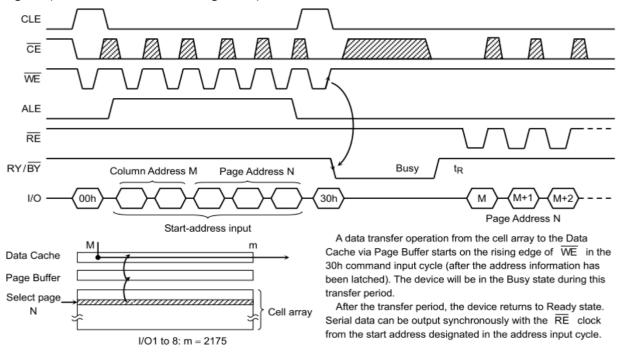

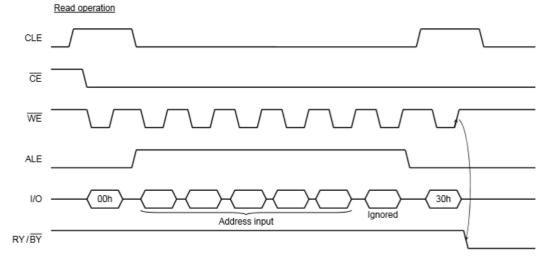

#### **Read Mode**

Read mode is set when the "00h" and "30h" commands are issued to the Command register. Between the two commands, a start address for the Read mode needs to be issued.. Refer to the figures below for the sequence and the block diagram (Refer to the detailed timing chart.).

XT61M2G8D2TA-B8Bxx

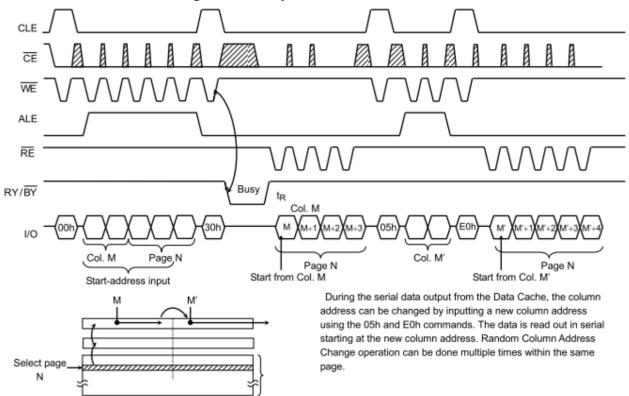

Random Column Address Change in Read Cycle

#### **Read Operation with Read Cache**

The device has a Read operation with Data Cache that enables the high speed read operation shown below. When the block address changes, this sequence has to be started from the beginning.

If the 31h command is issued to the device, the data content of the next page is transferred to the Page Buffer during serial data out from the Data Cache, and therefore the tR (Data transfer from memory cell to data register) will be reduced.

1. Normal read. Data is transferred from Page N to Data Cache through Page Buffer. During this time period, the device outputs Busy state for tR max.

2. After the Ready/Busy returns to Ready, 31h command is issued and data is transferred to Data Cache from Page Buffer again. This data transfer takes tDCBSYR1 max and the completion of this time period can be detected by Ready/Busy signal.

3. Data of Page N + 1 is transferred to Page Buffer from cell while the data of Page N in Data cache can be read out by /RE clock simultaneously.

The 31h command makes data of Page N + 1 transfer to Data Cache from Page Buffer after the completion of the transfer from cell to Page Buffer. The device outputs Busy state for tDCBSYR1 max. This Busy period depends on the combination of the internal data transfer time from cell to Page buffer and the serial data out time.

Data of Page N + 2 is transferred to Page Buffer from cell while the data of Page N + 1 in Data cache can be read out by /RE clock simultaneously

The 3Fh command makes the data of Page N + 2 transfer to the Data Cache from the Page Buffer after the completion of the transfer from cell to Page Buffer. The device outputs Busy state for tDCBSYR1 max. This Busy period depends on the combination of the internal data transfer time from cell to Page buffer and the serial data out time.

Data of Page N + 2 in Data Cache can be read out, but since the 3Fh command does not transfer the data from the memory cell to Page Buffer, the device can accept new command input immediately after the completion of serial data out.

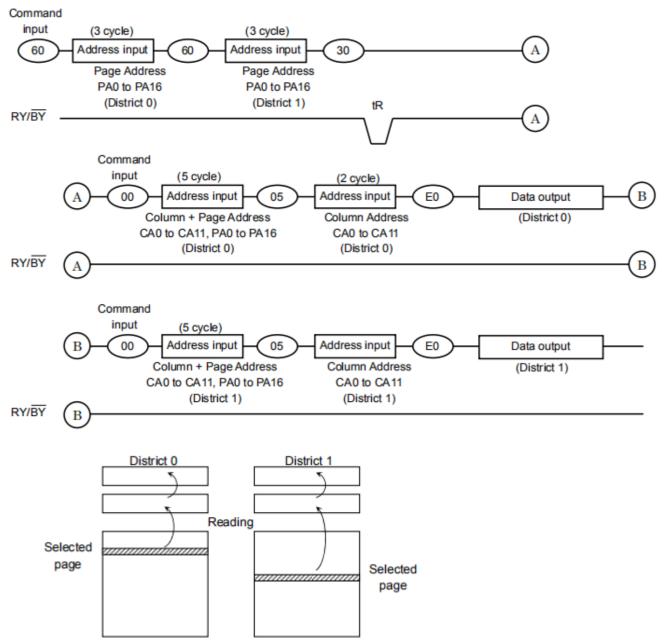

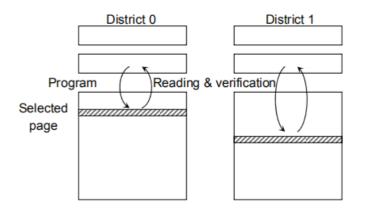

#### Multi Page Read Operation

The device has a Multi Page Read operation and Multi Page Read with Data Cache operation.

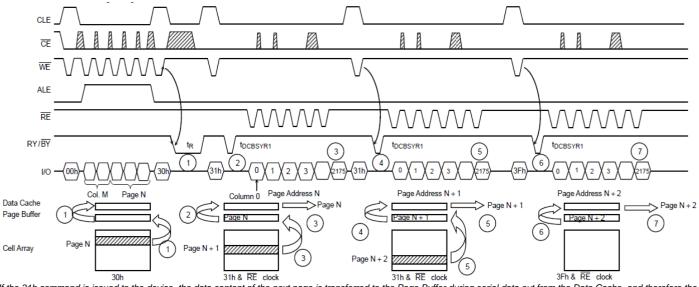

#### (1) Multi Page Read without Data Cache

The sequence of command and address input is shown below.

Same page address (PAO to PA5) within each district has to be selected.

The data transfer operation from the cell array to the Data Cache via Page Buffer starts on the rising edge of  $\overline{\text{WE}}$  in the 30h command input cycle (after the 2 Districts address information has been latched). The device will be in the Busy state during this transfer period.

After the transfer period, the device returns to Ready state. Serial data can be output synchronously with the  $\overline{RE}$  clock from the start address designated in the address input cycle.

(2) Multi Page Read with Data Cache

When the block address changes (increments) this sequenced has to be started from the beginning.

The sequence of command and address input is shown below.

Same page address (PAO to PA5) within each district has to be selected.

(a) Internal addressing in relation with the Districts

To use Multi Page Read operation, the internal addressing should be considered in relation with the District.

- The device consists from 2 Districts.

- Each District consists from 1024 erase blocks.

- The allocation rule is follows.

District 0: Block 0, Block 2, Block 4, Block 6,..., Block 2046 District 1: Block 1, Block 3, Block 5, Block 7,..., Block 2047

(b) Address input restriction for the Multi Page Read operation There are following restrictions in using Multi Page Read;

(Restriction)

Maximum one block should be selected from each District. Same page address (PA0 to PA5) within two districts has to be selected.

For example;

(60) [District 0, Page Address 0x00000] (60) [District 1, Page Address 0x00040] (30)

(60) [District 0, Page Address 0x00001] (60) [District 1, Page Address 0x00041] (30)

(Acceptance)

There is no order limitation of the District for the address input.

For example, following operation is accepted;

(60) [District 0] (60) [District 1] (30)

(60) [District 1] (60) [District 0] (30)

It requires no mutual address relation between the selected blocks from each District.

(c) /WP signal Make sure /WP is held to High level when Multi Page Read operation is performed

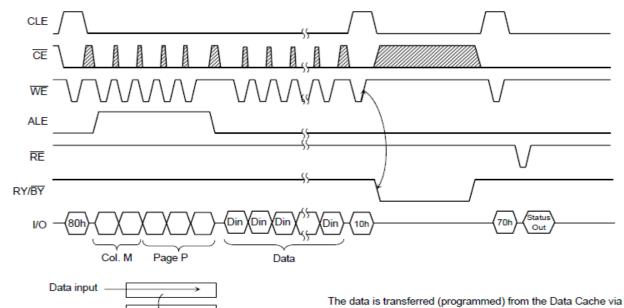

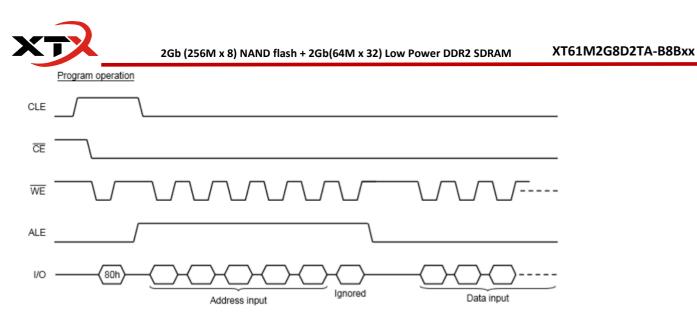

#### Auto Page Program Operation

The device carries out an Automatic Page Program operation when it receives a "10h" Program command after the address and data have been input. The sequence of command, address and data input is shown below. (Refer to the detailed timing chart.)

The data is transferred (programmed) from the Data Cache via the Page Buffer to the selected page on the rising edge of  $\overline{WE}$ following input of the "10h" command. After programming, the programmed data is transferred back to the Page Buffer to be automatically verified by the device. If the programming does not succeed, the Program/Verify operation is repeated by the device until success is achieved or until the maximum loop number set in the device is reached.

#### Random Column Address Change in Auto Page Program Operation

The column address can be changed by the 85h command during the data input sequence of the Auto Page Program operation.

Two address input cycles after the 85h command are recognized as a new column address for the data input. After the new data is input to the new column address, the 10h command initiates the actual data program into the selected page automatically. The Random Column Address Change operation can be repeated multiple times within the same page.

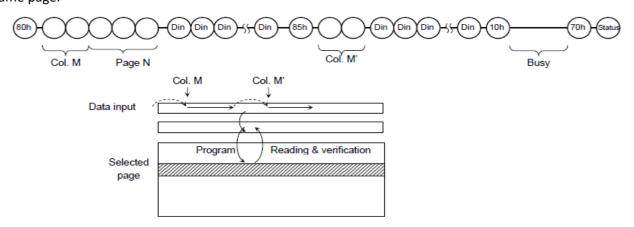

#### **Multi Page Program**

The device has a Multi Page Program, which enables even higher speed program operation compared to Auto Page Program. The sequence of command, address and data input is shown bellow. (Refer to the detailed timing chart.)

Although two planes are programmed simultaneously, pass/fail is not available for each page when the program operation completes. Status bit of I/O 0 is set to "1" when any of the pages fails. Limitation in addressing with Multi Page Program is shown below.

#### Multi Page Program

NOTE: Any command between 11h and 81h is prohibited except 70h and FFh.

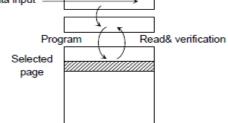

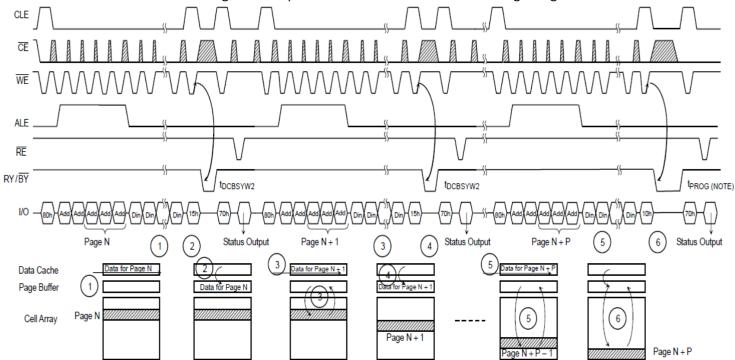

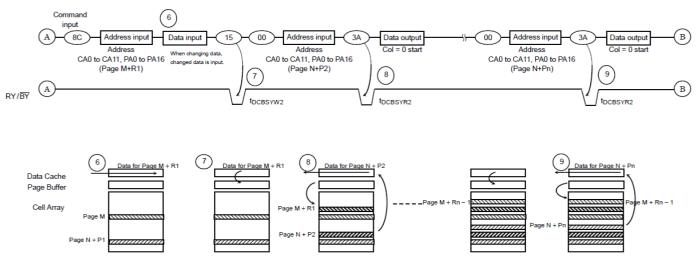

# Auto Page Program Operation with Data Cache

The device has an Auto Page Program with Data Cache operation enabling the high speed program operation shown below. When the block address changes this sequenced has to be started from the beginning

Issuing the 15h command to the device after serial data input initiates the program operation with Data Cache

- 1. Data for Page N is input to Data Cache.

- 2. Data is transferred to the Page Buffer by the 15h command. During the transfer the Ready/Busy outputs Busy State (tDCBSYW2).

- 3. Data is programmed to the selected page while the data for page N + 1 is input to the Data Cache.

- 4. By the 15h command, the data in the Data Cache is transferred to the Page Buffer after the programming of page N is completed. The device output busy state from the 15h command until the Data Cache becomes empty. The duration of this period depends on timing between the internal programming of page N and serial data input for Page N + 1 (tDCBSYW2).

- 5. Data for Page N + P is input to the Data Cache while the data of the Page N + P -1 is being programmed.

- 6. The programming with Data Cache is terminated by the 10h command. When the device becomes Ready, it shows that the internal programming of the Page N + P is completed.

NOTE: Since the last page programming by the 10h command is initiated after the previous cache program, the tPROG during cache programming is given by the following;

tPROG = tPROG for the last page + tPROG of the previous page – ( command input cycle + address input cycle + data input cycle time of the last page)

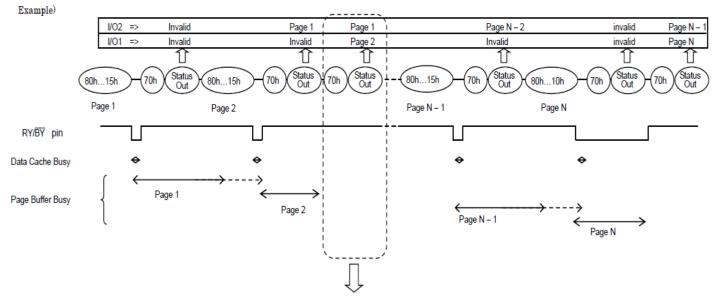

Pass/fail status for each page programmed by the Auto Page Programming with Data Cache operation can be detected by the Status Read operation.

. I/O1 : Pass/fail of the current page program operation.

. I/O2 : Pass/fail of the previous page program operation.

The Pass/Fail status on I/O1 and I/O2 are valid under the following conditions.

. Status on I/O1: Page Buffer Ready/Busy is Ready State.

The Page Buffer Ready/Busy is output on I/O6 by Status Read operation or RY / BY pin after the 10h command . Status on I/O2: Data Cache Read/Busy is Ready State.

The Data Cache Ready/Busy is output on I/O7 by Status Read operation or RY / BY pin after the 15h command.

If the Page Buffer Busy returns to Ready before the next 80h command input, and if Status Read is done during this Ready period, the Status Read provides pass/fail for Page 2 on I/O1 and pass/fail result for Page1 on I/O2

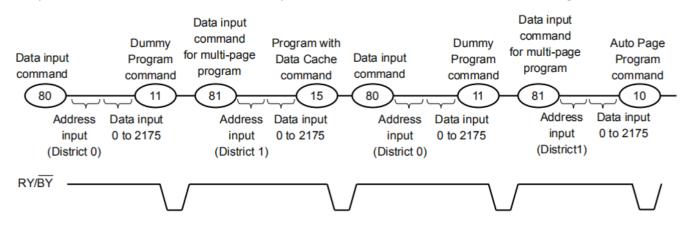

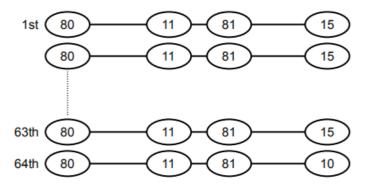

#### Multi Page Program with Data Cache

The device has a Multi Page Program with Data Cache operation, which enables even higher speed program operation compared to Auto Page Program with Data Cache as shown below. When the block address change(increments) this sequenced has to be started from the beginning.

The sequence of command, address and data input is shown below. (Refer to the detailed timing chart.)

After "15h" or "10h" Program command is input to device, physical programing starts as follows. For details of Auto Program with Data Cache, refer to "Auto Page Program with Data Cache".

The data is transferred (programmed) from the page buffer to the selected page on the rising edge of /WE following input of the "15h" or "10h" command. After programming, the programmed data is transferred back to the register to be automatically verified by the device. If the programming does not succeed, the Program/Verify operation is repeated by the device until success is achieved or until the maximum loop number set in the device is reached.

Starting the above operation from 1st page of the selected erase blocks, and then repeating the operation total 64 times with incrementing the page address in the blocks, and then input the last page data of the blocks, "10h" command executes final programming. Make sure to terminate with 81h-10h- command sequence. In this full sequence, the command sequence is following.

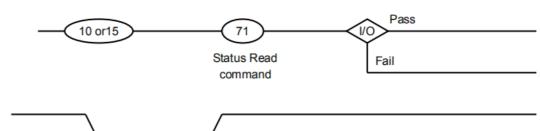

After the "15h" or "10h" command, the results of the above operation is shown through the "71h" Status Read

RY/BY

The 71h command Status description is as below.

|      | STATUS                              | OU         | TPUT           |

|------|-------------------------------------|------------|----------------|

| I/O1 | Chip Status1 : Pass/Fail            | Pass: 0    | Fail: 1        |

| I/O2 | District 0 Chip Status1 : Pass/Fail | Pass: 0    | Fail: 1        |

| I/O3 | District 1 Chip Status1 : Pass/Fail | Pass: 0    | Fail: 1        |

| I/O4 | District 0 Chip Status2 : Pass/Fail | Pass: 0    | Fail: 1        |

| I/O5 | District 1 Chip Status2 : Pass/Fail | Pass: 0    | Fail: 1        |

| I/O6 | Ready/Busy                          | Ready: 1   | Busy: 0        |

| 1/07 | Data Cache Ready/Busy               | Ready: 1   | Busy: 0        |

| I/O8 | Write Protect                       | Protect: 0 | Not Protect: 1 |

I/O1 describes Pass/Fail condition of district 0 and 1(OR data of I/O2 and I/O3). If one of the districts fails during multi page program operation, it shows "Fail".

I/O2 to 5 shows the Pass/Fail condition of each district. For details on "Chip Status1" and "Chip Status2", refer to section "Status Read".

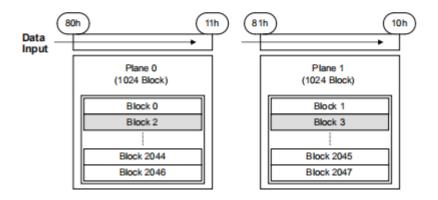

#### Internal addressing in relation with the Districts

To use Multi Page Program operation, the internal addressing should be considered in relation with the District.

• The device consists from 2 Districts.

• Each District consists from 1024 erase blocks.

• The allocation rule is follows.

District 0: Block 0, Block 2, Block 4, Block 6,..., Block 2046

District 1: Block 1, Block 3, Block 5, Block 7,..., Block 2047

#### Address input restriction for the Multi Page Program with Data Cache operation

There are following restrictions in using Multi Page Program with Data Cache;

(Restriction)

Maximum one block should be selected from each District.

Same page address (PA0 to PA5) within two districts has to be selected.

For example;

(80) [District 0, Page Address 0x00000] (11) (81) [District 1, Page Address 0x00040] (15 or 10)

(80) [District 0, Page Address 0x00001] (11) (81) [District 1, Page Address 0x00041] (15 or 10) (Acceptance)

There is no order limitation of the District for the address input.

For example, following operation is accepted;

(80) [District 0] (11) (81) [District 1] (15 or 10)

(80) [District 1] (11) (81) [District 0] (15 or 10)

It requires no mutual address relation between the selected blocks from each District.

#### Operating restriction during the Multi Page Program with Data Cache operation

(Restriction)

The operation has to be terminated with "10h" command.

Once the operation is started, no commands other than the commands shown in the timing diagram is allowed

to be input except for Status Read command and reset command

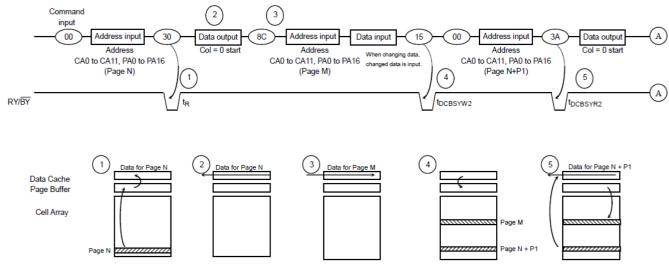

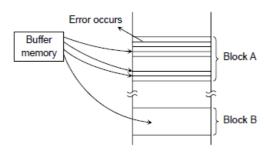

## Page Copy (2)

By using Page Copy (2), data in a page can be copied to another page after the data has been read out. When the block address changes (increments) this sequenced has to be started from the beginning.

#### Page Copy (2) operation is as following.

- 1. Data for Page N is transferred to the Data Cache.

- 2. Data for Page N is read out.

- 3. Copy Page address M is input and if the data needs to be changed, changed data is input.

- 4. Data Cache for Page M is transferred to the Page Buffer.

- 5. After the Ready state, Data for Page N + P1 is output from the Data Cache while the data of Page M is being programmed.

6. Copy Page address (M + R1) is input and if the data needs to be changed, changed data is input.

7. After programming of page M is completed, Data Cache for Page M + R1 is transferred to the Page Buffer.

- 8. By the 15h command, the data in the Page Buffer is programmed to Page M + R1. Data for Page N + P2 is transferred to the Data cache.

- 9. The data in the Page Buffer is programmed to Page M + Rn 1. Data for Page N + Pn is transferred to the Data Cache.

- 10. Copy Page address (M + Rn) is input and if the data needs to be changed, changed data is input.

- 11. By issuing the 10h command, the data in the Page Buffer is programmed to Page M + Rn.

(\*1) Since the last page programming by the 10h command is initiated after the previous cache program, the tPROG here will be expected as the following,

tPROG = tPROG of the last page + tPROG of the previous page - ( command input cycle + address input cycle + data output/input cycle time of the last page)

#### NOTE)

Data input is required only if previous data output needs to be altered.

If the data has to be changed, locate the desired address with the column and page address input after the 8Ch command, and change only the data that needs be changed.

If the data does not have to be changed, data input cycles are not required.

Make sure WP# is held to High level when Page Copy (2) operation is performed.

Also make sure the Page Copy operation is terminated with 8Ch-10h command sequence

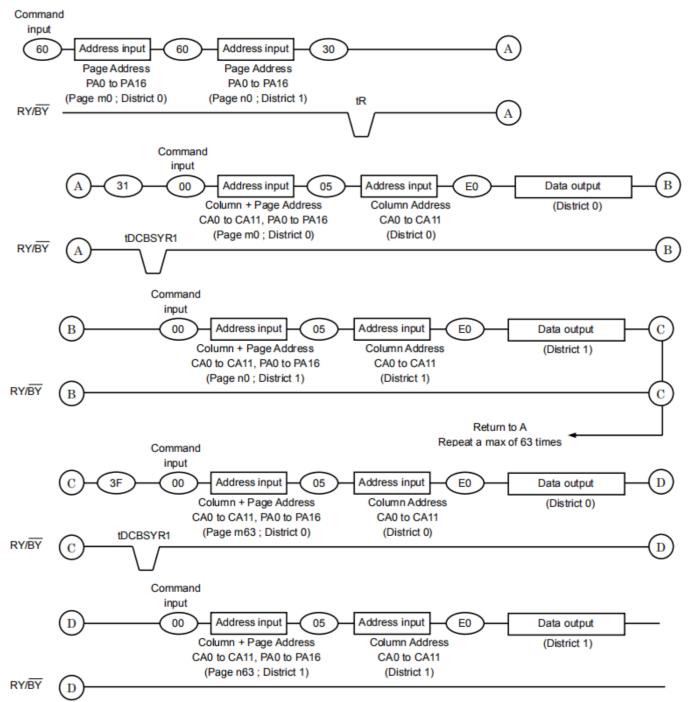

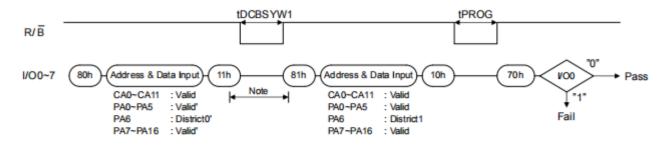

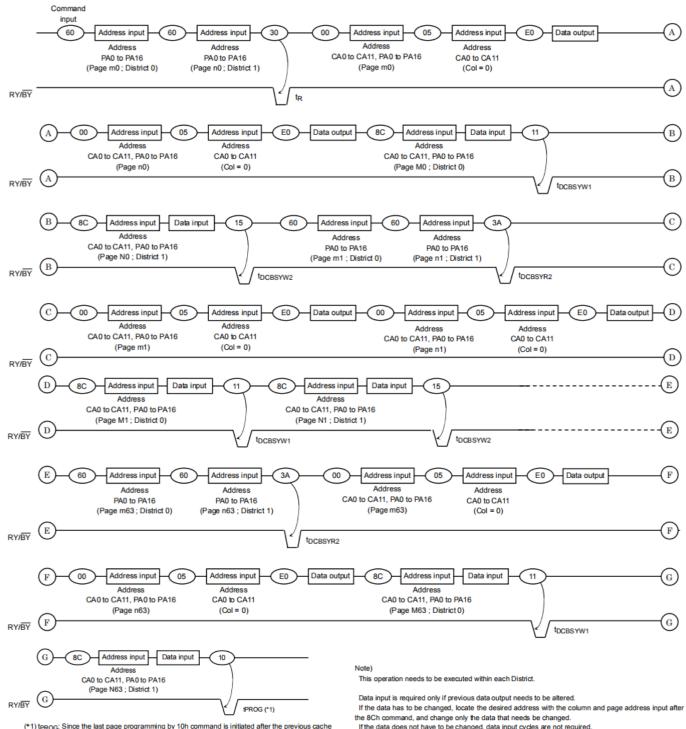

## Multi Page Copy (2)

By using Multi Page Copy (2), data in two pages can be copied to another pages after the data has been read out. When the each block address changes (increments) this sequenced has to be started from the beginning. Same page address (PA0 to PA5) within two districts has to be selected.

program, the tPROG+ during cache programming is given by the following equation.

tPROG = tPROG of the last page + tPROG of the previous page-A

A = (command input cycle + address input cycle + data output/input cycle time of the last page) If "A" exceeds the tpROG of previous page, tpROG of the last page is tpROG max.

If the data does not have to be changed, data input cycles are not required.

Make sure WP is held to High level when Multi Page Copy (2) operation is performed Also make sure the Multi Page Copy operation is terminated with 8Ch-10h command sequence

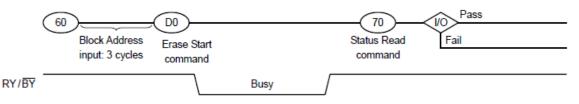

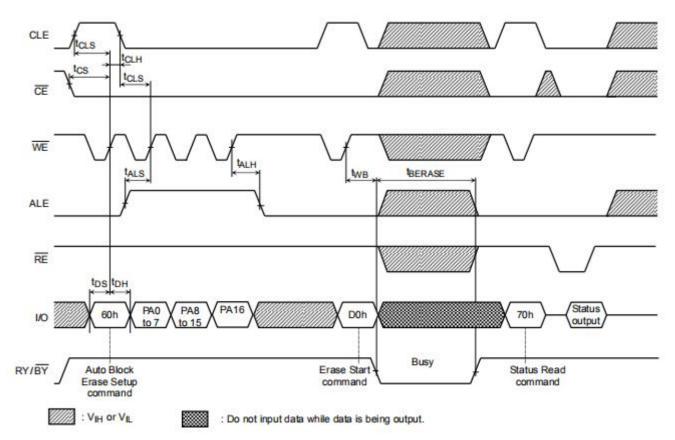

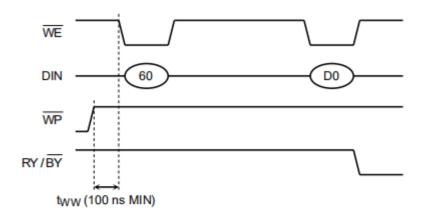

## **Auto Block Erase**

The Auto Block Erase operation starts on the rising edge of WE# after the Erase Start command "D0h" which follows the Erase Setup command "60h". This two-cycle process for Erase operations acts as an extra layer of protection from accidental erasure of data due to external noise. The device automatically executes the Erase and Verify operations.

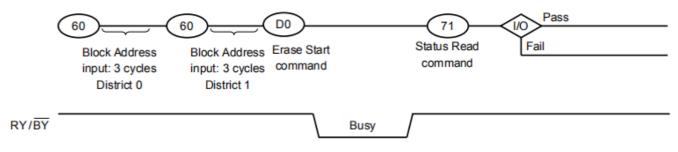

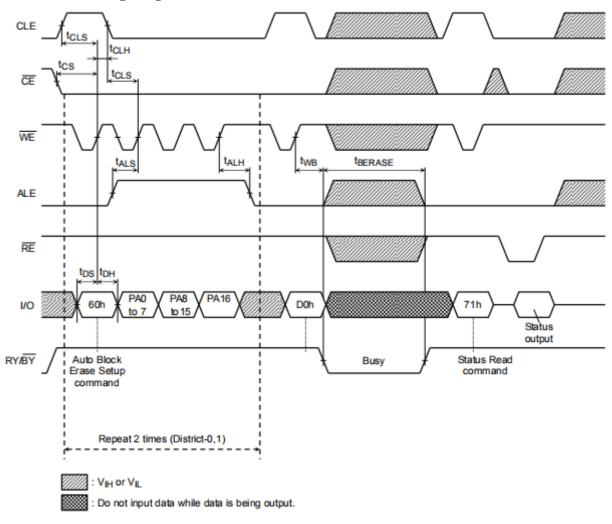

## **Multi Block Erase**

The Multi Block Erase operation starts by selecting two block addresses before D0h command as in below diagram. The device automatically executes the Erase and Verify operations and the result can be monitored by checking the status by 71h status read command. For details on 71h status read command, refer to section "Multi Page Program with Data Cache".

### Internal addressing in relation with the Districts

To use Multi Block Erase operation, the internal addressing should be considered in relation with the District.

- The device consists from 2 Districts.

- Each District consists from 1024 erase blocks.

- The allocation rule is follows.

District 0: Block 0, Block 2, Block 4, Block 6,..., Block 2046

District 1: Block 1, Block 3, Block 5, Block 7,..., Block 2047

# Address input restriction for the Multi Block Erase

There are following restrictions in using Multi Block Erase (Restriction) Maximum one block should be selected from each District.

For example; (60) [District 0] (60) [District 1] (D0) (Acceptance)

There is no order limitation of the District for the address input.

For example, following operation is accepted;

(60) [District 1] (60) [District 0] (D0)

It requires no mutual address relation between the selected blocks from each District.

Make sure to terminate the operation with D0h command. If the operation needs to be terminated before D0h command input, input the FFh reset command to terminate the operation.

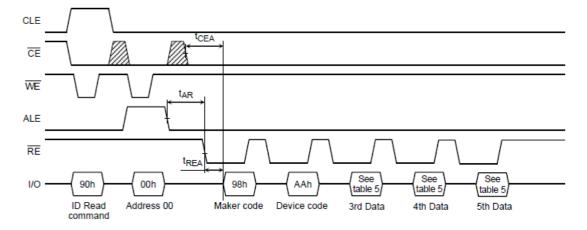

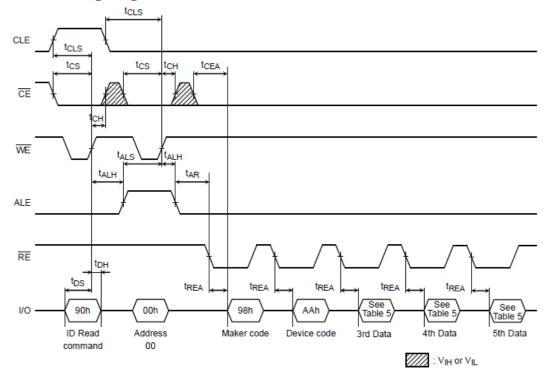

### ID Read

The device contains ID codes which can be used to identify the device type, the manufacturer, and features of the device. The ID codes can be read out under the following timing conditions:

### Table 5. Code table

|          | Description                         | I/O8 | I/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | Hex Data |

|----------|-------------------------------------|------|------|------|------|------|------|------|------|----------|

| 1st Data | Maker Code                          | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 98h      |

| 2nd Data | Device Code                         | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | AAh      |

| 3rd Data | Chip Number, Cell Type              | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 90h      |

| 4th Data | Page Size, Block Size,<br>I/O Width | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 15h      |

| 5th Data | Plane Number                        | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 76h      |

| Jata                 |                                                               |      |      |      |      |                  |                  |                  |                  |

|----------------------|---------------------------------------------------------------|------|------|------|------|------------------|------------------|------------------|------------------|

|                      | Description                                                   | I/O8 | I/07 | I/O6 | I/O5 | I/O4             | I/O3             | I/O2             | <b>I/</b> 01     |

| Internal Chip Number | 1<br>2<br>4<br>8                                              |      |      |      |      |                  |                  | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |

| Cell Type            | 2 level cell<br>4 level cell<br>8 level cell<br>16 level cell |      |      |      |      | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |                  |                  |

| Reserved             |                                                               | 1    | 0    | 0    | 1    |                  |                  |                  |                  |

### 4th Data

|                          | Description | I/O8 | I/07   | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 |

|--------------------------|-------------|------|--------|------|------|------|------|------|------|

| Page Size                | 1 KB        |      |        |      |      |      |      | 0    | 0    |

|                          | 2 KB        |      |        |      |      |      |      | 0    | 1    |

| (without redundant area) | 4 KB        |      |        |      |      |      |      | 1    | 0    |

|                          | 8 KB        |      |        |      |      |      |      | 1    | 1    |

| Block Size               | 64 KB       |      |        | 0    | 0    |      |      |      |      |

|                          | 128 KB      |      |        | 0    | 1    |      |      |      |      |

| (without redundant area) | 256 KB      |      |        | 1    | 0    |      |      |      |      |

|                          | 512 KB      |      |        | 1    | 1    |      |      |      |      |

| I/O Width                | x8<br>x16   |      | 0<br>1 |      |      |      |      |      |      |

| Reserved                 |             | 0    |        |      |      | 0    | 1    |      |      |

### 5th Data

|              | Description                              | I/O8 | I/07 | I/O6 | I/O5 | I/O4             | I/O3             | I/O2 | I/O1 |

|--------------|------------------------------------------|------|------|------|------|------------------|------------------|------|------|

| Plane Number | 1 Plane<br>2 Plane<br>4 Plane<br>8 Plane |      |      |      |      | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |      |      |

| Reserved     |                                          | 0    | 1    | 1    | 1    |                  |                  | 1    | 0    |

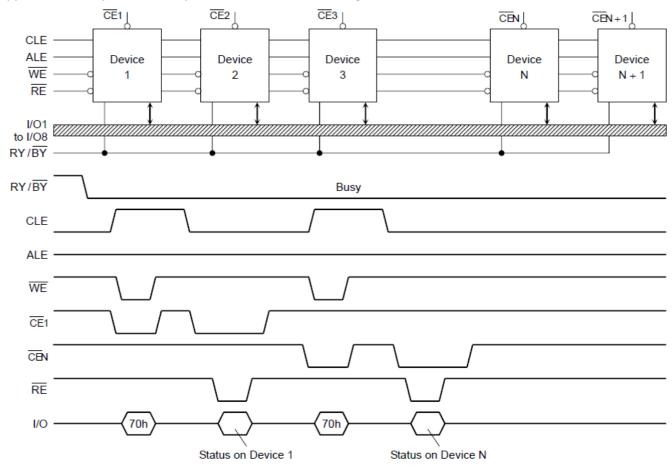

### Status Read

The device automatically implements the execution and verification of the Program and Erase operations. The Status Read function is used to monitor the Ready/Busy status of the device, determine the result (pass /fail) of a Program or Erase operation, and determine whether the device is in Protect mode. The device status is output via the I/O port using RE# after a "70h" command input. The Status Read can also be used during a Read operation to find out the Ready/Busy status.

The resulting information is outlined in Table 6.

## Table 6. Status output table

|      | Definition                                     | Page Program<br>Block Erase | Cache Program | Read<br>Cache Read |

|------|------------------------------------------------|-----------------------------|---------------|--------------------|

| I/O1 | Chip Status1<br>Pass: 0 Fail: 1                | Pass/Fail                   | Pass/Fail     | Invalid            |

| I/O2 | Chip Status 2<br>Pass: 0 Fail: 1               | Invalid                     | Pass/Fail     | Invalid            |

| I/O3 | Not Used                                       | 0                           | 0             | 0                  |

| I/O4 | Not Used                                       | 0                           | 0             | 0                  |

| I/O5 | Not Used                                       | 0                           | 0             | 0                  |

| I/O6 | Page Buffer Ready/Busy<br>Ready: 1 Busy: 0     | Ready/Busy                  | Ready/Busy    | Ready/Busy         |

| 1/07 | Data Cache Ready/Busy<br>Ready: 1 Busy: 0      | Ready/Busy                  | Ready/Busy    | Ready/Busy         |

| I/O8 | Write Protect<br>Not Protected :1 Protected: 0 | Write Protect               | Write Protect | Write Protect      |

The Pass/Fail status on I/O1 and I/O2 is only valid during a Program/Erase operation when the device is in the Ready state.

Chip Status 1:

During a Auto Page Program or Auto Block Erase operation this bit indicates the pass/fail result.

During a Auto Page Programming with Data Cache operation, this bit shows the pass/fail results of the current page program operation, and therefore this bit is only valid when I/O6 shows the Ready state.

Chip Status 2:

This bit shows the pass/fail result of the previous page program operation during Auto Page Programming with Data Cache. This status is valid when I/O7 shows the Ready State.

The status output on the I/O6 is the same as that of I/O7 if the command input just before the 70h is not 15h or 31h.

## 2Gb (256M x 8) NAND flash + 2Gb(64M x 32) Low Power DDR2 SDRAM

XT61M2G8D2TA-B8Bxx

An application example with multiple devices is shown in the figure below.

System Design Note: If the RY / BY# pin signals from multiple devices are wired together as shown in the diagram, the Status Read function can be used to determine the status of each individual device.

Rev A1.5

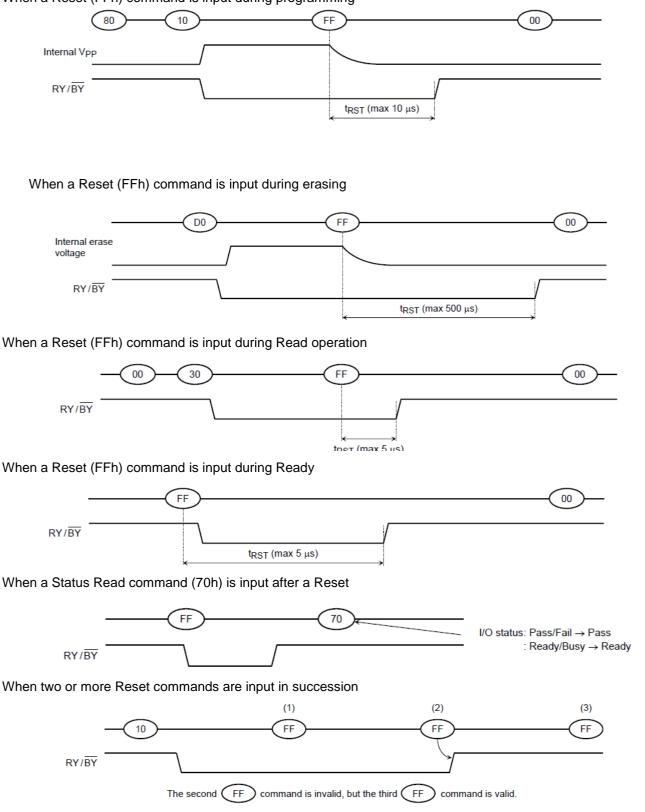

### Reset

The Reset mode stops all operations. For example, in case of a Program or Erase operation, the internally generated voltage is discharged to 0 volt and the device enters the Wait state.

Reset during a Cache Program/Page Copy may not just stop the most recent page program but it may also stop the previous program to a page depending on when the FF reset is input.

The response to a "FFh" Reset command input during the various device operations is as follows:

When a Reset (FFh) command is input during programming

# 1.16. Timing Diagrams

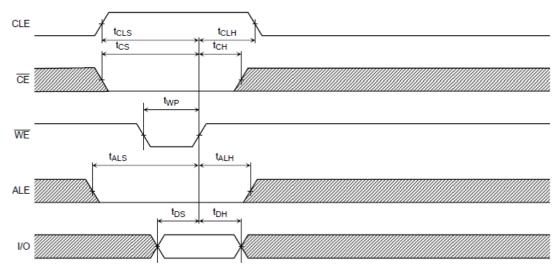

## Latch Timing Diagram for Command/Address/Data

# **Command Input Cycle Timing Diagram**

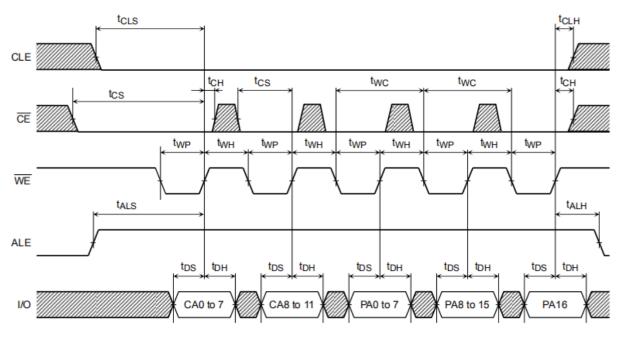

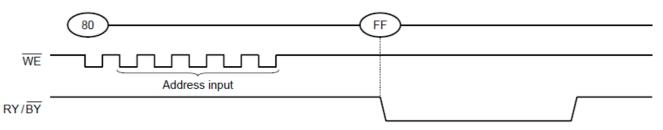

# Address Input Cycle Timing Diagram

: VIH or VIL

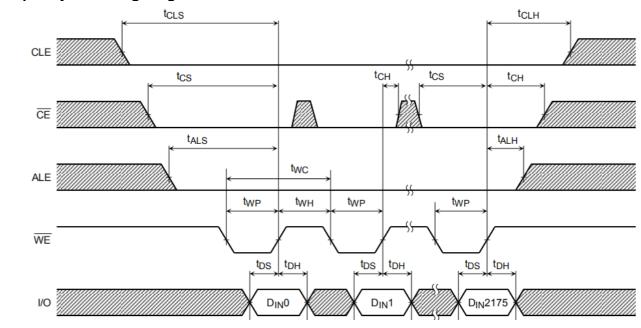

## Data Input Cycle Timing Diagram

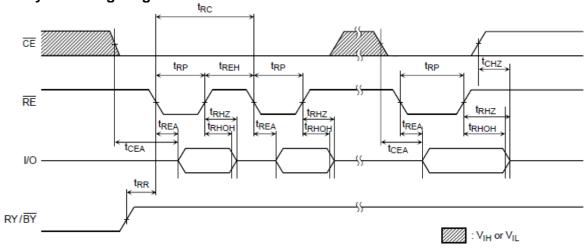

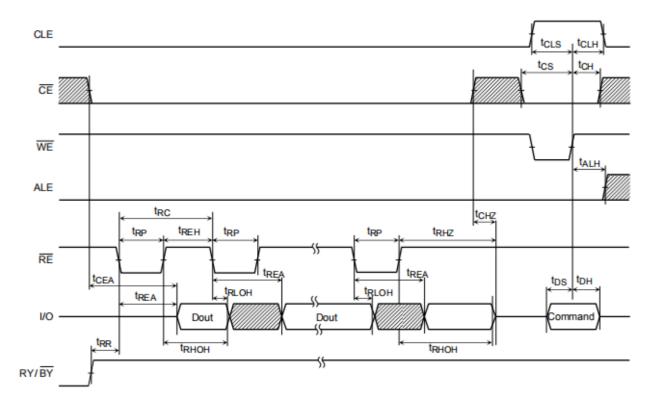

# Serial Read Cycle Timing Diagram

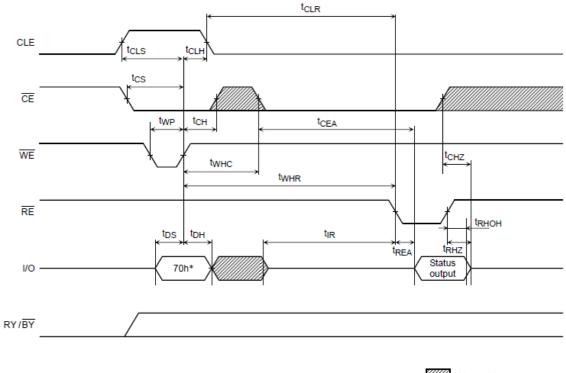

# Status Read Cycle Timing Diagram

\*: 70h represents the hexadecimal number

: VIH or VIL

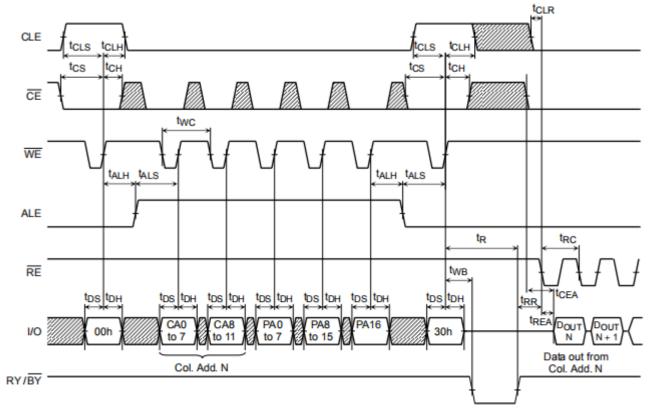

# Read Cycle Timing Diagram

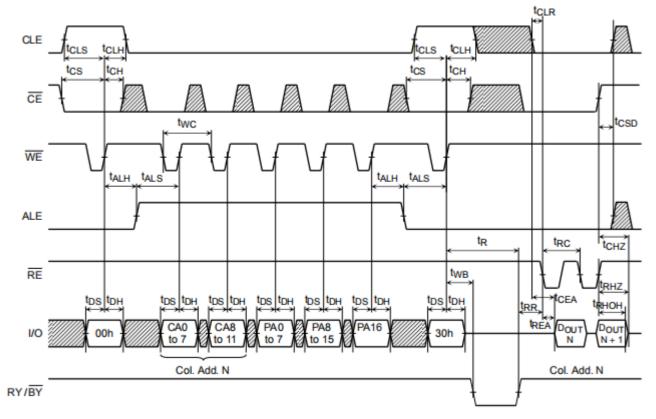

# Read Cycle Timing Diagram: When Interrupted by /CE

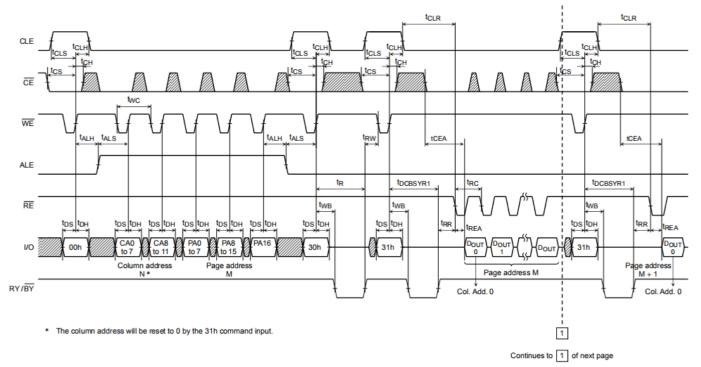

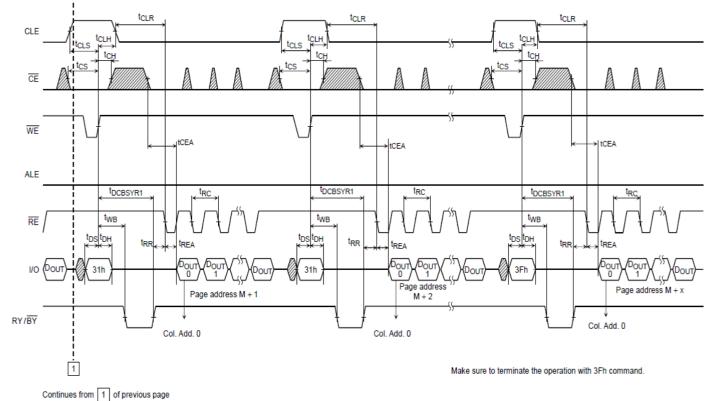

# Read Cycle with Data Cache Timing Diagram (1/2)

Read Cycle with Data Cache Timing Diagram (2/2)

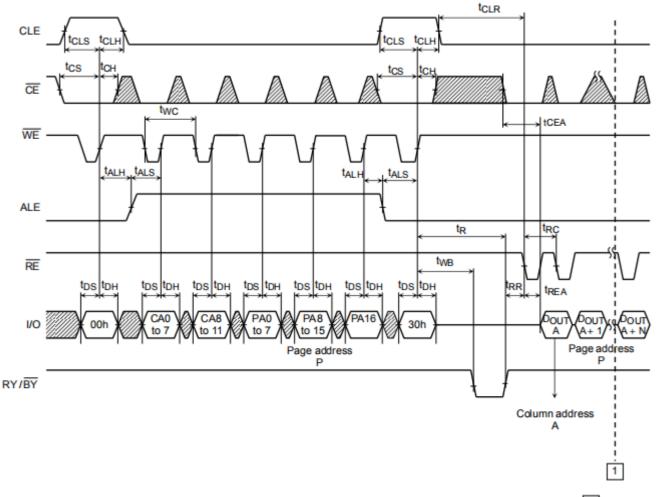

# Column Address Change in Read Cycle Timing Diagram (1/2)

Continues from 1 of next page

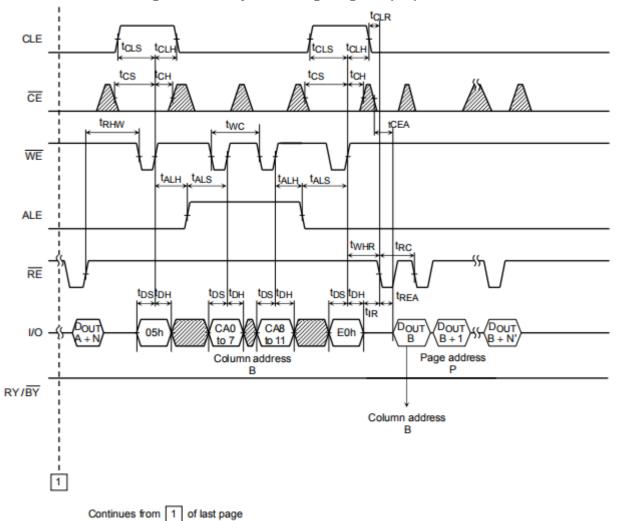

Column Address Change in Read Cycle Timing Diagram (2/2)

# Data Output Timing Diagram

# Auto-Program Operation Timing Diagram

\*) M: up to 2175 (byte input data for ×8 device).

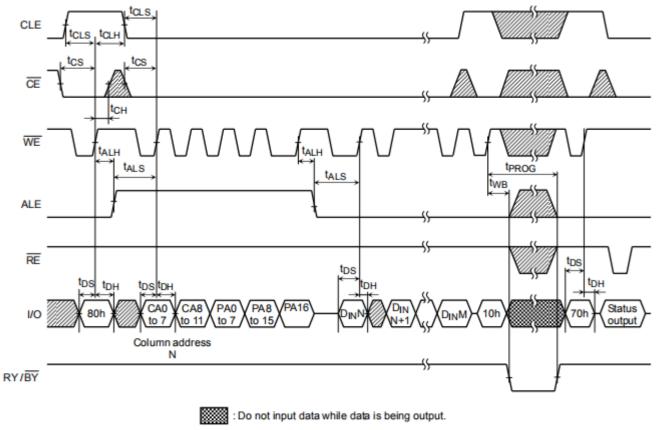

# Auto-Program Operation with Data Cache Timing Diagram (1/3)

Continues to 1 of next page

# Auto-Program Operation with Data Cache Timing Diagram (2/3)

Continued from 1 of last page

## Auto-Program Operation with Data Cache Timing Diagram (3/3)

(Note) Make sure to terminate the operation with 80h-10h- command sequence. If the operation is terminated by 80h-15h command sequence, monitor I/O 6 (Ready / Busy) by issuing Status Read command (70h) and make sure the previous page program operation is completed. If the page program operation is completed issue FFh reset before next operation.

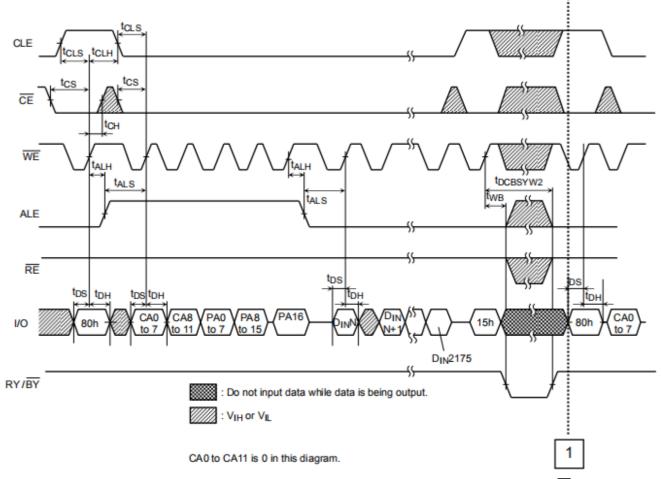

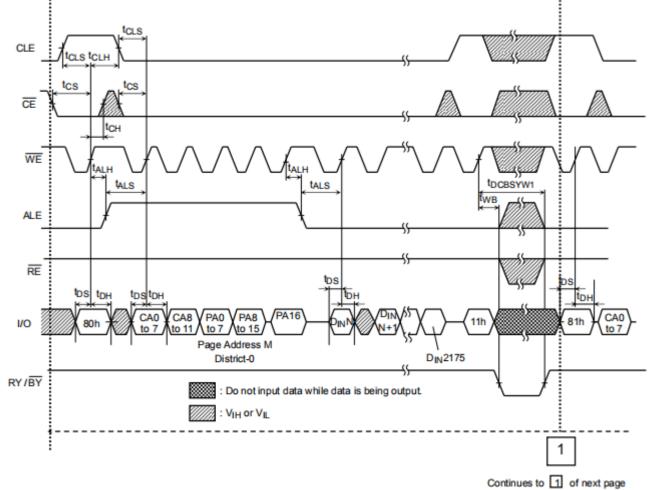

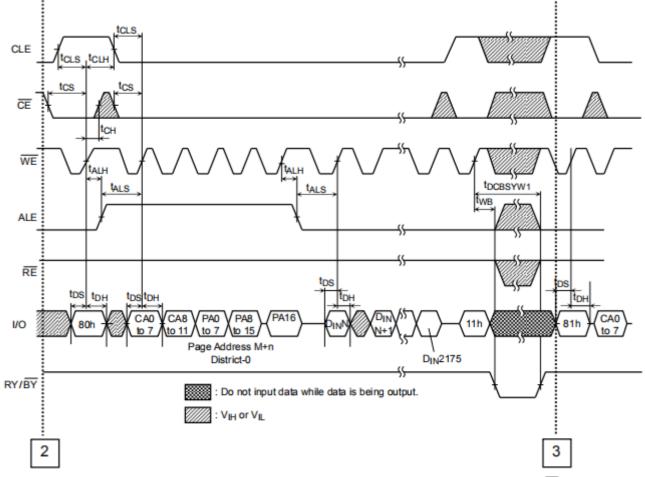

# Multi-Page Program Operation with Data Cache Timing Diagram (1/4)

# Multi-Page Program Operation with Data Cache Timing Diagram (2/4)

```

Continued from 1 of last page

```

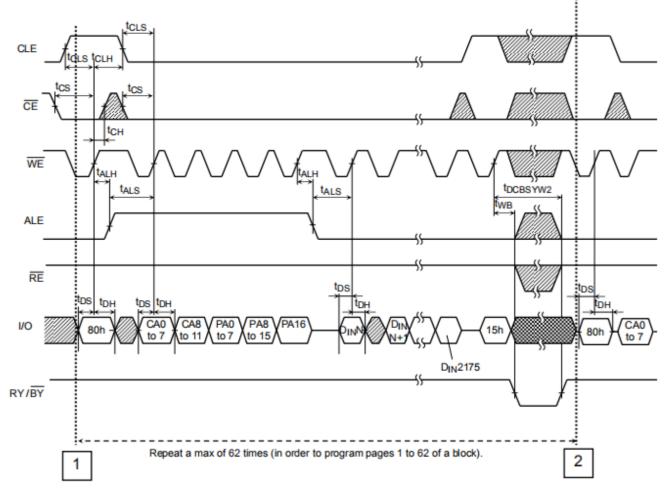

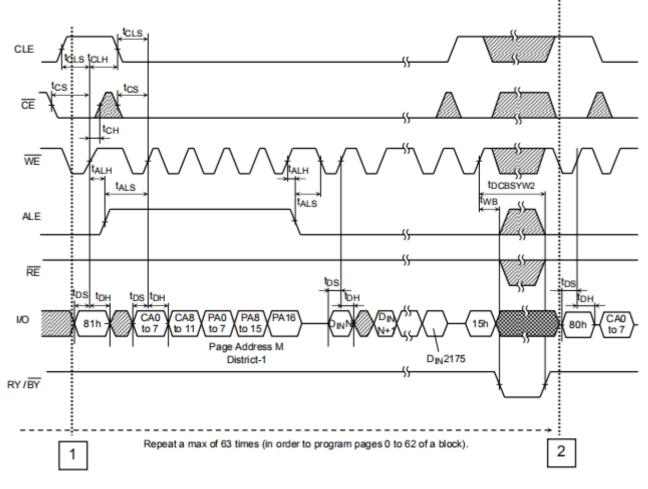

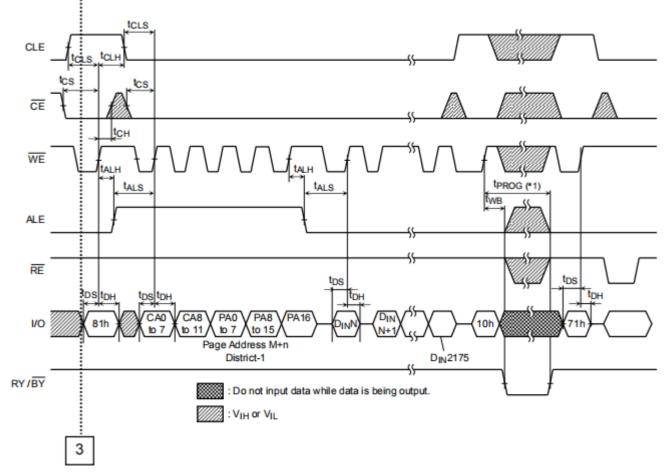

# Multi-Page Program Operation with Data Cache Timing Diagram (3/4)

Continues to 3 of next page

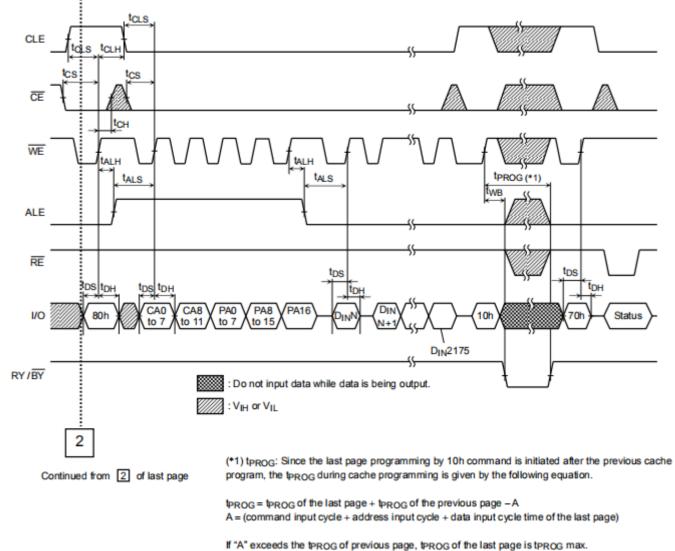

## Multi-Page Program Operation with Data Cache Timing Diagram (4/4)

Continued from 3 of last page

(\*1) tPROG: Since the last page programming by 10h command is initiated after the previous cache program, the tPROG during cache programming is given by the following equation.

tPROG = tPROG of the last page + tPROG of the previous page – A

A = (command input cycle + address input cycle + data input cycle time of the last page)

If "A" exceeds the tPROG of previous page, tPROG of the last page is tPROG max.

(Note) Make sure to terminate the operation with 81h-10h- command sequence.

If the operation is terminated by 81h-15h command sequence, monitor I/O 6 (Ready / Busy) by issuing Status Read command (70h) and make sure the previous page program operation is completed. If the page program operation is completed issue FFh reset before next operation.

## Auto Block Erase Timing Diagram

XT61M2G8D2TA-B8Bxx

# Multi Block Erase Timing Diagram

# **ID Read Operation Timing Diagram**

# **1.17. Application Notes and Comments**

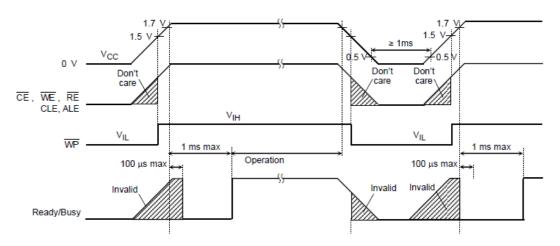

(1) Power-on/off sequence:

The timing sequence shown in the figure below is necessary for the power-on/off sequence.

The device internal initialization starts after the power supply reaches an appropriate level in the power on sequence. During the initialization the device Ready/Busy signal indicates the Busy state as shown in the figure below. In this time period, the acceptable commands are FFh or 70h.

The WP signal is useful for protecting against data corruption at power-on/off.

(2)Power-on Reset The following sequence is necessary because some input signals may not be stable at power-on.

(3) Prohibition of unspecified commands

The operation commands are listed in Table 3. Input of a command other than those specified in Table 3 is prohibited. Stored data may be corrupted if an unknown command is entered during the command cycle.

(4) Restriction of commands while in the Busy state

During the Busy state, do not input any command except 70h(71h) and FFh.

(5) Acceptable commands after Serial Input command "80h"

Once the Serial Input command "80h" has been input, do not input any command other than the Column Address Change in Serial Data Input command "85h", Auto Program command "10h", Multi Page Program command "11h", Auto Program with Data Cache Command "15h", or the Reset command "FFh".

If a command other than "85h", "10h", "11h", "15h" or "FFh" is input, the Program operation is not performed and the device operation is set to the mode which the input command specifies.

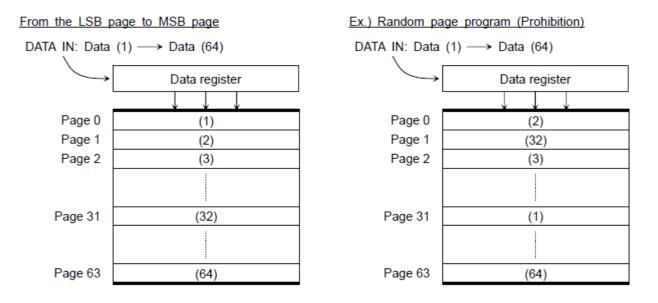

## (6) Addressing for program operation

Within a block, the pages must be programmed consecutively from the LSB (least significant bit) page of the block to MSB (most significant bit) page of the block. Random page address programming is prohibited.

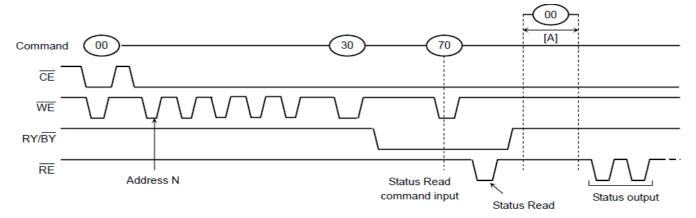

(7) Status Read during a Read operation

The device status can be read out by inputting the Status Read command "70h" in Read mode. Once the device has been set to Status Read mode by a "70h" command, the device will not return to Read mode unless the Read command "00h" is inputted during [A]. If the Read command "00h" is inputted during [A]. If the Read command "00h" is inputted during [A], Status Read mode is reset, and the device returns to Read mode. In this case, data output starts automatically from address N and address input is unnecessary

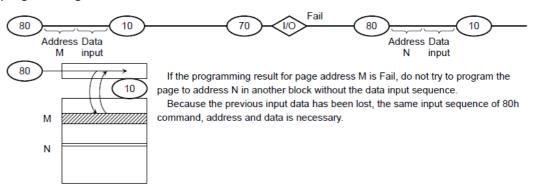

(8) Auto programming failure

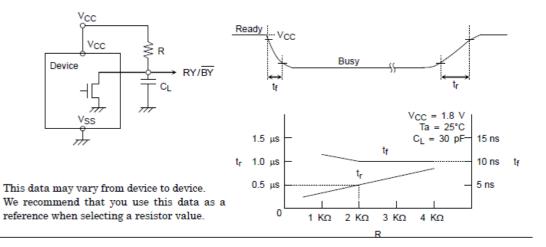

(9) RY / BY# : termination for the Ready/Busy pin (RY / BY# ) A pull-up resistor needs to be used for termination because the RY / BY# buffer consists of an open drain circuit.

## (10) Note regarding the WP# signal