# CURRENT MODE PWM CONTROL CIRCUITS

#### **DESCRIPTION**

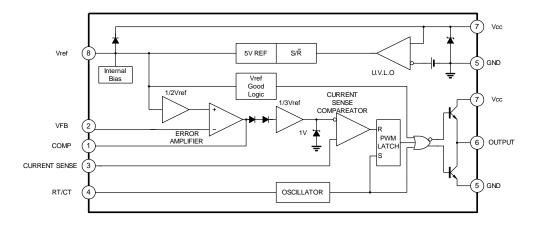

The UTC3843D/E provides the necessary features to implement off-line or DC to DC fixed frequency current mode control schemes with a minimal external parts count. Internally implemented circuits include under-voltage lockout featuring start up current less than 1mA,a precision reference trimmed for accuracy at the error amp input, logic to insure latched operation, a PWM comparator which also provides current limit control,and a totem pole output stage designed to source or sink high peak current. The output stage, suitable for driving N channel MOSFETs, is low in the off state.

#### **FEATURES**

- \*Optimized for off-line and DC to DC converts

- \*Low start up current(<1mA)

- \*Automatic feed forward compensation

- \*Pulse-by-Pulse current limiting

- \*Enhanced load response characteristics

- \*Under-voltage lockout with hysteresis

- \*Double pulse Suppression

- \*High current totem pole output

- \*Internally trimmed bandgap reference

- \*500kHz operation

- \*Low Ro error amp

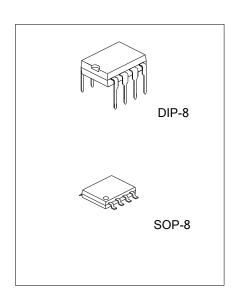

#### **ORDERING INFORMATION**

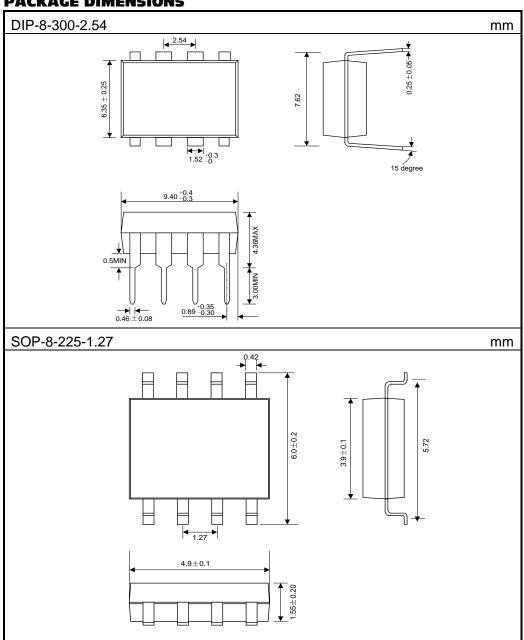

| Device   | Package        |

|----------|----------------|

| UTC3843D | DIP-8-300-2.54 |

| UTC3843E | SOP-8-225-1.27 |

#### **BLOCK DIAGRAM**

#### ABSOLUTE MAXIMUM RATINGS(Ta=25°C)

| Characteristic                       | Symbol    | Value                         | Unit |  |  |  |

|--------------------------------------|-----------|-------------------------------|------|--|--|--|

| Supply Voltage(Low Impedence Source) | Vcc       | 30                            | V    |  |  |  |

| Supply Voltage(Icc<30mA)             | Vcc       | Self Limiting                 | V    |  |  |  |

| Output Current                       | lo        | ±1                            | Α    |  |  |  |

| Output Energy(capacitive Load)       |           | 5                             | μЈ   |  |  |  |

| Analog Inputs(pin 2,3)               | VI(ANA)   | -0.3 to +6.3                  | V    |  |  |  |

| Error Amplifier Output Sink Current  | ISINK(EA) | 10                            | mA   |  |  |  |

| Power Dissipation                    | PD        | at T <sub>amb</sub> ≤25°C 1.0 | W    |  |  |  |

| Lead Temperature                     | Tlead     | 300                           | °C   |  |  |  |

| Storage Temperature                  | Tstg      | -65~+150                      | °C   |  |  |  |

Note 1: Ta>25°C,PD derated with 8mW/°C.

#### **ELECTRICAL CHARACTERISTICS**

(0≤Ta≤70°C,Vcc=15V,RT=10kΩ,CT=3.3nF,unless otherwise specified)

| Characteristic          | Symbol        | Test Conditions                     | Min  | Тур  | Max  | Units |

|-------------------------|---------------|-------------------------------------|------|------|------|-------|

| Reference Section       |               |                                     |      | •    |      |       |

| Output Voltage          | VREF          | Tj=25°C,lo=1mA                      | 4.90 | 5.00 | 5.10 | V     |

| Line Regulation         | $\Delta VREF$ | 12≤VIN≤25V                          |      | 6    | 20   | mV    |

| Load Regulation         | $\Delta VREF$ | 1≤lo=20mA                           |      | 6    | 25   | mV    |

| Temp Dtability          |               | (Note 2)                            |      | 0.2  | 0.4  | mV/°C |

| Total Output Variation  |               | Line,Load,Temp(note 2)              | 4.82 |      | 5.18 | μV    |

| Output Noise Voltage    | Vosc          | 10Hz≤f≤10kHz,Tj=25°C (note 2)       |      | 50   |      | mV    |

| Long term stability     |               | Ta=25°C,1000Hrs(note 2)             |      | 5    | 25   | mV    |

| Output Short Circuit    | Isc           |                                     | -30  | -100 | -180 | mA    |

| Oscillator Section      |               |                                     | •    |      |      |       |

| Initial Accurcy         | f             | Tj=25°C                             | 47   | 52   | 57   | kHz   |

| Voltage Stability       | Δf/ΔVcc       | 12≤Vcc≤25V                          |      | 0.2  | 1    | %     |

| Temp stability          |               | Tmin≤T <sub>A</sub> ≤Tmax(note 2)   |      | 5    |      | %     |

| Amplitude               | Vosc          | Vpin 4 peak to peak                 |      | 1.7  |      | V     |

| Error Amplifier Section |               |                                     | •    |      |      |       |

| Input Voltage           | VI(EA)        | Vpin 1=2.5V                         | 2.42 | 2.50 | 2.58 | V     |

| Input Bias current      | IBIAS         |                                     |      | -0.3 | -2   | μΑ    |

| AVOL                    |               | 2 ≤Vo≤4V                            | 60   | 90   |      | dB    |

| Unity Gain Bandwidth    |               | Tj=25°C (note 2)                    | 0.7  | 1    |      | mHz   |

| PSRR                    |               | I2≤Vcc≤25V                          | 60   | 70   |      | dB    |

| Output Sink Current     | Isink         | Vpin 2=2.7V,Vpin 1=1.1V             | 2    | 6    |      | mA    |

| Output Source Current   | Isource       | Vpin 2=2.3V,Vpin 1=5V               | -0.5 | -0.8 |      | mA    |

| Vout High               | Voн           | Vpin 2=2.3V, RL=15k $\Omega$ to GND | 5    | 6    |      | V     |

| Vout Low                | Vol           | Vpin 2=2.7V,Vpin 1=1.1V             |      | 0.7  | 1.1  | V     |

| Current Sense section   |               |                                     |      |      |      |       |

| Gain                    | G۷            | (note 3,4)                          | 2.85 | 3    | 3.15 | V/V   |

| Maximum Input signal    | VI(MAX)       | Vpin 1=5V( note 3)                  | 0.9  | 1    | 1.1  | V     |

| PSRR                    |               | 12≤Vcc≤25V                          |      | 70   |      | dB    |

| Input Bias Current      | IBIAS         |                                     |      | -2   | -10  | μА    |

| Delay to Output         |               | Vpin 3=0 to 2V                      |      | 150  | 300  | ns    |

| Output Section          |               |                                     |      |      |      |       |

| Output low Level        | Vol           | Isink=20mA                          |      | 0.1  | 0.4  | V     |

|                         |               | Isink=200mA                         |      | 1.5  | 2.2  | V     |

#### (conitinued)

| (continued)                         |           |                        |     |      |     |       |

|-------------------------------------|-----------|------------------------|-----|------|-----|-------|

| Characteristic                      | Symbol    | Test Conditions        | Min | Тур  | Max | Units |

| Output High Level                   | Voн       | Isource=20mA           | 13  | 13.5 |     | V     |

|                                     |           | Isource=200mA          | 12  | 13.5 |     | V     |

| Rise Time                           | tR        | Tj=25°C,CL=1nF(note 2) |     | 50   | 150 | ns    |

| Fall Time                           | tF        | Tj=25°C,CL=1nF(note 2) |     | 50   | 150 | ns    |

| UVLO Saturation                     |           | Vcc=5V,Isink=10mA      |     | 0.7  | 1.2 | V     |

| Under-Voltage Lockout Outpu         | t Section |                        |     |      |     |       |

| Start Threshold                     | VTH(ST)   |                        | 7.8 | 8.4  | 9.0 | V     |

| Min.Operating Voltage After Turn On | VOPR(min) |                        | 7.0 | 7.6  | 8.2 | V     |

| PWM Section                         |           |                        |     |      |     |       |

| Maximum duty Cycle                  | D(MAX)    |                        | 95  | 97   | 100 | %     |

| Minimum Duty Cycle                  | D(MIN)    |                        |     |      | 0   | %     |

| Total Standby Current               |           |                        |     |      |     |       |

| Start-up Current                    | Ist       |                        |     | 0.5  | 1   | mA    |

| Operating Supply Current            | ICC(opr)  | Vpin 2=Vpin 3=0V       |     | 11   | 17  | mA    |

| Vcc Zener Voltage                   | Vz        | Icc=25mA               |     | 34   |     | V     |

note 2:These parameters, although guaranteed , are not 100% tested in production.

note 3:Parameters measured at trip point of latch with Vpin 2=0.

note 4:Gain defined as:

$$A = \frac{\Delta Vpin 1}{\Delta Vpin 3} \quad ;0 \le Vpin 3 \le 0.8V$$

note 5:Adjust Vcc above the start threshold before setting at 15V.

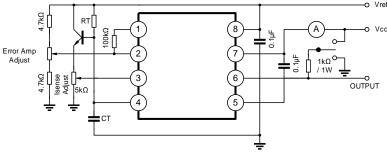

#### **OPEN-LOOP LABORATORY TEST CIRCUIT**

High peak current associated with capacitive loads necessitate careful grounding techniques. Timing and bypass capacitors should be connected close to pin 5 in single point GND.The transistor and  $5k\Omega$  potentiometer are used to sample the oscillator waveform and apply an adjustable Ramp to Pin 3.

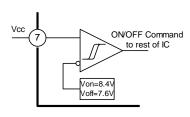

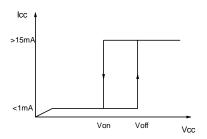

#### **UNDER-VOLTAGE LOCKOUT**

During Under-Voltage Lockout, the output driver is biased to a high impedance state. Pin 6 should be shunt to GND with a bleeder resistor to prevent

activating the power switch with output leakage currents.

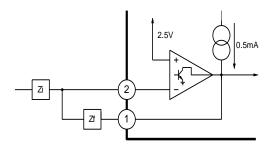

#### **ERROR AMPLIFIER CONFIGURATION**

Error amplifier can source or sink up to 0.5mA

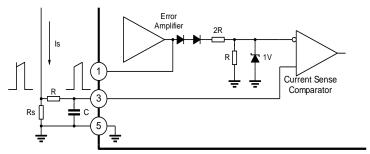

#### **CURRENT SENSE CIRCUIT**

Peak current (Is) determined by the formula: Ismax=10V/Rs.

A small RC filter be required to suppress switch transients.

#### **SLOPE COMPENSATION**

A fraction of the oscillator ramp can be resistively summed with the current sense signal to provide slope compensation for converts requiring duty cycles over 50%.Note that capacitor C, forms a filter with R2 to suppress the leading edge switch spikes.

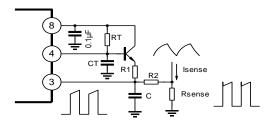

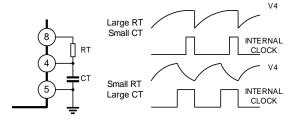

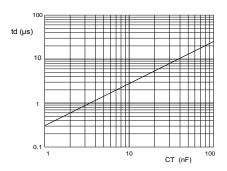

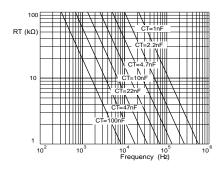

#### **OSCILLATOR SECTION**

Deadtime VS  $C_T(R_T > 5k\Omega)$

Timing Resistance Vs Frequency

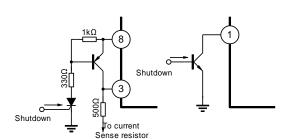

#### **SHUTDOWN TECHNIQUES**

Shutdown UTC3843D/E can be accomplished by two methods; either raise pin 3 above 1V or pull Pin 1 below a voltage two diode drops above ground. Either method caused the output of PWM comparator to be high(refer to block diagram). The PWM latch is reset dominant so that the output will remain low until the next clock cycle after the shutdown condition at pins a and/or 3 is removed . In one example, an externally latched shut down may be accomplished by adding an SCR which be reset by cycling Vcc below the lower UVLO threshold. At this point tyhe reference turns off allowing the SCR to reset.

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

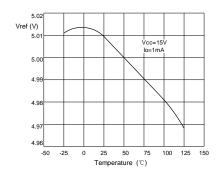

Vref Temperature Drift

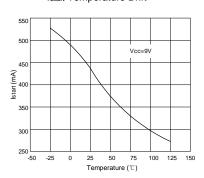

Istart Temperature Drift

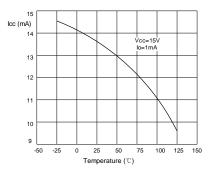

Icc Temperature Drift

# LINEAR INTEGRATED CIRCUIT

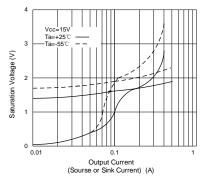

**Output Saturation Characteristics**

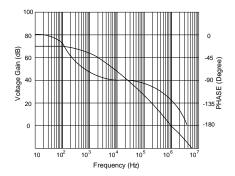

Error Amplifier Open-Loop Frequency Response

#### **PACKAGE DIMENSIONS**

## LINEAR INTEGRATED CIRCUIT

#### **ELECTROSTATIC DISCHARGE CAUTION**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage handing to prevent electrostatic damage to the device.

#### **NOTICE**

HANGZHOU YOUWANG ELECTRONICS CO.LTD assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all HANGZHOU YOUWANG ELECTRONICS CO.LTD's products described or contained herein. HANGZHOU YOUWANG ELECTRONICS CO.LTD's products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.

#### Attach

#### **Revision History**

| Data       | REV | Description                                            |     |  |  |

|------------|-----|--------------------------------------------------------|-----|--|--|

|            | 1.0 | Original                                               |     |  |  |

| 2006.07.11 | 1.1 | Add "OREDRING INFORMATION" and package outline "SOP-8" | 1,8 |  |  |

| 2017.08.21 | 1.2 | Add "Electrostatic Discharge Caution" and "NOTICE"     |     |  |  |

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Youwang Electronics manufacturer:

Other Similar products are found below:

LV5065VB-TLM-H LV5066V-TLM-H LV5725JAZ-AH 633888R MP2908AGF AZ7500EP-E1 NCP1012AP133G NCP1217P133G

NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP1587GDR2G NCP6153MNTWG

NCP81005MNTWG NCP81101BMNTXG NCP81205MNTXG HV9123NG-G-M934 IR35207MTRPBF ISL6367HIRZ CAT874-80ULGT3

SJ6522AG SJE6600 TLE63893GV50XUMA1 IR35215MTRPBF SG3845DM NCP1216P133G NCP1236DD65R2G NCP1247BD100R2G

NCP1250BP65G NCP4202MNR2G NCP4204MNTXG NCP6132AMNR2G NCP81141MNTXG NCP81142MNTXG NCP81172MNTXG

NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UC3845ADM UBA2051C IR35201MTRPBF MAX8778ETJ+

MAX17500AAUB+T MAX17411GTM+T MAX16933ATIR/V+ NCP1010AP130G NCP1063AD100R2G NCP1216AP133G

NCP1217AP100G