### Si522

## 13.56MHz 非接触式读写器芯片

#### 1. 介绍

本文档描述了非接触式读写器 Si522 的功能特性和电气特性。本文档为内部设计文档,设计参数仅作参考。

#### 2. 概述

Si522 是一个高度集成的,工作在 13.56MHz 的非接触式读写器芯片,阅读器支持 ISO/IEC 14443 A/MIFARE。

无需外围其他电路,Si522的内部发送器可驱动读写器天线与 ISO/IEC 14443 A/MIFARE 卡和应答机通信。接收器模块提供一个强大和高效的电路来解调译码 ISO/IEC 14443 A/MIFARE 兼容卡和应答机的信号。数字模块处理完整的 ISO/IEC 14443 A 帧和错误检测功能(奇偶和 CRC)。

Si522 支持 MIFARE 产品。Si522 支持非接触式通信,与 MIFARE 系列双向通信速率高达 848kBd。

提供以下主机接口:

- SPI(串行外设接口)

- 串行 UART (类似 RS232, 电压电平值取决于引脚供电电压)

- •标准双线串行接口

### 3. 参数和特性

- •高度集成的模拟电路,解调和译码响应

- •带缓冲的输出驱动器,使用最少的外围元件与天线连接

- •支持 ISO/IEC 14443 A/MIFARE

- •读写器模式的典型操作距离高达 50mm, 取决于天线的尺寸和圈数

- •读写器模式下支持 MIFARE 系列卡

- •支持 ISO/IEC 14443 A 更高速率通信, 最高达 848kBd

- 支持多种主机接口

- -SPI 接口,通信速率高达 10Mbit/s

- -标准双线串行接口

- -RS232 串行 UART 接口,通信速率高达 1228.8kBd,电压电平值取决于引脚供电电压

- 64 字节发送和接收 FIFO 缓冲区

- •灵活的中断模式

- •低功耗硬复位功能

- •软件掉电模式

- •可编程定时器

- •内部振荡器,连接 27.12MHz 石英晶体

- •2.5V至3.6V供电电压

- •CRC 协处理器

### 4. 主要参数指标

表1 极限参数

| 工作条件 | 最小值  | 最大值 | 单位           |

|------|------|-----|--------------|

| 电源电压 |      |     |              |

| VDD  | -0.5 | 4   | V            |

| 温度   |      |     |              |

| 工作温度 | -25  | +85 | $^{\circ}$ C |

表 2 主要参数指标

| 标志         | 参数        | 条件                                    |     | 最小  | 典型   | 最大   | 单            |

|------------|-----------|---------------------------------------|-----|-----|------|------|--------------|

|            |           |                                       |     | 值   | 值    | 值    | 位            |

| VDDA       | 模拟供电电压    | VDD (PVDD) ≤VDDA=VDDD=VDD (TVDD);     | (1) | 2.5 | 3. 3 | 4    | V            |

| VDDD       | 数字供电电压    | VSSA=VSSD=VSS (PVSS)=VSS (TVSS)=0V    |     | 2.5 | 3. 3 | 4    | V            |

| VDD (TVDD) | TVDD 供电电压 |                                       |     | 2.5 | 3. 3 | 4    | V            |

| VDD (PVDD) | PVDD 供电电压 |                                       | (1) | 2.5 | 3. 3 | 4    | V            |

| VDD (SVDD) | SVDD 供电电压 | VSSA=VSSD=VSS (PVSS)=VSS (TVSS)=0V    |     | 2.5 | 3. 3 | 4    | V            |

| Ipd        | 掉电电流      | VDDA=VDDD=VDD (TVDD)=VDD (PVDD)=3. 3V |     |     |      |      |              |

|            |           | 硬掉电; NRSTPD 引脚置低                      | (2) | _   | 1.5  | 2. 5 | uA           |

|            |           | 软掉电;射频电平检测器开启                         | (2) | -   | 1.2  | 1.5  | uA           |

| IDDD       | 数字供电电流    | DVDD 引脚; VDDD=3.3V                    |     | -   | 0.9  | 1.5  | uA           |

| IDDA       | 模拟供电电流    | AVDD 引脚; VDDA=3.3V, CommandReg        |     | -   | 2.9  | 4    | mA           |

|            |           | 寄存器的 RcvOff 位=0                       |     |     |      |      |              |

|            |           | AVDD 引脚;接收器关闭; VDDA=3.3V,             |     | -   | 0.8  | 1    | mA           |

|            |           | CommandReg 寄存器的 RcvOff 位=1            |     |     |      |      |              |

| IDD (TVDD) |           |                                       | (3) | -   | 25   | 30   | mA           |

| Tamb       |           |                                       |     | -25 | _    | +85  | $^{\circ}$ C |

- (1) VDDA, VDDD 和 VDD(TVDD)必须始终保持电压相同, VDD(PVDD)必须等于或小于 VDDD。

- (2) Ipd 是所有供电电源的总电流。

- (3)典型电路操作期间,总电流小于 30mA。

| 丰 | 3 | 推荐值     |

|---|---|---------|

| ベ | J | 11出/子1日 |

| 标志         | 参数        | 条件                                 | 最小  | 典型   | 最大  | 单位                                                                                 |

|------------|-----------|------------------------------------|-----|------|-----|------------------------------------------------------------------------------------|

|            |           |                                    | 值   | 值    | 值   |                                                                                    |

| VDDA       | 模拟供电电压    | VDD (PVDD) ≤VDDA=VDDD=VDD (TVDD);  | 2.5 | 3. 3 | 3.6 | V                                                                                  |

| VDDD       | 数字供电电压    | VSSA=VSSD=VSS (PVSS)=VSS (TVSS)=0V | 2.5 | 3. 3 | 3.6 | V                                                                                  |

| VDD (TVDD) | TVDD 供电电压 |                                    | 2.5 | 3. 3 | 3.6 | V                                                                                  |

| VDD (PVDD) | PVDD 供电电压 |                                    | 2.5 | 3. 3 | 3.6 | V                                                                                  |

| VDD (SVDD) | SVDD 供电电压 | VSSA=VSSD=VSS (PVSS)=VSS (TVSS)=0V | 2.5 | 3. 3 | 3.6 | V                                                                                  |

| Tamb       | 环境温度      | QFN32                              | -25 | 1    | +85 | $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

表 4 芯片版本信息

| 芯片型号  | 描述 |

|-------|----|

| Si522 | _  |

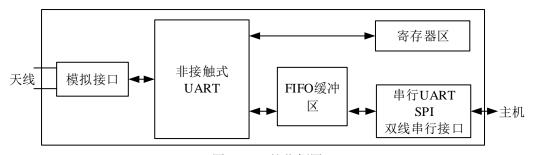

### 5. 框图

模拟接口处理模拟信号的调制解调。非接触 UART 处理与主机合作通信的协议要求。FIFO 缓冲区保证主机和非接触式 UART 之间快速方便的通信。

配备不同的主机接口满足不同的用户需求。

图1. Si522简化框图

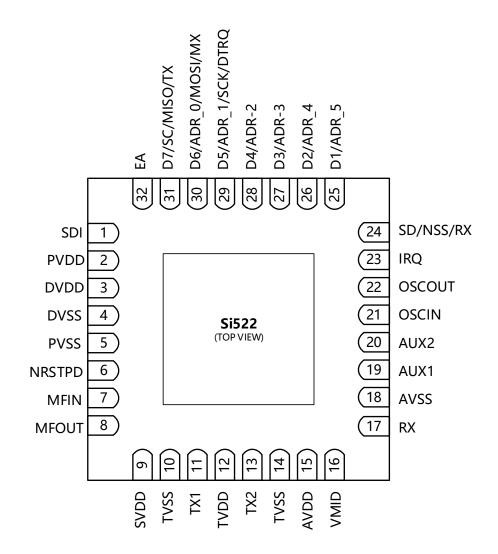

## 6. 引脚信息

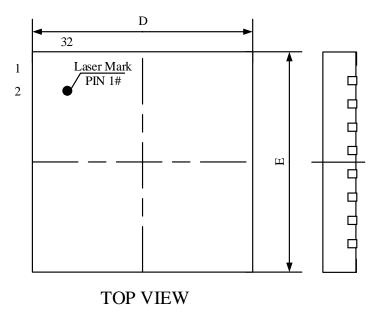

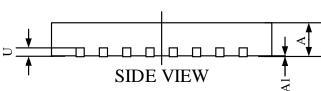

图2. 引脚配置图(QFN32L)

#### 6.1 引脚描述

表 5 引脚描述

| 引脚 | 标志     | 类型[1] | 描述                                  |

|----|--------|-------|-------------------------------------|

| 1  | SDI    | Ι     | 标准双线串行接口(Serial Data Interface)使能输入 |

| 2  | PVDD   | Р     | 引脚电源供电                              |

| 3  | DVDD   | Р     | 数字电源供电                              |

| 4  | DVSS   | G     | 数字地                                 |

| 5  | PVSS   | G     | 引脚电源地                               |

| 6  | NRSTPD | I     | 复位和掉电输入:                            |

# Si522Preliminary

| $\underline{}$ |        |     | 2                                   |  |  |  |

|----------------|--------|-----|-------------------------------------|--|--|--|

|                |        |     | 掉电: 低电平使能; 关闭内部电流吸收, 关闭振荡器, 断开输入引脚与 |  |  |  |

|                |        |     | 外部连接                                |  |  |  |

|                |        |     | 复位:上升沿使能                            |  |  |  |

| 7              | MFIN   | Ι   | MIFARE 信号输入                         |  |  |  |

| 8              | MFOUT  | 0   | MIFARE 信号输出                         |  |  |  |

| 9              | SVDD   | Р   | MFIN 和 MFOUT 引脚电源供电                 |  |  |  |

| 10             | TVSS   | G   | 发送器输出级 1 地                          |  |  |  |

| 11             | TX1    | 0   | 发送器 1 调制的载波信号输出                     |  |  |  |

| 12             | TVDD   | P   | 发送器电源供电:给发送器1和2的输出级供电               |  |  |  |

| 13             | TX2    | 0   | 发送器 2 调制的载波信号输出                     |  |  |  |

| 14             | TVSS   | G   | 发送器输出级 2 地                          |  |  |  |

| 15             | AVDD   | Р   | 模拟电源供电                              |  |  |  |

| 16             | VMID   | Р   | 内部参考电压                              |  |  |  |

| 17             | RX     | Ι   | 射频信号输入                              |  |  |  |

| 18             | AVSS   | G   | 模拟地                                 |  |  |  |

| 19             | AUX1   | 0   | 辅助输出,用于测试                           |  |  |  |

| 20             | AUX2   | 0   | 辅助输出,用于测试                           |  |  |  |

| 21             | OSCIN  | Ι   | 晶体振荡器的反相放大器的输入;同时也是外部产生的时钟输入(fclk=  |  |  |  |

|                |        |     | 27.12MHz)                           |  |  |  |

| 22             | OSCOUT | 0   | 晶体振荡器的反相放大器的输出                      |  |  |  |

| 23             | IRQ    | 0   | 中断请求输出: 指示一个中断事件                    |  |  |  |

| 24             | SD     | 1/0 | 标准双线串行的串行数据输入输出线                    |  |  |  |

|                | NSS    | Ι   | SPI 信号输入                            |  |  |  |

|                | RX     | I   | UART 地址输入                           |  |  |  |

| 25             | D1     | I/0 | 测试端口                                |  |  |  |

|                | ADR_5  | I/0 | 地址                                  |  |  |  |

| 26             | D2     | I/0 | 测试端口                                |  |  |  |

|                | ADR_4  | Ι   | 地址                                  |  |  |  |

|                |        |     |                                     |  |  |  |

# Si522 Preliminary

| 27 | D3    | I/0 | 测试端口              |  |

|----|-------|-----|-------------------|--|

|    | ADR_3 | Ι   | 地址                |  |

| 28 | D4    | I/0 | 测试端口              |  |

|    | ADR_2 | Ι   | 地址                |  |

| 29 | D5    | I/0 | 测试端口              |  |

|    | ADR_1 | Ι   | 地址                |  |

|    | SCK   | Ι   | SPI 串行时钟输入        |  |

|    | DTRQ  | 0   | UART 请求发送输出给微控制器  |  |

| 30 | D6    | I/0 | 测试端口              |  |

|    | ADR_0 | Ι   | 标准双线串行地址 0 输入     |  |

|    | MOSI  | I/0 | SPI 主机输出,从机输入     |  |

|    | MX    | 0   | UART 输出至微控制器      |  |

| 31 | D7    | I/0 | 测试端口              |  |

|    | SC    | I/0 | 标准双线串行时钟输入输出      |  |

|    | MISO  | I/0 | SPI 主机输入,从机输出     |  |

|    | TX    | 0   | UART 数据输出给微控制器    |  |

| 32 | EA    | Ι   | 编码标准双线串行地址的外部地址输入 |  |

<sup>1</sup> 引脚类型: I=输入, O=输出, I/O=输入/输出, P=电源, G=地

<sup>2</sup> 芯片封装底部散热焊盘的连接至 DVSS。

### 7. 功能描述

Si522 发送模块支持在不同的传输速率和调制协议下的 ISO/IEC 14443 A/MIFARE 读/写模式。

| 通信检测        | 信号类型 | 传输速率           |               |               |               |  |

|-------------|------|----------------|---------------|---------------|---------------|--|

|             |      | 106kBd         | 212kBd        | 424kBd        | 848kBd        |  |

| 阅读器至卡       | 阅读器方 | 100% ASK       | 100% ASK      | 100% ASK      | 100% ASK      |  |

| (Si522 发送数据 | 调制   |                |               |               |               |  |

| 给卡)         | 位编码  | 改进米勒编码         | 改进米勒编码        | 改进米勒编码        | 改进米勒编码        |  |

|             |      |                |               |               |               |  |

|             | 位长度  | 128 (13. 56us) | 64 (13. 56us) | 32 (13. 56us) | 16 (13. 56us) |  |

|             |      |                |               |               |               |  |

| 卡至阅读器(Si    | 卡方面的 | 副载波装载调         | 副载波装载调        | 副载波装载调        | 副载波装载调        |  |

| 522接收卡发送的   | 调制   | 制              | 制             | 制             | 制             |  |

| 数据)         | 副载波频 | 13.56MHz/16    | 13.56MHz/16   | 13.56MHz/16   | 13.56MHz/16   |  |

|             | 率    |                |               |               |               |  |

|             | 位编码  | 曼彻斯特编码         | BPSK          | BPSK          | BPSK          |  |

|             |      |                |               |               |               |  |

表 6 ISO/IEC 14443 A/MIFARE 读/写模式下通信概述

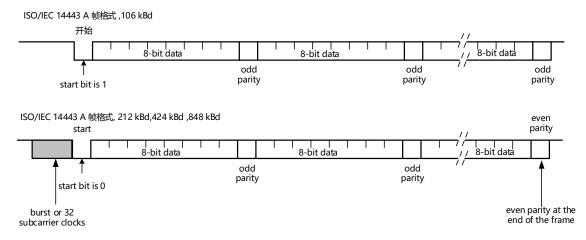

Si522 的非接触式 UART 和专用外围主机必须处理完整的 ISO/IEC 14443 A/MIFARE 协议。图 3 展示了 ISO/IEC 14443 A 协议的数据编码和帧格式。

图3. ISO/IEC 14443 A协议下的数据编码和帧格式

内部 CRC 协处理器根据 ISO/IEC 14443 A part3 计算 CRC 值并且根据传输速率产生奇偶校验位。自动奇偶校验位产生功能通过配置 MfRxReg 寄存器的 ParityDisable 位关闭。

#### 7.1 数字接口

#### 7.1.1 自动检测微控制器接口

Si522 支持 SPI,标准双线串行或串行 UART 接口与主机直连。Si522 在执行 掉电或者硬复位后会复位接口并自动检测当前主机的接口类型。复位阶段后 Si522 通过检测控制引脚上的逻辑电平来识别主机接口。这由固定引脚的连接完成。表 4 列出了不同的连接配置。

| 引脚  | 接口类型      |          |             |  |  |

|-----|-----------|----------|-------------|--|--|

|     | UART (输入) | SPI (输出) | 标准双线串行(I/0) |  |  |

| SD  | RX        | NSS      | SD          |  |  |

| SDI | 0         | 0        | 1           |  |  |

| EA  | 0         | 1        | EA          |  |  |

| D7  | TX        | MISO     | SC          |  |  |

| D6  | MX        | MOSI     | ADR_O       |  |  |

| D5  | DTRQ      | SCK      | ADR_1       |  |  |

| D4  | -         | -        | ADR_2       |  |  |

| D3  | -         | -        | ADR_3       |  |  |

| D2  | -         | -        | ADR_4       |  |  |

| D1  | _         | _        | ADR_5       |  |  |

表7检测不同接口类型的连接协议

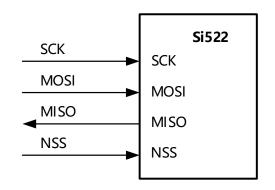

#### 7.1.2 串行外设接口

串行外设接口(兼容 SPI) 支持与主机高速通信,最高可达 10Mbit/s。当与主机通信时,Si522 作为从机,接收主机的寄存器配置以及发送或接收 RF 接口相关的通信数据。兼容 SPI 的接口实现 Si522 和微控制器间的高速串行通信。该接口协议与 SPI 标准一致。

图4. SPI连接主机

SPI 通信时 Si522 作为从机, SPI 时钟必须由主机产生。MOSI 和 MISO 上的数据均为 MSB 在前,数据必须在时钟的上升沿时保持稳定,在下降沿时可修改。Si522 在时钟下降沿时提供数据,上升沿时保持稳定。

#### 7.1.2.1SPI 读数据

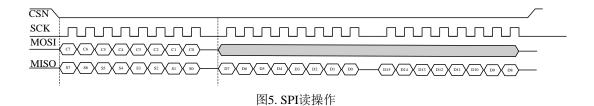

SPI 读数据的字节顺序如下表所示,读最多 n 字节数据,发送的首字节定义了模式和地址。SPI 读时序见图 5.

字节1 字节n 字节 n+1 数据线 字节0 字节2 至 ... MOSI 地址 0 地址1 地址 2 地址 n 00 MISO X 数据 0 数据1 数据 n-1 数据 n

表 8MOSI 和 MISO 上的字节顺序

注: 先发送最高位(MSB)

#### 7.1.2.2SPI 写数据

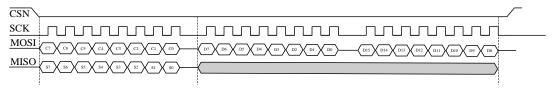

SPI 写数据的字节顺序如下表所示,发送一次地址,可写 n 字节数据,发送的首字节定义了模式和地址。

#### 表 9MOSI 和 MISO 上的字节顺序

| 数据线  | 字节 0 | 字节1  | 字节2 | 至   | 字节 n   | 字节 n+1 |

|------|------|------|-----|-----|--------|--------|

| MOSI | 地址 0 | 数据 0 | 数据1 | ••• | 数据 n-1 | 数据 n   |

| MISO | X    | X    | X   | ••• | X      | X      |

注: 先发送最高位(MSB)

图6. SPI写操作

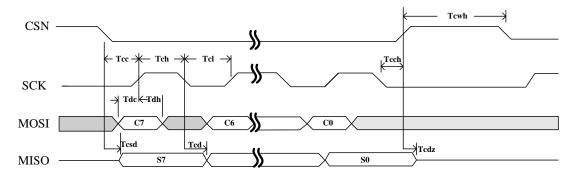

### 7.1.2.3SPI 典型时序

图 7 为 SPI 典型时序图,表 10 为 SPI 典型时序参数

图7. SPI典型时序

表 10SPI 典型时序参数

| Symbol | Parameters           | Min | Max | Units |

|--------|----------------------|-----|-----|-------|

| Tdc    | Data to SCK Setup    | 2   |     | ns    |

| Tdh    | SCK to Data Hold     | 2   |     | ns    |

| Tesd   | CSN to Data Valid    |     | 42  | ns    |

| Tcd    | SCK to Data Valid    |     | 58  | ns    |

| Tcl    | SCK Low Time         | 40  |     | ns    |

| Tch    | SCK High Time        | 40  |     | ns    |

| Fsck   | SCK Frequency        | 0   | 10  | MHz   |

| Tr,Tf  | SCK Rise and Fall    |     | 100 | ns    |

| Tec    | CSN to SCK Setup     | 2   |     | ns    |

| Tech   | SCK to CSN Hold      | 2   |     | ns    |

| Tcwh   | CSN Inactive time    | 50  |     | ns    |

| Tcdz   | CSN to Output High Z |     | 42  | ns    |

#### 7.1.2.4SPI 地址字节

SPI 地址字节必须符合以下格式。第一个字节的最高位(MSB)定义使用的模式,从 Si522 读回的数据的最高位(MSB)为逻辑 1,写给 Si522 的数据的最高位位(MSB)必设为逻辑 0,第 1 至 6 位定义地址且最低位(LSB)设为逻辑 0。

表 11 地址字节格式

| 7 (MSB) | 6  | 5 | 4 | 3 | 2 | 1 | 0 (LSB) |

|---------|----|---|---|---|---|---|---------|

| 1,读     | 地址 |   |   |   |   |   | 0       |

| 0, 写    |    |   |   |   |   |   |         |

#### 7.1.3 UART接口

#### 7.1.3.1 连接主机

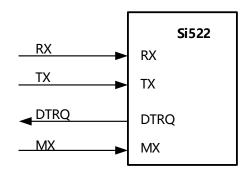

图8. UART连接微控制器

注: DTRQ 和 MX 信号通过清除 TestPinEnReg 寄存器的 RS232LineEn 位失能

#### 7.1.3.2 可选的 UART 传输速率

内部 UART 接口兼容 RS232 串行接口,默认传输速率为 9.6kBd。主机控制器 必 须 写一个新的传输 速率到 SerialSpeedReg 寄存器方能改变速率。 SerialSpeedReg 寄存器的 BR\_T0[2:0]和 BR\_T1[4:0]位定义了传输速率参数。

不同传输速率和相关寄存器配置示例如下表所示。

表 12 可选的 UART 传输速率

| 传输速率(kBd) | SerialSpeedReg 值 | 传输速率精度 |        |

|-----------|------------------|--------|--------|

|           | 十进制              | 十六进制   | (%)    |

| 7. 2      | 250              | FAh    | -0. 25 |

| 9.6       | 235              | EBh    | 0. 32  |

| 14. 4     | 218              | DAh    | -0. 25 |

| 19. 2     | 203              | CBh    | 0.32   |

| 38. 4     | 171              | ABh    | 0.32   |

| 57. 6     | 154              | 9Ah    | -0. 25 |

| 115. 2    | 122              | 7Ah    | -0. 25 |

| 128       | 116              | 7ah    | -0.06  |

| 230. 4    | 90               | 5Ah    | -0. 25 |

| 460.8     | 58               | 3Ah    | -0. 25 |

| 921.6     | 28               | 1Ch    | 1. 45  |

| 1228.8    | 21               | 15h    | 0. 32  |

上表中可选的传输速率根据下面公式计算得到:

$BR_T0[2:0] = 0:$

传输速率 =

$$(27.12 \times 10^6)/(BR_T0+1)$$

(1)

BR T0[2:0] > 0:

传输速率 =

$$(27.12 \times 10^6 \times 2^{(BR\_T0-1)})/(BR\_T1 + 33)$$

(2)

注: 不支持大于 1228. 8kBd 的传输速率

### 7.1.3.3UART 帧格式

表 13UART 帧格式

| 位  | 长度 | 值  |

|----|----|----|

| 开始 | 1位 | 0  |

| 数据 | 8位 | 数据 |

| 停止 | 1位 | 1  |

注: 必须先发送数据的最低位和地址字节, 无奇偶校验位

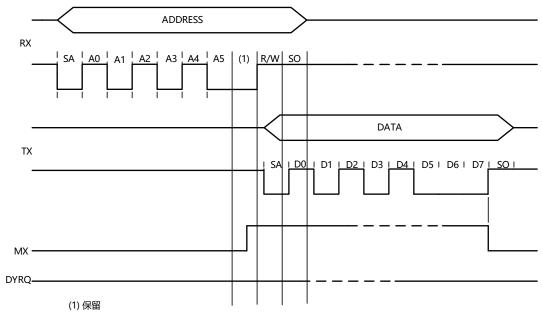

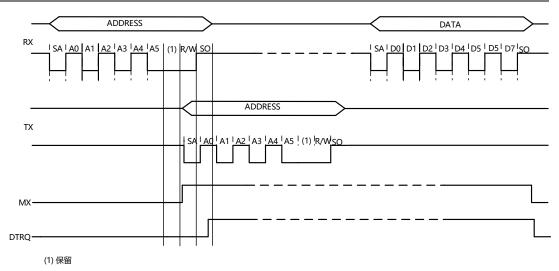

图9. UART读数据时序图

读数据: 使用以下数据流通过 UART 接口读取数据,发送的第一个字节定义 了模式和地址。

表 14 读数据的字节顺序

| 引脚 | 字节 0 | 字节1  |

|----|------|------|

| RX | 地址   | _    |

| TX | -    | 数据 0 |

写数据:使用以下结构通过 UART 接口写数据,发送的第一个字节定义了模式和地址。

表 15 写数据的字节顺序

| 引脚 | 字节 0 | 字节1  |

|----|------|------|

| RX | 地址 0 | 数据 0 |

| TX | _    | 地址 0 |

图10. UART写数据时序图

#### 7.1.4 标准双线串行接口

兼容标准双线串行总线。

#### 7. 2FIF0 缓冲区

Si522 包含一个 64x8 位的 FIF0 缓冲区,用来缓冲 Si522 和主机之间的输入输出数据流。输入输出接口为 FIF0DataReg 寄存器,地址为 0x09,通过读写该寄存器读写 FIF0 缓冲区。FIF0LevelReg 寄存器指示 FIF0 缓冲区存储的字节数,读/写 FIF0DataReg 寄存器分别减/增 FIF0Level 值。

为主机及时了解 FIFO 缓冲区的状况, FIFO 缓冲区会产生两个中断: HiAlertIRq 和 LoAlertIRq:

FIFO 缓冲区中的字节数满足以下等式时, HiAlert 置位, 若使能中断则产生 HiAlert IRq

#### $HiAlert = (64 - FIFOLength) \le WaterLevel$

FIFO 缓冲区中的字节数满足以下等式,LoAlert 置位,若使能中断则产生LoAlertIRq

#### LoAlert = FIFOLength ≤ WaterLevel

#### 7.3 中断请求系统

Si522通过置位Status1Reg寄存器的IRg位或者激活IRQ引脚来指示中断。

中断标志 中断源 触发操作 IRq 定时器单元 定时器计数到0 一次数据流发送结束 发送器 TxIRq CRC 协处理器 处理完 FIFO 缓冲区的所有数据 CRCIRq 接收器 一次数据流接收数据 RxIRq ComIrqReg 寄存器 执行完一个命令 IdleIRq FIFO 缓冲区 FIFO 缓冲区将满 HiAlertIRg FIFO 缓冲区 FIF0 缓冲区将空 LoAlertIRq 非接触式 UART 检测到一个错误 ErrIRq

表 16 中断源概览

#### 7.4 省电模式

#### 7.4.1 硬掉电

当 NRSTPD 引脚为低电平时芯片进入硬掉电。从硬掉电退出后所有寄存器变为复位值。

#### 7.4.2 软掉电

当 CommandReg 寄存器的 PowerDown 为置位时芯片立即进入软掉电,退出软掉电所有寄存器值不变。

#### 7.4.3 发送器掉电

发送器掉电模式关闭内部天线驱动器,即关闭射频场。将 TxControlReg 寄存器的 Tx1RFEn 位或 Tx2RFEn 位设为 0 即进入发送器掉电模式。

### 8. 命令集

#### 8.1 概述

Si522 的操作由可执行一系列命令的状态机决定,通过向命令寄存器 CommandReg 中写命令代码来执行命令。

#### 8.2 通用特性

- 除 Transceive 命令外,需要数据位流(或数据字节流)作为输入的命令立即处理 FIFO 缓冲区的任意数据,执行 Transceive 命令时,数据的发送由 BitFramingReg 寄存器的 StartSend 位启动。

- 需要一定数量的参数的命令只有当从 FIFO 缓冲区接收到正确数量的参数 时才开始处理。

- •命令开始时FIF0缓冲区不会自动清除,支持往FIF0缓冲区中写命令参数、数据字节,然后启动命令

- •主机往 CommandReg 寄存器中写一个新的命令代码中断当前执行的命令,比如, Idle 命令

### 8.3 命令概览

表 17 命令概览

| 命令                | 命令代码 | 操作                         |

|-------------------|------|----------------------------|

| Idle              | 0000 | 无操作,取消当前命令的执行              |

| Mem               | 0001 | 存储 25 个字节到 FIFO 缓冲区        |

| Generate RandomID | 0010 | 产生 10 字节随机 ID              |

| CalcCRC           | 0011 | 激活 CRC 协处理器                |

| Transmit          | 0100 | 发送缓冲区的数据                   |

| NoCmdChange       | 0111 | 无命令改变,用来修改 CommandReg 寄存器位 |

|                   |      | 而不影响命令的执行,比如,掉电位           |

| Receive           | 1000 | 激活接收器电路                    |

| Transceive        | 1100 | 发送 FIFO 缓冲区的数据至天线并在发送完成    |

|                   |      | 后自动激活接收器                   |

| MFAuthent         | 1110 | 作为阅读器执行 MIFARE 标准认证        |

| SoftReset         | 1111 | 复位 Si 522                  |

## 9. 寄存器映射表

表 18 寄存器映射表

| Address<br>(Hex) | Mnemonic     | Bit | Туре | Reset<br>Value | Description                                                                                                                              |

|------------------|--------------|-----|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 00h              | reserved     |     |      | 00h            | 保留                                                                                                                                       |

| 01h              | CommandReg   |     |      | 20h            | 命令寄存器                                                                                                                                    |

|                  | reserved     | 7-6 | -    |                | 保留                                                                                                                                       |

|                  | RcvOff       | 5   | R/W  |                | 1:接收器的模拟部分关闭                                                                                                                             |

|                  | PowerDown    | 4   | D    |                | 1: 进入软掉电<br>0: Si522 启动唤醒过程中该位始终为 1, 0 表示<br>Si522 已准备好<br>注: 如果 SoftReset 命令激活,该位不能再置位                                                  |

|                  | Command[3:0] | 3:0 | D    |                | 根据命令值激活命令,读该寄存器可知道正在执<br>行的命令                                                                                                            |

| 02h              | ComIEnReg    |     |      | 80h            | 中断控制和使能寄存器                                                                                                                               |

|                  | IRqInv       | 7   | R/W  |                | 1: IRQ 引脚上的信号与 StatusReg 寄存器的 IRQ<br>位的值相反<br>0: IRQ 引脚上的信号与 IRq 位的值相同,与<br>DivIEnReg 寄存器的 IRqPushPull 位配合,该位<br>默认为 1 以确保 IRQ 引脚输出电平为三态 |

|                  | TxIEn        | 6   | R/W  |                | 1: 允许发送器中断请求(TxIRq 位)传递到 IRQ 引<br>脚                                                                                                      |

|                  | RxIEn        | 5   | R/W  |                | 1: 允许接收器中断请求(RxIRq 位)传递到 IRQ 引<br>脚                                                                                                      |

|                  | IdleEn       | 4   | R/W  |                | 1: 允许空闲中断请求(IdleIRq 位)传递到 IRQ 引脚                                                                                                         |

|                  | HiAlertIEn   | 3   | R/W  |                | 1: 允许高于阈值预警中断请求(HiAlertIRq 位)<br>传递到 IRQ 引脚                                                                                              |

|                  | LoAlertIEn   | 2   | R/W  |                | 1: 允许低于阈值预警中断请求(LoAlertIRq 位)<br>传递到 IRQ 引脚                                                                                              |

|                  | ErrIEn       | 1   | R/W  |                | 1: 允许错误中断请求(ErrIRq 位)传递到 IRQ 引脚                                                                                                          |

|                  | TimerIEn     | 0   | R/W  |                | 1:允许定时器中断请求 (Timer IRq 位) 传递到 IRQ<br>引脚                                                                                                  |

| 03h              | DivIEnReg    |     |      | 00h            | 中断控制和使能寄存器                                                                                                                               |

|                  | IRQPushPull  | 7   | R/W  |                | 1: IRQ 作标准 CMOS 引脚<br>0: IRQ 作开漏输出引脚                                                                                                     |

|                  | reserved     | 6-5 | -    |                | 保留                                                                                                                                       |

# Si522 Preliminary

|     | T          | 1   | 1   | 1   | <b>Sie Zz</b> i rennmary                                                                                                                       |

|-----|------------|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

|     | MfinActIEn | 4   | R/W |     | 1: 允许 MFIN 激活中断请求传递到 IRQ 引脚                                                                                                                    |

|     | reserved   | 3   | -   |     | 保留                                                                                                                                             |

|     | CRCIEn     | 2   | R/W |     | 1: 允许 CRC 中断请求(由 DivIrqReg 寄存器的 CRCIRq 位指示)传递到 IRQ 引脚                                                                                          |

|     | reserved   | 1:0 | -   |     | 保留                                                                                                                                             |

| 04h | ComIrqReg  |     |     | 14h | 中断请求标志寄存器                                                                                                                                      |

|     | Set1       | 7   | w   |     | 1: 指示 ComIrqReg 寄存器的标志位置位<br>0: 指示 ComIrqReg 寄存器的标志位清零                                                                                         |

|     | TxIRq      | 6   | D   |     | 1: 发送数据最后一位发出后立即置位                                                                                                                             |

|     | RxIRq      | 5   | D   |     | 1:接收器检测到一个有效数据流的结束后置位如果 RxModeReg 寄存器的 RxNoErr 位置位,则RxIRq仅在FIFO中存在有效数据时置位                                                                      |

|     | IdleIRq    | 4   | D   |     | 1: 如果一个命令终止(比如, CommandReg 寄存器<br>从其他命令改变为 Idle 命令时);<br>如果一个未知命令启动, CommandReg 寄存器的<br>Command[3:0]值则变为 idle 且该位置位;<br>微控制器开始执行 Idle 命令,该位不置位 |

|     | HiAlertIRq | 3   | D   |     | 1: 当 StatusReg 寄存器的 HiAlertIrq 位置位<br>与HiAlert 位相反, HiAlertIRq 位保存中断事件,<br>只能在本寄存器 Set1 位指示后复位                                                 |

|     | LoAlertIRq | 2   | D   |     | 1: 当 StatusReg 寄存器的 HiAlertIrq 位置位<br>与LoAlert 位相反, LoAlertIRq 位保存中断事件,<br>只能在本寄存器 Set1 位指示后复位                                                 |

|     | ErrIRq     | 1   | D   |     | 1: ErrorReg 的任何错误位置位                                                                                                                           |

|     | TimerIRq   | 0   | D   |     | 1: TCounterValReg 中的计数值计到 0                                                                                                                    |

| 05h | DivIrqReg  |     |     | x0h | 中断请求标志寄存器                                                                                                                                      |

|     | Set2       | 7   | w   |     | 1: DivIrqReg 寄存器的标志位置位<br>0: DivIrqReg 寄存器的标志位清零                                                                                               |

|     | reserved   | 6-5 | -   |     | 保留                                                                                                                                             |

|     | MfinActIRq | 4   | D   |     | 1: MFIN 激活<br>检测到上升沿或下降沿该中断位均置位                                                                                                                |

| _   | reserved   | 3   | -   |     | 保留                                                                                                                                             |

|     | CRCIRq     | 2   | D   |     | 1: CalcCRC 命令激活且所有数据被处理                                                                                                                        |

|     | reserved   | 1:0 | -   |     | 保留                                                                                                                                             |

| 06h | ErrorReg   |     |     | 00h | 错误标志寄存器                                                                                                                                        |

|     | WrErr      | 7   | R   |     | 1: 当执行 MFAuthent 命令期间或在 RF 接口发送<br>最后一个字节和接收最后一个字节之间,主机往                                                                                       |

## Si522Preliminary

|     |             |   |   |     | Die Lai Temmany                                                                                                   |

|-----|-------------|---|---|-----|-------------------------------------------------------------------------------------------------------------------|

|     |             |   |   |     | FIFO 缓冲区中写数据                                                                                                      |

|     | TempErr     | 6 | R |     | 1: 内部温度传感器检测到过温,天线驱动器关断                                                                                           |

|     | reserved    | 5 | - |     | 保留                                                                                                                |

|     | BufferOvfl  | 4 | R |     | 1: 主机或 Si522 内部状态机(如接收器)在 FIF0 缓冲区已满情况下仍向其中写数据                                                                    |

|     | CollErr     | 3 | R |     | 1: 检测到位冲突接收器启动阶段自动清零,只在106kBd速率下位防冲突中有效,其他速率下无效,即212/424/848kBd                                                   |

|     | CRCErr      | 2 | R |     | 1: RxModeReg 寄存器的 RxCRCEn 位置位且 CRC 计算失败<br>接收器启动阶段自动清零                                                            |

|     | ParityErr   | 1 | R |     | 1: 奇偶校验失败<br>在接受器启动阶段自动清零,仅在 106kBd 的<br>ISO/IEC 14443 A/MIFARE 通信中有效                                             |

|     | ProtocolErr | 0 | R |     | 1: SOF 错误<br>接收器启动阶段自动清零,仅在 106kBd 速率下<br>有效,在 MFAuthent 命令执行期间,若一个数据<br>流收到的字节数错误则 ProtocolErr 位置位               |

| 07h | Status1Reg  |   |   | 21h | 状态寄存器                                                                                                             |

|     | reserved    | 7 | - |     | 保留                                                                                                                |

|     | CRCOk       | 6 | R |     | 1: CRC 结果为 0<br>在数据发送和接收期间 CRCOk 未定义而使用<br>ErrorReg 寄存器的 CRCErr 位<br>该位指示 CRC 协处理器,计算期间该位为 0,当<br>计算结束且正确该位置位     |

|     | CRCReady    | 5 | R |     | 1: CRC 计算结束<br>仅在使用 CalcCRC 命令, CRC 协处理器计算期间<br>有效                                                                |

|     | IRq         | 4 | R |     | 根据中断使能配置(见ComIEnReg和DivIEnReg),<br>指示中断请求的中断源                                                                     |

|     | TRunning    | 3 | R |     | 1: 定时器单元正在运行,当下一个时钟到来时定时器将递减 TCounterValReg 的值注:在门控模式中,定时器通过 TModeReg 的寄存器的 TGate[1:0]使能后 TRunning 位置位,该位不受门控信号影响 |

|     | reserved    | 2 | - |     | 保留                                                                                                                |

|     | HiAlert     | 1 | R |     | 1: FIFO 缓冲区中的字节数满足一下等式  HiAlert = (64-FIFOLength) ≤ WaterLevel 例: FIFO 长度 =60, WaterLevel = 4 → HiAlert = 1       |

# Si522Preliminary

| $\underline{}$ |                 |     |     |     | <b>Sical</b> Tellithing                                                                                                                                                                                                                                                                                                       |

|----------------|-----------------|-----|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                 |     |     |     | FIFO长度 =59, WaterLevel = 4 -> HiAlert = 0                                                                                                                                                                                                                                                                                     |

|                | LoAlert         | 0   | R   |     | 1: FIFO 缓冲区中的字节数满足一下等式  LoAlert = FIFOLength ≤ WaterLevel 例: FIFO 长度 = 4, WaterLevel = 4 → LoAlert = 1 FIFO 长度 = 5, WaterLevel = 4 → LoAlert = 0                                                                                                                                                                              |

| 08h            | Status2Reg      |     |     | 00h | 状态寄存器                                                                                                                                                                                                                                                                                                                         |

|                | TempSensClear   | 7   | R/W |     | 1: 当温度低于报警阈值 125℃时,温度错误被清除                                                                                                                                                                                                                                                                                                    |

|                | reserved        | 6:4 | -   |     | 保留                                                                                                                                                                                                                                                                                                                            |

|                | MFCrypto1On     | 3   | D   |     | 指示 MIFARE Cryptol 单元开启和因此所有卡的 通信数据被加密的情况 只有成功执行 MFAuthent 命令后才可置位 只在 MIFARE 标准卡的读/写模式中有效,软件清零                                                                                                                                                                                                                                 |

|                | ModemState[2:0] | 2:0 | R   |     | 指示发送器和接收器的状态机 000: 空闲(idle) 001: 等待 BitFramingReg 寄存器的 StartSend 位 010: 发送等待(TxWait),如果 TModeReg 寄存器的 TxWaitRF 位置位,则处于 TxWait 状态直到射频场存在,最小的 TxWait 时间由 TxWaitReg 寄存器定义 011: 发送(transmitting) 100: 接收等待(RxWait),如果 TModeReg 寄存器的 TxWaitRF 位置位,则处于 RxWait 状态直到射频场存在,最小的 RxWait 时间由 RxWaitReg 寄存器定义 101: 等待数据 110: 接收(receiving) |

| 09h            | FIFODataReg     |     |     | xxh | FIFO 缓冲区输入输出寄存器                                                                                                                                                                                                                                                                                                               |

|                | FIFOData[7:0]   | 7:0 | D   |     | 内部 64 字节 FIF0 缓冲区的数据输入输出口 FIF0 缓冲区作为所有数据流输入输出的并行输 入/输出转换器                                                                                                                                                                                                                                                                     |

| 0Ah            | FIFOLevelReg    |     |     | 00h | FIFO 缓冲区字节数指示寄存器                                                                                                                                                                                                                                                                                                              |

|                | FlushBuffer     | 7   | W   |     | 1: 立即清零内部 FIFO 的读写指针和 ErrorReg<br>寄存器的 BufferOvfl 位<br>读该位一直返回 0                                                                                                                                                                                                                                                              |

|                | FIFOLevel[6:0]  | 6:0 | R   |     | 指示 FIFO 缓冲区存储的字节数<br>读/写 FIFODataReg 寄存器分别减/增 FIFOLevel<br>值                                                                                                                                                                                                                                                                  |

# Si522 Preliminary

| 0Bh | WaterLevelReg   |     |     | 08h | FIFO 上/下溢出警告阈值寄存器                                                                                                                                         |

|-----|-----------------|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | reserved        | 7:6 | -   |     | 保留                                                                                                                                                        |

|     | WaterLevel[5:0] | 6:0 | R/W |     | 定义指示 FIFO 缓冲区上溢或下溢的警告值如果 FIFO 缓冲区的剩余字节数小于或等于定义的 WaterLevel 值, Status lReg 寄存器的 HiAlert 位置位如果 FIFO 缓冲区长度小于或等于定义的WaterLevel 值, Status lReg 寄存器的 LoAlert 位置位 |

| 0Ch | ControlReg      |     |     | 10h | 控制寄存器                                                                                                                                                     |

|     | TStopNow        | 7   | W   |     | 1: 定时器立即停止 读该位一直返回 0                                                                                                                                      |

|     | TStartNow       | 6   | W   |     | 1: 定时器立即启动 读该位一直返回 0                                                                                                                                      |

|     | reserved        | 5:3 | -   |     | 保留                                                                                                                                                        |

|     | RxLastBits[2:0] | 2:0 | R   |     | 指示最后接收的字节的有效位数<br>如果值为 000b,整个字节均有效                                                                                                                       |

| 0Dh | BitFramingReg   |     |     | 00h | 面向位的帧调节寄存器                                                                                                                                                |

|     | StartSend       | 7   | W   |     | 1: 开始传输数据<br>只有与 Transceive 命令一起使用时有效                                                                                                                     |

|     | RxAlign[2:0]    | 6:4 | R/W |     | 用于面向位的帧的接收:定义了接收到的第一个位在FIFO缓冲区中的存放位置,例如:0:收到的LSB存放在位0,第2位存放在位11:收到的LSB存放在位1,第2位存放在位27:收到的LSB存放在位7,第2位存放紧接着的下一字节的位0这些位仅用于106kBd下的位防冲突功能,其他模式下均为0           |

|     | reserved        | 3   | -   |     | 保留                                                                                                                                                        |

|     | TxLastBits[2:0] | 2:0 | R/W |     | 用于面向帧的发送: 定义了发送的最后一个字节的位数 000b 表示最后一个字节的所有位都应发送                                                                                                           |

| 0Eh | CollReg         |     |     | xxh | 射频接口第一个位冲突检测相关定义寄存器                                                                                                                                       |

|     | ValuesAfterColl | 7   | R/W |     | 0: 所有接收的位在冲突后被清除<br>只在 106kBd 下的为防冲突中使用,其他情况下<br>应设为1                                                                                                     |

|     | reserved        | 6   | -   |     | 保留                                                                                                                                                        |

|     | CollPosNotValid | 5   | R   |     | 1: 未检测到冲突或冲突位在 CollPos[4:0]表示的范围外                                                                                                                         |

# Si522Preliminary

|     |              |     |     |     | <u> </u>                                                                                                                                 |

|-----|--------------|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------|

|     | CollPos[4:0] | 4:0 | R   |     | 显示了接收帧中第一次检测到冲突的位的位置,<br>只显示数据位位置,例如:<br>00h:表明冲突位在起始位<br>01h:表明冲突位在第1位<br>08h:表明冲突位在第8位<br>只有在CollPosNotValid位为0时,这些位才有<br>效            |

| 0Fh | reserved     |     |     | 08h | 保留                                                                                                                                       |

| 10h | reserved     |     |     | 00h | 保留                                                                                                                                       |

| 11h | ModeReg      |     |     | 3Fh | 收发相关的模式配置寄存器                                                                                                                             |

|     | MSBFirst     | 7   | R/W |     | 1: CRC 协处理器计算 CRC 时先从 MSB 开始 CRCResultReg 寄存器的 CRCResultMSB[7:0]位和 CRCResultLSB[7:0]位按照二进制位的顺序相反的 注: 在射频通信期间该位被忽略                        |

|     | reserved     | 6   | -   |     | 保留                                                                                                                                       |

|     | TXWaitRF     | 5   | R/W |     | 1: 只有射频场产生后发送器才启动                                                                                                                        |

|     | reserved     | 4   | -   |     | 保留                                                                                                                                       |

|     | PolMFin      | 3   | R/W |     | 定义 MFIN 引脚的极性                                                                                                                            |

|     | reserved     | 2   | -   |     | 保留                                                                                                                                       |

|     | CRCPreset    | 1:0 | R/W |     | 定义 CRC 协处理器执行 CalcCRC 命令的预设值<br>注: 任何通信期间,预设值根据 RxModeReg 和<br>TxModeReg 寄存器的定义位自动选择<br>00: 0000h<br>01: 6363h<br>10: A671h<br>11: FFFFh |

| 12h | TxModeReg    |     |     | 00h | 定义发送时的数据速率                                                                                                                               |

|     | TxCRCEn      | 7   | R/W |     | 1: 使能数据发送期间的 CRC 产生<br>注: 只能在 106kBd 速率下设为 0                                                                                             |

|     | TxSpeed[2:0] | 6:4 | D   |     | 定义发送数据的位速率,最高可达 848kBd<br>000:106kBd<br>001:212kBd<br>010:424kBd<br>011:848kBd<br>100-111: 保留                                            |

|     | InvMod       | 3   | R/W |     | 1: 发送数据的调制反相                                                                                                                             |

|     | reserved     | 2:0 | -   |     | 保留                                                                                                                                       |

# Si522 Preliminary

| 13h | RxModeReg      |     |     | 00h | 定义接收时的数据速率                                                                                    |

|-----|----------------|-----|-----|-----|-----------------------------------------------------------------------------------------------|

|     | RxCRCEn        | 7   | R/W |     | 1: 使能数据接收期间的 CRC 产生注: 只能在 106kBd 速率下设为 0                                                      |

|     | TxSpeed[2:0]   | 6:4 | D   |     | 定义接收数据的位速率,最高可达 848kBd<br>000:106kBd<br>001:212kBd<br>010:424kBd<br>011:848kBd<br>100-111: 保留 |

|     | RxNoErr        | 3   | R/W |     | 1: 忽略一个无效的数据流(接收少于 4 位),接收器仍工作                                                                |

|     | RxMultiple     | 2   | R/W |     | 0:接收器在收到一个数据流后关闭<br>1:能够接收多个数据流                                                               |

|     | reserved       | 1:0 | -   |     | 保留                                                                                            |

| 14h | TxControlReg   |     |     | 80h | 控制天线驱动引脚 TX1 和 TX2                                                                            |

|     | InvTx2RFOn     | 7   | R/W |     | 1: 当 TX2 使能, TX2 引脚输出信号反相                                                                     |

|     | InvTx1RFOn     | 6   | R/W |     | 1: 当 TX1 使能, TX1 引脚输出信号反相                                                                     |

|     | InvTx2RFOff    | 5   | R/W |     | 1: 当 TX2 失能, TX2 引脚输出信号反相                                                                     |

|     | InvTx1RFOff    | 4   | R/W |     | 1: 当 TX1 失能, TX1 引脚输出信号反相                                                                     |

|     | Tx2CW          | 3   | R/W |     | 1: TX2 引脚输出为连续的未调制的 13.56MHz 载 波 0: Tx2CW 位使能调制 13.56MHz 载波                                   |

|     | reserved       | 2   | -   |     | 保留                                                                                            |

|     | Tx2RFEn        | 1   | R/W |     | 1: TX2 引脚传输调制了发送数据的 13.56MHz 载 波                                                              |

|     | Tx1RFEn        | 0   | R/W |     | 1: TX1 引脚传输调制了发送数据的 13.56MHz 载 波                                                              |

| 15h | TxASKReg       |     |     | 00h | 控制发送的调制配置                                                                                     |

|     | reserved       | 7   | -   |     | 保留                                                                                            |

|     | Force100ASK    | 6   | R/W |     | 1: 独立于 ModGsPReg 寄存器配置,强制 100%ASK<br>调制                                                       |

|     | reserved       | 5:0 | -   |     | 保留                                                                                            |

| 16h | TxSelReg       |     |     | 10h | 为模拟模块选择内部信号                                                                                   |

|     | reserved       | 7:6 | -   |     | 保留                                                                                            |

|     | DriverSel[1:0] | 5:4 | R/W |     | 选择驱动器 TX1 和 TX2 的输入 00: 三态,如果 DriverSel[1:0]值设为三态模式, 软掉电模式下驱动器只有三态模式                          |

# Si522 Preliminary

|     |                |     |     |     | <b>Dicas</b> remining                                                                                                                          |  |

|-----|----------------|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     |                |     |     |     | 01: 来自内部编码器的调制信号(包络), 米勒脉冲编码         10: 来自 MFIN 引脚的调制信号(包络)         11: 高电平,高电平取决于InvTx1RFOn/InvTx1RFOff         和InvTx2RFOn/InvTx2RFOff 位的设置 |  |

|     | MFOutSel       | 3:0 | R/W |     | 选择到引脚 MFOUT 的输入信号                                                                                                                              |  |

| 17h | RxSelReg       |     |     | 84h | 选择内部接收器配置                                                                                                                                      |  |

|     | UARTSel[1:0]   | 7:6 | R/W |     | 选择非接触式 UART 的输入 00: 恒定的低电平 01: 来自 MFIN 引脚的曼彻斯特编码的副载波信号 10: 默认,内部模拟模块的调制信号 11: 来自 MFIN 引脚,不带副载波的 NRZ 编码信号,仅在 106kBd 以上传输速率下有效                   |  |

|     | RxWait[5:0]    | 5:0 | R/W |     | 数据发送后,接收器会延时 RxWait 个时钟后开启,这段"帧保护时间"内,RX 引脚上的任何信号都被忽略 Receive 命令忽略该参数 其他所有命令,比如 Transceive,MFAuthent 都使用这一参数 外部射频场开启后计数器立即开始计数                 |  |

| 18h | RxThresholdReg |     |     |     | 选择位译码器的阈值                                                                                                                                      |  |

|     | MinLevel[3:0]  | 7:4 | R/W |     | 定义译码器能接受的最小输入信号强度<br>信号强度低于该值的信号无效                                                                                                             |  |

|     | reserved       | 7:4 | -   |     | 保留                                                                                                                                             |  |

|     | CollLevel[2:0] | 3:0 | R/W |     | 定义译码器输入的最小信号强度,曼彻斯特编码<br>信号的弱半位必须达到该强度来产生于较强半<br>位幅度相关的一个位冲突                                                                                   |  |

| 19h | DemodReg       |     |     |     | 解调器设置寄存器                                                                                                                                       |  |

|     | AddIQ[1:0]     | 7:6 | R/W |     | 定义了在接收过程中 I 和 Q 通道的使用注: FixIQ 位必须设为 0 才能使能以下配置: 00: 选择较强的通道 01: 通信中选择较强的通道并冻结选择的通道 10: 保留 11: 保留                                               |  |

|     | FixIQ          | 5   | R/W |     | 1: 如果 AddIQ[1:0]设为 X0b,接收固定为 I 通道;如果 AddIQ[1:0]设为 X1b,接收固定为 Q 通道                                                                               |  |

|     | TPrescalEven   | 4   | R/W |     | 设置分频模式                                                                                                                                         |  |

|     |                | 1   | 1   | 1   | <u>I</u>                                                                                                                                       |  |

# Si522Preliminary

|     | TauRcv[1:0]                | 3:2 | R/W |     | 改变数据接收过程中内部 PLL 的时间常数                                                  |

|-----|----------------------------|-----|-----|-----|------------------------------------------------------------------------|

|     | TauSync[1:0]               | 1:0 | R/W |     | 改变突发过程中内部 PLL 的时间常数                                                    |

| 1Ah | reserved                   |     |     | 00h | 保留                                                                     |

| 1Bh | reserved                   |     |     | 00h | 保留                                                                     |

| 1Ch | MfTxReg                    |     |     | 62h | 控制一些 MIFARE 通信的发送参数                                                    |

|     | reserved                   | 7:2 | -   |     | 保留                                                                     |

|     | TxWait                     | 1:0 | R/W |     | 定义额外响应时间                                                               |

| 1Dh | MfRxReg                    |     |     | 00h | 控制一些 MIFARE 通信的接收参数                                                    |

|     | reserved                   | 7:5 | -   |     | 保留                                                                     |

|     | ParityDisable              | 4   | R/W |     | 1: 产生发送所需的奇偶校验位,同时关闭接收的奇偶校验检查<br>收到的奇偶校验位当作数据位来处理                      |

|     | reserved                   | 3:0 | -   |     | 保留                                                                     |

| 1Eh | reserved                   |     |     | 00h | 保留                                                                     |

| 1Fh | SerialSpeedReg             |     |     | EBh | 选择串行 UART 接口的速率                                                        |

|     | BR_T0[2:0]                 | 7:5 | R/W |     | 调整传输速率,详见7.1.3节                                                        |

|     | BR_T1[4:0]                 | 4:0 | R/W |     | 调整传输速率,详见7.1.3节                                                        |

| 20h | reserved                   |     |     | 00h | 保留                                                                     |

| 21h | CRCResultReg (higher bits) |     |     | FFh | CRC 计算结果的 MSB                                                          |

|     | CRCResultMSB [7:0]         | 7:0 | R   |     | 表示了 CRCResultReg 寄存器的高字节的值<br>仅在 Status1Reg 寄存器的 CRCReady 位为 1 时有<br>效 |

| 22h | CRCResultReg (lower bits)  |     |     | FFh | CRC 计算结果的 LSB                                                          |

|     | CRCResultLSB               | 7:0 | R/W |     | 表示了 CRCResultReg 寄存器的低字节的值<br>仅在 Status1Reg 寄存器的 CRCReady 位为 1 时有<br>效 |

| 23h | reserved                   |     |     | 88h | 保留                                                                     |

| 24h | ModeWidthReg               |     |     | 26h | 配置调制宽度                                                                 |

|     | ModWidth[7:0]              | 7:0 | R/W |     | 定义了米勒调制的宽度为载波频率发的倍数组成(ModWidth+1/Fclk)                                 |

# Si522 Preliminary

|     |                     |     |     |     | 最大值为位周期的一半                                                                                                                                      |

|-----|---------------------|-----|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 25h | reserved            |     |     | 87h | 保留                                                                                                                                              |

| 26h | RFCfgReg            |     |     | 48h | 配置接收器的增益                                                                                                                                        |

|     | reserved            | 7   | -   |     | 保留                                                                                                                                              |

|     | RxGain[2:0]         | 6:4 | R/W |     | 定义接收器的信号电压增益参数 000: 18dB 001: 23dB 010: 18dB 011: 23dB 100: 33dB 101: 38dB 110: 43dB 111: 48dB                                                  |

|     | reserved            | 3:0 | -   |     | 保留                                                                                                                                              |

| 27h | GsNReg              |     |     | 88h | 定义 TX1 和 TX2 引脚的 n 驱动器的电导                                                                                                                       |

| 28h | CWGsPReg            |     |     | 20h | 定义无调制期间 p 驱动器的电导                                                                                                                                |

| 29h | ModGsPReg           |     |     | 20h | 定义调制期间 p 驱动器的电导                                                                                                                                 |

| 2Ah | TModeReg            |     |     | 00h | 定义定时器的设置                                                                                                                                        |

|     | TAuto               | 7   | R/W |     | 1: 在所有的速率,所有通信模式下,定时器在<br>发送结束后自动启动<br>0: 定时器不受协议的影响                                                                                            |

|     | TGated[1:0]         | 6:5 | R/W |     | 内部定时器工作在门控模式<br>注:在门控模式中,当定时器通过 TModeReg 寄存器的 TGated[1:0]使能时,Status1Reg 寄存器的 TRunning 位置位,该位不受门控信号的影响00:无门控模式01:MFIN 引脚作为门控信号10:AUX1 作为门控信号11:- |

|     | TAutoRestart        | 4   | R/W |     | 1: 定时器不计数到 0, 从 16 位的定时器重装载值开始重新计数 0: 定时器计数到 0 且 ComIrqReg 寄存器的TimerIRq 为置位                                                                     |

|     | TPrescaler_Hi [3:0] | 3:0 | R/W |     | 定义了分频器的高 4 位值                                                                                                                                   |

| 2Bh | TPrescalerReg       |     |     | 00h | 定义了分频器的低8位值                                                                                                                                     |

|     | TPrescaler_Lo       | 7   | R/W |     | 定义了分频器的低 8 位值                                                                                                                                   |

|     |                     |     |     |     |                                                                                                                                                 |

# Si522Preliminary

|      | [7:0]          |  |  |      |                        |

|------|----------------|--|--|------|------------------------|

| 2.01 | TReloadReg     |  |  | 00h  | 定义了 16 位计数器的自动重装载值的高八位 |

| 2Ch  | (higher bits)  |  |  | OON  | 足入 10 世 日              |

| 2Dh  | TReloadReg     |  |  | 00h  | 定义了 16 位计数器的自动重装载值的低八位 |

|      | (lower bits)   |  |  |      | 足义 10 世 1 奴益的日 9 里 农   |

| 2Eh  | TCounterValReg |  |  | xxh  | 定时器值的高八位               |

|      | (higher bits)  |  |  | XXII | <b>足明確但时间八位</b>        |

| 2Fh  | TCounterValReg |  |  | xxh  | 定时器值的低 8 位             |

|      | (lower bits)   |  |  | XXII | 是 1                    |

注: R/W: 读/写; D: 动态; R: 只读; W: 只写;

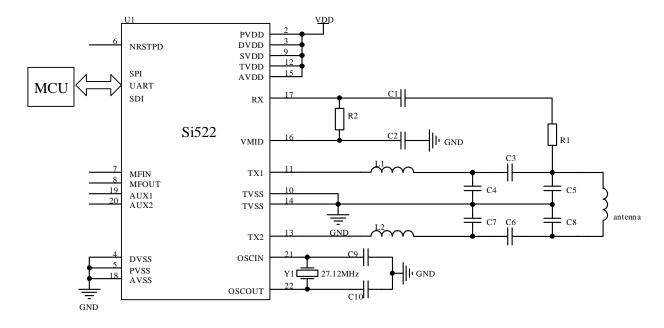

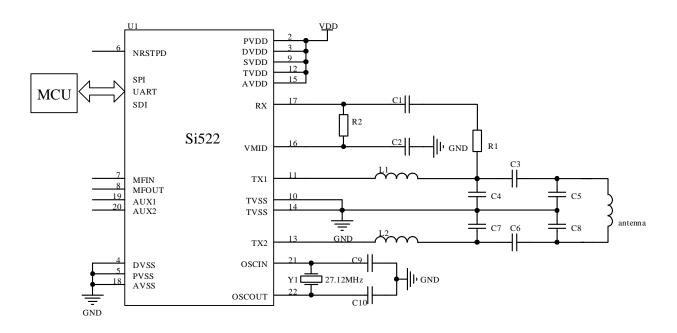

## 10. 典型应用图

图14. 典型应用图-1

图15. 典型应用图-2

1. 使用纽扣电池工作时, 电源部分推荐加 100uF 大电容;

## 11. 封装尺寸

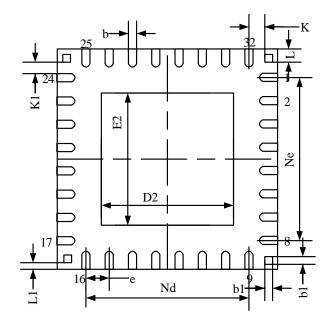

图16. 芯片封装(QFN32L)

### 表 19 封装尺寸

| SYMBOL    | MILLIMETER |          |      |  |  |  |  |

|-----------|------------|----------|------|--|--|--|--|

|           | MIN        | NOM      | MAX  |  |  |  |  |

| Α         | 0.70       | 0.75     | 0.80 |  |  |  |  |

| A1        | 0          | 0.2      | 0.05 |  |  |  |  |

| b         | 0.20       | 0.25     | 0.30 |  |  |  |  |

| <b>b1</b> | 0.20       | 0.25     | 0.30 |  |  |  |  |

| С         |            | 0.203REF |      |  |  |  |  |

| D         | 4.90       | 5.00     | 5.10 |  |  |  |  |

| D2        | 3.40       | 3.50     | 3.60 |  |  |  |  |

| е         | 0.50BSC    |          |      |  |  |  |  |

| Nd        | 3.5BSC     |          |      |  |  |  |  |

| Ne        | 3.5BSC     |          |      |  |  |  |  |

| E         | 4.90       | 5.0      | 5.10 |  |  |  |  |

| E2        | 3.40       | 3.50     | 3.60 |  |  |  |  |

| L         | 0.35       | 0.40     | 0.45 |  |  |  |  |

| L1        | 0.15REF    |          |      |  |  |  |  |

| K         | 0.35REF    |          |      |  |  |  |  |

| K1        | 0.225REF   |          |      |  |  |  |  |

## 12 修改记录

| 版本   | 修改日期       | 修改内容 | 修改人员      |

|------|------------|------|-----------|

| V1.0 | 2019/09/27 | 初稿   | DIG Group |

## 13. 技术支持与联系方式

## 南京中科微电子有限公司 技术支持中心

地址: 南京市玄武区徐庄软件园研发三区 B 栋 201

电话: 025-68517780

邮箱: sales-wxzk@casic.ac.cn

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RF Receiver category:

Click to view products by Zhongke manufacturer:

Other Similar products are found below:

TDA5240 TDA5225 PQJ7911AHN/C0C,515 ATA8205P6C-TKQW SI4732-A10-GS FM17580-QNA-T-G PCF7991AT/1081/M WS1830S SI522 SI522A Ci522 U3741BM-P3FLG3 MICRF229YQS ATA8202C-PXQW-1 STA8088FGTR SI4362-C2A-GM Si4836-A10-GS SI4825-A10-CS SI4730-D60-GMR SI4730-D60-GUR MICRF219AAYQS SI4831-B30-GUR SI4844-B20-GUR AW13412DNR SI4705-D60-GM SI4734-D60-GU T5743P3-TGQ AS3932-BQFT AD6643BCPZ-250 AD9864BCPZ FM12AG16M01 B82450A1084C CMX994GQ4 BGT24MR2E6327XUMA1 TDA5210 TDA5210XUMA1 TDA5211 TDA7200 TDA5240XUMA1 MICRF011YM MAX1473EUI+T MLX71122RLQ-BAA-000-SP MICRF022YM-FS48 MICRF220AYQS-TR SI4355-B1A-FMR SI4362-B1B-FMR MICRF21AYQS-TR MICRF010YM MICRF007YM MICRF219AAYQS-TR