# eZ80Acclaim!® Flash Microcontrollers

# eZ80F92/eZ80F93

**Product Specification**

PS015313-0508

Warning: DO NOT USE IN LIFE SUPPORT

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Zilog is a registered trademark of Zilog, Inc. in the United States and in other countries. eZ80Acclaim!, eZ80, and Z80 are trademarks or registered trademarks of Zilog Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510

Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

### **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links given in the table below.

| Date             | Revision<br>Level | Section                                                                                       | Description                                        | Page<br>No          |

|------------------|-------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------|

| May 2008         | 13                | Zilog Debug<br>Interface, ZDI-<br>Supported Protocol,<br>Figure 37 Typical<br>ZDI Debug Setup | Replaced ZPAK II with USB Smart Cable              | 162,<br>163,<br>162 |

|                  |                   |                                                                                               | Updated for Style guide                            | All                 |

| May 2007         | 12                | Electrical<br>Characteristics                                                                 | Updated Table 144                                  | 222                 |

|                  |                   | Serial Peripheral Interface                                                                   | Added note for SPI module                          | 130                 |

| February<br>2007 | 11                | Electrical<br>Characteristics                                                                 | Updated Figure 53, Figure 54, and Figure 55.       | 225,<br>226,<br>227 |

| March<br>2005    | 10                | Added registered trademark to eZ80 <sup>®</sup> and eZ80Acclaim! <sup>®</sup>                 |                                                    | All                 |

| October          | 09                | Formatted to current                                                                          | publication standards                              | All                 |

| 2004             |                   | Timer Control<br>Register                                                                     | Clarified RST_EN descriptions.                     | 81                  |

|                  |                   | Figure 58                                                                                     | Corrected CS rise time label from T8 to T6.        | 230                 |

|                  |                   | Figure 60                                                                                     | Corrected CS rise time label from T8 to T6.        | 233                 |

|                  |                   | Real-Time Clock<br>Oscillator and<br>Source Selection                                         | Clarified language describing RTC drive frequency. | 89                  |

PS015313-0508 Revision History

# **Table of Contents**

| Architectural Overview                                 | 1    |

|--------------------------------------------------------|------|

| Features                                               |      |

| Pin Description                                        |      |

| Pin Characteristics                                    |      |

| Register Map                                           | . 25 |

| eZ80 <sup>®</sup> CPU Core                             | . 31 |

| Features                                               |      |

| Reset                                                  |      |

|                                                        |      |

| Reset Operation                                        |      |

| Power-On Reset                                         |      |

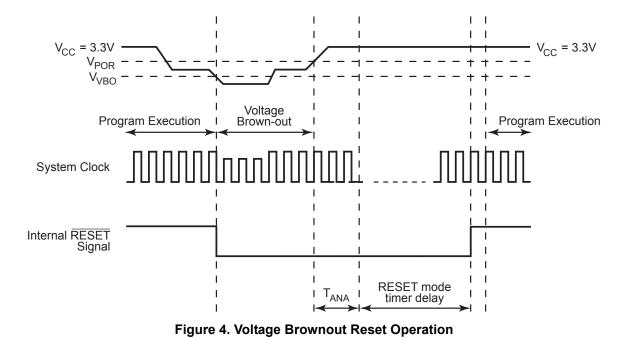

| Voltage Brownout Reset                                 |      |

| Low-Power Modes                                        |      |

| Overview                                               |      |

| SLEEP Mode                                             |      |

| HALT Mode                                              |      |

| Clock Peripheral Power-Down Registers                  | . 36 |

| General-Purpose Input/Output                           | 39   |

| GPIO Overview                                          |      |

| GPIO Operation                                         |      |

| GPIO Interrupts                                        |      |

| GPIO Control Registers                                 |      |

| · ·                                                    |      |

| Interrupt Controller                                   |      |

| Maskable Interrupts                                    |      |

| Nonmaskable Interrupts                                 |      |

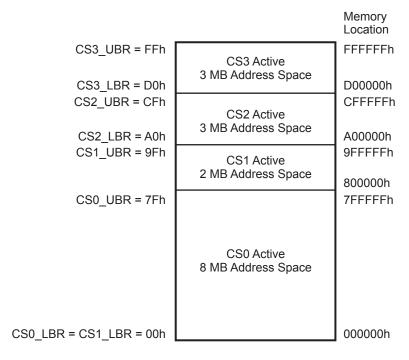

| Chip Selects and Wait States                           | . 48 |

| Memory and I/O Chip Selects                            |      |

| Memory Chip Select Operation                           |      |

| I/O Chip Select Operation                              |      |

| Wait States                                            |      |

| WAIT Input Signal                                      | . 51 |

| Chip Selects During Bus Request/Bus Acknowledge Cycles |      |

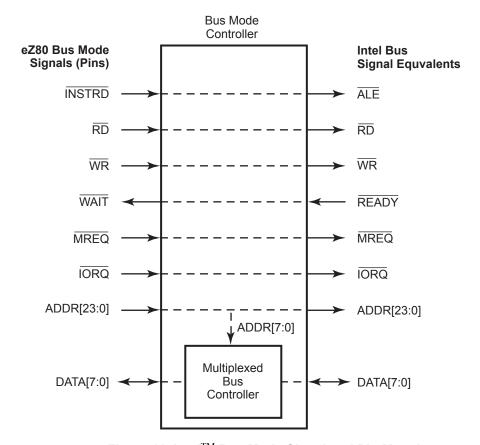

| Bus Mode Controller                                    |      |

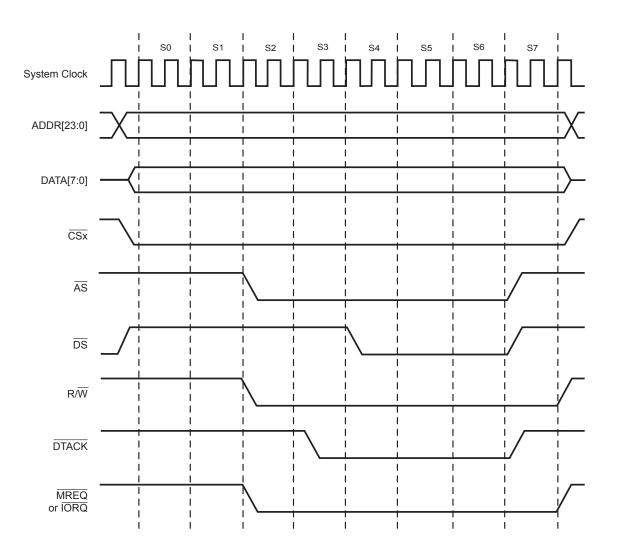

| eZ80 Bus Mode                                          | . 53 |

| Z80 Bus Mode                                           |      |

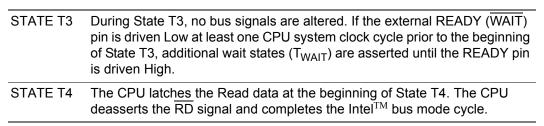

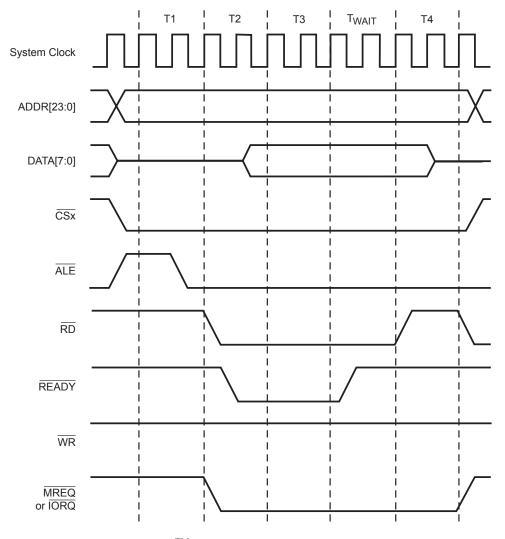

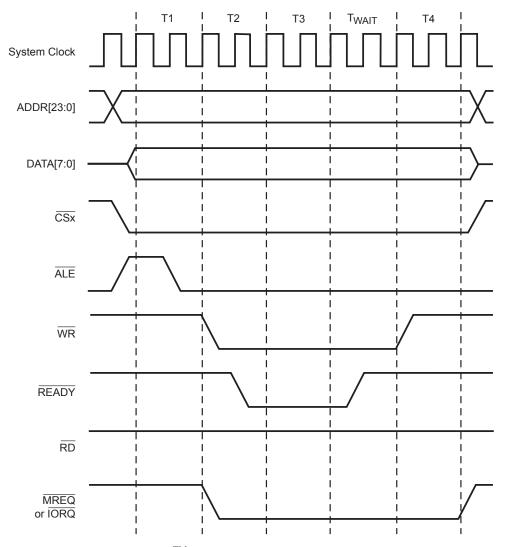

| Intel <sup>TM</sup> Bus Mode                           | . 55 |

| Motorola Bus Mode                                      | . 63 |

| Chip Select Registers                                  | . 67 |

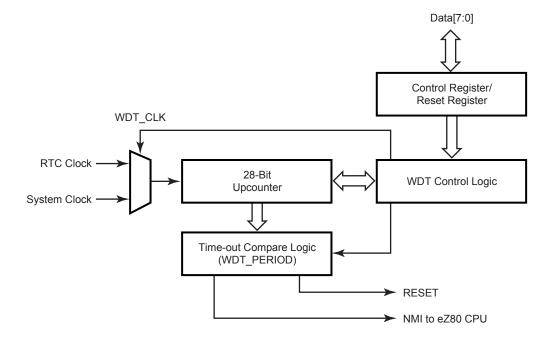

| Watchdog Timer                                         | . 72 |

| Watchdog Timer Overview                                |      |

PS015313-0508

#### eZ80F92/eZ80F93 Product Specification

| Watchdog Timer Operation                                             |     |

|----------------------------------------------------------------------|-----|

| Watchdog Timer Registers                                             |     |

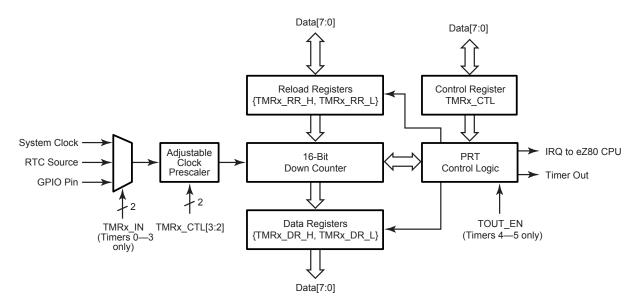

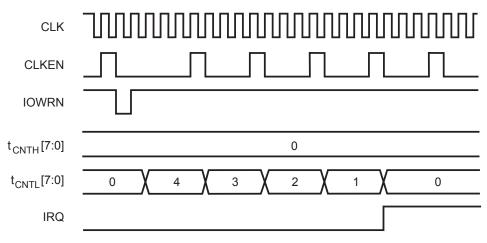

| Programmable Reload Timers       Programmable Reload Timers Overview |     |

| Programmable Reload Timer Operation                                  |     |

| Programmable Reload Timer Registers                                  |     |

| Real-Time Clock                                                      |     |

| Real-Time Clock Overview                                             |     |

| Real-Time Clock Alarm                                                |     |

| Real-Time Clock Oscillator and Source Selection                      |     |

| Real-Time Clock Battery Backup                                       |     |

| Real-Time Clock Recommended Operation                                |     |

| Real-Time Clock Registers                                            |     |

| Universal Asynchronous Receiver/Transmitter                          |     |

| UART Functional Description                                          |     |

| UART Functions                                                       |     |

| UART Interrupts                                                      |     |

| Baud Rate Generator                                                  |     |

| BRG Control Registers                                                |     |

| UART Registers                                                       |     |

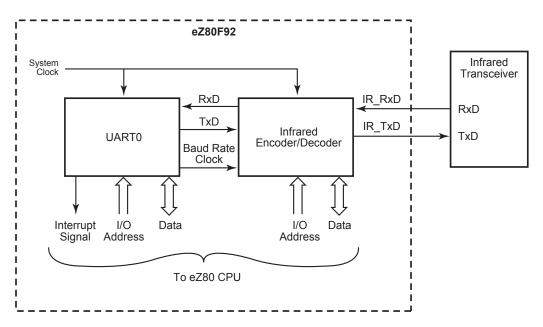

| Infrared Encoder/Decoder                                             | 124 |

| Functional Description                                               |     |

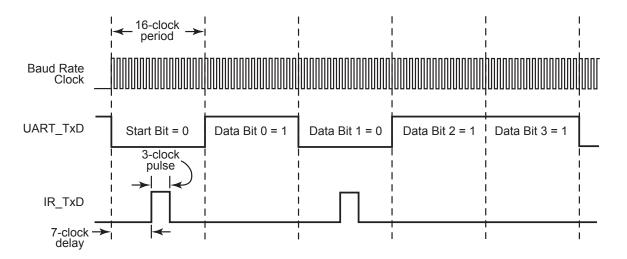

| Transmit                                                             |     |

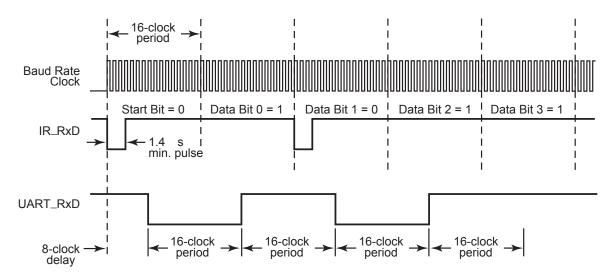

| Receive                                                              |     |

| Receiver Frequency Divider                                           |     |

| Jitter                                                               |     |

| Infrared Encoder/Decoder Signal Pins                                 |     |

| · · · · · · · · · · · · · · · · · · ·                                |     |

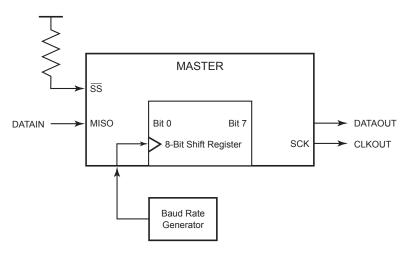

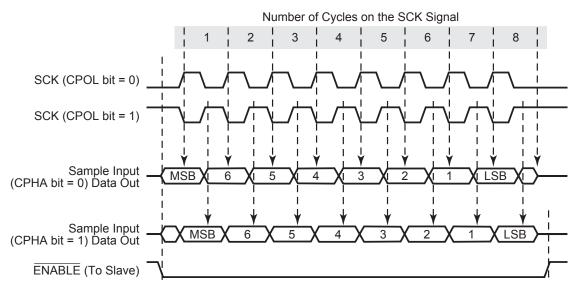

| Serial Peripheral Interface                                          |     |

| SPI Signals                                                          |     |

| SPI Flags                                                            |     |

| SPI Baud Rate Generator                                              |     |

| Data Transfer Procedure with SPI Configured as the Master            | 135 |

| Data Transfer Procedure with SPI Configured as a Slave               |     |

| SPI Registers                                                        | 135 |

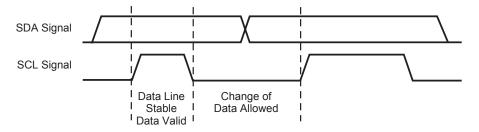

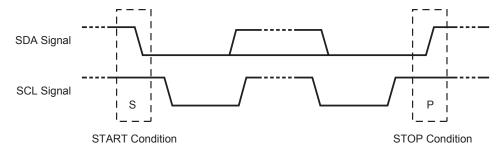

| I <sup>2</sup> C Serial I/O Interface                                |     |

| I <sup>2</sup> C General Characteristics                             |     |

| Transferring Data                                                    |     |

| Clock Synchronization                                                |     |

| I2C Registers                                                        |     |

| Zilog Debug Interface                                                | 162 |

| 4.11.00 DEDUG 111611616                                              | 102 |

PS015313-0508 Table of Contents

### eZ80F92/eZ80F93 Product Specification

| Introduction                                                   |     |

|----------------------------------------------------------------|-----|

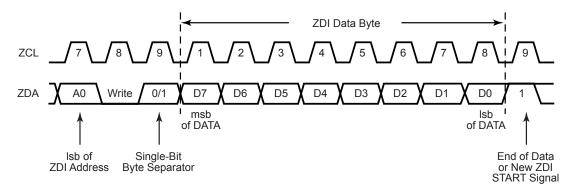

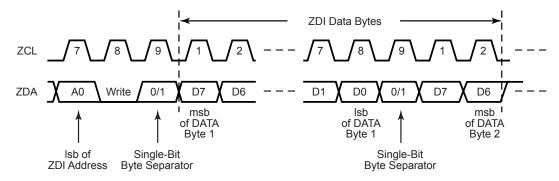

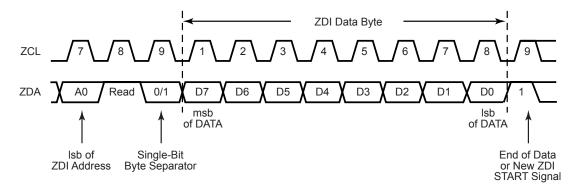

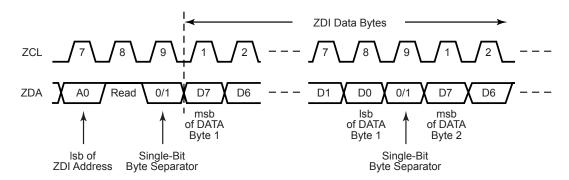

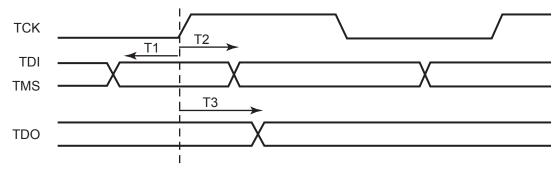

| ZDI-Supported Protocol                                         | 163 |

| ZDI Clock and Data Conventions                                 | 164 |

| ZDI Start Condition                                            | 164 |

| ZDI Register Addressing                                        | 165 |

| ZDI Write Operations                                           |     |

| ZDI Read Operations                                            |     |

| Operation of the eZ80F92 Device During ZDI Breakpoints         |     |

| Bus Requests During ZDI DEBUG Mode                             | 169 |

| ZDI Write Only Registers                                       |     |

| ZDI Read Only Registers                                        |     |

| ZDI Register Definitions                                       | 171 |

| On-Chip Instrumentation                                        | 187 |

| Introduction to On-Chip Instrumentation                        |     |

| OCI Activation                                                 | 187 |

| OCI Interface                                                  | 188 |

| OCI Information Requests                                       | 189 |

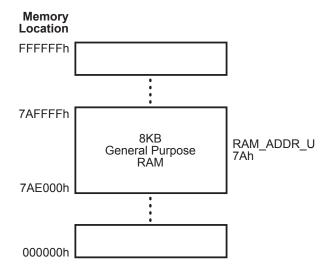

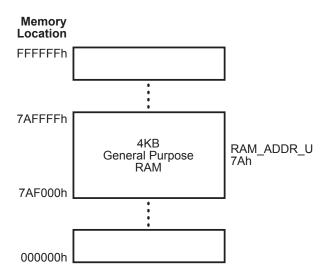

| Random Access Memory                                           | 190 |

| RAM Control Registers                                          |     |

| · ·                                                            |     |

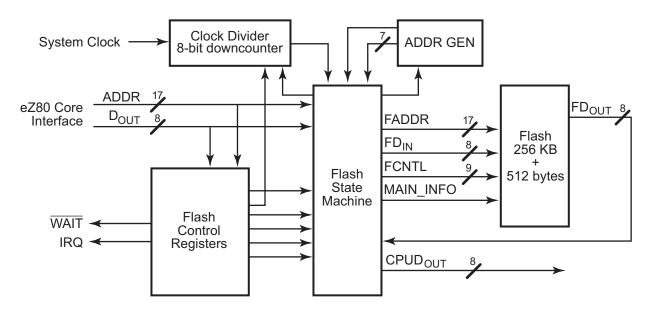

| Flash Memory                                                   |     |

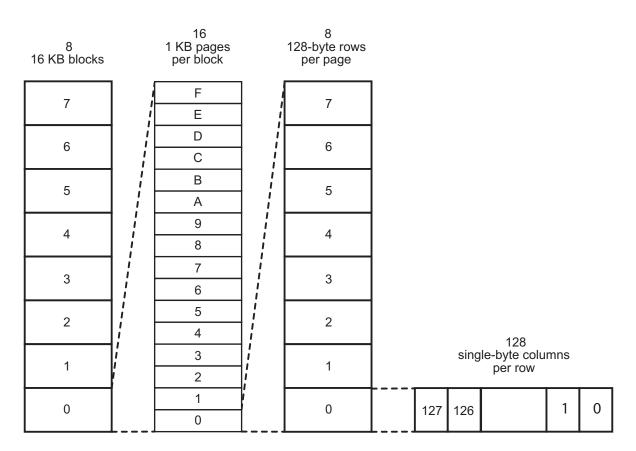

| Flash Memory Arrangement in eZ80F92                            |     |

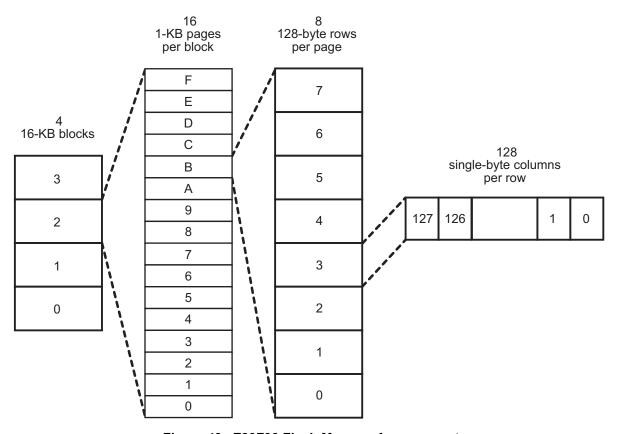

| Flash Memory Arrangement in the eZ80F93                        |     |

| Flash Memory Overview                                          |     |

| Programming Flash Memory                                       |     |

| Erasing Flash Memory                                           |     |

| Flash Control Registers                                        |     |

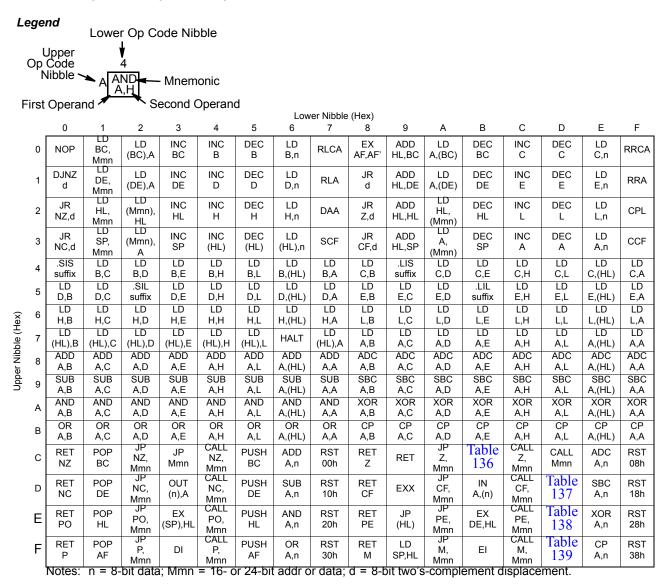

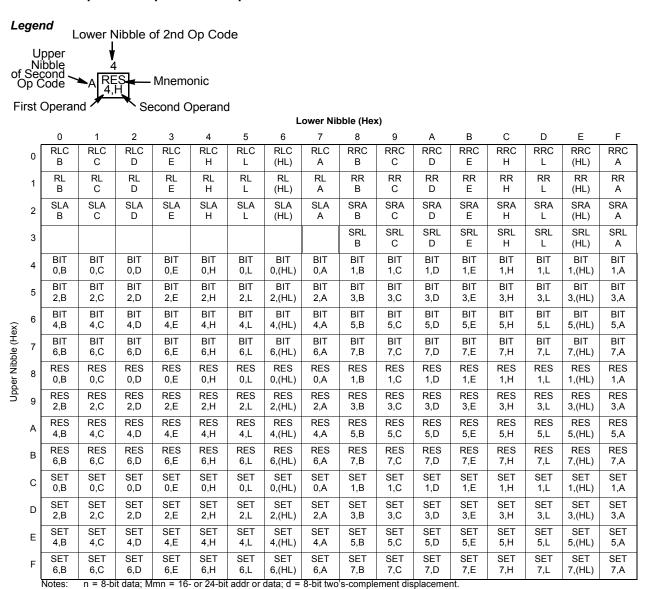

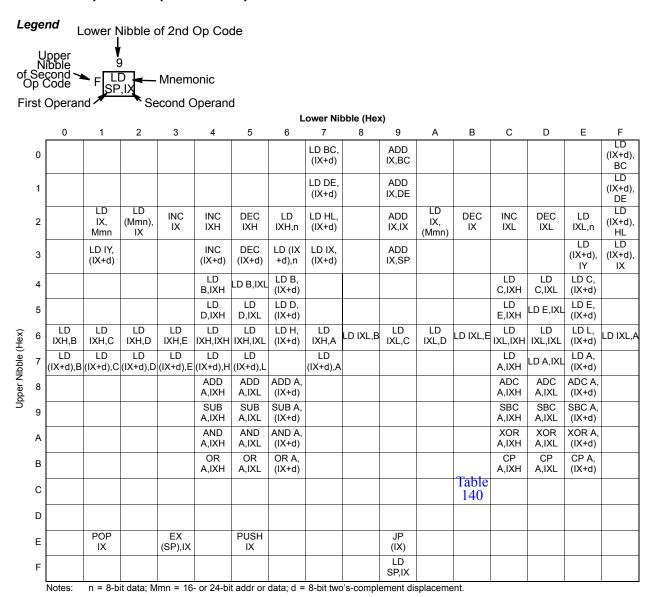

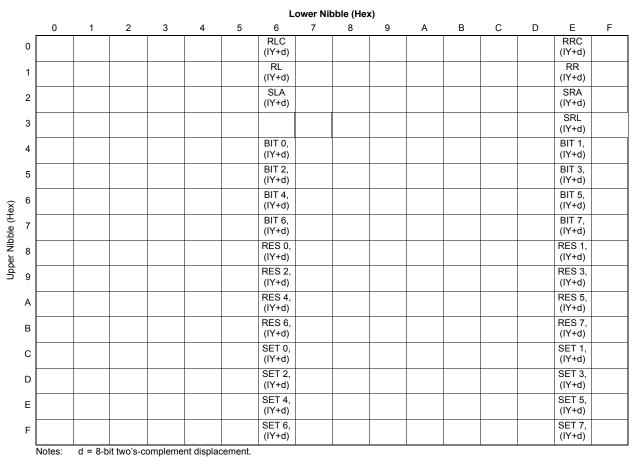

| eZ80 <sup>®</sup> CPU Instruction Set                          | 208 |

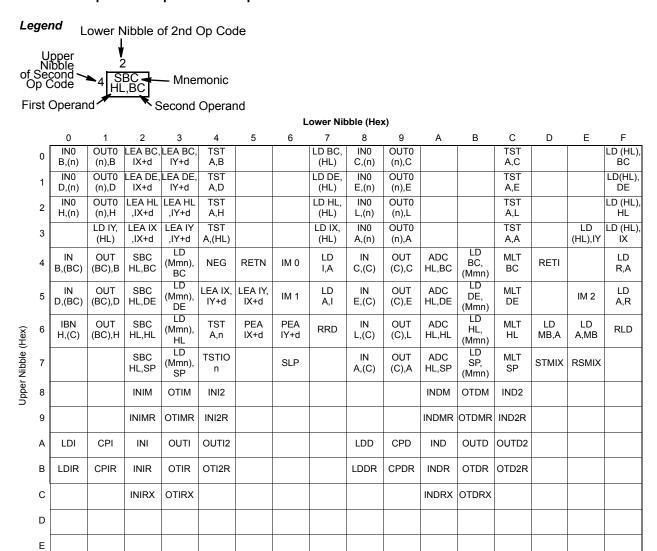

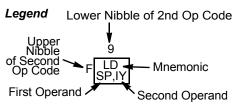

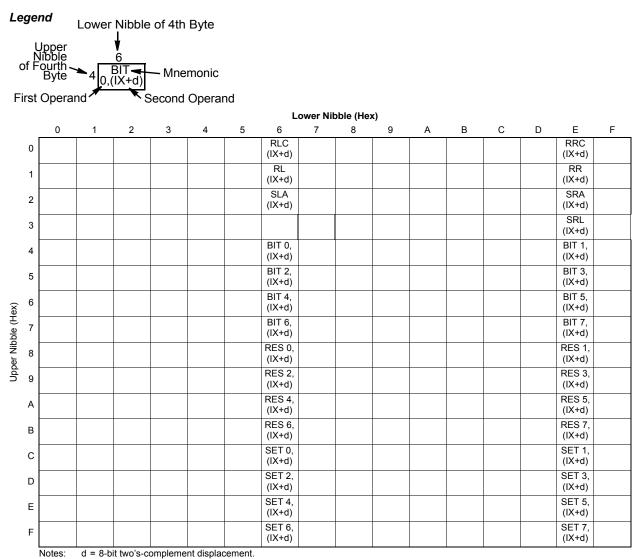

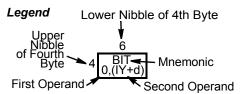

| Op-Code Map                                                    | 213 |

| On-Chip Oscillators                                            |     |

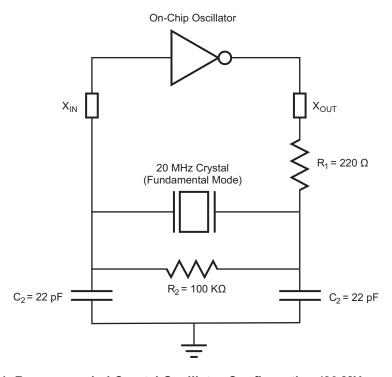

| 20 MHz Primary Crystal Oscillator Operation                    |     |

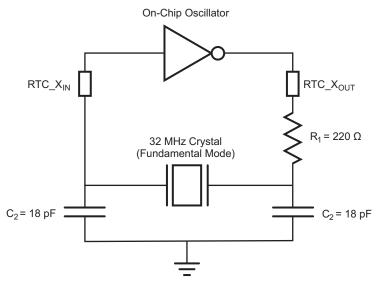

| 32 kHz Real-Time Clock Crystal Oscillator Operation            |     |

|                                                                |     |

| Electrical Characteristics                                     |     |

| Absolute Maximum Ratings                                       |     |

| DC Characteristics                                             |     |

| POR and VBO Electrical Characteristics                         |     |

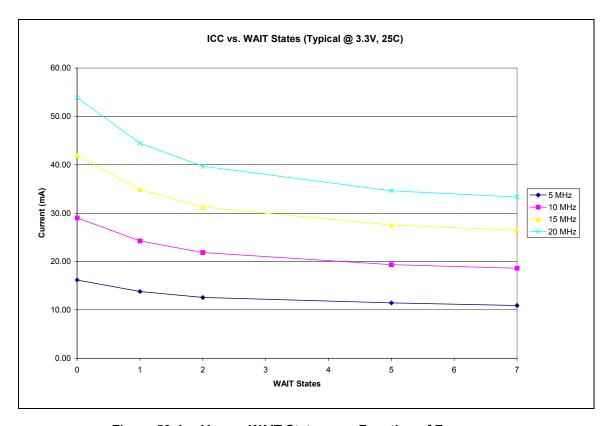

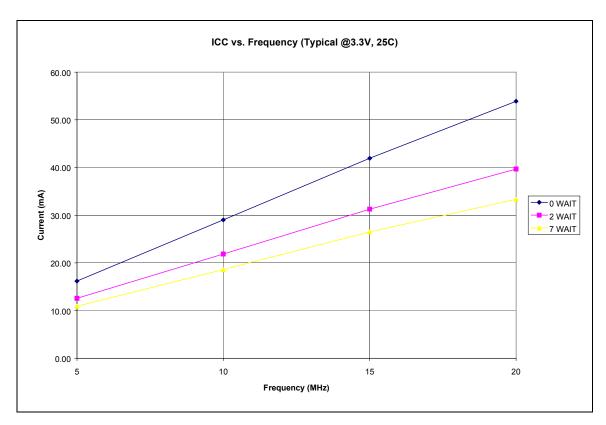

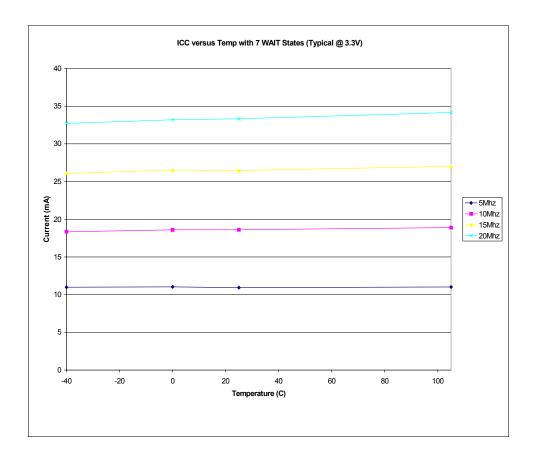

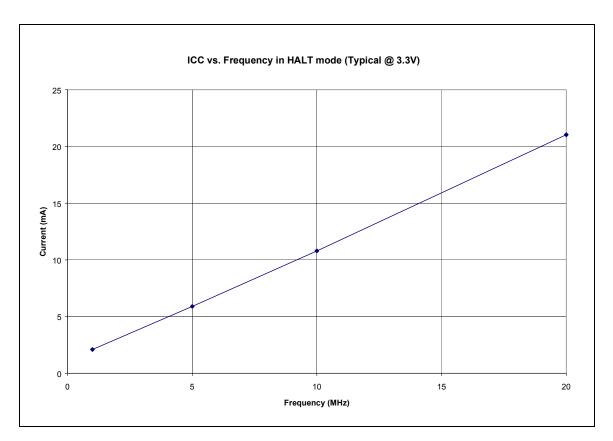

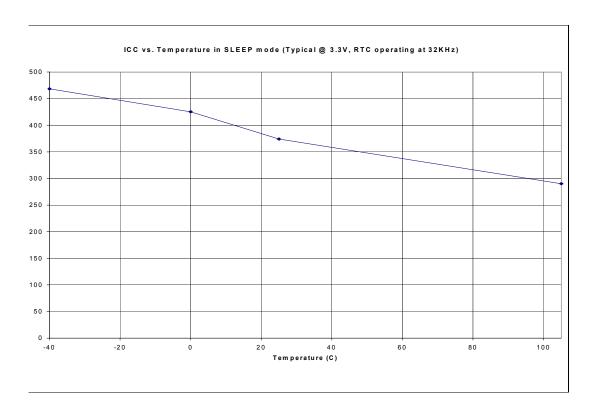

| Typical Current Consumption Under Various Operating Conditions | 224 |

| AC Characteristics                                             |     |

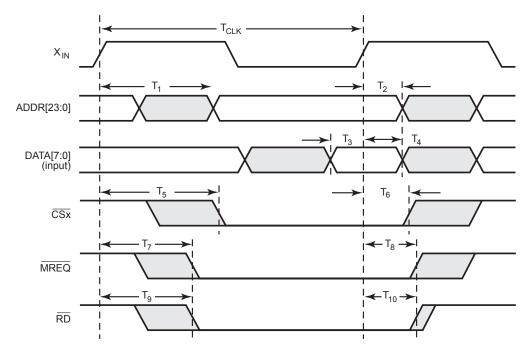

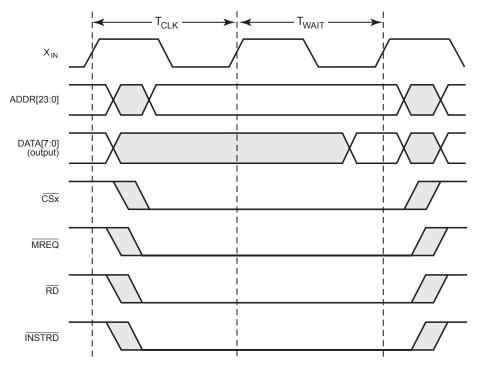

| External Memory Read Timing                                    |     |

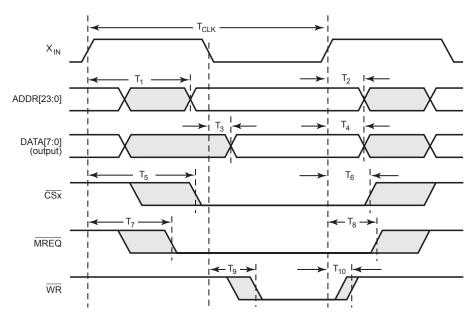

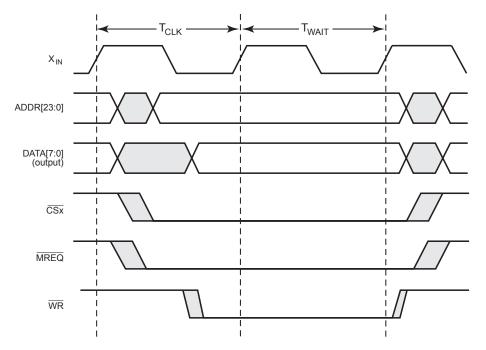

| External Memory Write Timing                                   | 231 |

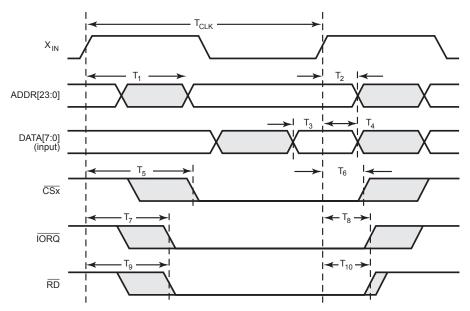

| External I/O Read Timing                                       |     |

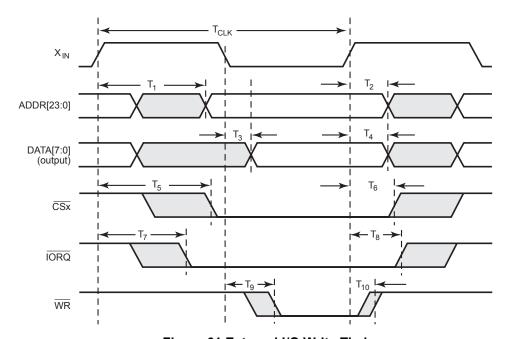

| External I/O Write Timing                                      |     |

| Wait State Timing for Read Operations                          |     |

| Wait State Timing for Write Operations                         |     |

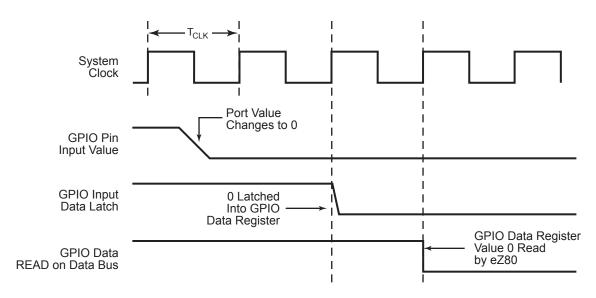

| General Purpose I/O Port Input Sample Timing                   | 237 |

PS015313-0508 Table of Contents

### eZ80F92/eZ80F93 Product Specification

| External Bus Acknowledge Timing           | 238 |

|-------------------------------------------|-----|

| External System Clock Driver (PHI) Timing | 238 |

| Zilog Debug Interface Timing              | 239 |

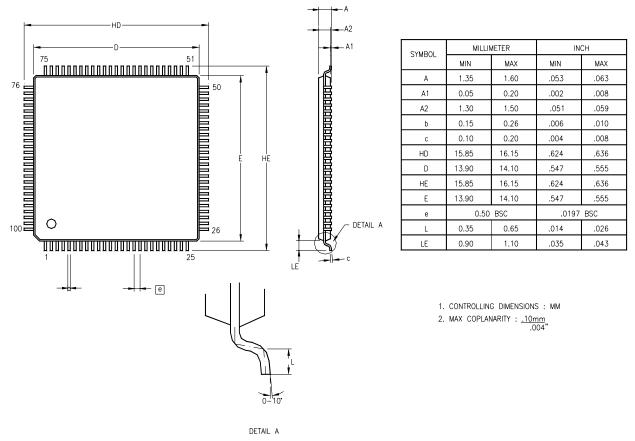

| Packaging                                 | 240 |

| Ordering Information                      | 241 |

| Part Number Description                   | 241 |

| Index                                     | 243 |

| Customer Support                          | 253 |

PS015313-0508 Table of Contents

## **Architectural Overview**

Zilog's eZ80F92 device is a high-speed single-cycle instruction-fetch microcontroller with a maximum clock speed of 20 MHz. It is the first member of Zilog's new eZ80Acclaim!® product family, which offers on-chip Flash program memory.

The eZ80F92 device can operate in Z80<sup>®</sup> compatible addressing mode (64 KB) or full 24-bit addressing mode (16 MB). The rich peripheral set of the eZ80F92 device makes it suitable for a variety of applications including industrial control, embedded communication, and point-of-sale terminals.

**Note:** Additionally, Zilog offers the eZ80F93 device, which features scaled-down memory options. For clarity, this document refers to both devices collectively as the eZ80F92 device, unless otherwise specified.

#### **Features**

The features of eZ80F92/eZ80F93 device include:

- Single-cycle instruction fetch, high-performance, pipelined eZ80<sup>®</sup> CPU core<sup>1</sup>

- eZ80F92 contains 128 KB Flash memory and 8 KB SRAM

- eZ80F93 contains 64 KB Flash memory and 4 KB SRAM

- Low power features including SLEEP mode, HALT mode, and selective peripheral power-down control

- Two UARTs with independent baud rate generators

- SPI with independent clock rate generator

- I<sup>2</sup>C with independent clock rate generator

- IrDA-compliant infrared encoder/decoder

- New DMA-like CPU instructions for efficient block data transfer

- Glueless external peripheral interface with 4 Chip Selects, individual Wait State generators, and an external WAIT input pin—supports Z80-, Intel-, and Motorolastyle buses

- Fixed-priority vectored interrupts (both internal and external) and interrupt controller

- Real-Time Clock with on-chip 32 kHz oscillator, selectable 50/60 Hz input, and separate V<sub>DD</sub> pin for battery backup

- Six 16-bit Counter/Timers with clock dividers and direct input/output drive

<sup>1.</sup> For simplicity, the term  $eZ80^{\text{@}}$  CPU is referred to as CPU for the bulk of this document.

- Watchdog Timer (WDT)

- 24 bits of General-Purpose I/O and ZDI debug interfaces

- 100-pin LQFP package

- 3.0–3.6 V supply voltage with 5V tolerant inputs

- Operating Temperature Range:

- Standard: 0 °C to +70 °C

- Extended: -40 °C to +105 °C

**Note:** All signals with an overline are active Low. For example,  $B/\overline{W}$ , for which WORD is active Low, and  $\overline{B}/W$ , for which BYTE is active Low.

Power connections follow these conventional descriptions:

| Connection | Circuit  | Device      |

|------------|----------|-------------|

| Power      | $V_{CC}$ | $V_{ m DD}$ |

| Ground     | GND      | $V_{ m SS}$ |

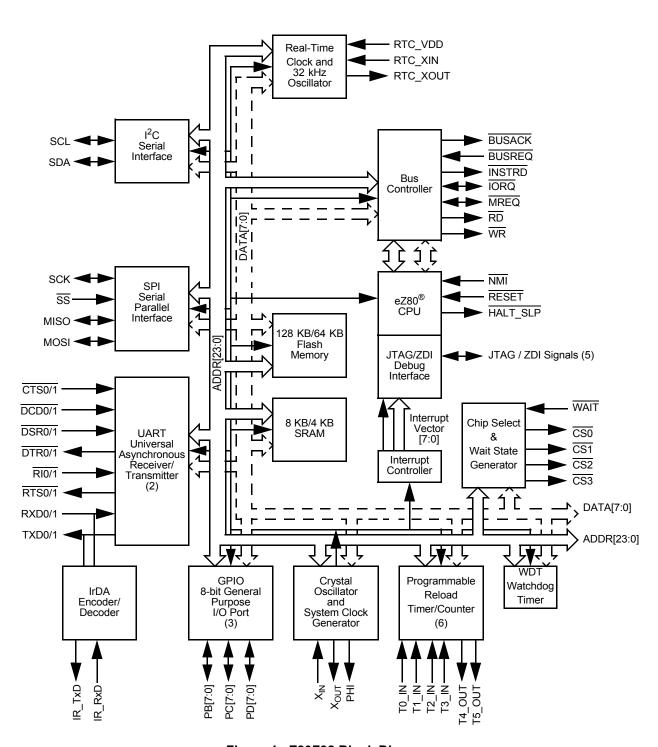

### **Block Diagram**

Figure 1 on page 3 displays the block diagram of the eZ80F92 processor.

Figure 1.eZ80F92 Block Diagram

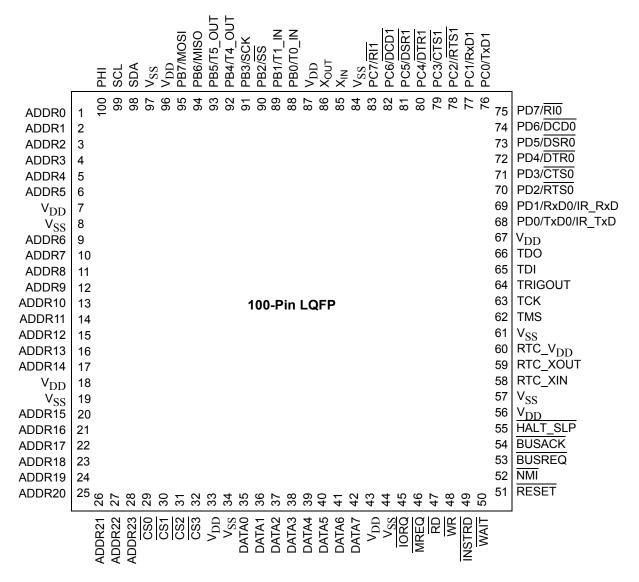

#### **Pin Description**

Figure 2 displays the pin layout of the eZ80F92 device in the 100-pin LQFP package. Table 1 on page 5 lists the pins and their functions.

Figure 2.100-Pin LQFP Configuration of the eZ80F92 Device

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device

| Pin N | o Symbol | Function    | Signal Direction | Description                                                                                                                                                                                                                                                     |

|-------|----------|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | ADDR0    | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 2     | ADDR1    | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 3     | ADDR2    | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 4     | ADDR3    | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 5     | ADDR4    | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol   | Function     | Signal Direction | Description                                                                                                                                                                                                                                                     |

|--------|----------|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6      | ADDR5    | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 7      | $V_{DD}$ | Power Supply |                  | Power Supply.                                                                                                                                                                                                                                                   |

| 8      | $V_{SS}$ | Ground       |                  | Ground.                                                                                                                                                                                                                                                         |

| 9      | ADDR6    | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 10     | ADDR7    | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 11     | ADDR8    | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 12     | ADDR9    | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol          | Function     | Signal Direction | Description                                                                                                                                                                                                                                                     |

|--------|-----------------|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13     | ADDR10          | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 14     | ADDR11          | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 15     | ADDR12          | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 16     | ADDR13          | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 17     | ADDR14          | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 18     | V <sub>DD</sub> | Power Supply |                  | Power Supply.                                                                                                                                                                                                                                                   |

| 19     | $V_{SS}$        | Ground       |                  | Ground.                                                                                                                                                                                                                                                         |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin N | o Symbol | Function    | Signal Direction | Description                                                                                                                                                                                                                                                     |

|-------|----------|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20    | ADDR15   | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 21    | ADDR16   | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 22    | ADDR17   | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 23    | ADDR18   | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 24    | ADDR19   | Address Bus | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol | Function      | Signal Direction   | Description                                                                                                                                                                                                                                                     |

|--------|--------|---------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25     | ADDR20 | Address Bus   | Bidirectional      | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 26     | ADDR21 | Address Bus   | Bidirectional      | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 27     | ADDR22 | Address Bus   | Bidirectional      | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 28     | ADDR23 | Address Bus   | Bidirectional      | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

| 29     | CS0    | Chip Select 0 | Output, Active Low | CS0 Low indicates that an access is occurring in the defined CS0 memory or I/O address space.                                                                                                                                                                   |

| 30     | CS1    | Chip Select 1 | Output, Active Low | CS1 Low indicates that an access is occurring in the defined CS1 memory or I/O address space.                                                                                                                                                                   |

| 31     | CS2    | Chip Select 2 | Output, Active Low | CS2 Low indicates that an access is occurring in the defined CS2 memory or I/O address space.                                                                                                                                                                   |

| 32     | CS3    | Chip Select 3 | Output, Active Low | CS3 Low indicates that an access is occurring in the defined CS3 memory or I/O address space.                                                                                                                                                                   |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin N | No Symbol       | Function     | Signal Direction | Description                                                                                                                                                   |

|-------|-----------------|--------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33    | V <sub>DD</sub> | Power Supply |                  | Power Supply.                                                                                                                                                 |

| 34    | V <sub>SS</sub> | Ground       |                  | Ground.                                                                                                                                                       |

| 35    | DATA0           | Data Bus     | Bidirectional    | The data bus transfers data to and from I/O and memory devices. The eZ80Acclaim!® drives these lines only during Write cycles when the CPU is the bus master. |

| 36    | DATA1           | Data Bus     | Bidirectional    | The data bus transfers data to and from I/O and memory devices. The CPU drives these lines only during Write cycles when the CPU is the bus master.           |

| 37    | DATA2           | Data Bus     | Bidirectional    | The data bus transfers data to and from I/O and memory devices. The CPU drives these lines only during Write cycles when the CPU is the bus master.           |

| 38    | DATA3           | Data Bus     | Bidirectional    | The data bus transfers data to and from I/O and memory devices. The CPU drives these lines only during Write cycles when the CPU is the bus master.           |

| 39    | DATA4           | Data Bus     | Bidirectional    | The data bus transfers data to and from I/O and memory devices. The CPU drives these lines only during Write cycles when the CPU is the bus master.           |

| 40    | DATA5           | Data Bus     | Bidirectional    | The data bus transfers data to and from I/O and memory devices. The CPU drives these lines only during Write cycles when the CPU is the bus master.           |

| 41    | DATA6           | Data Bus     | Bidirectional    | The data bus transfers data to and from I/O and memory devices. The CPU drives these lines only during Write cycles when the CPU is the bus master.           |

| 42    | DATA7           | Data Bus     | Bidirectional    | The data bus transfers data to and from I/O and memory devices. The CPU drives these lines only during Write cycles when the CPU is the bus master.           |

| 43    | V <sub>DD</sub> | Power Supply |                  | Power Supply.                                                                                                                                                 |

| 44    | V <sub>SS</sub> | Ground       |                  | Ground.                                                                                                                                                       |

|       |                 |              |                  |                                                                                                                                                               |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No Symbol |        | Function                      | Signal Direction                     | Description                                                                                                                                                                                                                                              |

|---------------|--------|-------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45            | ĪORQ   | Input/Output<br>Request       | Bidirectional, Active<br>Low         | IORQ indicates that the CPU is accessing a location in I/O space. RD and WR indicate the type of access. It is an input in bus acknowledge cycles.                                                                                                       |

| 46            | MREQ   | Memory<br>Request             | Bidirectional, Active<br>Low         | MREQ Low indicates that the CPU is accessing a location in memory. The RD, WR, and INSTRD signals indicate the type of access. It is an input in bus acknowledge cycles.                                                                                 |

| 47            | RD     | Read                          | Output, Active Low                   | RD Low indicates that the CPU is reading from the current address location. This pin is tristated during bus acknowledge cycles.                                                                                                                         |

| 48            | WR     | Write                         | Output, Active Low                   | WR indicates that the CPU is writing to the current address location. This pin is tristated during bus acknowledge cycles.                                                                                                                               |

| 49            | INSTRD | Instruction<br>Read Indicator | Output, Active Low                   | INSTRD (with MREQ and RD) indicates the CPU is fetching an instruction from memory. This pin is tristated during bus acknowledge cycles.                                                                                                                 |

| 50            | WAIT   | WAIT Request                  | Input, Active Low                    | Driving the WAIT pin Low forces the CPU to wait additional clock cycles for an external peripheral or external memory to complete its Read or Write operation.                                                                                           |

| 51            | RESET  | System Reset                  | Schmitt Trigger Input,<br>Active Low | This signal is used to initialize the CPU. This input must be Low for a minimum of 3 system clock cycles, and must be held Low until the clock is stable. This input includes a Schmitt trigger to allow RC rise times.                                  |

| 52            | NMI    | Nonmaskable<br>Interrupt      | Schmitt Trigger Input,<br>Active Low | The NMI input is a higher priority input than the maskable interrupts. It is always recognized at the end of an instruction, regardless of the state of the interrupt enable control bits. This input includes a Schmitt trigger to allow RC rise times. |

| 53            | BUSREQ | Bus Request                   | Input, Active Low                    | External devices can request the CPU to release the memory interface bus for their use, by driving this pin Low.                                                                                                                                         |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol               | Function                             | Signal Direction   | Description                                                                                                                                                                                                                                       |  |  |

|--------|----------------------|--------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 54     | BUSACK               | Bus<br>Acknowledge                   | Output, Active Low | The CPU responds to a Low on BUSREQ, by tristating the address, data, and control signals, and by driving the BUSACK line Low. During bus acknowledge cycles ADDR[23:0], IORQ, and MREQ are inputs.                                               |  |  |

| 55     | HALT_SLP             | HALT and<br>SLEEP<br>Indicator       | Output, Active Low | A Low on this pin indicates that the CPU has entered either HALT or SLEEP mode because of execution of either a HALT or SLP instruction.                                                                                                          |  |  |

| 56     | V <sub>DD</sub>      | Power Supply                         |                    | Power Supply.                                                                                                                                                                                                                                     |  |  |

| 57     | V <sub>SS</sub>      | Ground                               |                    | Ground.                                                                                                                                                                                                                                           |  |  |

| 58     | RTC_X <sub>IN</sub>  | Real-Time<br>Clock Crystal<br>Input  | Input              | This pin is the input to the low-power 32 kHz crystal oscillator for the Real-Time Clock.                                                                                                                                                         |  |  |

| 59     | RTC_X <sub>OUT</sub> | Real-Time<br>Clock Crystal<br>Output | Bidirectional      | This pin is the output from the low-power 32 kHz crystal oscillator for the Real-Time Clock. This pin is an input when the RTC is configured to operate from 50/60 Hz input clock signals and the 32 kHz crystal oscillator is disabled.          |  |  |

| 60     | RTC_V <sub>DD</sub>  | Real-Time<br>Clock Power<br>Supply   |                    | Power supply for the Real-Time Clock and associated 32 kHz oscillator. Isolated from the power supply to the remainder of the chip. A battery can be connected to this pin to supply constant power to the Real-Time Clock and 32 kHz oscillator. |  |  |

| 61     | V <sub>SS</sub>      | Ground                               |                    | Ground.                                                                                                                                                                                                                                           |  |  |

| 62     | TMS                  | JTAG Test<br>Mode Select             | Input              | JTAG Mode Select Input.                                                                                                                                                                                                                           |  |  |

| 63     | TCK                  | JTAG Test<br>Clock                   | Input              | JTAG and ZDI clock input.                                                                                                                                                                                                                         |  |  |

| 64     | TRIGOUT              | JTAG Test<br>Trigger Output          | Output             | Active High trigger event indicator.                                                                                                                                                                                                              |  |  |

| 65     | TDI                  | JTAG Test<br>Data In                 | Bidirectional      | JTAG data input pin. Functions as ZDI data I/O pin when JTAG is disabled.                                                                                                                                                                         |  |  |

| 66     | TDO                  | JTAG Test<br>Data Out                | Output             | JTAG data output pin.                                                                                                                                                                                                                             |  |  |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol          | Function              | Signal Direction   | Description                                                                                                                                                                                                                                                                                             |

|--------|-----------------|-----------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 67     | V <sub>DD</sub> | Power Supply          |                    | Power Supply.                                                                                                                                                                                                                                                                                           |

| 68     | PD0             | GPIO Port D           | Bidirectional      | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port D pin, when programmed as output, can be selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|        | TxD0            | UART<br>Transmit Data | Output             | This pin is used by the UART to transmit asynchronous serial data. This signal is multiplexed with PD0.                                                                                                                                                                                                 |

|        | IR_TxD          | IrDA Transmit<br>Data | Output             | This pin is used by the IrDA encoder/<br>decoder to transmit serial data. This signal<br>is multiplexed with PD0.                                                                                                                                                                                       |

| 69     | PD1             | GPIO Port D           | Bidirectional      | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port D pin, when programmed as output, can be selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|        | RxD0            | Receive Data          | Input              | This pin is used by the UART to receive asynchronous serial data. This signal is multiplexed with PD1.                                                                                                                                                                                                  |

|        | IR_RxD          | IrDA Receive<br>Data  | Input              | This pin is used by the IrDA encoder/<br>decoder to receive serial data. This signal is<br>multiplexed with PD1.                                                                                                                                                                                        |

| 70     | PD2             | GPIO Port D           | Bidirectional      | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port D pin, when programmed as output, can be selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|        | RTS0            | Request To<br>Send    | Output, Active Low | Modem control signal from UART. This signal is multiplexed with PD2.                                                                                                                                                                                                                                    |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No Symbol |                 | Function                   | Signal Direction   | Description                                                                                                                                                                                                                                                                                             |

|---------------|-----------------|----------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71            | PD3 GPIO Port D |                            | Bidirectional      | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port D pin, when programmed as output, can be selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|               | CTS0            | Clear To Send              | Input, Active Low  | Modem status signal to the UART. This signal is multiplexed with PD3.                                                                                                                                                                                                                                   |

| 72            | PD4             | GPIO Port D                | Bidirectional      | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port D pin, when programmed as output, can be selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|               | DTR0            | Data Terminal<br>Ready     | Output, Active Low | Modem control signal to the UART. This signal is multiplexed with PD4.                                                                                                                                                                                                                                  |

| 73            | PD5             | PD5 GPIO Port D Bidirectio |                    | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port D pin, when programmed as output, can be selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|               | DSR0            | Data Set<br>Ready          | Input, Active Low  | Modem status signal to the UART. This signal is multiplexed with PD5.                                                                                                                                                                                                                                   |

| 74            | PD6             | GPIO Port D                | Bidirectional      | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port D pin, when programmed as output, can be selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|               | DCD0            | Data Carrier<br>Detect     | Input, Active Low  | Modem status signal to the UART. This signal is multiplexed with PD6.                                                                                                                                                                                                                                   |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol | Function                  | Signal Direction  | Description                                                                                                                                                                                                                                                                                             |

|--------|--------|---------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 75     | PD7    | GPIO Port D               | Bidirectional     | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port D pin, when programmed as output, can be selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|        | RI0    | Ring Indicator            | Input, Active Low | Modem status signal to the UART. This signal is multiplexed with PD7.                                                                                                                                                                                                                                   |

| 76     | PC0    | GPIO Port C Bidirectional |                   | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port C pin, when programmed as output, can be selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        | TxD1   | Transmit Data             | Output            | This pin is used by the UART to transmit asynchronous serial data. This signal is multiplexed with PC0.                                                                                                                                                                                                 |

| 77     | PC1    | GPIO Port C               | Bidirectional     | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port C pin, when programmed as output, can be selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        | RxD1   | Receive Data              | Input             | This pin is used by the UART to receive asynchronous serial data. This signal is multiplexed with PC1.                                                                                                                                                                                                  |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol | Function                  | Signal Direction   | Description                                                                                                                                                                                                                                                                                             |

|--------|--------|---------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78     | PC2    | GPIO Port C               | Bidirectional      | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port C pin, when programmed as output, can be selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        | RTS1   | Request To<br>Send        | Output, Active Low | Modem control signal from UART. This signal is multiplexed with PC2.                                                                                                                                                                                                                                    |

| 79     | PC3    | GPIO Port C Bidirectional |                    | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port C pin, when programmed as output, can be selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        | CTS1   | Clear To Send             | Input, Active Low  | Modem status signal to the UART. This signal is multiplexed with PC3.                                                                                                                                                                                                                                   |

| 80     | PC4    | GPIO Port C Bidirectional |                    | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port C pin, when programmed as output, can be selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        | DTR1   | Data Terminal<br>Ready    | Output, Active Low | Modem control signal to the UART. This signal is multiplexed with PC4.                                                                                                                                                                                                                                  |

| 81     | PC5    | GPIO Port C               | Bidirectional      | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port C pin, when programmed as output, can be selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        | DSR1   | Data Set<br>Ready         | Input, Active Low  | Modem status signal to the UART. This signal is multiplexed with PC5.                                                                                                                                                                                                                                   |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol           | Function                             | Signal Direction  | Description                                                                                                                                                                                                                                                                                             |

|--------|------------------|--------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82     | PC6 GPIO Port C  |                                      | Bidirectional     | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port C pin, when programmed as output, can be selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        | DCD1             | Data Carrier<br>Detect               | Input, Active Low | Modem status signal to the UART. This signal is multiplexed with PC6.                                                                                                                                                                                                                                   |

| 83     | PC7              | GPIO Port C                          | Bidirectional     | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port C pin, when programmed as output, can be selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        | RI1              | Ring Indicator                       | Input, Active Low | Modem status signal to the UART. This signal is multiplexed with PC7.                                                                                                                                                                                                                                   |

| 84     | V <sub>SS</sub>  | Ground                               |                   | Ground.                                                                                                                                                                                                                                                                                                 |

| 85     | X <sub>IN</sub>  | System Clock<br>Oscillator Input     | Input             | This pin is the input to the onboard crystal oscillator for the primary system clock. If an external oscillator is used, its clock output should be connected to this pin. When a crystal is used, it should be connected between $X_{\rm IN}$ and $X_{\rm OUT}$ .                                      |

| 86     | X <sub>OUT</sub> | System Clock<br>Oscillator<br>Output | Output            | This pin is the output of the onboard crystal oscillator. When used, a crystal should be connected between ${\sf X}_{IN}$ and ${\sf X}_{OUT}$ .                                                                                                                                                         |

| 87     | $V_{DD}$         | Power Supply                         |                   | Power Supply.                                                                                                                                                                                                                                                                                           |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol | Function            | Signal Direction  | Description                                                                                                                                                                                                                                                        |

|--------|--------|---------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 88     | PB0    | GPIO Port B         | Bidirectional     | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port B pin, when programmed as output, can be selected to be an open-drain or open-source output. |

|        | T0_IN  | Timer 0 In          | Input             | Alternate clock source for Programmable Reload Timers 0 and 2. This signal is multiplexed with PB0.                                                                                                                                                                |

| 89     | PB1    | GPIO Port B         | Bidirectional     | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port B pin, when programmed as output, can be selected to be an open-drain or open-source output. |

|        | T1_IN  | Timer 1 In          | Input             | Alternate clock source for Programmable Reload Timers 1 and 3. This signal is multiplexed with PB1.                                                                                                                                                                |

| 90     | PB2    | GPIO Port B         | Bidirectional     | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port B pin, when programmed as output, can be selected to be an open-drain or open-source output. |

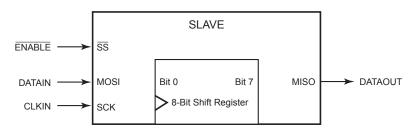

|        | SS     | Slave Select        | Input, Active Low | The slave select input line is used to select a slave device in SPI mode. This signal is multiplexed with PB2.                                                                                                                                                     |

| 91     | PB3    | GPIO Port B         | Bidirectional     | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port B pin, when programmed as output, can be selected to be an open-drain or open-source output. |

|        | SCK    | SPI Serial<br>Clock | Bidirectional     | SPI serial clock. This signal is multiplexed with PB3.                                                                                                                                                                                                             |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | Symbol                        | Function                | Signal Direction | Description                                                                                                                                                                                                                                                        |

|--------|-------------------------------|-------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 92     | PB4 GPIO Port B E             |                         | Bidirectional    | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port B pin, when programmed as output, can be selected to be an open-drain or open-source output. |

|        | T4_OUT                        | Timer 4 Out             | Output           | Programmable Reload Timer 4 timer-out signal. This signal is multiplexed with PB4.                                                                                                                                                                                 |

| 93     | PB5 GPIO Port B Bidirectional |                         | Bidirectional    | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port B pin, when programmed as output, can be selected to be an open-drain or open-source output. |

|        | T5_OUT                        | Timer 5 Out             | Output           | Programmable Reload Timer 5 timer-out signal. This signal is multiplexed with PB5.                                                                                                                                                                                 |

| 94     | PB6                           | GPIO Port B             | Bidirectional    | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port B pin, when programmed as output, can be selected to be an open-drain or open-source output. |

|        | MISO                          | Master In,<br>Slave Out | Bidirectional    | The MISO line is configured as an input when the CPU is an SPI master device and as an output when CPU is an SPI slave device. This signal is multiplexed with PB6.                                                                                                |

| 95     | PB7                           | GPIO Port B             | Bidirectional    | This pin can be used for general-purpose I/O. It can be individually programmed as input or output and can also be used individually as an interrupt input. Each Port B pin, when programmed as output, can be selected to be an open-drain or open-source output. |

|        | MOSI                          | Master Out,<br>Slave In | Bidirectional    | The MOSI line is configured as an output when the CPU is an SPI master device and as an input when the CPU is an SPI slave device. This signal is multiplexed with PB7.                                                                                            |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No Symbol |                 | Function                         | Signal Direction | Description                                                          |  |

|---------------|-----------------|----------------------------------|------------------|----------------------------------------------------------------------|--|

| 96            | V <sub>DD</sub> | Power Supply                     |                  | Power Supply.                                                        |  |

| 97            | $V_{SS}$        | Ground                           |                  | Ground.                                                              |  |

| 98            | SDA             | I <sup>2</sup> C Serial Data     | Bidirectional    | This pin carries the I <sup>2</sup> C data signal.                   |  |

| 99            | SCL             | I <sup>2</sup> C Serial<br>Clock | Bidirectional    | This pin is used to receive and transmit the I <sup>2</sup> C clock. |  |

| 100           | PHI             | System Clock                     | Output           | This pin is an output driven by the internal system clock.           |  |

#### **Pin Characteristics**

Table 2 lists the characteristics of each pin in the eZ80F92 device's 100-pin LQFP package.

Table 2. Pin Characteristics of the eZ80F92 Device

| Pin<br>No | Symbol          | Direction | Reset<br>Direction | Active<br>Low/High | Tristate<br>Output | Pull<br>Up/Down | Schmitt<br>Trigger<br>Input | Open Drain/<br>Source |

|-----------|-----------------|-----------|--------------------|--------------------|--------------------|-----------------|-----------------------------|-----------------------|

| 1         | ADDR0           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 2         | ADDR1           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 3         | ADDR2           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 4         | ADDR3           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 5         | ADDR4           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 6         | ADDR5           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 7         | V <sub>DD</sub> |           |                    |                    |                    |                 |                             |                       |

| 8         | $V_{SS}$        |           |                    |                    |                    |                 |                             |                       |

| 9         | ADDR6           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 10        | ADDR7           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 11        | ADDR8           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 12        | ADDR9           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 13        | ADDR10          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 14        | ADDR11          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 15        | ADDR12          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

Table 2. Pin Characteristics of the eZ80F92 Device (Continued)

| Pin<br>No | Symbol          | Direction | Reset<br>Direction | Active<br>Low/High | Tristate<br>Output | Pull<br>Up/Down | Schmitt<br>Trigger<br>Input | Open Drain/<br>Source |

|-----------|-----------------|-----------|--------------------|--------------------|--------------------|-----------------|-----------------------------|-----------------------|

| 16        | ADDR13          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 17        | ADDR14          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 18        | $V_{DD}$        |           |                    |                    |                    |                 |                             |                       |

| 19        | V <sub>SS</sub> |           |                    |                    |                    |                 |                             |                       |

| 20        | ADDR15          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 21        | ADDR16          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 22        | ADDR17          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 23        | ADDR18          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 24        | ADDR19          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 25        | ADDR20          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 26        | ADDR21          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 27        | ADDR22          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 28        | ADDR23          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

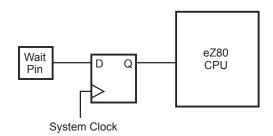

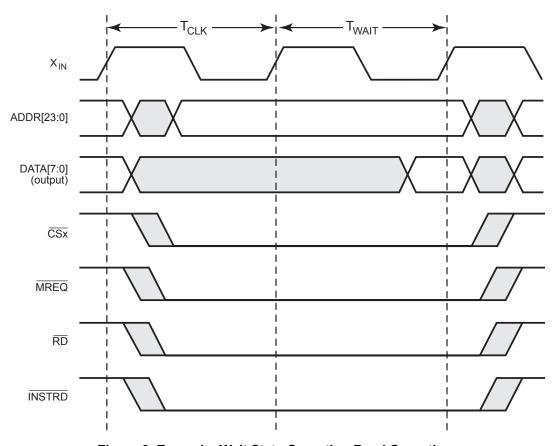

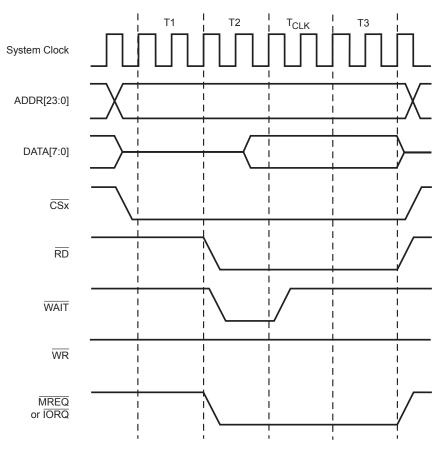

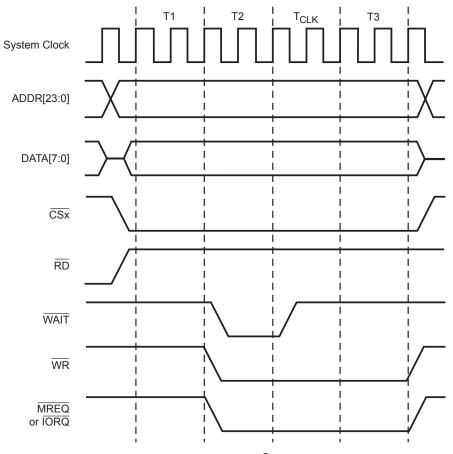

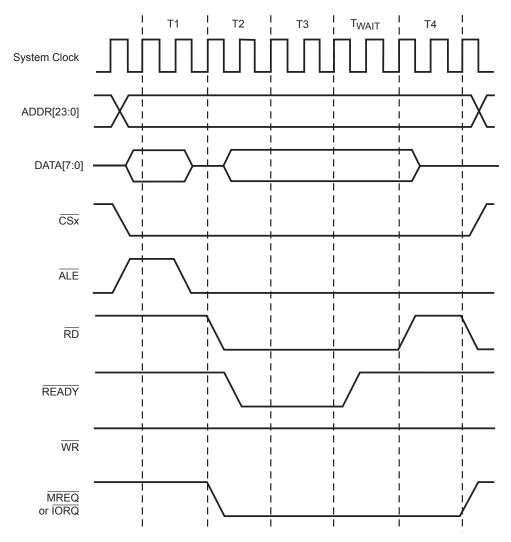

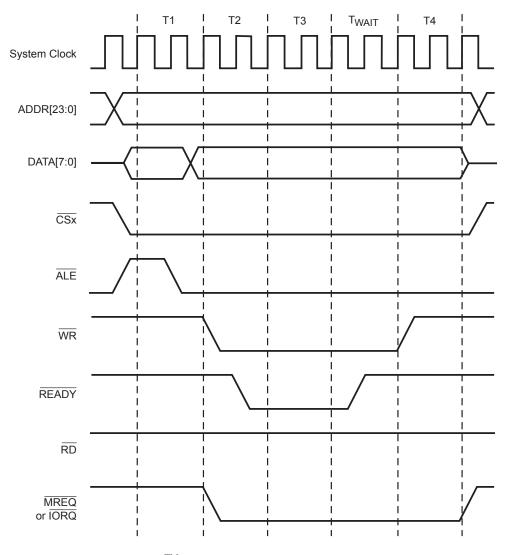

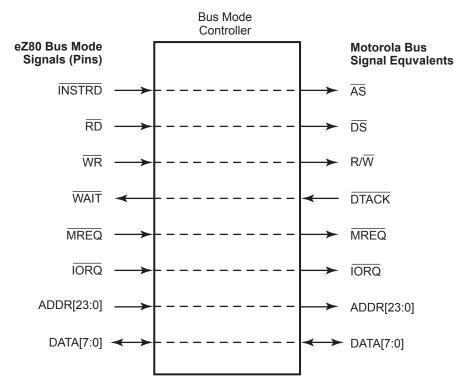

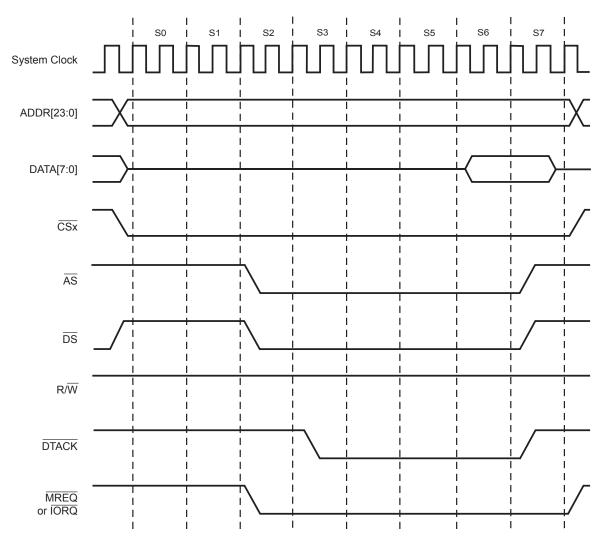

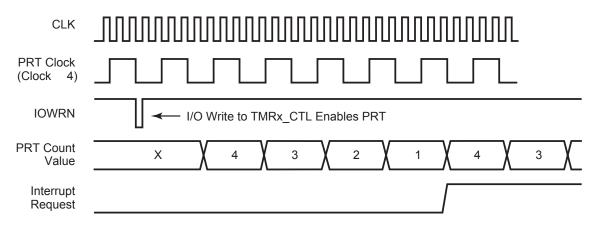

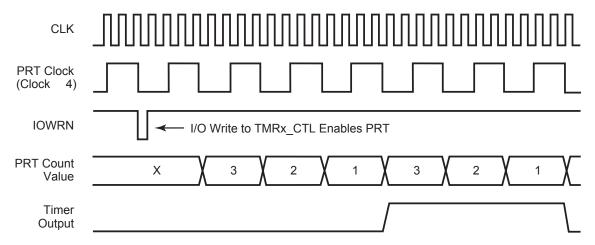

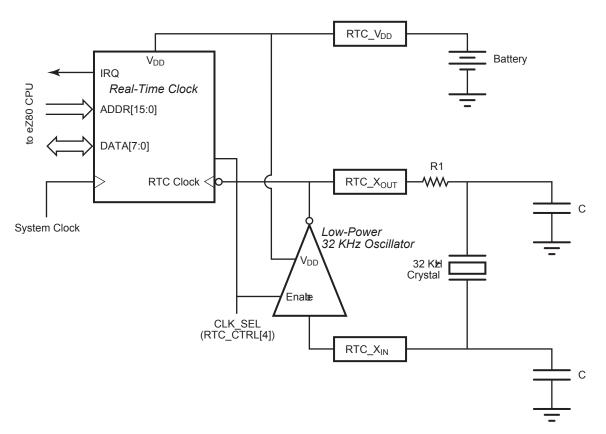

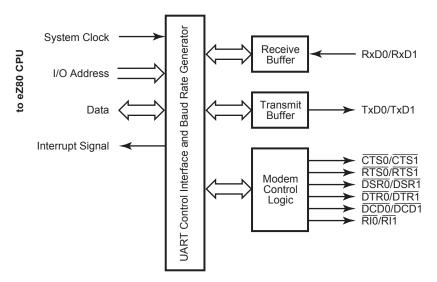

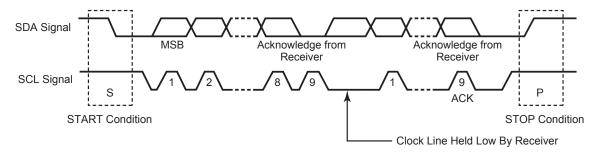

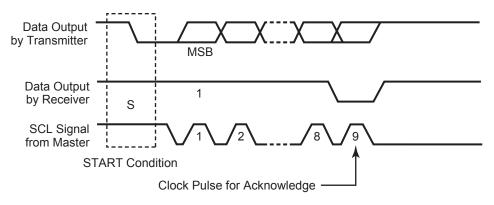

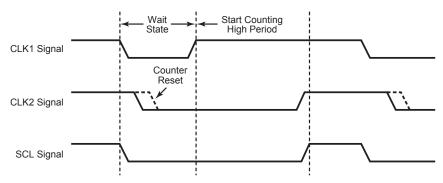

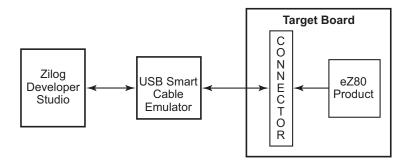

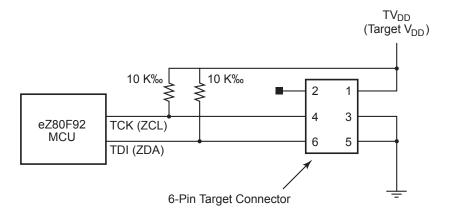

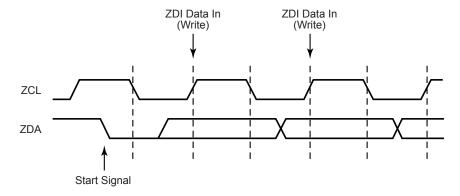

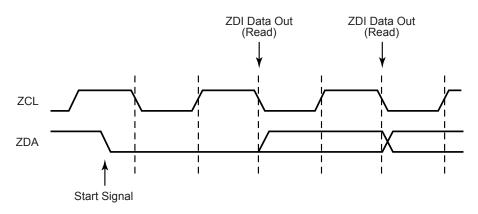

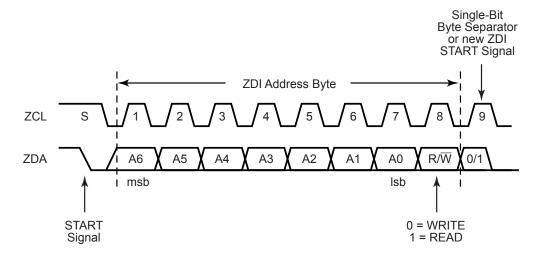

| 29        | CS0             | 0         | 0                  | Low                | No                 | No              | No                          | No                    |