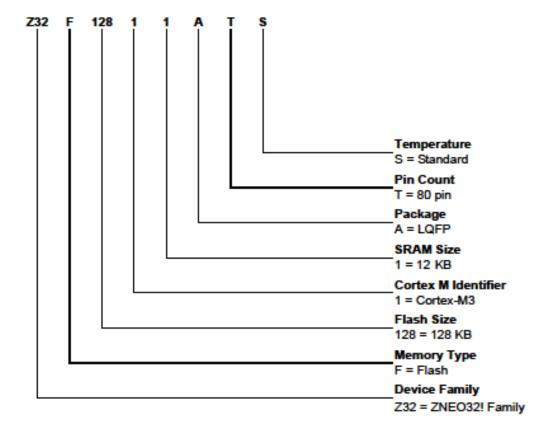

## **ZNEO32! Family of Microcontrollers**

# Z32F1281 MCU

**Product Specification**

PS034504-0617

PRELIMINARY

Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2017 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

ZNEO32! is a trademark or registered trademark of Zilog, Inc. All other product or service names are the property of their respective owners.

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Description                                                         | Page |

|-------------|-------------------|---------------------------------------------------------------------|------|

| Jun<br>2017 | 04                | Updated part numbers to include the Cortex M identifier.            | All  |

| May<br>2016 | 03                | Added Quadrature Encoder Interface information.                     | 122  |

| Apr<br>2016 | 02                | Added timing information for peripherals; global edits for clarity. | All  |

| Nov<br>2015 | 01                | Original issue.                                                     |      |

# 1. Overview

# Introduction

Zilog's Z32F1281 MCU, a member of the ZNEO32! Family of microcontrollers is a cost-effective and high-performance 32-bit microcontroller. The Z32F1281 MCU provides 3-phase PWM generator units which are suitable for inverter bridges, including motor drive systems. The two built-in channels of these generators control two inverter motors simultaneously.

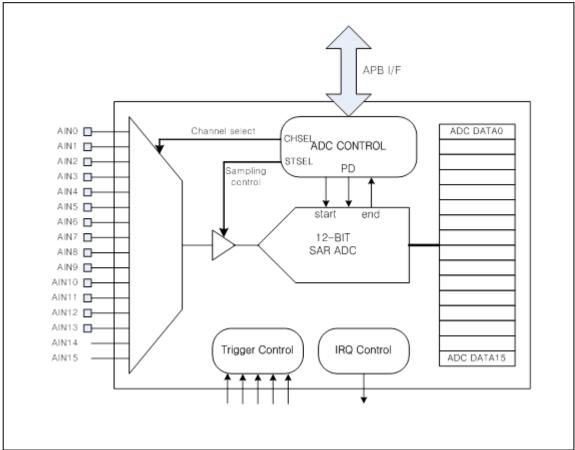

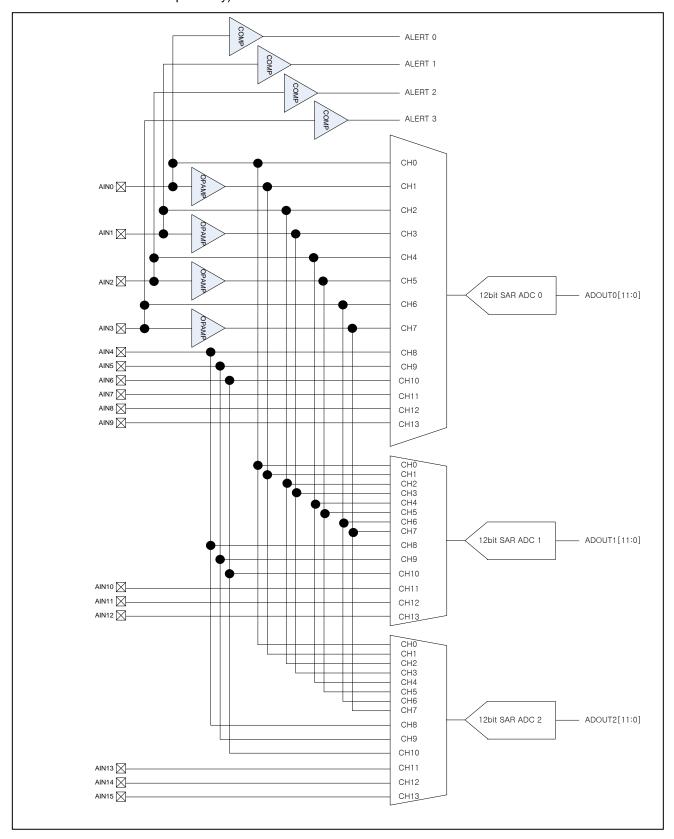

Three 12-bit high speed ADC units with 16-channel analog multiplexed inputs are included to gather information from the motor. The Z32F1281 MCU can control up to two inverter motors or one inverter motor and the Power Factor Correction (PFC) function simultaneously. Four on-chip operational AMPs and four analog comparators are available to measure analog input signals. The operational amplifier can amplify the input signal to the proper signal range and transfer it to the ADC input channel. The comparator monitors external signals and helps create an internal emergency signal. Multiple powerful external serial interface engines communicate with on-board sensors.

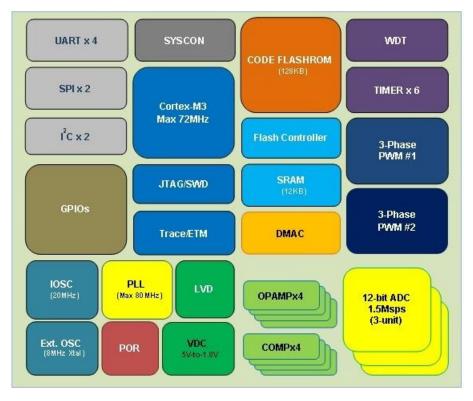

Figure 1.1 shows a block diagram of the Z32F1281 MCU.

Figure 1.1. Z32F1281 MCU Block Diagram

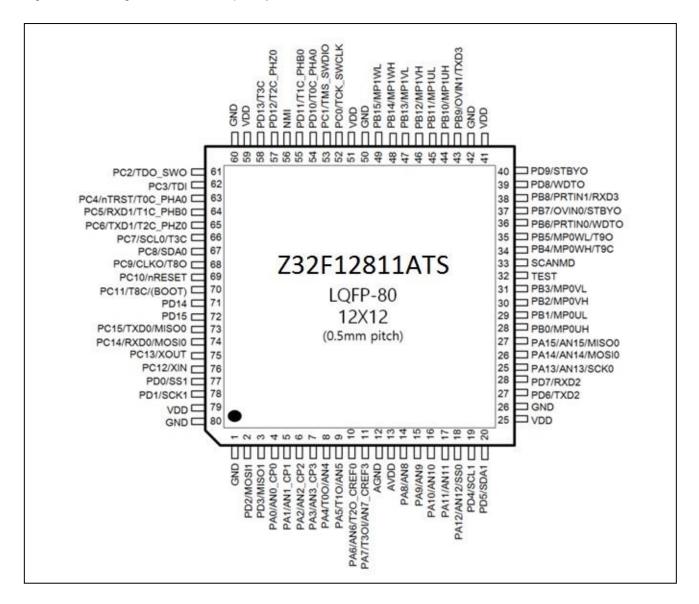

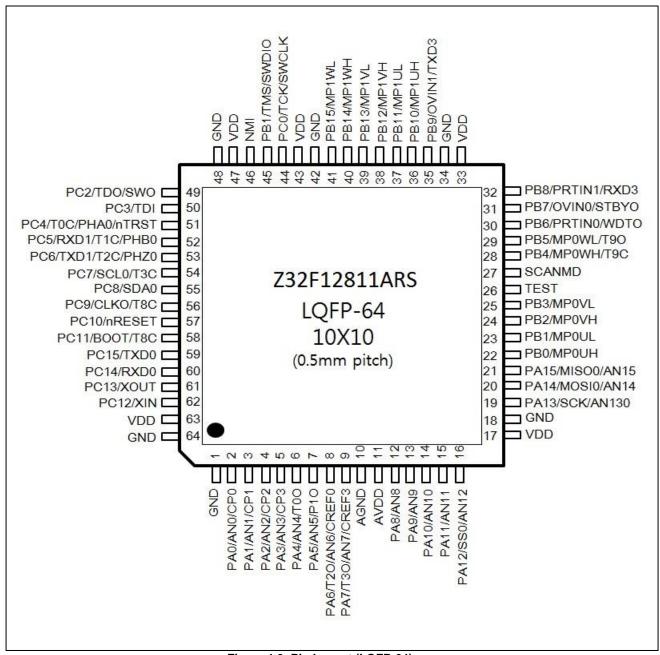

Figure 1.2 and Figure 1.3 show the pin layouts.

Figure 1.2. Pin Layout (LQFP-80)

Figure 1.3. Pin Layout (LQFP-64)

## **Product Features**

The Z32F1281 MCU offers the following features:

- High performance low-power Cortex-M3 core

- 128 KB code Flash memory with cache function

- 12 KB SRAM

- 3-Phase Motor PWM with ADC triggering function

- o 2 channels

- 1.5Msps high-speed ADC with burst conversion function

- o 2 or 3 units with 16 channel input

- Built-in Programmable Gain Amplifier (PGA) for ADC inputs

- o 4 channels

- 3 channels for 3 shunt resistor configuration

- 1 channel for 1 shunt resistor configuration

- Built-in analog comparator

- o 4 channels

- 3 channels for 3 shunt resistor configuration

- 1 channel for 1 shunt resistor configuration

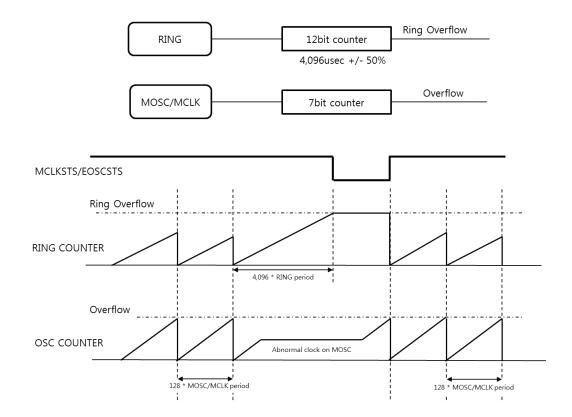

- System fail-safe function by clock monitoring

- XTAL OSC fail monitoring

- Precision internal oscillator clock (20MHz ±3%)

- Watchdog timer

- Six general purpose timers

- Quadrature encoder interface counter

- External communication ports: 4 UARTs, 2 I<sup>2</sup>Cs, 2 SPIs

- High current driving port for UART photo couplers

- Debug and emergency stop function

- Real-time monitoring function support for more effective development

- JTAG and Serial Wire Debug (SWD) in-circuit debugger

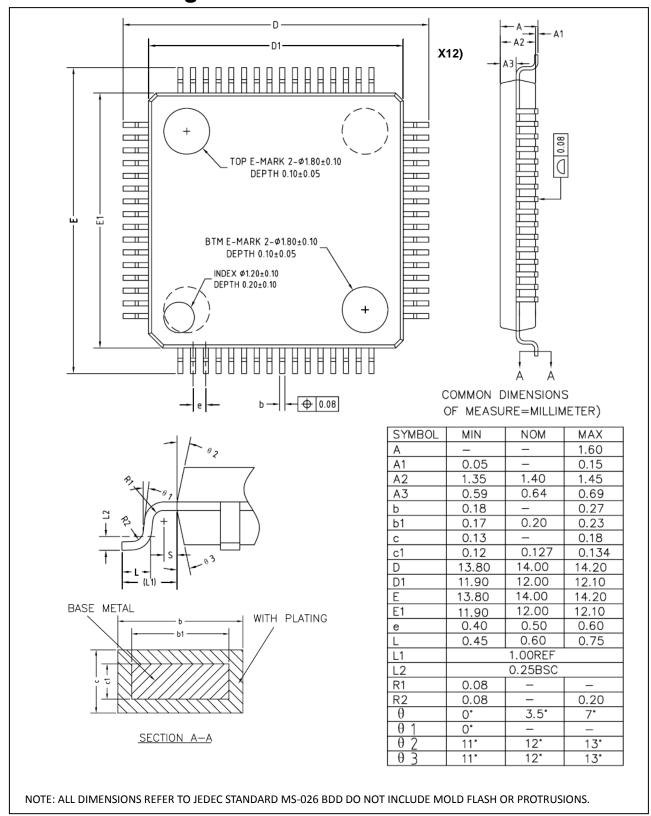

- Various memory size and package options

- o LQFP-80, LQFP-64

- Industrial grade operating temperature (-40 ~ +85 °C)

Table 1.1. Device Type

| Part Number  | Flash | SRAM | UART | SPI | I2C | MPWM | ADC    | I/O PORT | PKG     |

|--------------|-------|------|------|-----|-----|------|--------|----------|---------|

| Z32F12811ATS | 128KB | 10KD | 4    | 2   | 2   | 2    | 3-unit | 68       | LQFP-80 |

| Z32F12811ARS |       | 12KB | 2    | 2   | 1   | 2    | 16 ch  | 48       | LQFP-64 |

# **Architecture**

### **Block Diagram**

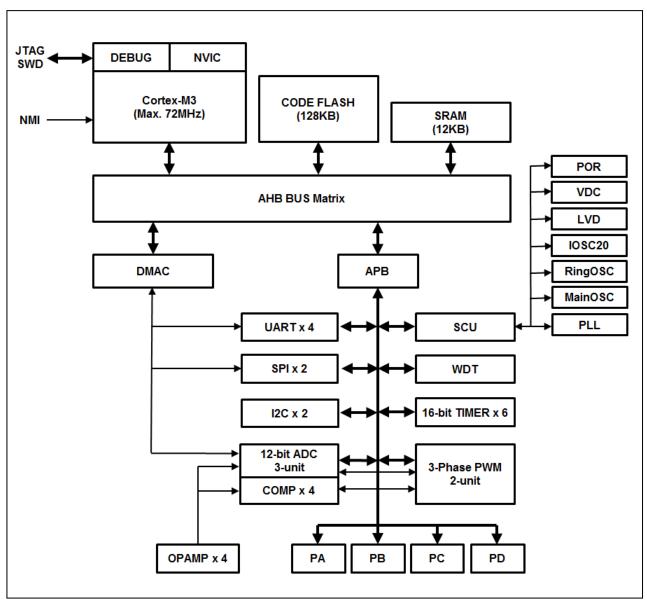

An internal block diagram of the Z32F1281 MCU is shown in Figure 1.4.

Figure 1.4. Internal Block Diagram

### **Functional Description**

The following section provides an overview of the features of the Z32F1281 microcontroller.

#### **ARM Cortex-M3**

- ARM powered Cortex-M3 Core based on v7M architecture, which is optimized for small size and low-power systems. On core system timer (SYSTICK) provides a simple 24-bit timer that makes it easy to manage the system operations

- Thumb-compatible Thumb-2 only instruction set processor core makes code high-density

- · Hardware division and single-cycle multiplication

- Integrated Nested Vectored Interrupt Controller (NVIC) provides deterministic interrupt handling

- Full featured debug solutions JTAG and SWD, FPB, DWT, ITM, and TPIU

- Maximum 72 MHz operating frequency with zero wait execution

### **Nested Vector-Interrupt Controller (NVIC)**

- The ARM Nested Vectored Interrupt Controller (NVIC) on the ARM Cortex-M3 core handles all internal and external exceptions. When an interrupt condition is detected, the processor state is automatically stored to the stack and automatically restored from the stack at the end of the interrupt service routine.

- The vector is fetched in parallel to the state saving, which enables efficient interrupt entry.

- The processor supports tail-chaining, which enables back-to-back interrupts to be performed without the overhead of state saving and restoring.

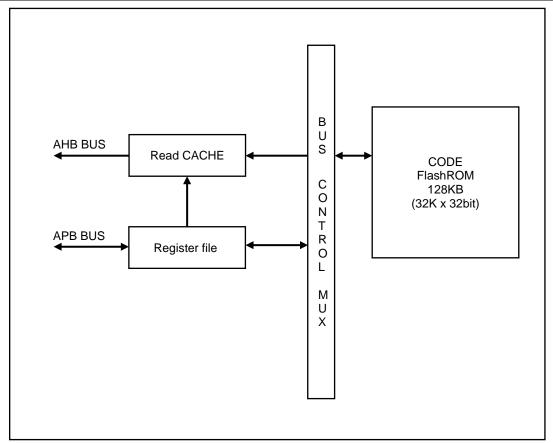

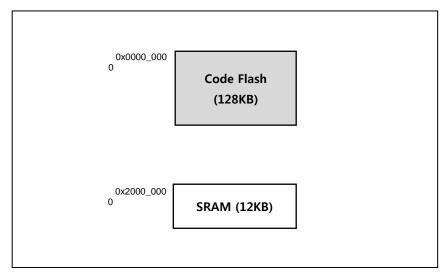

### 128 KB Internal Code Flash Memory

- The Z32F1281 MCU provides internal 128 KB code Flash memory and its controller. This is enough to program the motor algorithm and control the system. Self-programming is available and ISP and JTAG programming is also supported in Boot or Debugging Mode.

- Instruction and data cache buffer overcome the limitations of low-bandwidth Flash memory.

The CPU can execute from Flash memory with zero wait state up to 72 MHz bus frequency.

### 12 KB Zero-wait Internal SRAM

On chip 12 KB zero-wait SRAM can be used for working memory space and program code can be loaded on this SRAM.

#### **Boot Logic**

The smart boot logic supports Flash programming. The Z32F1281 MCU can be entered by external boot pin and UART and SPI programming are available in Boot Mode. UART0 or SPI0 is used in Boot mode communication.

### System Control Unit (SCU)

• The SCU block manages internal power, clock, reset and operation mode. It also controls analog blocks (INTOSC, VDC and LVD).

### 32-bit Watchdog Timer (WDT)

The watchdog timer performs the system monitoring function. It generates an internal reset or interrupt to notice an abnormal status of the system.

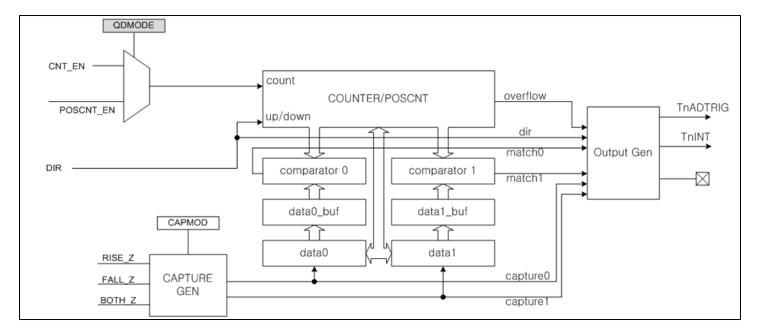

#### **Multi-purpose 16-bit Timer**

- Six-channel 16-bit general purpose timers support:

- o Periodic timer mode

- Counter mode

- PWM mode

- Capture mode

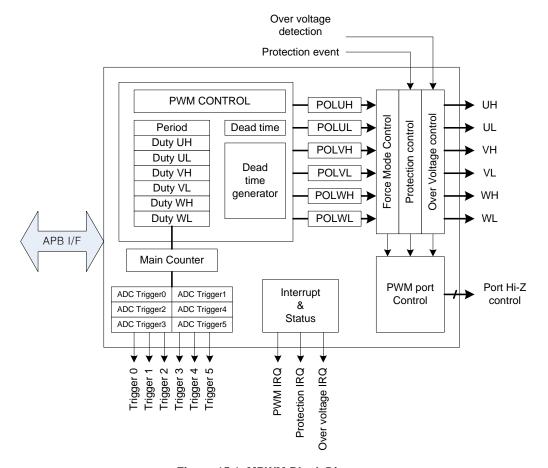

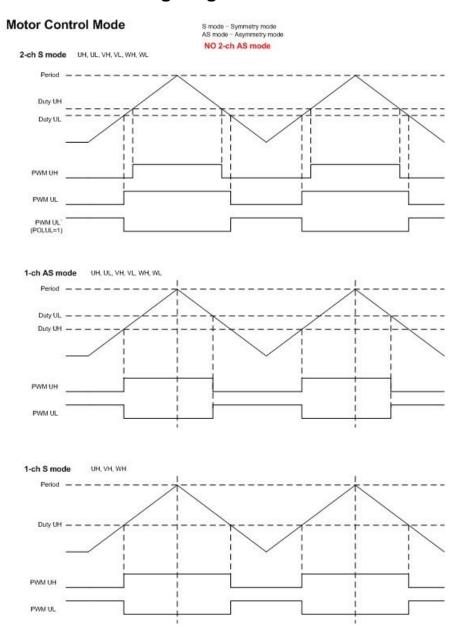

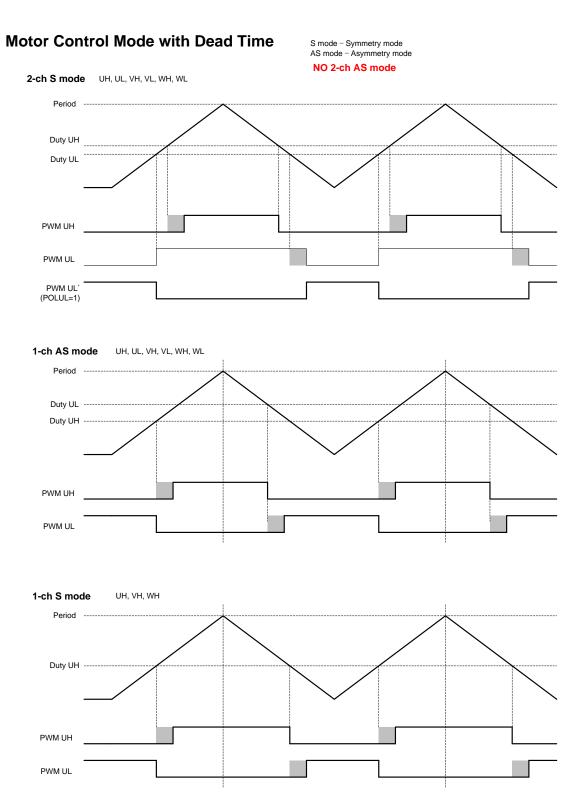

#### **PWM Generator**

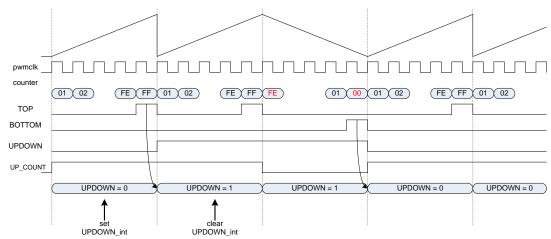

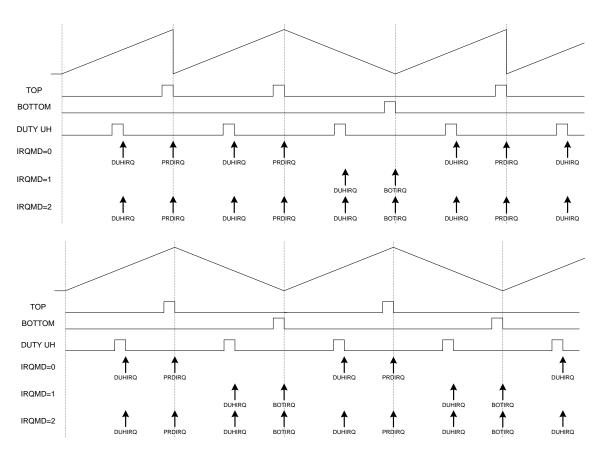

- Two channels of the 3-phase PWM generator are implemented. 16 bit up/down counter with prescaler supports triangular and saw tooth waveforms.

- The PWM generates an internal ADC trigger signal to measure the signal on time.

- Dead time insertion and emergency stop functionality ensure that the chip and system operate under safe conditions.

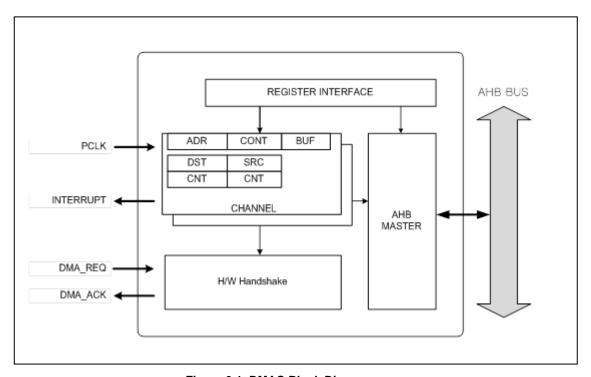

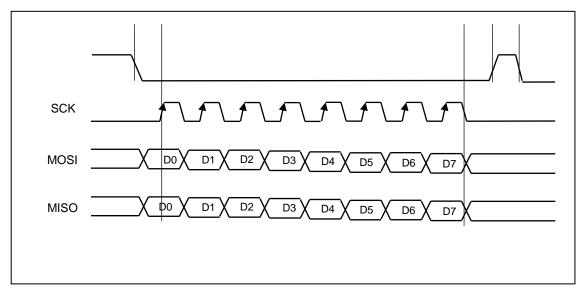

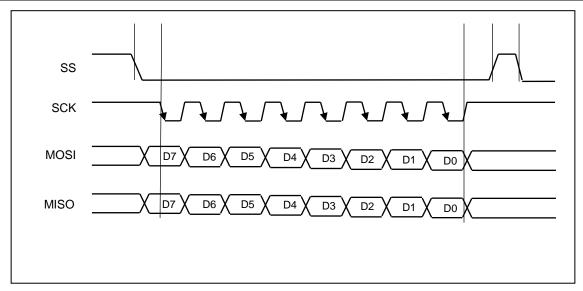

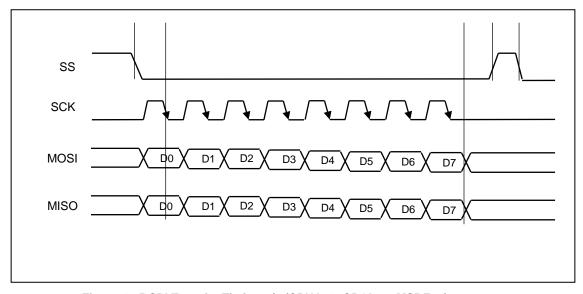

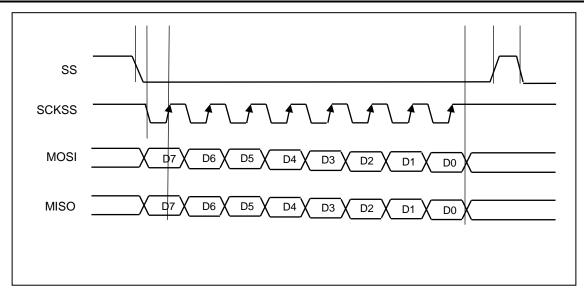

### **Serial Peripheral Interface (SPI)**

- Synchronous serial communication is provided by the SPI block. The Z32F1281 MCU has 2 channel SPI modules. The DMA function is supported by the DMA controller. Transfer data is moved to/from the memory area without CPU operation.

- Boot mode uses this SPI block to download the Flash program.

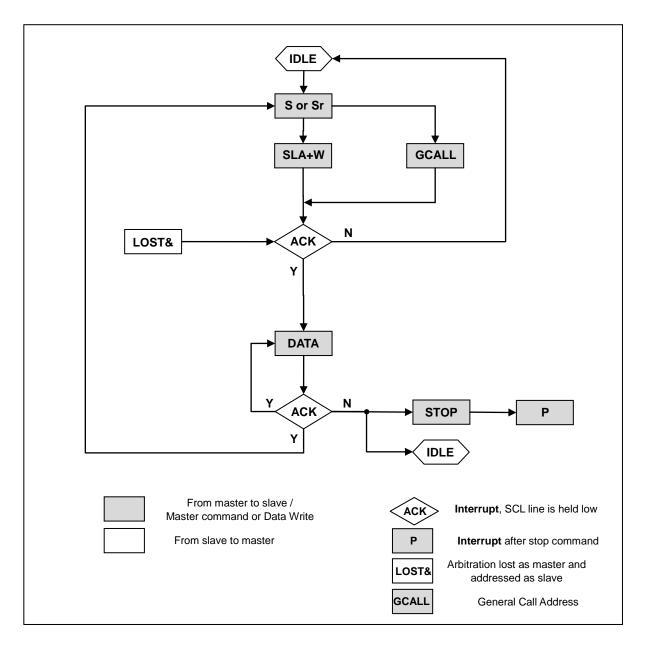

## Inter-Integrated Circuit Interface (I<sup>2</sup>C)

The Z32F1281 MCU has a 2-channel I<sup>2</sup>C block and it supports up to 400 kHz I<sup>2</sup>C communication. Master and the slave modes are supported.

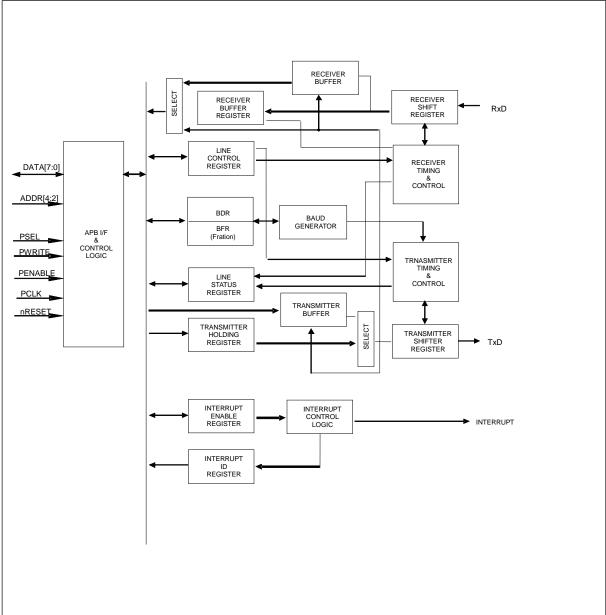

### **Universal Asynchronous Receiver/Transmitter (UART)**

- The Z32F1281 MCU includes a 4-channel UART block. For accurate baud rate control, a fractional baud rate generator is provided.

- The DMA function is supported by the DMA controller. Transfer data is moved to/from memory area without CPU operation.

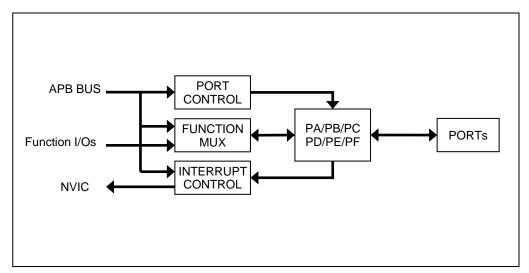

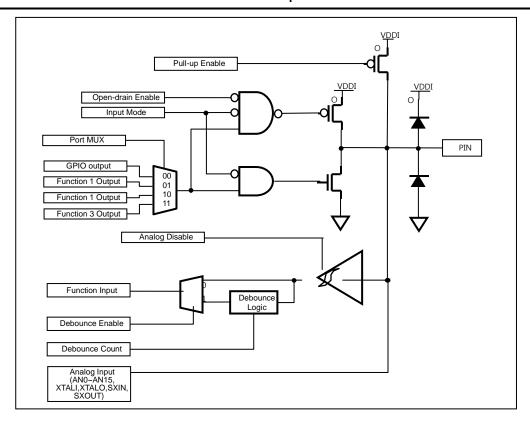

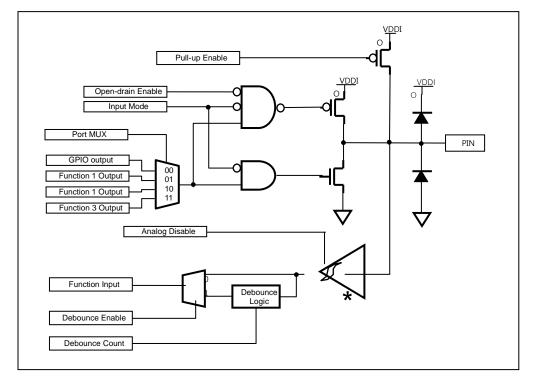

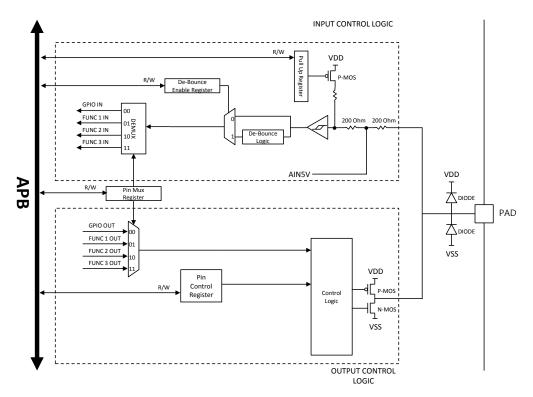

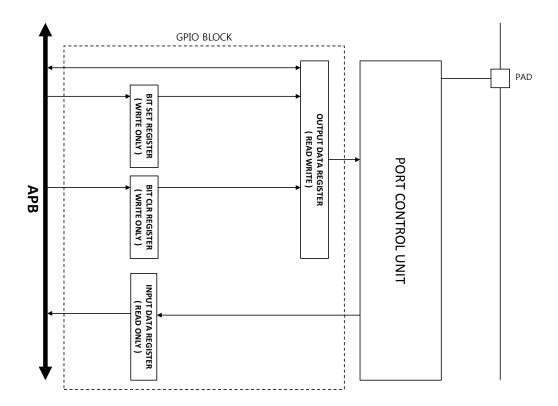

#### **General PORT I/Os**

- 16-bit PA, PB, PC, PD ports are available and provide multiple functionality:

- General I/O port

- Independent bit set/clear function

- · External interrupt input port

- Pull-up/Open-drain

- On chip debounce Filter

### 12-bit Analog-to-Digital Converter (ADC)

3 built-in ADCs can convert analog signal up to 1usec conversion rate. 16-channel analog mux and OP-AMP provides various combinations from external analog signals.

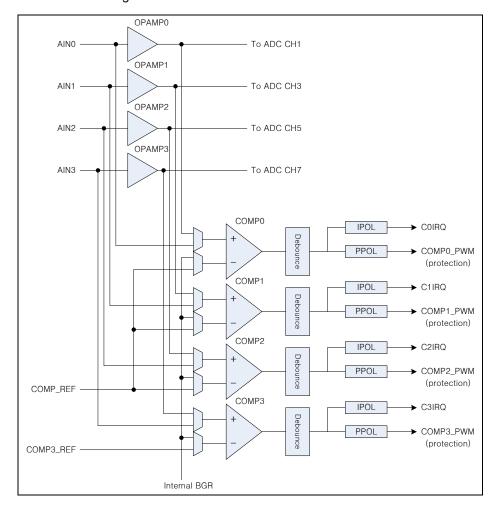

### **Analog Front End (AFE)**

- Operational Amplifier (OPAMP)

- o 4 built-in OPAMPs amplify analog signals up to x8.74 gain

- Analog Comparator (COMP)

- 4 built-in analog comparators

# **Pin Description**

The pin configurations are shown in Table 1.2. 16 pins are reserved for power/ground pair and dedicated pins.

Table 1.2. Pin Description

|        |        |          | Table 1.2. | Pin Description                     |        |

|--------|--------|----------|------------|-------------------------------------|--------|

| Pin N  | lame   | Туре     |            | Description                         | Remark |

| LQFP80 | LQFP64 |          |            |                                     |        |

| 79     | 63     | VDD      | Р          | VDD                                 |        |

| 80     | 64     | GND      | Р          | Ground                              |        |

| 1      | 1      | GND      | Р          | Ground                              |        |

|        |        | PD2      | IOUS       | PORT D Bit 2 Input/Output           |        |

| 2      | -      | MOSI1    | 1/0        | SPI Channel 1 Master Out / Slave In |        |

|        |        | PD3*     | IOUS       | PORT D Bit 3 Input/Output           |        |

| 3      | -      | MISOI1   | 1/0        | SPI Channel 1 Master In / Slave Out |        |

|        |        | PA0*     | IOUS       | PORT A Bit 0 Input/Output           |        |

| 4      | 2      | ANO      | IA         | Analog Input 0                      |        |

| 4      |        | COMP0    | IA         | Comparator 0 Input                  |        |

|        |        | PA1*     | +          | '                                   |        |

| -      | _      |          | IOUS       | PORT A Bit 1 Input/Output           |        |

| 5      | 3      | AN1      | IA         | Analog Input1                       |        |

|        |        | COMP1    | IA         | Comparator 1 Input                  |        |

| -      |        | PA2*     | IOUS       | PORT A Bit 2 Input/Output           |        |

| 6      | 4      | AN2      | IA         | Analog Input 2                      |        |

|        |        | COMP2    | IA         | Comparator 2 Input                  |        |

|        |        | PA3*     | IOUS       | PORT A Bit 3 Input/Output           |        |

| 7      | 5      | AN3      | IA         | Analog Input 3                      |        |

|        |        | СОМР3    | IA         | Comparator 3 Input                  |        |

|        |        | PA4*     | IOUS       | PORT A Bit 4 Input/Output           |        |

| 8      | 6      | T00      | Output     | Timer 0 Output                      |        |

|        |        | AN4      | IA         | Analog Input 4                      |        |

|        | 7      | PA5*     | IOUS       | PORT A Bit 5 Input/Output           |        |

| 9      |        | T10      | Output     | Timer 1 Output                      |        |

|        |        | AN5      | IA         | Analog Input 5                      |        |

|        |        | PA6*     | IOUS       | PORT A Bit 6 Input/Output           |        |

| 10     | 8      | T20      | Output     | Timer 2 Output                      |        |

| 10     | ٥      | AN6      | IA         | Analog Input 6                      |        |

|        |        | CREF0    | IA         | Comparator 0 Reference Input        |        |

|        |        | PA7*     | IOUS       | PORT A Bit 7 Input/Output           |        |

|        |        | TRACED3  | Output     | ETM Trace Data 3                    |        |

| 11     | 9      | T30      | Output     | Timer 3 Output                      |        |

|        |        | AN7      | IA         | Analog Input 7                      |        |

|        |        | CREF1    | IA         | Comparator 1 Reference Input        |        |

| 12     | 10     | AGND     | Р          | Analog Ground                       |        |

| 13     | 11     | AVDD     | Р          | Analog VDD                          |        |

|        |        | PA8*     | IOUS       | PORT A Bit 8 Input/Output           |        |

|        |        | TRACECLK | Output     | ETM Trace Clock                     |        |

| 14     | 12     | AD00     | Output     | ADC0 Start Signal                   |        |

|        |        | AN8      | IA         | Analog Input 8                      |        |

|        |        | PA9*     | IOUS       | PORT A Bit 9 Input/Output           |        |

| 15     |        | TRACED0  | Output     | ETM Trace Data 0                    |        |

|        | 13     | AD10     | Output     | ADC1 Start Signal                   |        |

|        |        | AN9      | IA         | Analog Input 9                      |        |

|        |        | PA10*    | IOUS       | PORT A Bit 10 Input/Output          |        |

|        |        | TRACED1  | Output     | ETM Trace Data 1                    |        |

| 16     | 14     | AD2O     | Output     | ADC2 Start Signal                   |        |

|        |        | AN10     | IA         | Analog Input 10                     |        |

|        |        | PA11*    | IOUS       | PORT A Bit 11 Input/Output          |        |

| 17     | 15     | TRACED2  | Output     | ETM Trace Data 2                    |        |

|        |        | INACLUZ  | σαιμαι     | LINI Hace Data Z                    |        |

|    |    | AN11    | IA          | Analog Input 11                            |          |

|----|----|---------|-------------|--------------------------------------------|----------|

| -  |    | PA12*   | IOUS        | PORT A Bit 12 Input/Output                 | -        |

|    |    | SSO     | 1/0         | SPIO Slave Select signal                   |          |

| 18 | 16 | AD2I    | Input       | ADC2 Start Input signal                    |          |

|    |    | AN12    | IA          | Analog Input 12                            |          |

|    |    | PD4     | IOUS        | PORT D Bit 4 Input/Output                  |          |

| 19 | -  | SCL1    | Output      | I <sup>2</sup> C Channel 1 SCL In/Out      |          |

| -  |    | PD5     | IOUS        | PORT D Bit 5 Input/Output                  |          |

| 20 | -  | SDA1    |             | I <sup>2</sup> C Channel 1 SDA In/Out      |          |

| 21 | 17 | VDD     | Output<br>P | VDD                                        |          |

| 22 | 18 | GND     | P           | Ground                                     |          |

|    | 10 | PD6*    | IOUS        |                                            |          |

| 22 |    |         |             | PORT D Bit 6 Input/Output                  |          |

| 23 | -  | TXD2    | Output      | UART Channel 2 TxD Input                   |          |

|    |    | AD0I    | Input       | ADCO Start Input signal                    |          |

|    |    | PD7*    | IOUS        | PORT D Bit 7 Input/Output                  |          |

| 24 | -  | RXD2    | Input       | UART Channel 2 RxD Input                   |          |

|    |    | AD1I    | Input       | ADC1 Start Input signal                    |          |

|    |    | PA13*   | IOUS        | PORT A Bit 13 Input/Output                 | _        |

| 25 | 19 | SCK0    | 1/0         | SPIO Data Clock Input/Output               |          |

|    |    | AN13    | IA          | Analog Input 13                            |          |

|    |    | PA14*   | IOUS        | PORT A Bit 14 Input/Output                 |          |

| 26 | 20 | MOSI0   | 1/0         | SPIO Master-Output/Slave-Input Data signal |          |

|    |    | AN14    | IA          | Analog Input 14                            |          |

|    | 21 | PA15*   | IOUS        | PORT A Bit 15 Input/Output                 |          |

| 27 |    | MISO0   | I/O         | SPIO Master-Input/Slave-Output Data signal |          |

|    |    | AN15    | IA          | Analog Input 15                            |          |

| 28 | 22 | PB0     | IOUS        | PORT B Bit 0 Input/Output                  |          |

|    | 22 | PWM0H0  | Output      | PWM0 H0 Output                             |          |

| 29 | 23 | PB1     | IOUS        | PORT B Bit 1 Input/Output                  |          |

|    | 23 | PWM0L0  | Output      | PWM0 L0 Output                             |          |

| 30 | 24 | PB2     | IOUS        | PORT B Bit 0 Input/Output                  |          |

|    |    | PWM0H1  | Output      | PWM0 H1 Output                             |          |

| 21 | 25 | PB3     | IOUS        | PORT B Bit 1 Input/Output                  |          |

| 31 | 25 | PWM0L1  | Output      | PWM0 L1 Output                             |          |

| 22 | 26 | TECT    | l.a.u.u.t   | Took woods lawy t / Always tip d (1/)      | Pull-    |

| 32 | 26 | TEST    | Input       | Test-mode Input (Always tied 'L')          | down     |

| 22 | 27 | CCANIAD | Innut       | Scan made Input (Always tied (1')          | Pull-    |

| 33 | 27 | SCANMD  | Input       | Scan-mode Input (Always tied 'L')          | down     |

|    |    | PB4     | IOUS        | PORT B Bit 4 Input/Output                  |          |

| 34 | 28 | PWM0H2  | Output      | PWM0 H2 Output                             |          |

|    |    | T9C     | 1/0         | Timer 9 Clock/Capture Input                |          |

|    |    | PB5     | IOUS        | PORT B Bit 5 Input/Output                  |          |

| 35 | 29 | PWM0L2  | Output      | PWM0 L2 Output                             |          |

|    |    | Т9О     | 1/0         | Timer 9 Output                             |          |

|    |    | PB6     | IOUS        | PORT B Bit 6 Input/Output                  |          |

| 36 | 30 | PRTINO  | Input       | PWM0 Protection Input signal 0             |          |

|    | 1  | WDTO    | Output      | WDT Output                                 |          |

|    |    | PB7     | IOUS        | PORT B Bit 7 Input/Output                  |          |

| 37 | 31 | OVIN0   | Input       | PWM0 Over-voltage put signal 1             |          |

|    |    | STBYO   | Output      | Power-down mode indication signal          |          |

|    |    | PB8     | IOUS        | PORT B Bit 8 Input/Output                  | <u> </u> |

| 38 | 32 | PRTIN1  | Input       | PWM1 Protection Input signal 0             | <u> </u> |

|    | 32 | RXD3    | Input       | UART3 RXD Input                            |          |

|    | 1  |         | ,5 6.6      | - commentered                              |          |

|            |        |           | ı      |                                     |

|------------|--------|-----------|--------|-------------------------------------|

| 39         | _      | PD8       | IOUS   | PORT D Bit 8 Input/Output           |

|            |        | WDTO      | Output | WDT Output                          |

| 30         |        | PD9       | IOUS   | PORT D Bit 9 Input/Output           |

|            |        | STBYO     | Output | Power-down mode indication signal   |

| 41         | 33 VDD |           | Р      | VDD                                 |

| 42         | 34     | GND       | Р      | Ground                              |

|            |        | PB9       | IOUS   | PORT B Bit 9 Input/Output           |

| 43         | 35     | OVIN1     | Input  | PWM1 Over-voltage Input signal 1    |

|            |        | TXD3      | Output | UART3 TXD Output                    |

| 44         | 36     | PB10      | IOUS   | PORT B Bit 10 Input/Output          |

|            | 30     | PWM1H0    | Output | PWM Channel 1 Phase 0 H-side Output |

| 45         | 37     | PB11      | IOUS   | PORT B Bit 11 Input/Output          |

|            | 37     | PWM1L0    | Output | PWM Channel 1 Phase 0 L-side Output |

| 46         | 38     | PB12      | IOUS   | PORT B Bit 12 Input/Output          |

|            | 30     | PWM1H1    | Output | PWM Channel 1 Phase 1 H-side Output |

| 47         | 39     | PB13      | IOUS   | PORT B Bit 13 Input/Output          |

|            | 33     | PWM1L1    | Output | PWM Channel 1 Phase 1 L-side Output |

| 48         | 40     | PB14      | IOUS   | PORT B Bit 14 Input/Output          |

|            | 40     | PWM1H2    | Output | PWM Channel 1 Phase 2 H-side Output |

| 49         | 41     | PB15      | IOUS   | PORT B Bit 15 Input/Output          |

|            | 71     | PWM1L2    | Output | PWM Channel 1 Phase 2 L-side Output |

| 50         | 42     | GND       | Р      | Ground                              |

| 51         | 43     | VDD       | Р      | VDD                                 |

| 52         | 44     | PC0       | IOUS   | PORT C Bit 0 Input/Output           |

|            |        | TCK/SWCK  | Input  | JTAG TCK, SWD Clock Input           |

| 53         | 45     | PC1       | IOUS   | PORT C Bit 1 Input/Output           |

|            | .5     | TMS/SWDIO | I/O    | JTAG TMS, SWD Data Input/Output     |

|            |        | PD10      | IOUS   | PORT D Bit 10 Input/Output          |

| 54         | -      | AD0SOC    | Output | ADC0 Start-of-Conversion            |

|            |        | TOC/PHA   | Input  | Timer 0 Clock/Capture/Phase-A Input |

|            |        | PD11      | IOUS   | PORT D Bit 10 Input/Output          |

| 55         | -      | AD0EOC    | Output | ADC0 End-of-Conversion              |

|            |        | T1C/PHB   | Input  | Timer 1 Clock/Capture/Phase-B Input |

| 56         | 46     | NMI       | Input  | Non-maskable Interrupt Input        |

|            |        | PD12      | IOUS   | PORT D Bit 12 Input/Output          |

| 57         | -      | AD1SOC    | Output | ADC1 Start-of-Conversion            |

|            |        | T2C/PHZ0  | Input  | Timer 2 Clock/Capture/Phase-Z Input |

|            |        | PD13      | IOUS   | PORT D Bit 13 Input/Output          |

| 58         | -      | AD1EOC    | Output | ADC1 End-of-Conversion              |

|            |        | T3C       | Input  | Timer 3 Clock/Capture Input         |

| 59         | 47     | VDD       | Р      | VDD                                 |

| 60         | 48     | GND       | Р      | Ground                              |

| 61         | 49     | PC2       | IOUS   | PORT C Bit 2 Input/Output           |

|            |        | TDO/SWO   | Output | JTAG TDO, SWO Output                |

| 62         | 50     | PC3       | IOUS   | PORT C Bit 3 Input/Output           |

|            |        | TDI       | Input  | JTAG TDI Input                      |

|            |        | PC4       | IOUS   | PORT C Bit 4Input/Output            |

| 63         | 51     | nTRST     | Input  | JTAG nTRST Input                    |

|            | 1      | TOC/PHA   | Input  | Timer 0 Clock/Capture/Phase-A Input |

| <i>C</i> * | F.2    | PC5       | IOUS   | PORT C Bit 5Input/Output            |

| 64         | 52     | RXD1      | Input  | UART1 RXD Input                     |

|            |        | T1C/PHB   | Input  | Timer 1 Clock/Capture/Phase-B Input |

| 65         | 53     | PC6       | IOUS   | PORT C Bit 6Input/Output            |

|     |    | TXD1    | Output | UART1 TXD Output                       |         |

|-----|----|---------|--------|----------------------------------------|---------|

|     |    | T2C/PHZ | Input  | Timer 2 Clock/Capture/Phase-Z Input    |         |

|     |    | PC7     | IOUS   | PORT C Bit 7Input/Output               |         |

| 66  | 54 | SCL0    | Output | I <sup>2</sup> C Channel 0 SCL In/Out  |         |

|     |    | T3C     | Input  | Timer 3 Clock/Capture input            |         |

| 67  |    | PC8     | IOUS   | PORT C Bit 8 Input/Output              |         |

| 67  | 55 | SDA0    | Output | I <sup>2</sup> C Channel 0 SDA In/Out  |         |

|     |    | PC9     | IOUS   | PORT C Bit 9 Input/Output              |         |

| 68  | 56 | CLKO    | Output | System Clock Output                    |         |

|     |    | T80     | Output | Timer 8 Output                         |         |

|     |    | PC10    | IOUS   | PORT C Bit 10 Input/Output             |         |

| 69  | 57 | nRESET  | Input  | External Reset Input                   | Pull-up |

|     |    | PC11    | IOUS   | PORT C Bit 11 Input/Output             |         |

| 70  | 58 | воот    | Input  | Boot mode Selection Input              |         |

|     |    | T8C     | Input  | Timer 8 Clock/Capture Input            |         |

| 71  | -  | PD14    | IOUS   | PORT D Bit 14 Input/Output             |         |

|     |    | AD2SOC  | Output | ADC2 Start-of-Conversion Output signal |         |

| 72  | -  | TD15    | IOUS   | PORT D Bit 15 Input/Output             |         |

| 72  |    | AD2EOC  | Output | ADC2 Start-of-Conversion Output signal |         |

|     | 59 | PC15    | IOUS   | PORT C Bit 14 Input/Output             |         |

| 73  |    | TXD0    | Output | UARTO TXD Output                       |         |

|     |    | MISO0   | 1/0    | SPI0 Master-Input/Slave-Output         |         |

|     |    | PC14    | IOUS   | PORT C Bit 14 Input/Output             |         |

| 7.4 | 60 | RXD0    | Input  | UARTO RXD Input                        |         |

| 74  | 60 | MOSI0   | I/O    | SPI0 Master-Output/Slave-Input         |         |

|     |    | VMARGIN | OA     | Not used. (test purpose)               |         |

| 75  | 61 | PC13    | IOUS   | PORT C Bit 13 Input/Output             |         |

| 75  | 91 | XOUT    | OA     | External Crystal Oscillator Output     |         |

| 7.0 | 63 | PC12    | IOUS   | PORT C Bit 12 Input/Output             |         |

| 76  | 62 | XIN     | IA     | External Crystal Oscillator Input      |         |

| 77  |    | PD0     | IOUS   | PORT D Bit 0 Input/Output              |         |

| //  | -  | SS1     | 1/0    | SPI1 Slave Select                      |         |

| 78  |    | PD1     | IOUS   | PORT D Bit 1 Input/Output              |         |

| 78  | -  | SCK1    | 1/0    | SPI1 Clock Input/Output                |         |

<sup>\*</sup>Notation: I=Input, O=Output, U=Pull-up, D=Pull-down,

S=Schmitt-Trigger Input Type, C=CMOS Input Type, A=Analog, P=Power

<sup>(\*)</sup> Selected pin function after reset condition

Pin order may be changed with revision notice

# **Memory Map**

| Address                    | Memory map                     |

|----------------------------|--------------------------------|

| 0x0000_0000                |                                |

| _                          | Code Flash ROM                 |

|                            | (128KB)                        |

| 0x0001_FFFF                | (=====                         |

| 0x0002_0000                |                                |

|                            | Reserved                       |

| 0x1FFE_FFFF                |                                |

| 0x1FFF_0000                |                                |

|                            | Boot ROM                       |

| 0x1FFF_07FF                |                                |

| 0x1FFF_0800                |                                |

|                            | Reserved                       |

| 0x1FFF_FFFF                |                                |

| 0x2000_0000                | SRAM                           |

|                            | (12K)                          |

| 0x2000_5FFF                | (12K)                          |

| 0x2000_6000<br>0x2FFF FFFF | Reserved                       |

| 0x2200_0000                |                                |

| -                          | SRAM Bit-banding region        |

| 0x23FF_FFFF<br>0x2400 0000 |                                |

| 0x2FFF FFFF                | Reserved                       |

| 0x3000_0000                | Code Floor BONA(NAirroand)     |

|                            | Code Flash ROM(Mirrored)       |

| 0x3001_FFFF                | (128KB)                        |

| 0x3002_0000                |                                |

| 0x3002 07FF                | Boot ROM (Mirrored)            |

| 0x3003 0000                |                                |

| _                          | OTP ROM (Mirrored)             |

| 0x3003_07FF<br>0x3004_0000 |                                |

| _                          | Reserved                       |

| 0x3FFF_FFFF                |                                |

| 0x4000_0000                |                                |

|                            | Peripherals                    |

| 0x4000 FFFF                | •                              |

| 0x4000 PPPP                | Description                    |

| 0x41FF_FFFF                | Reserved                       |

| 0x4200_0000                | Davishavala hit handing vacion |

| 0x43FF FFFF                | Peripherals bit-banding region |

| 0x4400_0000                | Reserved                       |

| 0x5FFF_FFFF<br>0x6000 0000 | Neser veu                      |

| 0x6000_0000                | External Memory                |

| _ [                        | (Not supported)                |

| 0x9FFF_FFFF                | ,                              |

| 0xA000_0000                | External Device                |

|                            | (Not supported)                |

| 0xDFFF_FFFF                | (                              |

| 0xE000_0000                | Private peripheral bus:        |

|                            | Internal                       |

| 0xE003_FFFF                | 32                             |

| 0xE004_0000                | Private peripheral bus:        |

|                            | Debug/External                 |

| 0xE00F_FFFF                |                                |

| 0xE010_0000                |                                |

|                            | Vendor Specific                |

| 0xffff ffff                | ·                              |

| VALUE EEFF                 |                                |

Figure 1.5. Main Memory Map

|                            | Core memory map |  |

|----------------------------|-----------------|--|

| Address                    |                 |  |

| 0xE000_0000                |                 |  |

|                            | ITM             |  |

|                            | HIVI            |  |

| 0xE000_0FFF                |                 |  |

| 0xE000_1000                |                 |  |

|                            | DWT             |  |

|                            | DVVI            |  |

| 0xE000_1FFF                |                 |  |

| 0xE000_2000                |                 |  |

|                            | FPB             |  |

|                            | 5               |  |

| 0xE000_2FFF<br>0xE000 3000 |                 |  |

| 0xE000_3000                | <b>D</b>        |  |

|                            | Reserved        |  |

| 0xE000_DFFF                |                 |  |

| 0xE000_E000                |                 |  |

|                            | System Control  |  |

|                            | System Control  |  |

| 0xE000 EFFF                |                 |  |

| 0xE000_F000                |                 |  |

| 0xE003 FFFF                | Reserved        |  |

| 0xE003_FFFF                |                 |  |

|                            | TPIU            |  |

| 0                          | IFIU            |  |

| 0xE004_0FFF<br>0xE004_1000 |                 |  |

|                            | ETM             |  |

|                            | E I IVI         |  |

| 0xE004_1FFF<br>0xE004_2000 |                 |  |

| VALUO 4_2000               |                 |  |

|                            | External PPB    |  |

| 0xE00F EFFF                |                 |  |

| 0xE00F_EFFF                |                 |  |

| _                          | ROM Table       |  |

| 0xE00F FFFF                | NOW TABLE       |  |

Figure 1.6. Cortex-M3 Private Memory Map

Note: For more information about the memory maps, refer to document number DDI337 from ARM.

| Address          | Peripheral map    |

|------------------|-------------------|

| 0x4000_0000      | SCU               |

| 0x4000_0100      | FMC               |

| 0x4000_0200      | WDT               |

| 0x4000_0300      | Reserved          |

| 0x4000_0400      | DMAC(15)          |

| 0x4000_0500      | Reserved          |

| 0x4000_1000      | PCU               |

| 0x4000_2000      | GPIO(A,B,C,D)     |

| 0x4000_3000      | TIMER(6)          |

| 0x4000_4000      | MPWM0             |

| 0x4000_5000      | MPWM1             |

| 0x4000_6000      | Reserved          |

| 0x4000_8000      | UART0             |

| 0x4000_8100      | UART1             |

| 0x4000_8200      | UART2             |

| 0x4000_8300      | UART3             |

| 0x4000_8600      | Reserved          |

| 0x4000_9000      | SPI0              |

| 0x4000_9100      | SPI1              |

| 0x4000_9200      | Reserved          |

| 0x4000_A000      | I <sup>2</sup> C0 |

| 0x4000_A100      | I <sup>2</sup> C1 |

| 0x4000_A200      | Reserved          |

| 0z4000_B000      | ADC0              |

| 0x4000_B100      | ADC1              |

| 0x4000_B200      | ADC2              |

| 0x4000_B300      | AFE               |

| 0x4000_B400      |                   |

| -<br>0x4000 FFFF | Reserved          |

Figure 1.7. Peripheral Memory Map

# 2. CPU

### **Cortex-M3 Core**

The CPU core is supported by the ARM Cortex-M3 processor which provides a high-performance, low-cost platform. For more information about Cortex-M3, refer to document number DDI337 from ARM.

# **System Timer**

The System Timer (SYSTICK) is a 24-bit timer and is part of the Cortex-M3 core. The system timer can be configured either through the registers (see the Cortex-M3 Technical Reference Manual) or through the provided functions defined in <code>core\_cm3.h</code>. There is an interrupt vector for the system timer. To configure the system timer, call <code>SysTickConfig()</code> with the number of system clocks in between interrupt intervals (up to a maximum of 24 bits).

# **Interrupt Controller**

The Nested Vectored Interrupt Controller (NVIC) is part of the core Cortex-M3 MCU. The NVIC controls system exceptions and peripheral interrupts and is closely coupled with the core to provide low latency and efficient processing of late arriving interrupts. The NVIC maintains knowledge of the nested interrupts to enable tail-chaining of interrupts.

The Z32F1281 MCU supports 64 peripheral interrupts (of which 25 are not used) and 16 system interrupts. The NVIC also allows setting software interrupts and resetting the system.

Interrupts can be assigned a PRIORITY GROUP (common interrupts with the same priorities) as well as individual priorities. There are 8 priority levels available. For an interrupt to be active, it must be enabled in the peripheral and the NVIC registers. For more information on NVIC, see the Cortex M3 Technical Reference Manual.

The system includes functions to set the NVIC registers which are defined in core cm3.h.

Table2.1. Interrupt Vector Map

| Interrupt<br>Number | Vector Address | Interrupt Source      |  |  |

|---------------------|----------------|-----------------------|--|--|

| -16                 | 0x0000_0000    | Stack Pointer         |  |  |

| -15                 | 0x0000_0004    | Reset Address         |  |  |

| -14                 | 0x0000_0008    | NMI Handler           |  |  |

| -13                 | 0x0000_000C    | Hard Fault Handler    |  |  |

| -12                 | 0x0000_0010    | MPU Fault Handler     |  |  |

| -11                 | 0x0000_0014    | BUS Fault Handler     |  |  |

| -10                 | 0x0000_0018    | Usage Fault Handler   |  |  |

| -9                  | 0x0000_001C    |                       |  |  |

| -8                  | 0x0000_0020    | Bassand               |  |  |

| -7                  | 0x0000_0024    | Reserved              |  |  |

| -6                  | 0x0000_0028    |                       |  |  |

| -5                  | 0x0000_002C    | SVCall Handler        |  |  |

| -4                  | 0x0000_0030    | Debug Monitor Handler |  |  |

| -3                  | 0x0000_0034    | Reserved              |  |  |

| -2                  | 0x0000_0038    | PenSV Handler         |  |  |

| -1                  | 0x0000_003C    | SysTick Handler       |  |  |

| 0                   | 0x0000_0040    | LVDDETECT             |  |  |

| 1                   | 0x0000_0044    | SCLKFAIL              |  |  |

| 2                   | 0x0000_0048    | XOSCFAIL              |  |  |

| 3                   | 0x0000_004C    | WDT                   |  |  |

| 4                   | 0x0000_0050    | Reserved              |  |  |

| 5                   | 0x0000_0054    | TIMERO                |  |  |

| 6                   | 0x0000_0058    | TIMER1                |  |  |

| 7                   | 0x0000_005C    | TIMER2                |  |  |

| 8                   | 0x0000_0060    | TIMER3                |  |  |

| 9                   | 0x0000_0064    | Percented             |  |  |

| 10                  | 0x0000_0068    | Reserved              |  |  |

| 11 | 0x0000_006C |           |

|----|-------------|-----------|

| 12 | 0x0000_0000 |           |

| 13 | 0x0000_0074 | TIMER8    |

| 14 | 0x0000_0078 | TIMER9    |

| 15 | 0x0000_007C | Reserved  |

| 16 | 0x0000_0080 | GPIOAE    |

| 17 | 0x0000_0084 | GPIOAO    |

| 18 | 0x0000_0088 | GPIOBE    |

| 19 | 0x0000 008C | GPIOBO    |

| 20 | 0x0000 0090 | GPIOCE    |

| 21 | 0x0000_0094 | GPIOCO    |

| 22 | 0x0000_0098 | GPIODE    |

| 23 | 0x0000 009C | GPIODO    |

| 24 | 0x0000_00A0 | MPWM0     |

| 25 | 0x0000_00A4 | MPWM0PROT |

| 26 | 0x0000_00A8 | MPWM00VV  |

| 27 | 0x0000_00AC | MPWM1     |

| 28 | 0x0000_00B0 | MPWM1PROT |

| 29 | 0x0000_00B4 | MPWM10VV  |

| 30 | 0x0000_00B8 | Reserved  |

| 31 | 0x0000_00BC | Reserved  |

| 32 | 0x0000_00C0 | SPI0      |

| 33 | 0x0000_00C4 | SPI1      |

| 34 | 0x0000_00C8 | Reserved  |

| 35 | 0x0000_00CC | Nesei veu |

| 36 | 0x0000_00D0 | 12C0      |

| 37 | 0x0000_00D4 | I2C1      |

| 38 | 0x0000_00D8 | UARTO     |

| 39 | 0x0000_00DC | UART1     |

| 40 | 0x0000_00E0 | UART2     |

| 41 | 0x0000_00E4 | UART3     |

| 42 | 0x0000_00E8 | Reserved  |

| 43 | 0x0000_00EC | ADC0      |

| 44 | 0x0000_00F0 | ADC1      |

| 45 | 0x0000_00F4 | ADC2      |

| 46 | 0x0000_00F8 | COMP0     |

| 47 | 0x0000_00FC | COMP1     |

| 48 | 0x0000_0100 | COMP2     |

| 49 | 0x0000_0104 | COMP3     |

| 50 | 0x0000_0108 | Reserved  |

| 51 | 0x0000_010C | Reserved  |

| 52 | 0x0000_0110 | Reserved  |

| 53 | 0x0000_0114 | Reserved  |

| 54 | 0x0000_0118 | Reserved |

|----|-------------|----------|

| 55 | 0x0000_011C | Reserved |

| 56 | 0x0000_0120 | Reserved |

| 57 | 0x0000_0124 | Reserved |

| 58 | 0x0000_0128 | Reserved |

| 59 | 0x0000_012C | Reserved |

| 60 | 0x0000_0130 | Reserved |

| 61 | 0x0000_0134 | Reserved |

| 62 | 0x0000_0138 | Reserved |

| 63 | 0x0000_013C | Reserved |

# 3. Boot Mode

### **Boot Mode Pins**

**Block**

**SYSTEM**

**UARTO**

SPI0

The Z32F1281 MCU has a Boot Mode option to program internal Flash memory. When the BOOT pin is pulled low, the system will start up in the BOOT area  $(0x1FFF\_0000)$  instead of the default Flash area  $(0x0000\_0000)$ . This provides the ability to flash the part using either UART or SPI interfaces. The BOOT pin has an internal pull up resistor. Therefore, when the BOOT pin is not connected, it rides high (normal state).

Boot Mode uses the UART0 port and the SPI0 ports for the interface. The JTAG and SW interfaces can also be used, which provide the ability to recover from a bad Flash update that prevents the JTAG or SW debugger from attaching.

The pins for Boot Mode are listed in Table 3.1.

SCK0/PA13

MOSI0/PA14

MISO0/PA15

**Pin Name** Dir **Description** nRESET/PC10 1 Reset Input signal ı BOOT/PC11 '0' to enter Boot mode RXD0/PC14 Ι **UART Boot Receive Data** TXD0/PC15 0 **UART Boot Transmit Data** SS0/PA12 Ι SPI Boot Slave Select

SPI Boot Clock Input

SPI Boot Data Input

SPI Boot Data Output

Table 3.1. Boot Mode Pin List

1

ı

0

# **Boot Mode Connections**

The target board can be designed using either of the Boot Mode ports – UART or SPI.

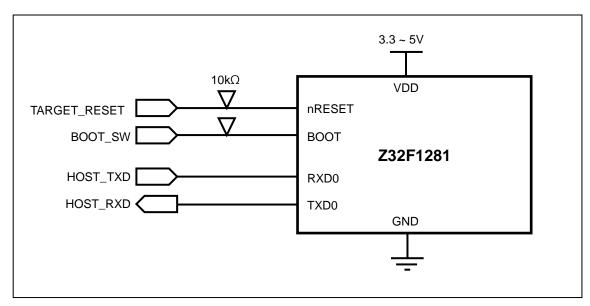

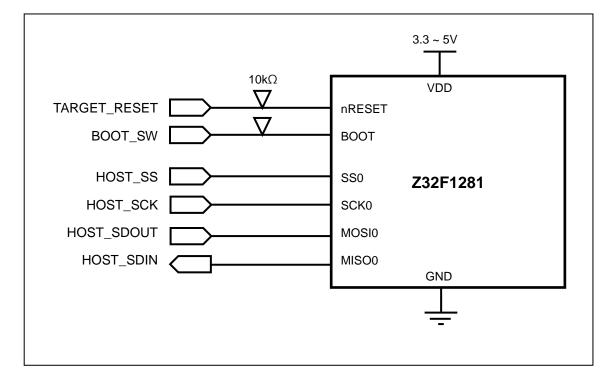

Figure 3.1 and Figure 4.1Figure 3.2 show sample connection diagrams in Boot Mode.

Figure 3.1. Connection Diagram of UART Boot

Figure 3.2. Connection Diagram of SPI Boot

# 4. System Control Unit

## **Overview**

The Z32F1281 MCU has a built-in intelligent power control block which manages system analog blocks and operating modes. Internal reset and clock signals are controlled by the SCU block to maintain optimal system performance and power dissipation.

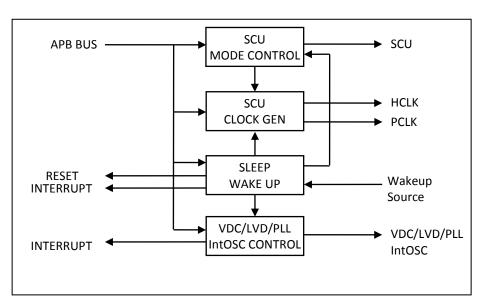

Figure 4.1. SCU Block Diagram

# **Clock System**

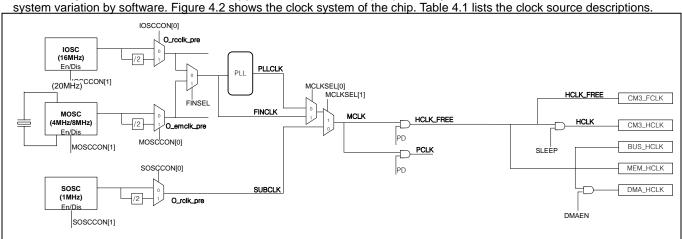

The Z32F1281 MCU contains two main operating clocks – HCLK, which supplies the clock to the CPU and the AHB bus system; and PCLK, which supplies the clock to the peripheral systems. Users can control the clock system varieties by a few systems of the clock system varieties by a few systems.

Figure 4.2. System Clock Configuration

Each of the registers to switch the clock source has a glitch-free circuit. Therefore, the clock can be switched without the risk of glitches.

**Table 4.1. Clock Sources**

| Clock name | Frequency       | Description           |

|------------|-----------------|-----------------------|

| IOSC20     | 20MHz           | Internal OSC          |

| MOSC       | XTAL(4MHz~8MHz) | External Crystal IOSC |

| PLL Clock  | 8MHz ~ 80MHz    | On Chip PLL           |

| ROSC       | 1MHz            | Internal RING OSC     |

The PLL can synthesize the PLLCLK clock up to 80 MHz with the FIN reference clock. It also has an internal pre-divider and post-divider.

### **HCLK Clock Domain**

The HCLK clock feeds the clock to the CPU and AHB bus. The Cortex-M3 CPU requires two clocks related with HCLK clock – FCLK and HCLK. FCLK is the free running clock and it is always running except in Power-down mode. HCLK can be stopped in Idle mode.

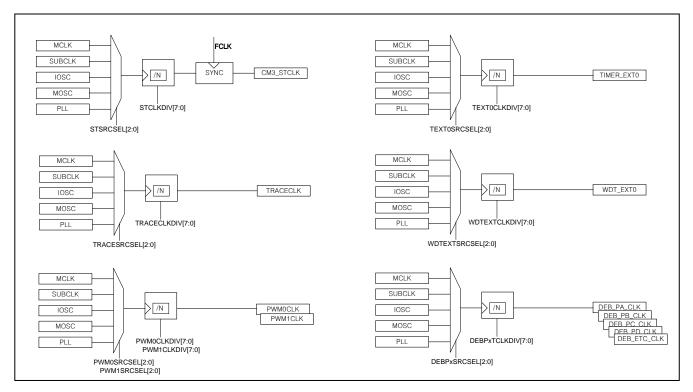

### Miscellaneous Clock Domain for Cortex-M3

Figure 4.3. Miscellaneous Clock Configuration

### **PCLK Clock Domain**

PCLK is the master clock of all the peripherals. It can be stopped in Power-down mode. Each peripheral clock is generated by the PCER register set.

### **Clock Configuration**

After power up, the default system clock is fed by the RINGOSC (1MHz) clock. RINGOSC is enabled by default during the power up sequence. The other clock sources are enabled by user controls with the RINGOSC system clock.

The MOSC clock can be enabled by the CSCR register. Before enabling the MOSC block, the pin mux configuration should be set for XIN, XOUT function. PC12 and PC13 pins are shared with MOSC's XIN and XOUT function - PCCMR and PCCCR registers should be configured properly. After enabling the MOSC block, you must wait for more than 1 msec to ensure stable operation of crystal oscillation.

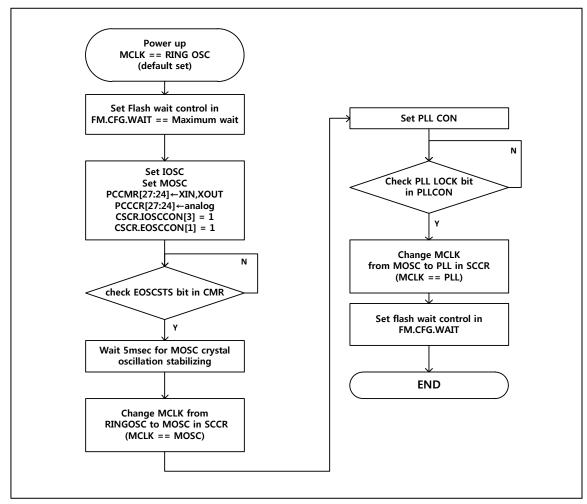

The PLL clock can be enabled by the PLLCON register. After enabling the PLL block, you must wait for the PLL lock flag. When the PLL output clock is stable, you can select MCLK for your system requirement. Before changing the system clock, set Flash access wait to the maximum value. After the system clock is changed, set the desired Flash access wait time.

Figure 4.4 shows a flow chart outlining the process to configure the system clock.

Figure 4.4. Clock Configuration Procedure Flowchart

When you speed up the system clock up to the maximum operating frequency, check the Flash wait control configuration. The CLK3 and CLK4 bit fields in the FMCR register can control the wait time. Flash read access time is one of the limiting factors that can impact performance.

The wait control recommendation is provided in Table 4.2.

**Table 4.2. Flash Wait Control Recommendation**

| FMCR | Flash Access Wait | Available Max System Clock Frequency |

|------|-------------------|--------------------------------------|

| CLK3 | 3 Clock Wait      | ~48MHz                               |

| CLK4 | 4 Clock Wait      | ~72MHz                               |

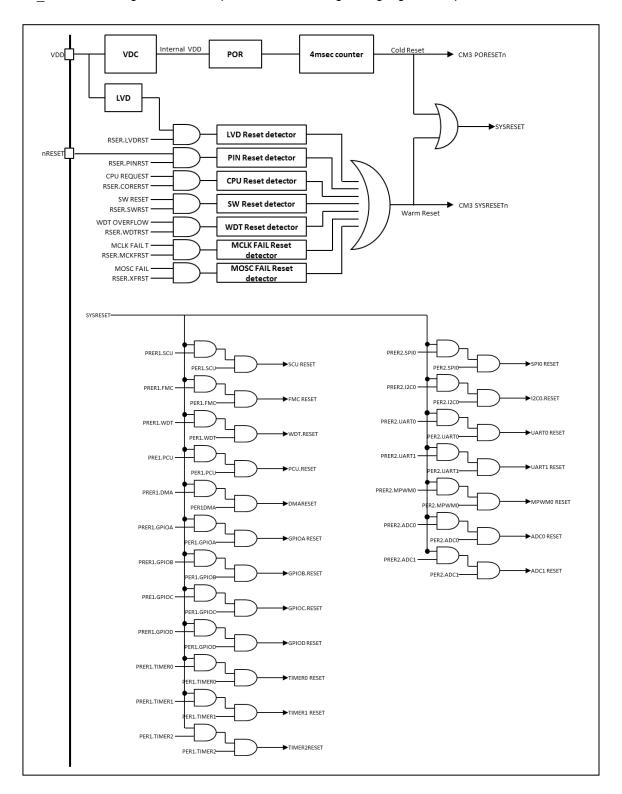

### Reset

The Z32F1281 MCU has two system resets:

- Cold reset by POR which is effective during power up or down sequence

- Warm reset which is generated by several reset sources.

The reset event causes the chip to return to its initial state.

Cold reset has only one reset source, which is POR. Warm reset has the following reset sources:

- nRESET pin

- WDT reset

- LVD reset

- MCLK Fail reset

- MOSC Fail reset

- S/W reset

- CPU request reset

### **Cold Reset**

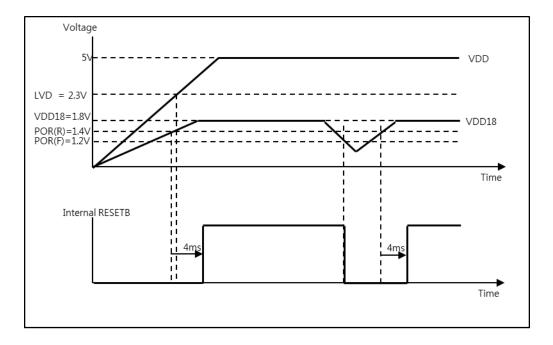

The cold reset is an important feature of the chip when power is up. This characteristic affects the system boot globally. Internal VDC is enabled when VDD power is turned on. The internal VDD level slope is followed by the external VDD power slope. The boot operation is started when the internal PoR trigger level is 1.4V of the internal VDC voltage out level. The RINGOSC clock is enabled and counts 4 msec to stabilize the internal VDC level. During this time, the external VDD voltage level should be higher than the initial LVD level (2.3V). After counting 4 msec, the CPU reset is released and the operation is started.

Figure 4.5 shows the power up sequence and internal reset waveform.

Figure 4.5. Power Up POR Sequence

The RSSR register shows the POR reset status. The last reset comes from POR. RSSR.PORST is set to "1". After power up, this bit is always "1". If an abnormal internal voltage drop occurs during normal operation, the system is reset and this bit is also set to "1".

When a cold reset is applied, the entire chip returns to its initial state.

### **Warm Reset**

The warm reset event has several reset sources and some parts of the chip return to initial state when a warm reset condition occurs.

The warm reset source is controlled by the RSER register and the status appears in the RSSR register. The reset for each peripheral block is controlled by the PRER register. The reset can be masked independently.

The CM3 SYSRESETn signal resets the processor, excluding debug logic in the processor.

Figure 4.6. Reset Configuration

# **Operation Mode**

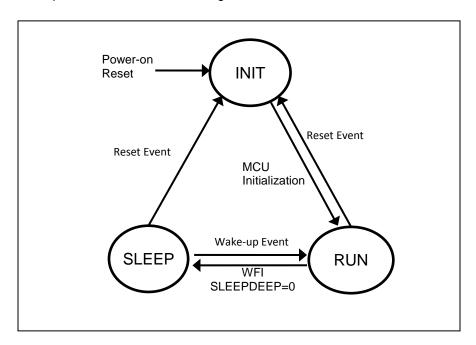

Three operational states are available in addition to the Initialization state (INIT). When the reset is asserted (brought low), the Z32F1281 MCU runs at 1 MHz, driven by the ROSC. All the other clocks are disabled and peripheral power and clocks are reset.

The RUN mode is designed to run at maximum performance of the CPU with a high-speed clock system. The IOSC must be enabled in order to enable the MOSC. The SLEEP mode is designed to run in Low Power consumption mode by halting the processor core and any unused peripherals.

Figure 4.7 shows the operation mode transition diagram.

Figure 4.7. Operating Mode

### **RUN Mode**

This mode operates the MCU core and the peripheral hardware by using the high-speed clock. After reset, followed by the INIT state, the system can be configured to enter into RUN mode.

### **SLEEP Mode**

Only the CPU is stopped in this mode. Each peripheral function can be enabled by the function enable and clock enable bit in the PER and PCER registers. To enter sleep mode, configure the system for the desired low power state then use the "wfi" instruction. When exiting sleep mode, the clock will be set to the RING oscillator.

# **Pin Description**

Table 4.3. SCU and PLL Pins

| PIN NAME | TYPE | DESCRIPTION                    |

|----------|------|--------------------------------|

| nRESET   | I    | External Reset Input           |

| XIN/XOUT | osc  | External Crystal Oscillator    |

| STBYO    | 0    | Stand-by Output Signal         |

| CLKO     | 0    | Clock Output Monitoring Signal |

# Registers

The base address of SCU is  $0x4000\_0000$ . The register map is described in Table 4.4.

Table 4.4. SCU Register Map

| Name     | Offset | R/W | Description                          | Reset      |  |  |  |

|----------|--------|-----|--------------------------------------|------------|--|--|--|

| CIDR     | 0x0000 | R   | CHIP ID Register                     | AC33_8128  |  |  |  |

| SMR      | 0x0004 | R/W | System Mode Register                 | 0000_0000  |  |  |  |

| SRCR     | 0x0008 | R/W | System Reset Control Register        | 0000_0000  |  |  |  |

| WUER     | 0x0010 | R/W | Wake up source enable register       | 0000_0000  |  |  |  |

| WUSR     | 0x0014 | R/W | Wake up source status register       | 0000_0000  |  |  |  |

| RSER     | 0x0018 | R/W | Reset source enable register         | 0000_0049  |  |  |  |

| RSSR     | 0x001C | R/W | Reset source status register         | 0000_0080* |  |  |  |

| PRER1    | 0x0020 | R/W | Peripheral reset enable register 1   | 03FF_1F1F* |  |  |  |

| PRER2    | 0x0024 | R/W | Peripheral reset enable register 2   | 00F3_0F33* |  |  |  |

| PER1     | 0x0028 | R/W | Peripheral enable register 1         | 0000_000F* |  |  |  |

| PER2     | 0x002C | R/W | Peripheral enable register 2         | 0000_0101* |  |  |  |

| PCER1    | 0x0030 | R/W | Peripheral clock enable register 1   | 0000_000F* |  |  |  |

| PCER2    | 0x0034 | R/W | Peripheral clock enable register 2   | 0000_0101* |  |  |  |

| CSCR     | 0x0040 | R/W | Clock Source Control register        | 0000_0020  |  |  |  |

| SCCR     | 0x0044 | R/W | System Clock Control register        | 0000_0000  |  |  |  |

| CMR      | 0x0048 | R/W | Clock Monitoring register            | 0000_0003  |  |  |  |

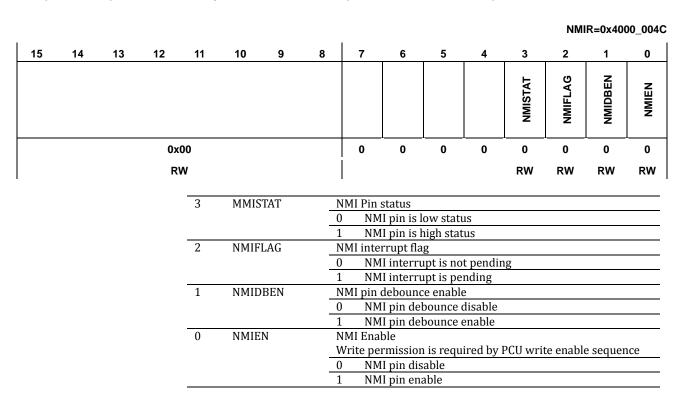

| NMIR     | 0x004C | R/W | NMI control register                 | 0000_0000  |  |  |  |

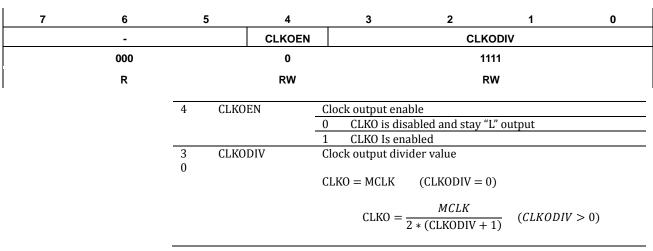

| COR      | 0x0050 | R/W | Clock Output Control register        | 0000_000F  |  |  |  |

| PLLCON   | 0x0060 | R/W | PLL Control register                 | 0000_1000  |  |  |  |

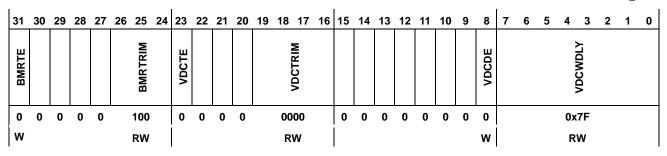

| VDCCON   | 0x0064 | R/W | VDC Control register                 | 0000_000F  |  |  |  |

| LVDCON   | 0x0068 | R/W | LVD Control register                 | 0000_0001  |  |  |  |

| IOSCTRIM | 0x006C | R/W | Internal RC OSC Control Register     | 0000_0000  |  |  |  |

| OPA0TRIM | 0x0070 | R/W | OPAM 0 trim register                 | 0000_0000  |  |  |  |

| OPA1TRIM | 0x0074 | R/W | OPAM 1 trim register                 | 0000_0000  |  |  |  |

| OPA2TRIM | 0x0078 | R/W | OPAM 2 trim register 000             |            |  |  |  |

| OPA3TRIM | 0x007C | R/W | OPAM 3 trim register                 | 0000_0000  |  |  |  |

| EOSCR    | 0x0080 | R/W | External Oscillator control register | 0000_0000  |  |  |  |

| EMODR    | 0x0084 | R/W | External mode pin read register      | 0000_000X  |  |  |  |

| DBCLK1 | 0x009C | R/W | Debounce Clock Control register 1 | 0000_0000 |

|--------|--------|-----|-----------------------------------|-----------|

| DBCLK2 | 0x00A0 | R/W | Debounce Clock Control register 2 | 0000_0000 |

| MCCR1  | 0x0090 | R/W | Misc Clock Control register 1     | 0404_0001 |

| MCCR2  | 0x0094 | R/W | Misc Clock Control register 2     | 0000_0000 |

| MCCR3  | 0x0098 | R/W | Misc Clock Control register 3     | 0000_0001 |

| MCCR4  | 0x00A4 | R/W | Misc Clock Control register 4     | 0000_0001 |

## **CIDR** Chip ID Register

The Chip ID Register shows chip identification information. This register is a 32-bit read-only register.

CIDR=0x4000\_0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20   | 19 | 18 | 17 | 16  | 15    | 14    | 13       | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|------|----|----|----|-----|-------|-------|----------|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    |    |    |    |    |    |      |    |    |    | СН  | IPID  |       |          |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |      |    |    | 0x | AC3 | 3_81  | 28    |          |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |      |    |    |    | I   | ₹     |       |          |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    | _  | 1  | C  | HIP  | ID |    |    | Г   | Devid | חו מי | <u> </u> |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    | (  | )  | C  | 1111 | ID |    |    |     | xAC   |       |          | 8  |    |    |   |   |   |   |   |   |   |   |   |   |

## **SMR** System Mode Register

The current operating mode is shown in this SCU mode register and the operation mode can be changed by writing the new mode in this register. The previous operating mode will be saved in this register after a reset event. System Mode Register is a 16-bit register.

SMR=0x4000\_0004

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4        | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|----------|---|---|---|---|

|    |    |    |    |    |    |   |   |   |   | Ļ | ñ        |   |   |   |   |

|    |    |    |    |    |    |   |   |   |   |   | 2        |   |   |   |   |

|    |    |    |    |    |    |   |   |   |   |   | <u> </u> |   |   |   |   |

|    |    |    |    |    |    |   |   |   |   | 8 | Ĭ        |   |   |   |   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0        | 0 | 0 | 0 | 0 |

|    |    |    |    |    |    |   |   |   |   | _ |          |   |   |   |   |

|    |    |    |    |    |    |   |   |   |   | F | •        |   |   |   | ļ |

| 5 | PREVMODE | Previous operating mode before current reset event. |  |  |  |  |  |  |  |

|---|----------|-----------------------------------------------------|--|--|--|--|--|--|--|

| 4 |          | 00 Previous operating mode was RUN mode             |  |  |  |  |  |  |  |

|   |          | 01 Previous operating mode was SLEEP mode           |  |  |  |  |  |  |  |

|   |          | 10 Previous operating mode was Power-down mode      |  |  |  |  |  |  |  |

|   |          | 11 Previous operating mode was INIT mode            |  |  |  |  |  |  |  |

PS034504-0617 PRELIMINARY 30

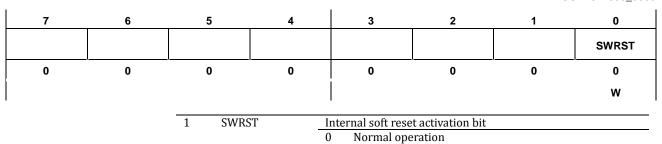

## **SRCR System Reset Control Register**

The System Reset Control Register allows the software to initiate a reset. This register also provides the polarity for the STBYOP pin.

#### SCR=0x4000\_0008

Internal soft reset is applied and auto cleared

PS034504-0617 PRELIMINARY 31

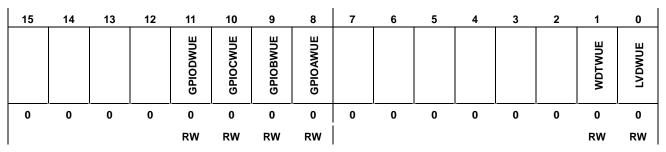

## **WUER Wakeup Source Enable Register**

This is the enable wakeup source. The source of chip wakeup should be enabled in each bit field. If the source will be used as the wakeup source, write **1** to its enable bit. If the source will not be used as the wakeup source, write **0** into its enable bit. This register is a 16-bit register.

#### WUER=-0x4000\_0010

| 12 | GPIOEWUE | Enable wakeup source of GPIOE port pin change event |

|----|----------|-----------------------------------------------------|

|    |          | 0 Not used for wakeup source                        |

|    |          | 1 Enable the wakeup event generation                |

| 11 | GPIODWUE | Enable wakeup source of GPIOD port pin change event |

|    |          | 0 Not used for wakeup source                        |

|    |          | 1 Enable the wakeup event generation                |

| 10 | GPIOCWUE | Enable wakeup source of GPIOC port pin change event |

|    |          | 0 Not used for wakeup source                        |

|    |          | 1 Enable the wakeup event generation                |

| 9  | GPIOBWUE | Enable wakeup source of GPIOB port pin change event |

|    |          | 0 Not used for wakeup source                        |

|    |          | 1 Enable the wakeup event generation                |

| 8  | GPIOAWUE | Enable wakeup source of GPIOA port pin change event |

|    |          | 0 Not used for wakeup source                        |

|    |          | 1 Enable the wakeup event generation                |

| 1  | WDTWUE   | Enable wakeup source of watchdog timer event        |

|    |          | 0 Not used for wakeup source                        |

|    |          | 1 Enable the wakeup event generation                |

| 0  | LVDWUE   | Enable wakeup source of LVD event                   |

|    |          | 0 Not used for wakeup source                        |

|    |          | 1 Enable the wakeup event generation                |

## **WUSR Wakeup Source Status Register**

When the system is woken up by any wakeup source, the wakeup source is identified by reading this register. When the bit is set to 1, the related wakeup source issues the wakeup to the SCU. The bit will be cleared when the event is cleared by the software.

### WUSR=0x4000\_0014

| 15 | 14 | 13 | 12 | 11      | 10      | 9       | 8     | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0     |

|----|----|----|----|---------|---------|---------|-------|---|---|---|---|---|---|-----|-------|

|    |    |    |    | 2       | 0       | 2       | 2     |   |   |   |   |   |   | _   |       |

|    |    |    |    | GPIODWU | GPIOCWU | GPIOBWU | IOAWU |   |   |   |   |   |   | UWT | -VDWU |

|    |    |    |    | GPIC    | GPIC    | GPIC    | GPIC  |   |   |   |   |   |   | WDT | ≥     |

|    |    |    |    |         |         |         |       |   |   |   |   |   |   |     |       |

| 0  | 0  | 0  | 0  | 0       | 0       | 0       | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0     |

|    |    |    |    | R       | R       | R       | R     |   |   |   |   |   |   | R   | R     |

| 12 | GPIOEWU | Status of wakeup source of GPIOE port pin change event |

|----|---------|--------------------------------------------------------|

|    |         | 0 No wakeup event                                      |

|    |         | 1 Wakeup event was generated                           |

| 11 | GPIODWU | Status of wakeup source of GPIOD port pin change event |

|    |         | 0 No wakeup event                                      |

|    |         | 1 Wakeup event was generated                           |

| 10 | GPIOCWU | Status of wakeup source of GPIOC port pin change event |

|    |         | 0 No wakeup event                                      |

|    |         | 1 Wakeup event was generated                           |

| 9  | GPIOBWU | Status of wakeup source of GPIOB port pin change event |

|    |         | 0 No wakeup event                                      |

|    |         | 1 Wakeup event was generated                           |

| 8  | GPIOAWU | Status of wakeup source of GPIOA port pin change event |

|    |         | 0 No wakeup event                                      |

|    |         | 1 Wakeup event was generated                           |

| 1  | WDTWU   | Status of wakeup source of watchdog timer event        |

|    |         | 0 No wakeup event                                      |

|    |         | 1 Wakeup event was generated                           |

| 0  | LVDWU   | Status of wakeup source of LVD event                   |

|    |         | 0 No wakeup event                                      |

|    |         | 1 Wakeup event was generated                           |

PS034504-0617 PRELIMINARY 33

## **RSER Reset Source Enable Register**

The reset source which will generate the reset event can be selected by the RSER register. Write 1 in the bit field of each reset source to transfer the reset source event to the reset generator. Write 0 in the bit field of each reset source to mask the reset source event, and therefore, not generate the reset event.

#### RSER=0x4000\_0018

| 7 | 6      |            | 5     | 4     | 3                                                                    | 2                 | 1     | 0      |  |  |  |  |

|---|--------|------------|-------|-------|----------------------------------------------------------------------|-------------------|-------|--------|--|--|--|--|

|   | PINRST | СР         | URST  | SWRST | WDTRST                                                               | MCKFRST           | XFRST | LVDRST |  |  |  |  |

| 0 | 1      | - <u>-</u> | 0     | 0     | 1                                                                    | 0                 | 0     | 1      |  |  |  |  |

|   | RW     | F          | RW    | RW    | RW                                                                   | RW                | RW    | RW     |  |  |  |  |

|   |        | 6 PINRS    |       | T .   | External pin rese                                                    |                   |       |        |  |  |  |  |

|   |        |            |       |       |                                                                      | this event is ma  |       |        |  |  |  |  |

|   |        |            | CDUD  | 2m    |                                                                      | this event is ena | ibled |        |  |  |  |  |

|   |        | 5          | CPURS |       | CPU request rese                                                     |                   | alrad |        |  |  |  |  |

|   |        |            |       | -     | 0 Reset from this event is masked 1 Reset from this event is enabled |                   |       |        |  |  |  |  |

|   |        | 4          | SWRS  | Г     | Software reset e                                                     |                   | ibieu |        |  |  |  |  |

|   |        | •          | SWIG  | •     |                                                                      | this event is ma  | sked  |        |  |  |  |  |

|   |        |            |       | •     | 1 Reset from this event is enabled                                   |                   |       |        |  |  |  |  |

|   |        | 3          | WDTF  | ST    | Watchdog Timer                                                       | reset enable bit  |       |        |  |  |  |  |

|   |        |            |       |       | 0 Reset from this event is masked                                    |                   |       |        |  |  |  |  |

|   |        |            |       |       | 1 Reset from                                                         | this event is ena | ıbled |        |  |  |  |  |

|   |        | 2          | MCKF  | RST   | MCLK Clock fail                                                      |                   |       |        |  |  |  |  |

|   |        |            |       | -     |                                                                      | this event is ma  |       |        |  |  |  |  |

|   |        |            |       |       |                                                                      | this event is ena |       |        |  |  |  |  |

|   |        | 1          | XFRST |       | External OSC Clo                                                     |                   |       |        |  |  |  |  |

|   |        |            |       | -     |                                                                      | this event is ma  |       |        |  |  |  |  |

|   |        | 0          | LVDRS | T     | 1 Reset from this event is enabled LVD reset enable bit              |                   |       |        |  |  |  |  |

|   |        | U          | LVDI  |       | 0 Reset from this event is masked                                    |                   |       |        |  |  |  |  |

|   |        |            |       | •     |                                                                      | this event is ena |       |        |  |  |  |  |

## **RSSR** Reset Source Status Register

The RSSR shows the reset source information when a reset event occurs. For a given reset source, 1 indicates that a reset event exists and 0 shows that a reset event does not exist. When a reset source is found, writing 1 to the corresponding bit will clear the reset status. This register is an 8-bit register.

#### RSSR=0x4000\_001C

| 7 6   |        | 5   |       | 4          | 3                                                                   | 2                                    | 1     | 0     |

|-------|--------|-----|-------|------------|---------------------------------------------------------------------|--------------------------------------|-------|-------|

| PORST | PINRST | СР  | JRST  | SWRST      | WDTRST                                                              | MCKFRST                              | XFRST | LVDRS |

| 1     | 0      | •   | 0     | 0          | 0                                                                   | 0                                    | 0     | 0     |

| RC1   | RC1    | RC1 |       | RC1        | RC1                                                                 | RC1                                  | RC1   | RC1   |

|       |        | 7   | PORS  | Τ .        | Write : no e                                                        | t from this even                     |       |       |

|       |        | 6   | PINRS | ST .       | External pin rese  Read : Rese Write : no e  Read : Rese            | t status bit<br>t from this even     |       |       |

|       |        | 5   | CPUR  | ST .       | O Read : Rese<br>Write : no e                                       | et status bit<br>et from this even   |       |       |

|       |        | 4   | SWRS  | T .        | Software reset st<br>0 Read : Rese<br>Write : no e<br>1 Read :Reset | atus bit<br>t from this even         |       |       |

|       |        | 3   | WDTI  | RST .      | Watchdog Timer 0 Read : Rese Write : no e 1 Read :Rese              | reset status bit<br>t from this even |       |       |

|       |        | 2   | MCLK  | FRST       | MCLK Fail reset  Read : Rese Write : no e  Read : Reset             | status bit<br>t from this even       |       |       |

|       |        | 1   | XFRS  | Γ <u>.</u> | Clock fail reset st 0 Read : Rese Write : no e 1 Read :Reset        | atus bit<br>t from this even         |       |       |

|       |        | 0   | LVDR  | ST .       | LVD reset status  Read : Rese Write : no e  Read : Reset            | bit<br>t from this even              |       |       |

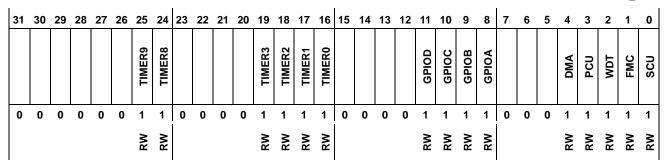

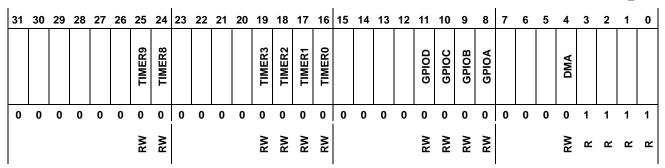

## PRER1 Peripheral Reset Enable Register 1

The reset of each peripheral by an event reset can be masked by user settings. The PRER1/2 register controls enabling of the event reset. If the corresponding bit is 1, the peripheral corresponding to this bit accepts the reset event. Otherwise, the peripheral is protected from the reset event and maintains its current operation.

#### PRER1=0x4000\_0020

| 25 | TIMER9 | TIMER9 reset mask                  |

|----|--------|------------------------------------|

| 24 | TIMER8 | TIMER8 reset mask                  |

| 19 | TIMER3 | TIMER3 reset mask                  |

| 18 | TIMER2 | TIMER2 reset mask                  |

| 17 | TIMER1 | TIMER1 reset mask                  |

| 16 | TIMER0 | TIMER0 reset mask                  |

| 11 | GPIOD  | GPIOE reset mask                   |

| 10 | GPIOC  | GPIOE reset mask                   |

| 9  | GPIOB  | GPIOE reset mask                   |

| 8  | GPIOA  | GPIOA reset mask                   |

| 4  | DMA    | DMA reset mask                     |

| 3  | PCU    | Port Control Unit reset mask       |

| 2  | WDT    | Watchdog Timer reset mask          |

| 1  | FMC    | Flash memory controller reset mask |

| 0  | SCU    | System Control Unit reset mask     |

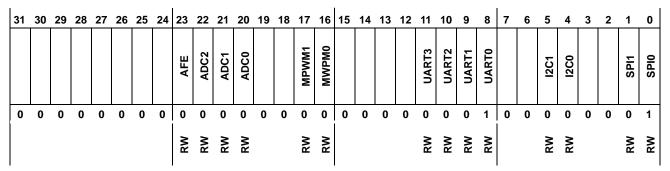

## PRER2 Peripheral Reset Enable Register 2

The reset of each peripheral by an event reset can be masked by user settings. The PRER1/2 register controls enabling of the event reset. If the corresponding bit is 1, the peripheral corresponding to this bit accepts the reset event. Otherwise, the peripheral is protected from the reset event and maintains its current operation.

#### PRER2=0x4000\_0024

| 23 | AFE   | AFE reset enable               |

|----|-------|--------------------------------|

| 22 | ADC2  | ADC2 reset enable              |

| 21 | ADC1  | ADC1 reset enable              |

| 20 | ADC0  | ADC0 reset enable              |

| 17 | MPWM1 | MPWM1 reset enable             |

| 16 | MPWM0 | MPWM0 reset enable             |

| 11 | UART3 | UART3 reset enable             |

| 10 | UART2 | UART2 reset enable             |

| 9  | UART1 | UART1 reset enable             |

| 8  | UART0 | UART0 reset enable             |

| 5  | I2C1  | I <sup>2</sup> C1 reset enable |

| 4  | I2C0  | I <sup>2</sup> CO reset enable |

| 1  | SPI1  | SPI1 reset enable              |

| 0  | SPI0  | SPIO reset enable              |

## PER1 Peripheral Enable Register 1

To use a peripheral unit, it should be activated by writing **1** to the corresponding bit in the PER1/2 register. Prior to activation, the peripheral stays in reset state.

To disable the peripheral unit, write **0** to the corresponding bit in the PER0/1 register, after which the peripheral enters the reset state.

#### PER1=0x4000\_0028

| 25 | TIMER9 | TIMER9 function enable |

|----|--------|------------------------|

| 24 | TIMER8 | TIMER8 function enable |

| 19 | TIMER3 | TIMER3 function enable |

| 18 | TIMER2 | TIMER2 function enable |

| 17 | TIMER1 | TIMER1 function enable |

| 16 | TIMER0 | TIMER0 function enable |

| 11 | GPIOD  | GPIOD function enable  |

| 10 | GPIOC  | GPIOC function enable  |

| 9  | GPIOB  | GPIOB function enable  |

| 8  | GPIOA  | GPIOA function enable  |

| 4  | DMA    | DMA function enable    |

| 3  |        |                        |

| 2  |        | Reserved               |

| 1  |        | nesei veu              |

| 0  |        |                        |

|    |        |                        |

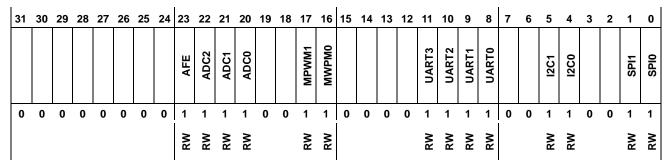

## PER2 Peripheral Enable Register 2

To use a peripheral unit, it should be activated by writing **1** to the corresponding bit in the PER1/2 register. Prior to activation, the peripheral stays in reset state.

To disable the peripheral unit, write  $\bf 0$  to the corresponding bit in the PER0/1 register, after which the peripheral enters the reset state.

#### PER2=0x4000\_002C

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22   | 21   | 20   | 19 | 18 | 17    | 16           | 15 | 14 | 13 | 12 | 11    | 10    | 9     | 8     | 7 | 6 | 5    | 4    | 3 | 2 | 1    | 0    |

|----|----|----|----|----|----|----|----|-----|------|------|------|----|----|-------|--------------|----|----|----|----|-------|-------|-------|-------|---|---|------|------|---|---|------|------|

|    |    |    |    |    |    |    |    | AFE | ADC2 | ADC1 | ADC0 |    |    | MPWM1 | <b>MWPM0</b> |    |    |    |    | UART3 | UART2 | UART1 | UART0 |   |   | I2C1 | 12C0 |   |   | SPI1 | SP10 |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0    | 0    | 0    | 0  | 0  | 0     | 0            | 0  | 0  | 0  | 0  | 0     | 0     | 0     | 1     | 0 | 0 | 0    | 0    | 0 | 0 | 0    | 1    |

|    |    |    |    |    |    |    |    | RW  | RW   | RW   | RW   |    |    | RW    | RW           |    |    |    |    | RW    | RW    | RW    | RW    |   |   | RW   | RW   |   |   | RW   | RW   |

| 23 | AFE   | AFE function enable               |

|----|-------|-----------------------------------|

| 22 | ADC2  | ADC2 function enable              |

| 21 | ADC1  | ADC1 function enable              |

| 20 | ADC0  | ADC0 function enable              |

| 17 | MPWM1 | MPWM1 function enable             |

| 16 | MPWM0 | MPWM0 function enable             |

| 11 | UART3 | UART3 function enable             |

| 10 | UART2 | UART2 function enable             |

| 9  | UART1 | UART1 function enable             |

| 8  | UART0 | UART0 function enable             |

| 5  | I2C1  | I <sup>2</sup> C1 function enable |

| 4  | I2C0  | I <sup>2</sup> C0 function enable |

| 1  | SPI1  | SPI1 function enable              |

| 0  | SPI0  | SPI0 function enable              |

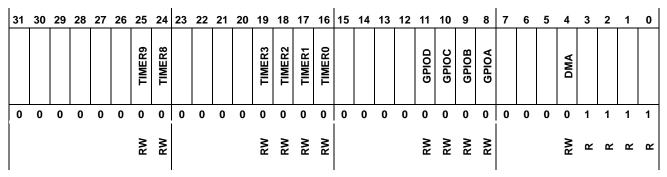

## PCER1 Peripheral Clock Enable Register 1

To use a peripheral unit, its clock should be activated by writing **1** to the corresponding bit in the PCER1/2 register. The peripheral will not operate correctly until its clock is enabled.

To stop the clock of the peripheral unit, write **0** to the corresponding bit in the PCER1/2 register.

#### PCER1=0x4000\_0030

| 25 | TIMER9 | TIMER9 clock enable |

|----|--------|---------------------|

| 24 | TIMER8 | TIMER8 clock enable |

| 19 | TIMER3 | TIMER3 clock enable |

| 18 | TIMER2 | TIMER2 clock enable |

| 17 | TIMER1 | TIMER1 clock enable |

| 16 | TIMER0 | TIMER0 clock enable |

| 11 | GPIOD  | GPIOD clock enable  |

| 10 | GPIOC  | GPIOC clock enable  |

| 9  | GPIOB  | GPIOB clock enable  |

| 8  | GPIOA  | GPIOA clock enable  |

| 4  | DMA    | DMA clock enable    |

| 3  |        |                     |

| 2  | •      | Reserved            |

| 1  | •      | neseiveu            |

| 0  |        |                     |

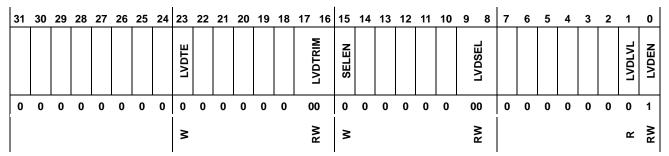

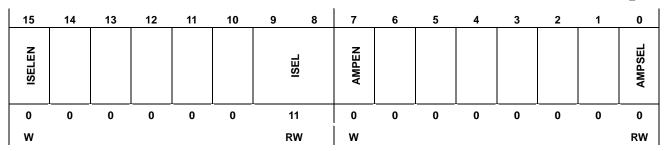

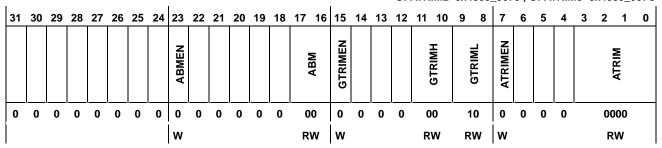

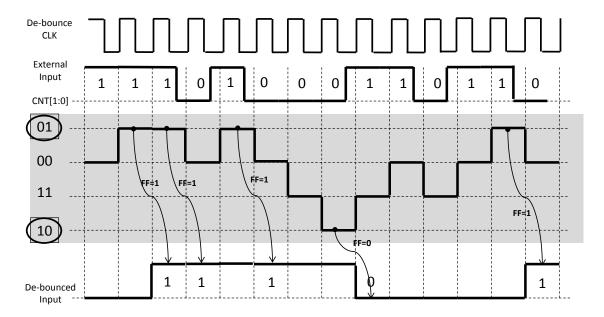

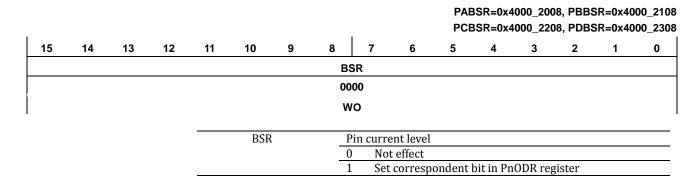

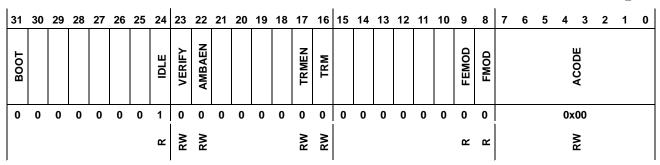

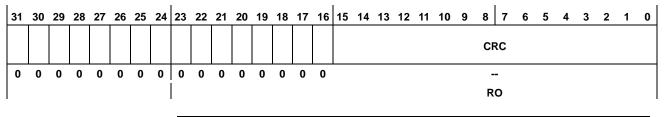

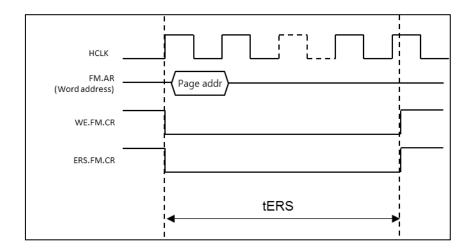

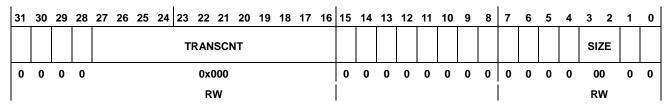

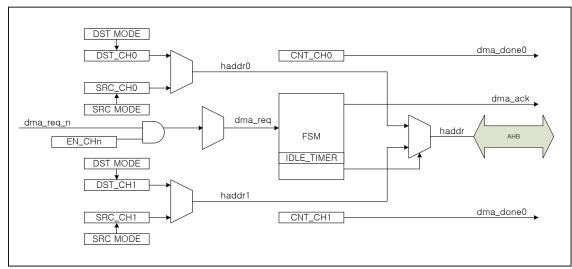

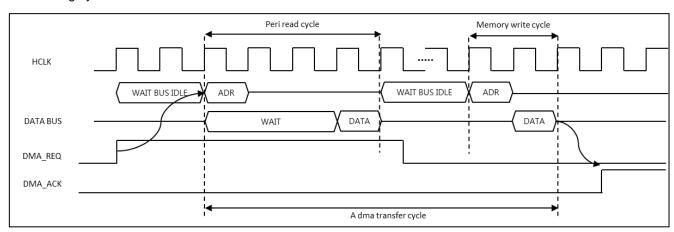

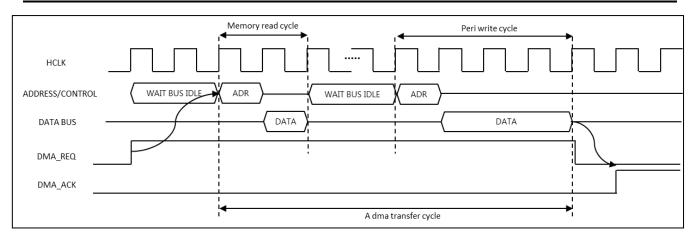

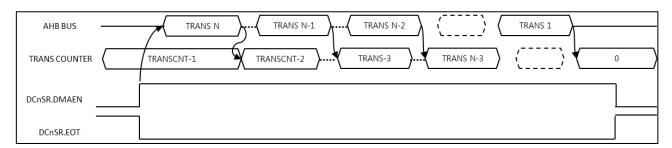

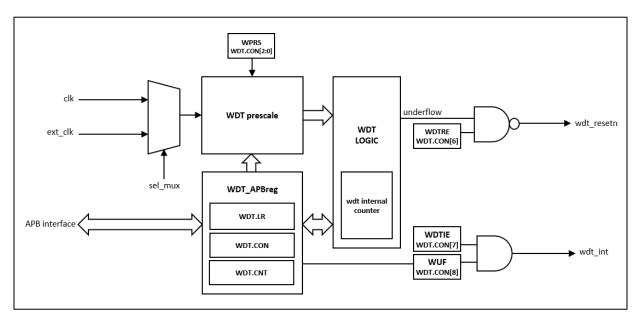

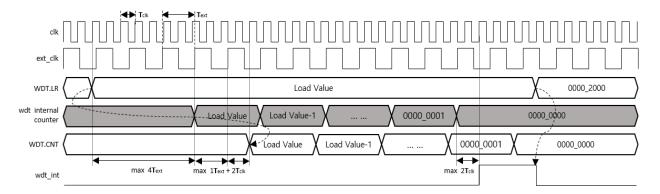

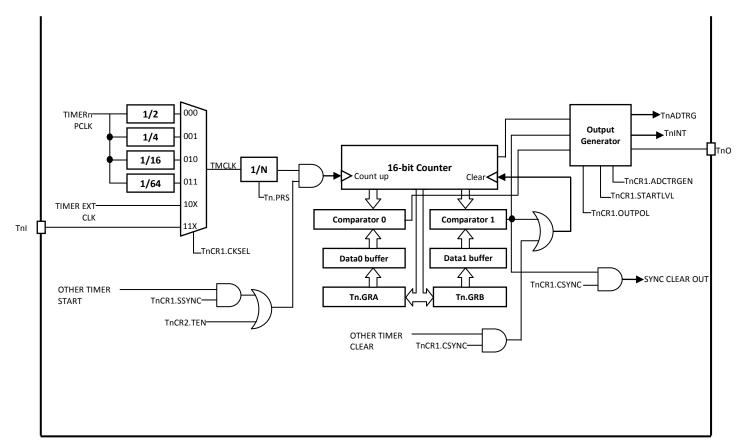

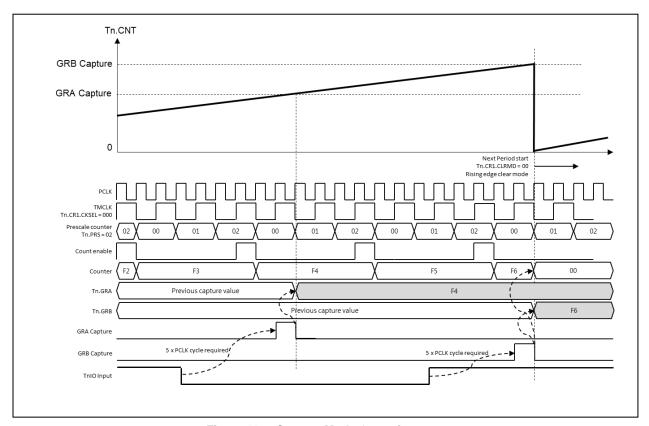

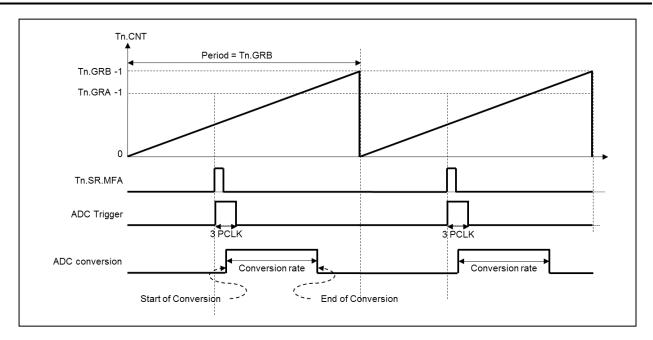

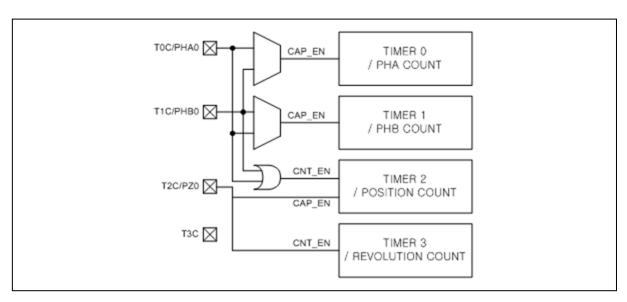

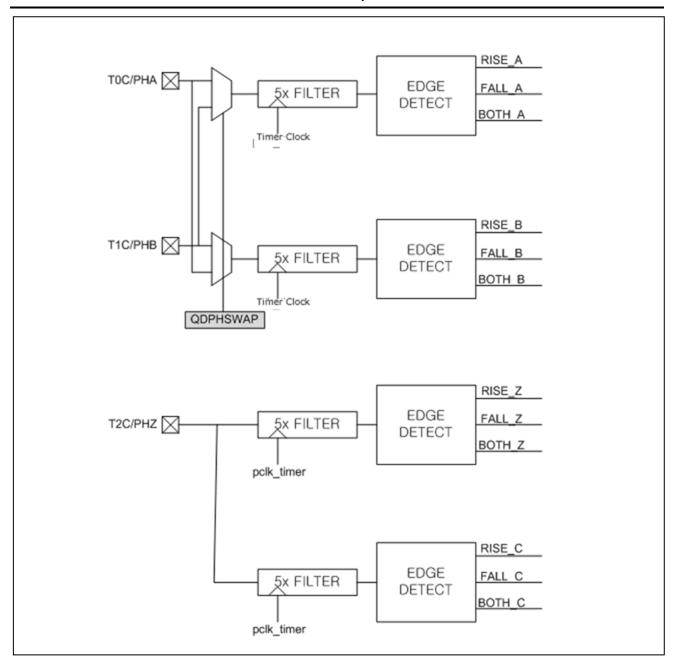

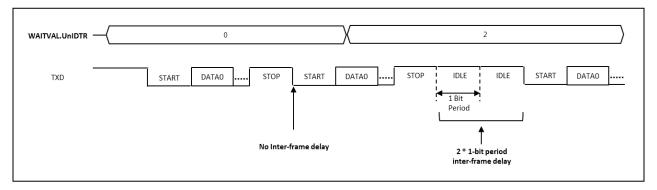

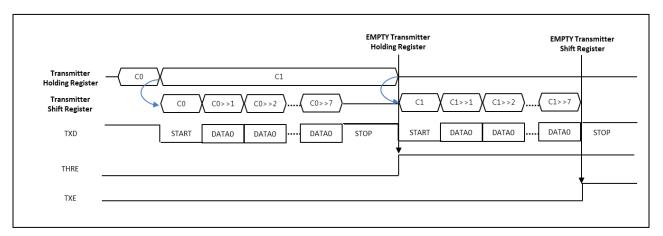

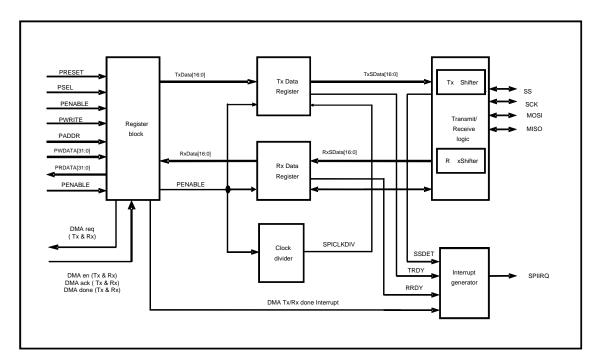

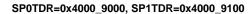

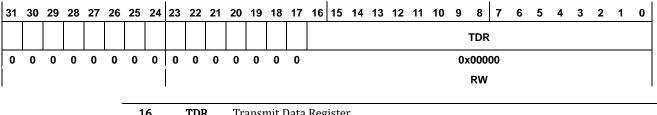

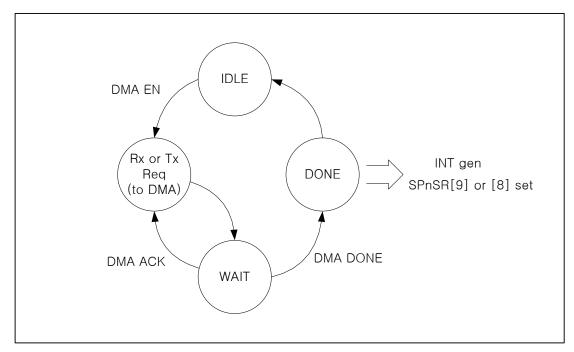

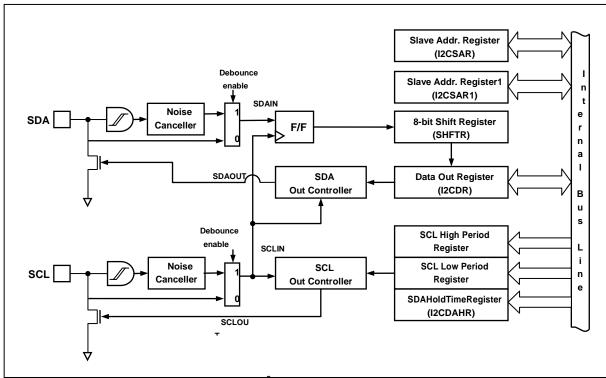

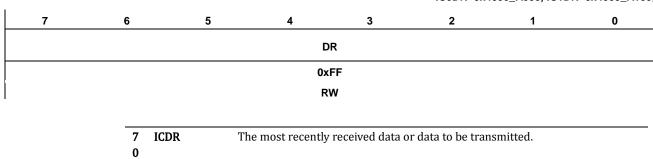

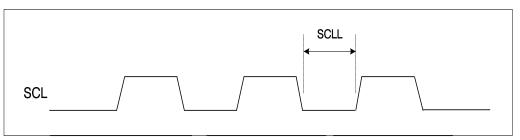

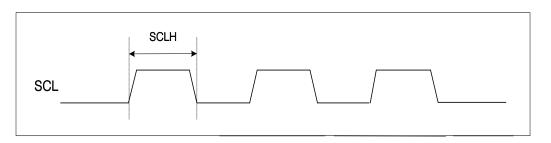

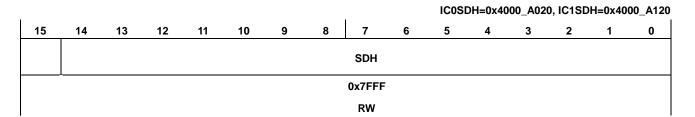

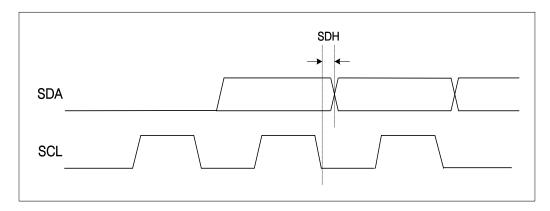

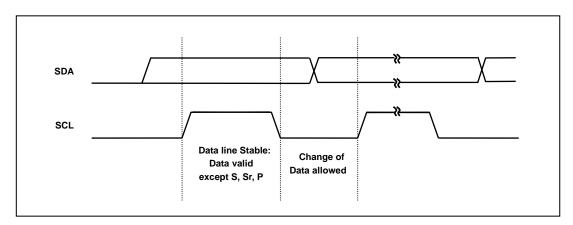

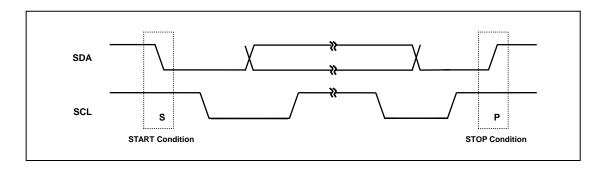

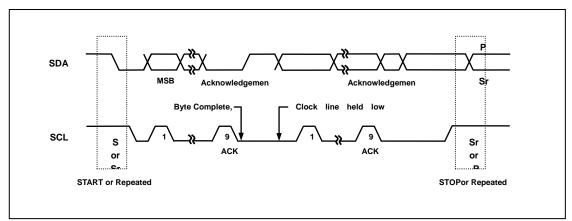

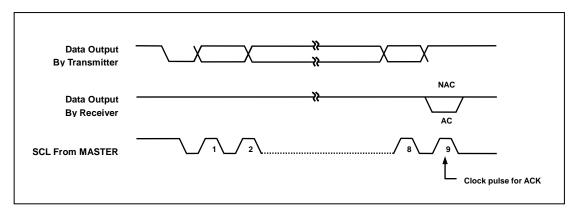

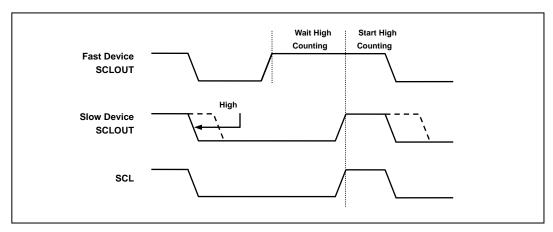

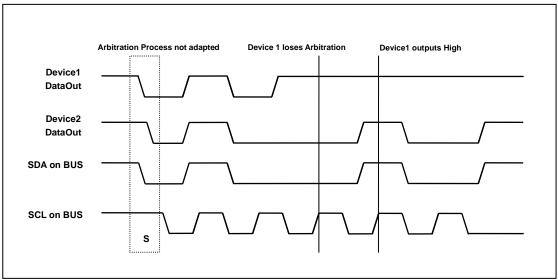

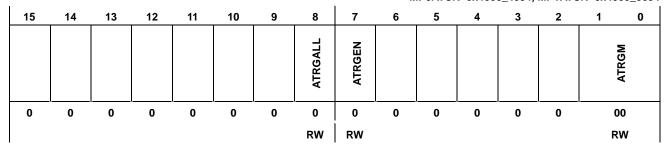

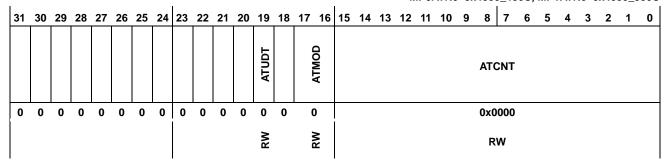

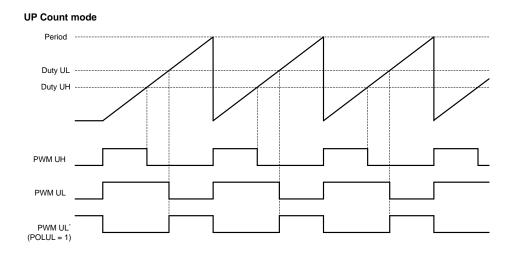

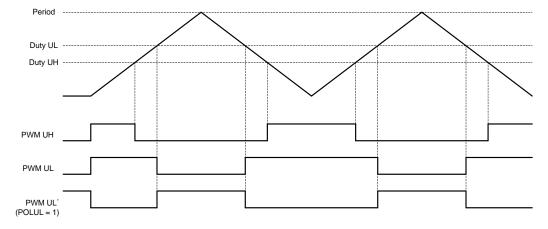

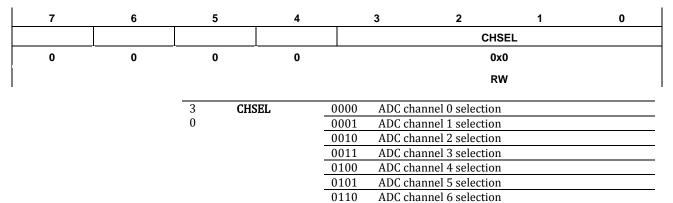

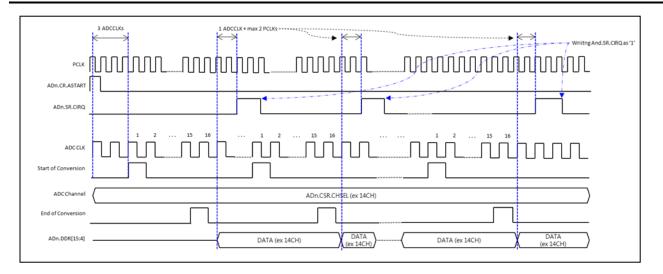

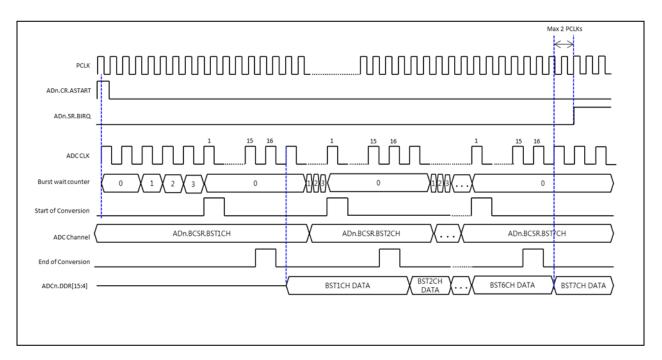

### PCER2