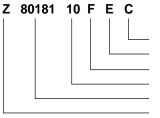

PRELIMINARY PRODUCT SPECIFICATION

### **Z80181** SMART ACCESS CONTROLLER (SAC<sup>M</sup>)

#### FEATURES

- Z80180 Compatible MPU Core with 1 Channel of Z85C30 SCC, Z80 CTC, Two 8-Bit General-Purpose Parallel Ports, and Two Chip Select Signals.

- High Speed Operation (10 MHz)

- Low Power Consumption in Two Operating Modes:

(TBD) mA Typ. (Run Mode)

- (TBD) mA Typ. (STOP Mode)

- Wide Operational Voltage Range (5V ±10%)

- TTL/CMOS Compatible

- Clock Generator

- One Channel of Z85C30 Serial Communication Controller (SCC)

- Z180 Compatible MPU Core Includes:

Enhanced Z80 CPU Core

- Memory Management Unit (MMU) Enables Access to 1MB of Memory

- Two Asynchronous Channels

- Two DMA Channels

- Two 16-Bit Timers

- Clocked Serial I/O Port

- On-Board Z84C30 CTC

- Two 8-Bit General-Purpose Parallel Ports

- Memory Configurable RAM and ROM Chip Select Pins

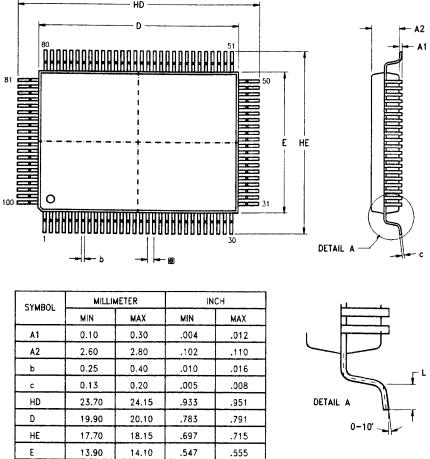

- 100-Pin QFP Package

#### **GENERAL DESCRIPTION**

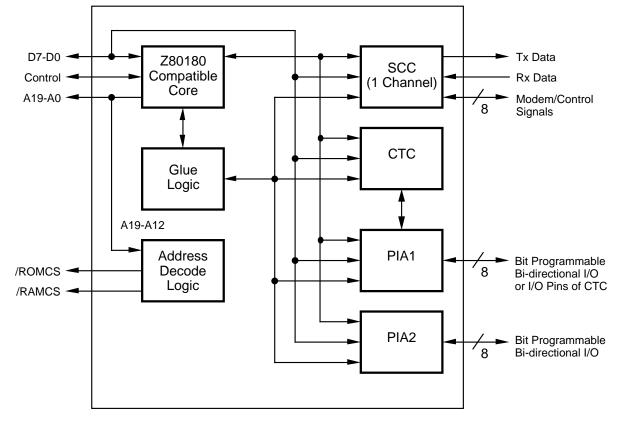

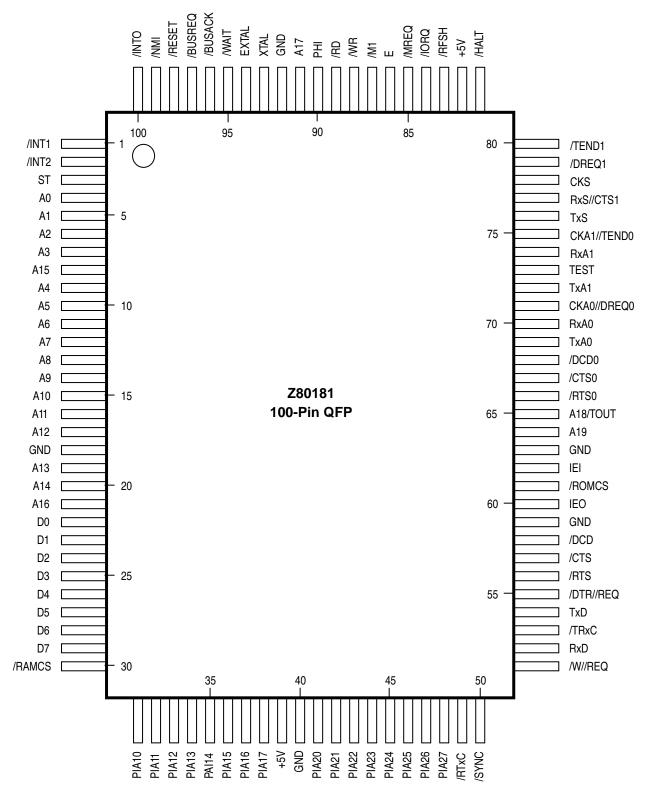

The Z80181 SAC<sup>™</sup> Smart Access Controller (hereinafter, referred to as Z181 SAC) is a sophisticated 8-bit CMOS microprocessor that combines a Z180-compatible MPU (Z181 MPU), one channel of Z85C30 Serial Communication Controller (SCC), a Z80 CTC, two 8-bit general-purpose parallel ports, and two chip select signals, into a single 100-pin Quad Flat Pack (QFP) package (Figures 1 and 2). Created using Zilog's patented Superintegration<sup>™</sup> methodology of combining proprietary IC cores and cells, this high-end intelligent peripheral controller is well-suited for a broad range of intelligent communication control applications such as terminals, printers, modems, and slave communication processors for 8-, 16- and 32- bit MPU based systems.

Information on enhancement/cost reductions of existing hardware using Z80/Z180 with Z8530/Z85C30 applications is also included in this product specification.

#### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g., B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

#### **GENERAL DESCRIPTION** (Continued)

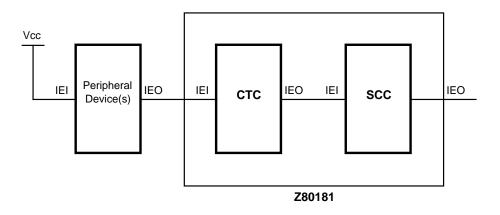

Z80181 = Z180 + SCC/2 + CTC + PIA

Figure 1. Z80181 Functional Block Diagram

#### **PIN DESCRIPTION**

Figure 2. 100-Pin QFP Pin Configuration

#### **CPU SIGNALS**

| Pin Name | Pin Number                 | Input/Output, Tri-State  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|----------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

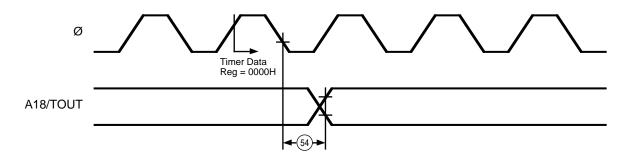

| A19 - A0 | 4-17, 19-21,<br>64, 65, 91 | I/O, Active 1            | Address Bus. A19 - A0 form a 20-bit address bus which specifies I/O and memory addresses to be accessed. During the refresh period, addresses for refreshing are output. The address bus enters a high-impedance state during Reset and external bus acknowledge cycles. The bus is an input when the external bus master is accessing the on-chip peripherals. Address line A18 is multiplexed with the output of PRT Channel 1 ( $T_{OUT}$ , selected as address output on Reset). |

| D0-D7    | 22-29                      | I/O, Active 1            | <b>8-Bit Bidirectional Data Bus.</b> When the on-chip CPU is accessing on-chip peripherals, these lines are outputs and hold the data to/from the on-chip peripherals.                                                                                                                                                                                                                                                                                                               |

| /RD      | 89                         | I/O, Active 0            | <b>Read Signal.</b> CPU read signal for accepting data from memory or I/O devices. When an external master is accessing the on-chip peripherals, it is an input signal.                                                                                                                                                                                                                                                                                                              |

| /WR      | 88                         | I/O, Active 0            | Write Signal. This signal is active when data to be stored<br>in a specified memory or peripheral device is on the MPU<br>data bus. When an external master is accessing the on-<br>chip peripherals, it is an input signal.                                                                                                                                                                                                                                                         |

| /MREQ    | 85                         | I/O, tri-state, Active 0 | <b>Memory Request Signal.</b> When an effective address for memory access is on the address bus, /MREQ is active. This signal is analogous to the /ME signal of the Z64180.                                                                                                                                                                                                                                                                                                          |

| /IORQ    | 84                         | I/O, tri-state, Active 0 | <b>I/O Request Signal.</b> When addresses for I/O are on the lower 8 bits (A7-A0) of the address bus in the I/O operation, "0" is output. In addition, the /IORQ signal is output with the /M1 signal during the interrupt acknowledge cycle to inform peripheral devices that the interrupt response vector is on the data bus. This signal is analogous to the /IOE signal of the Z64180.                                                                                          |

| /M1      | 87                         | I/O, tri-state, Active 0 | Machine Cycle "1". /MREQ and /M1 are active together<br>during the operation code fetch cycle. /M1 is output for<br>every opcode fetch when a two byte opcode is executed.<br>In the maskable interrupt acknowledge cycle, this signal is<br>output together with /IORQ. It is also used with<br>/HALT and ST signal to decode the status of the CPU<br>Machine cycle. This signal is analogous to the /LIR signal<br>of the Z64180.                                                 |

| /RFSH    | 83                         | Out, tri-state, Active 0 | <b>The Refresh Signal.</b> When the dynamic memory refresh address is on the low order 8-bits of the address bus (A7 - A0), /RFSH is active along with the /MREQ signal. This signal is analogous to the /REF signal of the Z64180.                                                                                                                                                                                                                                                  |

| Pin Name        | Pin Number | Input/Output, Tri-State  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /INTO           | 100        | Wired-OR I/O, Active 0   | <b>Maskable Interrupt Request 0.</b> Interrupt is generated by peripheral devices. This signal is accepted if the interrupt enable Flip-Flop (IFF) is set to "1". Internally, the SCC and CTC's interrupt signals are connected to this line, and require an external pull-up resistor.                                                                                                                                                                                                              |

| /INT1,<br>/INT2 | 1, 2,      | In, Active 0             | Maskable Interrupt Request 1 and 2. This signal is<br>generated by external peripheral devices. The CPU hon-<br>ors these requests at the end of current instruction cycle as<br>long as the /NMI, /BUSREQ and /INTO signals are inactive.<br>The CPU will acknowledge these interrupt requests with an<br>interrupt acknowledge cycle. Unlike the acknowledgment<br>for /INTO, during this cycle, neither /M1 or /IORQ will<br>become active.                                                       |

| /NMI            | 99         | In, Active 0             | <b>Non-Maskable Interrupt Request Signal.</b> This interrupt request has a higher priority than the maskable interrupt request and does not rely upon the state of the interrupt enable Flip-Flop (IFF).                                                                                                                                                                                                                                                                                             |

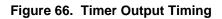

| HALT            | 81         | Out, tri-state, Active 0 | Halt Signal. This signal is asserted after the CPU has executed either the HALT or SLP instruction, and is waiting for either non-maskable interrupt maskable interrupt before operation can resume. It is also used with the /M1 and ST signals to decode the status of the CPU machine cycle.                                                                                                                                                                                                      |

| /BUSREQ         | 97         | In, Active 0             | <b>BUS Request Signal.</b> This signal is used by external devices (such as a DMA controller) to request access to the system bus. This request has higher priority than /NMI and is always recognized at the end of the current machine cycle. This signal will stop the CPU from executing further instructions and place the address bus, data bus, /MREQ, /IORQ, /RD and /WR signals into the high impedance state. /BUSREQ is normally wired-OR and a pull-up resistor is externally connected. |

| /BUSACK         | 96         | Out, Active 0            | <b>Bus Acknowledge Signal.</b> In response to /BUSREQ signal, /BUSACK informs a peripheral device that the address bus, data bus, /MREQ, /IORQ, /RD and /WR signals have been placed in the high impedance state.                                                                                                                                                                                                                                                                                    |

| /WAIT           | 95         | Wired-OR I/O, Active 0   | <b>Wait Signal.</b> /WAIT informs the CPU that the specified memory or peripheral is not ready for a data transfer. As long as /WAIT signal is active, the MPU is continuously kept in the wait state. Internally, the /WAIT signal from the SCC interface logic is connected to this line, and requires an external pull-up resistor.                                                                                                                                                               |

#### PERIPHERAL SIGNALS

| Pin Name    | Pin Number | Input/Output, Tri-State | Function                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXA0, RXA1  | 70, 74     | In, Active 1            | <b>ASCI Receive Data 0 and 1.</b> These signals are the receive data to the ASCI channels.                                                                                                                                                                                                                                                                                   |

| TXA0, TXA1  | 69, 72     | Out, Active 1           | <b>ASCI Transmit Data 0 and 1.</b> These signals are the receive data to the ASCI channels. Transmit data changes are with respect to the falling edge of the transmit clock.                                                                                                                                                                                                |

| /RTS0       | 66         | Out, Active 0           | <b>Request to Send 0.</b> This is a programmable modem control signal for ASCI channel 0.                                                                                                                                                                                                                                                                                    |

| /DCD0       | 68         | In, Active 0            | <b>Data Carrier Detect 0.</b> This is a programmable modem control signal for ASCI channel 0.                                                                                                                                                                                                                                                                                |

| /CTS0       | 67         | In, Active 0            | <b>Clear To Send 0.</b> This is a programmable modem control signal for ASCI channel 0.                                                                                                                                                                                                                                                                                      |

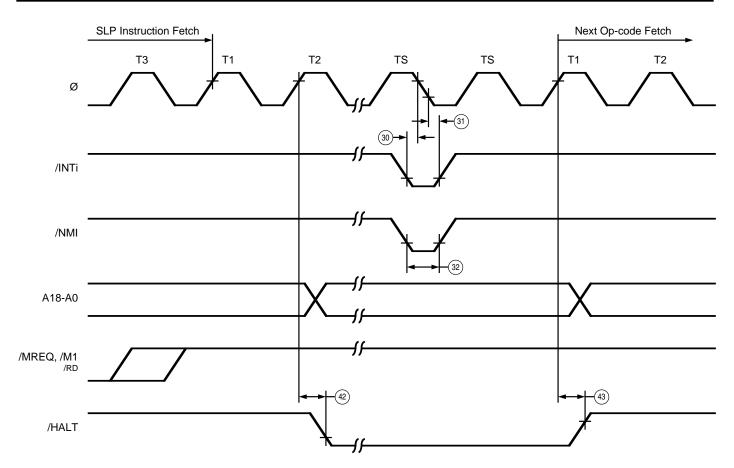

| /CTS1/RXS   | 77         | In, Active 0            | <b>Clear To Send 0/Clocked Serial Receive Data.</b> This is a programmable modem control signal for ASCI channel 0. Also, this signal becomes receive data for the CSIO channel under program control. On power-on Reset, this pin is set as RxS.                                                                                                                            |

| CKA0//DREQ0 | 71         | I/O, Active 1           | <b>Asynchronous Clock0/DMAC0 Request.</b> This pin is the transmit and receive clock for the Asynchronous channel 0. Also, under program control, this pin is used to request a DMA transfer from DMA channel 0. DMA0 monitors this input to determine when an external device is ready for a read or write operation. On power-on Reset, this pin is initialized as CKA0.   |

| CKA1//TEND0 | 75         | I/O, Active 1           | <b>Asynchronous Clock1/DMAC0 Transfer End.</b> This pin is<br>the transmit and receive clock for the Asynchronous chan-<br>nel 1. Also, under program control, this pin becomes<br>/TEND0 and is asserted during the last write cycle of the<br>DMA0 operation and is used to indicate the end of the<br>block transfer. On power-on Reset, this pin initializes<br>as CKA1. |

| /TEND1      | 80         | Out, Active 0           | <b>DMAC1 Transfer End.</b> This pin is asserted during the last write cycle of the DMA1 operation and is used to indicate the end of the block transfer.                                                                                                                                                                                                                     |

| CKS         | 78         | I/O, Active 1           | CSIO Clock. This line is the clock for the CSIO channel.                                                                                                                                                                                                                                                                                                                     |

| TXS         | 76         | Out, Active 1           | <b>CSI/O Tx Data.</b> This line carries the transmit data from the CSIO channel.                                                                                                                                                                                                                                                                                             |

| /DREQ1      | 79         | In, Active 0            | <b>DMAC1 Request.</b> This pin is used to request a DMA transfer from DMA channel 1. DMA1 monitors this input to determine when an external device is ready for a read or write operation.                                                                                                                                                                                   |

#### SCC SIGNALS

| Pin Name | Pin Number | Input/Output, Tri-State | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /W//REQ  | 51         | Active 0                | <b>Wait/Request.</b> Open-drain when programmed for a Wait function, driven "1" or "0" when programming for a Request function. Used as /WAIT or /REQUEST depending upon SCC programming. When programmed as /WAIT, this signal is asserted to alert the CPU that addressed memory or I/O devices are not ready and that the CPU should wait. When programmed as /REQUEST, this signal is asserted when a peripheral device associated with a DMA port is ready to read/write data. After reset, this pin becomes "/WAIT". |

| /SYNC    | 50         | I/O, Active 0           | <b>Synchronization.</b> This pin can act either as input, output, or part of the crystal oscillator circuit. In asynchronous receive mode (crystal oscillator option not selected), this pin is an input similar to /CTS and /DCD. In this mode, transitions on this line affect the state of the Sync/Hunt status bit in Read Register 0 but has no other function.                                                                                                                                                       |

|          |            |                         | In external sync mode with crystal oscillator option not<br>selected, this line also acts as an input. In this mode,<br>/SYNC must be driven "0" two receive clock cycles after<br>the last bit in the synchronous character is received.<br>Character assembly begins on the rising edge of the<br>receive clock immediately preceding the activation<br>of /SYNC.                                                                                                                                                        |

|          |            |                         | In internal sync mode (Monosync and Bisync) with the crystal oscillator option not selected, this line acts as output and is active only during the part of the receive clock cycle in which a synchronous character is recognized (regardless of character boundaries). In SDLC mode, this pin acts as an output and is valid on receipt of a flag.                                                                                                                                                                       |

| RxD      | 52         | In, Active 1            | <b>Receive Data.</b> This input signal receives serial data at standard TTL levels.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| /RTxC    | 49         | In, Active 0            | <b>Receive/Transmit Clock.</b> This pin can be programmed in several different modes of operation. /RTxC may supply the receive clock, the transmit clock, the clock for the Baud Rate Generator, or the clock for the Digital Phase-Locked Loop. This pin can also be programmed for use with the /SYNC pin as a crystal oscillator. The receive clocks can be 1, 16, 32, or 64 times the data transfer rate in Asynchronous mode.                                                                                        |

| /TRxC    | 53         | I/O, Active 0           | <b>Transmit/Receive Clock.</b> This pin can be programmed in several different modes of operation. /TRxC can supply the receive clock or the transmit clock in the input mode. Also, it can supply the output of the Digital Phase-Locked Loop, the crystal oscillator, the Baud Rate Generator, or the transmit clock in the output mode.                                                                                                                                                                                 |

# Zilog SCC SIGNALS (Continued)

| Pin Name  | Pin Number | Input/Output, Tri-State | Function                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxD       | 54         | Out, Active 1           | <b>Transmit Data.</b> This Output signal transmits serial data at standard TTL level.                                                                                                                                                                                                                                                                                                              |

| /DTR//REQ | 55         | Out, Active 0           | <b>Data Terminal Ready/Request.</b> This output follows the state programmed into the DTR bit. It can also be used as general-purpose output or as Request line for a DMA controller.                                                                                                                                                                                                              |

| /RTS      | 56         | Out, Active 0           | <b>Request To Send.</b> When the RTS bit in Write Register 5 is set, the /RTS signal goes low. When the RTS bit is reset in Asynchronous mode and auto enable is on, the signal goes high after the transmitter is empty. In synchronous mode or in Asynchronous mode, with Auto Enable off, the /RTS pin follows the state of the RTS bit. This pin can be used as a general-purpose output.      |

| /CTS      | 57         | In, Active 0            | <b>Clear To Send.</b> If this pin is programmed as auto enable,<br>a "0" on the input enables the transmitter. If not pro-<br>grammed as Auto Enable, it may be used as a general-<br>purpose input. This input is Schmitt-trigger buffered to<br>accommodate inputs with slow rise times. The SCC de-<br>tects pulses on this input and can interrupt the CPU on both<br>logic level transitions. |

| /DCD      | 58         | In, Active 0            | <b>Data Carrier Detect.</b> This pin functions as receiver enable<br>if it is programmed for auto enable. Otherwise, it may be<br>used as a general-purpose input. This input is Schmitt-<br>trigger buffered to accommodate slow rise-time inputs.<br>The SCC detects pulses on this input and can interrupt the<br>CPU on both logic level transitions.                                          |

#### PIA/CTC SIGNALS

| Pin Name    | Pin Number | Input/Output, Tri-State | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIA17-PIA14 | 35-38      | I/O                     | <b>Port 1 Data 7-Port 1 Data 4 or CTC ZC/TO3 - ZC/TO0.</b><br>These lines can be configured as inputs or outputs on a bit<br>-by-bit basis. Also, under program control, these bits<br>become Z80 CTC's ZC/TO3 - ZC/TO0, and in either timer<br>or counter mode, pulses are output when the down counter<br>has reached zero. On reset, these signals function as<br>PIA17-14 and are inputs.                                                                                                                              |

| PIA13-PIA10 | 31-34      | I/O                     | <b>Port 1 Data 3-Port 1 Data 0 or CTC CLK/TRG3-0.</b> These lines can be configured as inputs or outputs on a bit by bit basis. Also, under program control, these bits become Z80 CTC's CLK/TRG3-CLK/TRG0, and correspond to four Counter/Timer Channels. In the counter mode, each active edge causes the downcounter to decrement by one. In timer mode, an active edge starts the timer. It is program selectable whether the active edge is rising or falling. On reset, these signals are set to PIA13-10 as inputs. |

| PIA27-20    | 41-48      | Ι/Ο                     | <b>Port 2 Data.</b> These lines are configured as inputs or outputs on a bit-by-bit basis. On reset, they are inputs.                                                                                                                                                                                                                                                                                                                                                                                                      |

#### Zilog

| SYSTEM CONTROL SIGNALS | • |

|------------------------|---|

|------------------------|---|

| Pin Name | Pin Number | Input/Output, Tri-State | Fund                   | tion                       |                                     |                                                                                                                               |

|----------|------------|-------------------------|------------------------|----------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| ST       | 3          | Out, Active 1           | to de<br>the /N<br>OMC | code the st<br>1 output is | atus of th<br>affected<br>The follo | d with the /M1 and /HALT output<br>le CPU machine cycle. Note that<br>by the status of the M1E bit in the<br>wing table shows |

|          |            |                         | ST                     | /HALT                      | /M1                                 | Operation                                                                                                                     |

|          |            |                         | 0                      | 1                          | 0                                   | CPU Operation<br>(1st Opcode fetch)                                                                                           |

|          |            |                         | 1                      | 1                          | 0                                   | CPU Operation (2nd and 3rd Opcode fetch)                                                                                      |

|          |            |                         | 1                      | 1                          | 1                                   | CPU Operation<br>(MC other than Opcode fetch)                                                                                 |

|          |            |                         | 0                      | Х                          | 1                                   | DMA operation                                                                                                                 |

|          |            |                         | 0                      | 0                          | 0                                   | HALT mode                                                                                                                     |

|          |            |                         | 1                      | 0                          | 1                                   | SLEEP mode<br>(Incl. System STOP mode)                                                                                        |

| Pin Name        | Pin Number            | Input/Output, Tri-State | Function                                                                                                                                                                                                                            |

|-----------------|-----------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEI             | 62                    | In, Active 1            | <b>Interrupt enable input signal.</b> IEI is used with the IEO to form a priority daisy chain when there is more than one interrupt-driven peripheral.                                                                              |

| IEO             | 60                    | Out, Active 1           | The interrupt enable output signal. In the daisy-chain interrupt control, IEO controls the interrupt of external peripherals. IEO is active when IEI is "1" and the CPU is not servicing an interrupt from the on-chip peripherals. |

| /ROMCS          | 61                    | Out, Active 0           | <b>ROM Chip select.</b> Used to access ROM. Refer to "Func-<br>tional Description" on chip select signals for further expla-<br>nation.                                                                                             |

| /RAMCS          | 30                    | Out, Active 0           | <b>RAM Chip Select.</b> Used to access RAM. Refer to "Func-<br>tional Description" on chip select signals for further expla-<br>nation.                                                                                             |

| /RESET          | 98                    | In, Active 0            | <b>Reset signal.</b> /RESET signal is used for initializing the MPU and other devices in the system. It must be kept in the active state for a period of at least 3 system clock cycles.                                            |

| EXTAL           | 94                    | In, Active 1            | <b>Crystal oscillator connecting terminal.</b> A parallel resonant crystal is recommended. If an external clock source is used as the input to the Z180 Clock Oscillator unit, supply the clock into this terminal.                 |

| XTAL            | 93                    | Out                     | Crystal oscillator connecting terminal.                                                                                                                                                                                             |

| PHI             | 90                    | Out, Active 1           | System Clock. Single-phase clock output from Z181 MPU.                                                                                                                                                                              |

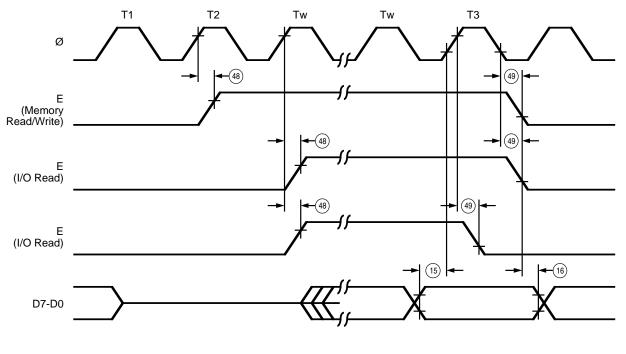

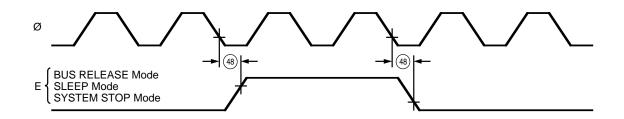

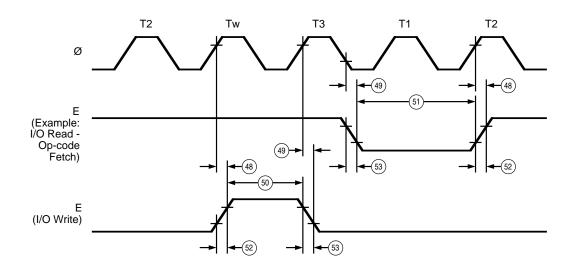

| E               | 86                    | Out, Active 1           | <b>Enable Clock.</b> Synchronous Machine cycle clock output during a bus transaction.                                                                                                                                               |

| TEST            | 73                    | Out                     | Test pin. Used in the open state.                                                                                                                                                                                                   |

| V <sub>cc</sub> | 39, 82                |                         | Power Supply. +5 Volts                                                                                                                                                                                                              |

| V <sub>SS</sub> | 18, 40, 59,<br>63, 92 |                         | Power Supply. 0 Volts                                                                                                                                                                                                               |

#### FUNCTIONAL DESCRIPTION

Functionally, the on-chip Z181 MPU, SCC, and CTC are the same as the discrete devices (Figure 1). Therefore, refer to the Product Specification/Technical Manual of each discrete product for a detailed description of each individual unit. The following subsections describe each individual functional unit of the SAC.

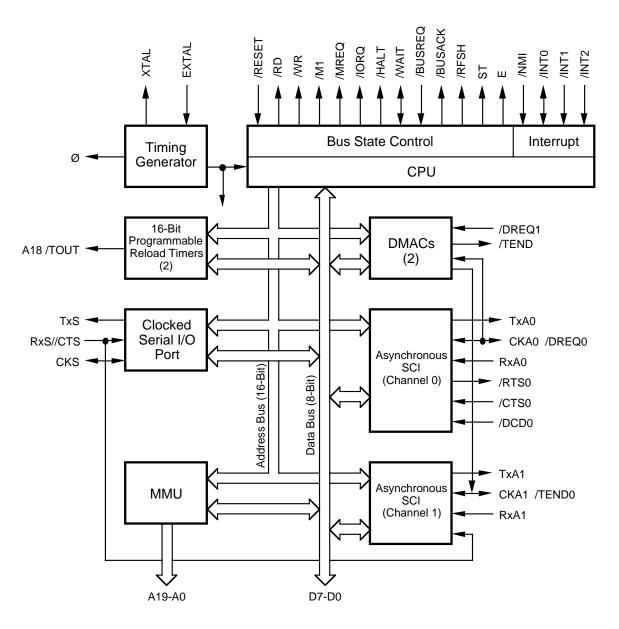

Figure 3. Z181 MPU Block Diagram

#### Z181 MPU

This unit provides all the capabilities and pins of the Zilog Z180 MPU. Figure 3 shows the Z181 MPU block diagram. This allows 100% software compatibility with existing Z180 (and Z80) software. Note that the on-chip I/O address should not be relocated to the I/O address (from 0C0h to 0FFh) to avoid address conflicts. The following is an overview of the major functional units of the Z181.

#### Z181 CPU

The Z181 CPU has 100% software compatibility with the Z80 CPU. In addition, the Z181 CPU has the following features:

**Faster execution speed.** The Z181 CPU is "fine tuned" making execution speed, on average, 10% to 20% faster than the Z80 CPU.

**Enhanced DRAM Refresh Circuit.** Z181 CPU's DRAM refresh circuit does periodic refresh and generates an 8-bit refresh address. It can be disabled or the refresh period adjusted, through software control.

**Enhanced Instruction Set.** The Z181 CPU has seven additional instructions to those of the Z80 CPU which include the MLT (Multiply) instruction.

**HALT and Low Power Modes of Operation.** The Z181 CPU has HALT and low power modes of operation, which are ideal for the applications requiring low power consumption like battery operated portable terminals.

**System Stop Mode.** When the Z181 SAC is in SYSTEM STOP mode, it is only the Z181 MPU which is in STOP mode. The on-chip CTC and SCC continue their normal operation.

**Instruction Set.** The instruction set of the Z181 CPU is identical to the Z180. For more details about each transaction, please refer to the Data Sheet/Technical Manual for the Z180/Z80 CPU.

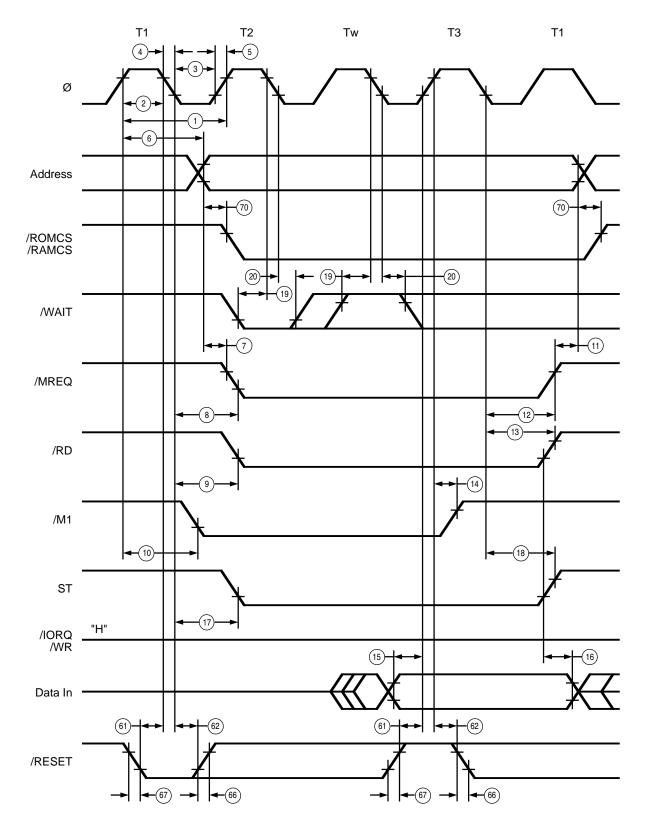

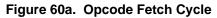

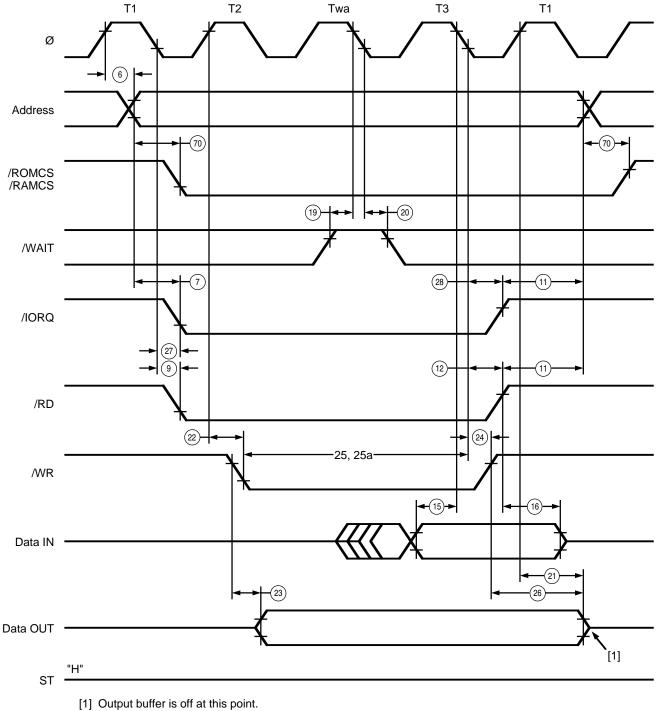

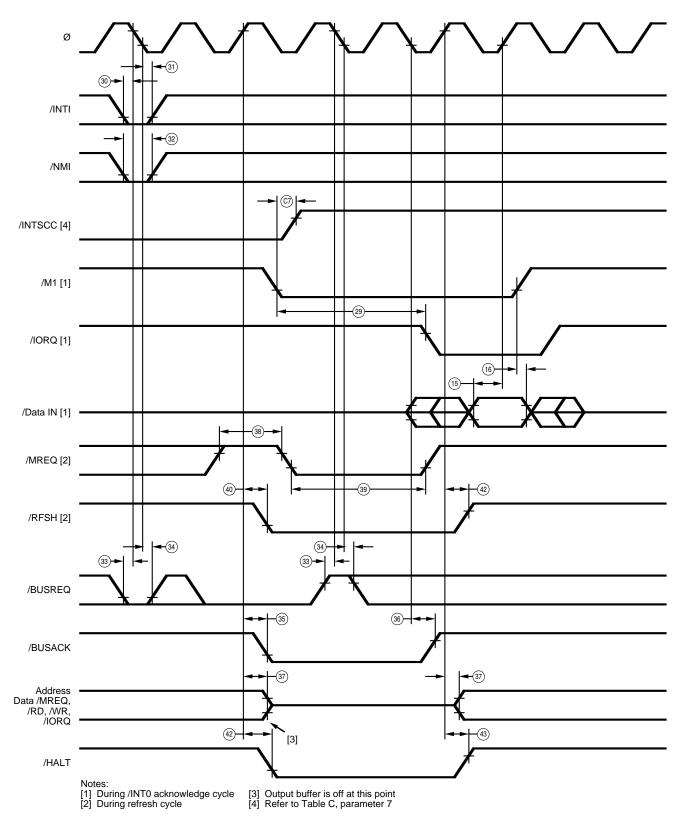

#### **Z181 CPU Basic Operation**

Z181 CPU's basic operation consists of the following events. These are identical to the Z180 MPU. For more details about each operation, please refer to the Data Sheet/Technical manual for the Z180.

- Operation code fetch cycle

- Memory Read/Write operation

- Input/Output operation

- Bus request/acknowledge operation

- Maskable interrupt request operation

- Trap and Non-Maskable interrupt request operation

- HALT and low power modes of operation

- Reset Operation

#### Memory Management Unit (MMU)

The Memory Management Unit (MMU) allows the user to "map" the memory used by the CPU (64K bytes of logical addressing space) into 1M bytes of physical addressing space. The organization of the MMU allows object code compatibility with the Z80 CPU while offering access to an extended memory space. This is accomplished by using an effective "common area-banked area" scheme.

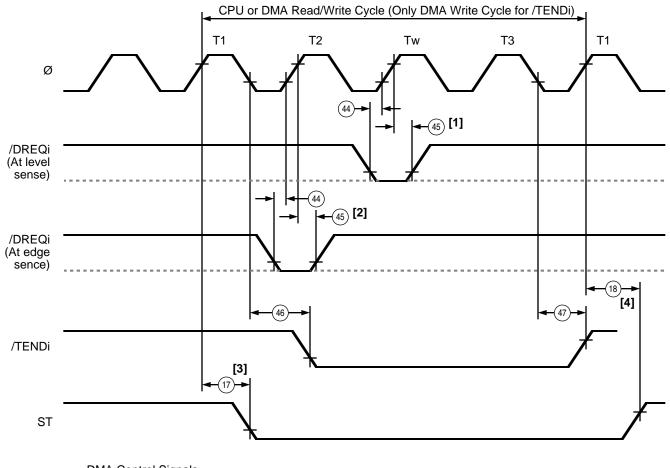

#### **DMA Controller**

The Z181 MPU has two DMA controllers. Each DMA controller provides high-speed data transfers between memory and I/O devices. Transfer operations supported are memory to memory, memory to/from I/O, and I/O to I/O. Transfer modes supported are request, burst, and cycle steal. The DMA can access the full 1M bytes addressing range with a block length up to 64K bytes and can cross over 64K boundaries.

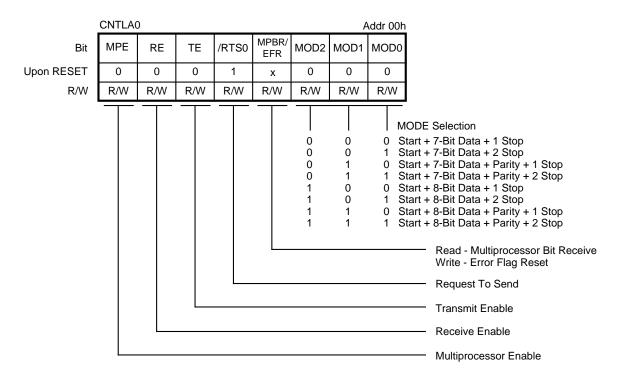

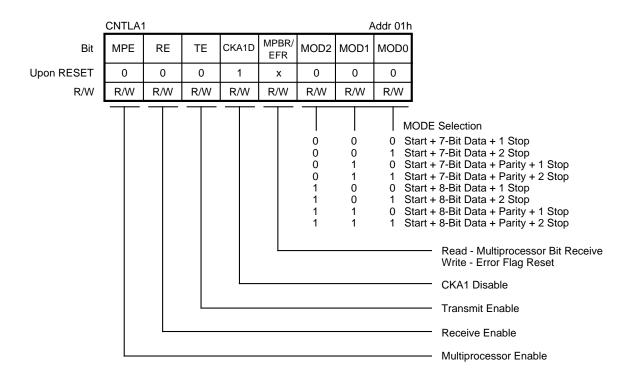

## Asynchronous Serial Communication Interface (ASCI)

This unit provides two individual full-duplex UARTs. Each channel includes a programmable baud rate generator and modem control signals. The ASCI channels also support a multiprocessor communication format.

#### Programmable Reload Timer (PRT)

The Z181 MPU has two separate Programmable Reload Timers, each containing a 16-bit counter (timer) and count reload register. The time base for the counters is system clock divided by 20. PRT channel 1 provides an optional output to allow for waveform generation.

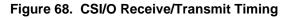

#### Clocked Serial I/O (CSI/O)

The CSI/O channel provides a half-duplex serial transmitter and receiver. This channel can be used for simple highspeed data connection to another CPU or MPU.

#### **Programmable Wait State Generator**

To ease interfacing with slow memory and I/O devices, the Z181 MPU unit has a programmable wait state generator. By programming the DMA/WAIT Control Register (DCNTL), up to three wait states are automatically inserted in memory and I/O cycles. This unit also inserts wait states during on-chip DMA transactions.

#### FUNCTIONAL DESCRIPTION (Continued)

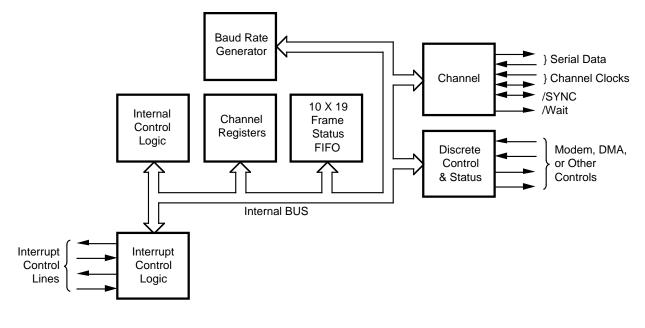

Figure 4. SCC Block Diagram

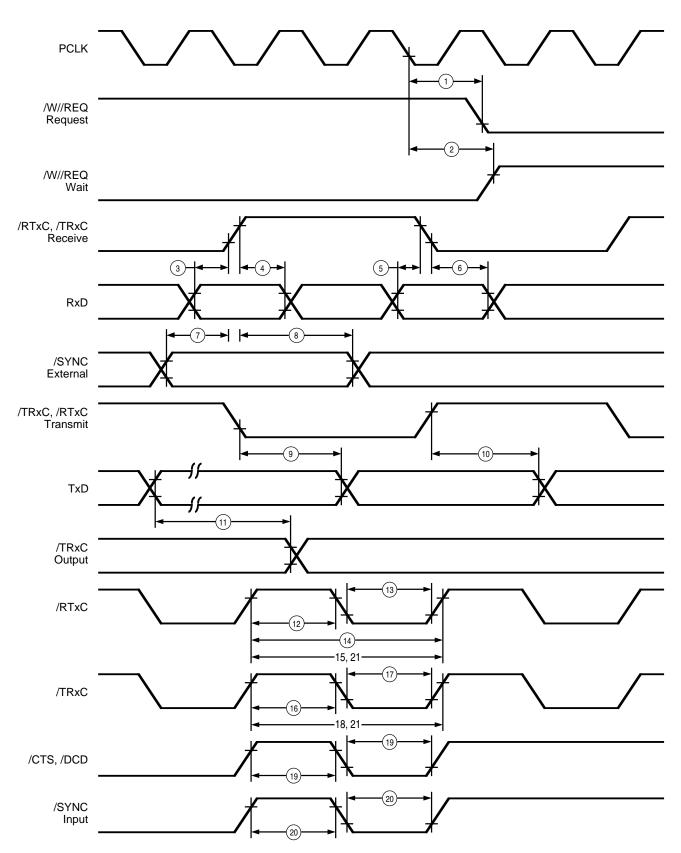

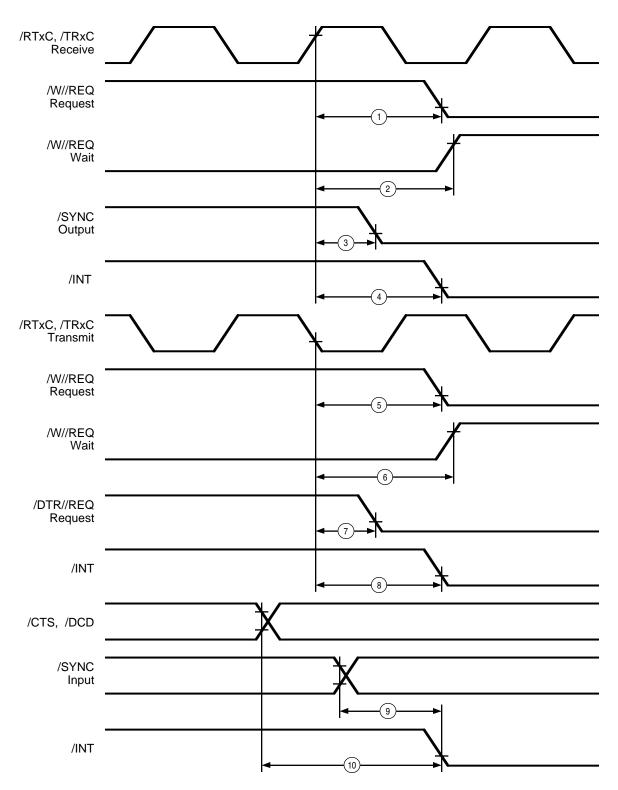

#### Z85C30 Serial Communication Controller Logic Unit

This logic unit provides the user with a multi-protocol serial I/O channel that is completely compatible with the two channel Z85C30 SCC with the following exceptions:

Their basic functions as serial-to-parallel and parallel-toserial converters can be programmed by the CPU for a broad range of serial communications applications. This logic unit is capable of supporting all common asynchronous and synchronous protocols (Monosync, Bisync, and SDLC/HDLC, byte or bit oriented - Figure 4).

On the discrete version of the SCC (dual channel version), there are two registers shared between channels A and B, and two registers whose functions are different by channel. These are: WR2, WR9 (shared registers), and RR2 and RR3 (different functionality).

Following are the differences in functionality:

RR2 - Returns Unmodified Vector or modified vector depends on the status of "VIS" (Vector Include Status) bit in WR9.

- **RR3** Returns IP status (Ch.A side).

- WR9 Ch.B Software Reset command has no effect.

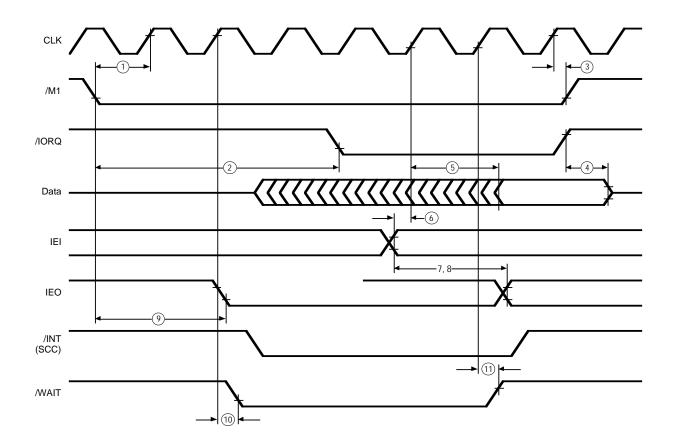

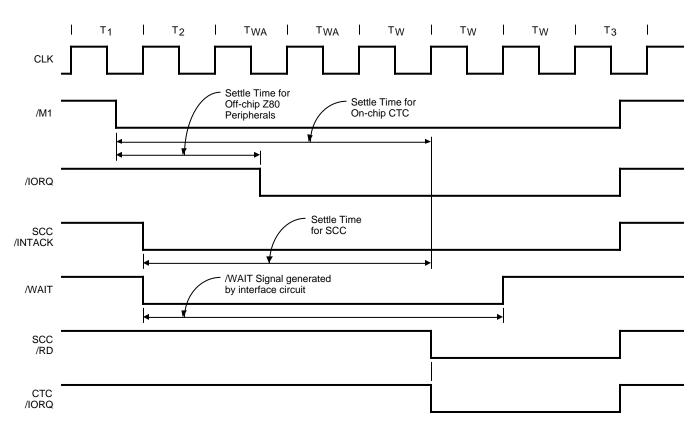

The PCLK for the SCC is connected to PHI (System clock), the /INT signal is connected to /INTO signal internally (requires external pull-up resistor) and SCC is reset when /RESET input becomes active. Interrupt from the SCC is handled through Mode 2 interrupt. During the interrupt acknowledge cycle, the on-chip SCC interface circuit inserts two wait states automatically.

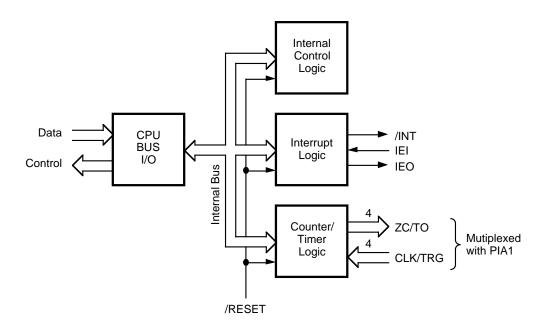

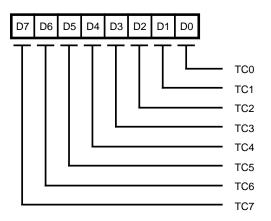

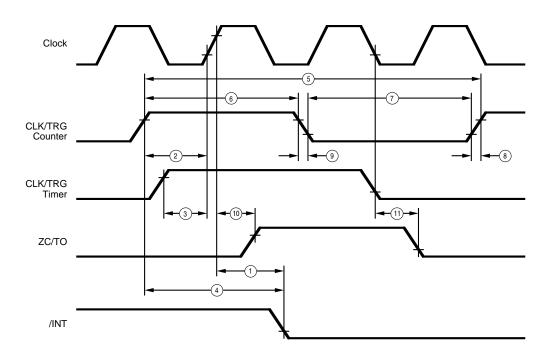

#### Z84C30 Counter/Timer Logic Unit

This logic unit provides the user with four individual 8-bit Counter/Timer Channels that are compatible with the Z84C30 CTC (Figure 5). The Counter/Timers are programmed by the CPU for a broad range of counting and timing applications. Typical applications include event counting, interrupt and interval counting, and serial baud rate clock generation. Each of the Counter/Timer Channels, designated Channels 0-3, have an 8-bit prescaler (when used in timer mode) and its own 8-bit counter to provide a wide range of count resolution. Each of the channels have their own Clock/Trigger input to quantify the counting process and an output to indicate zero crossing/timeout conditions. These signals are multiplexed with the Parallel Interface Adapter 1 (PIA1). With only one interrupt vector programmed into the logic unit, each channel can generate a unique interrupt vector in response to the interrupt acknowledge cycle.

Figure 5. CTC Block Diagram

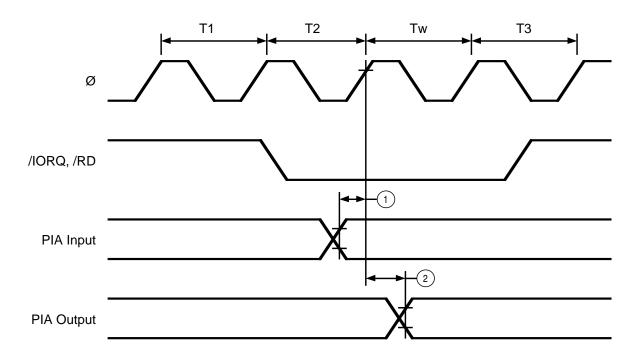

#### Parallel Interface Adapter (PIA)

The SAC has two 8-bit Parallel Interface Adapter (PIA) Ports. The ports are referred to as PIA1 and PIA2. Each port has two associated control registers; a Data Register and a register to determine each bit's direction (input or output). PIA1 is multiplexed with the CTC I/O pins. When the CTC I/O feature is selected, the CTC I/O functions override the PIA1 feature. Mode Selection is made through the System Configuration Register (Address: EDh; Bit D0). PIA1 has Schmitt-triggered inputs to have a better noise margin. These ports are inputs after reset.

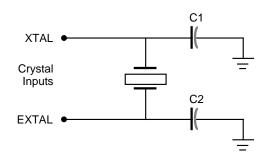

#### **Clock Generator**

The SAC uses the Z181 MPU's on-chip clock generator to supply system clock. The required clock is easily generated by connecting a crystal to the external terminals (XTAL, EXTAL). The clock output runs at half the crystal frequency. The system clock inputs of the SCC and the CTC are internally connected to the PHI output of the Z181 MPU.

Figure 6. Circuit Configuration For Crystal

#### FUNCTIONAL DESCRIPTION (Continued)

Recommended characteristics of the crystal and the values for the capacitor are as follows (the values will change with crystal frequency).

Type of crystal: Fundamental, parallel type crystal (AT cut is recommended).

Frequency tolerance: Application dependent. CL, Load capacitance: Approximately 22 pF (acceptable range is 20-30 pF)

Rs, equivalent-series resistance:  $\leq$  30 Ohms Drive level: 10 mW (for  $\leq$  10 MHz crystal) 5 mW (for  $\geq$  10 MHz crystal)

$C_{IN} = C_{OUT} = 15 \sim 22 \text{ pF}.$

#### **Chip Select Signals**

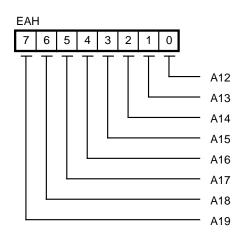

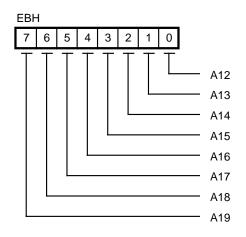

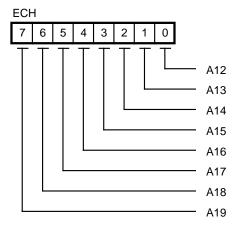

The SAC has two chip select (/RAMCS, /ROMCS) pins. /ROMCS is the chip select signal for ROM and /RAMCS is the chip select signal for RAM. The boundary value for each chip select signal is 8 bits wide allowing all memory accesses with addresses less than or equal to this boundary value. This causes assertion of the corresponding /CS pin. These features are controlled through the RAM upper boundary address register (I/O address EAh), RAM lower boundary address register (I/O address EBh) and ROM upper boundary address register (I/O address ECh). These two signals are generated by decoding address lines A19-A12. Note that glitches may be observed on the /RAMCS and /ROMCS signals because the address decoding logic decodes only A19-A12, without any control signals.

Bit D5 of the System Configuration Register allows the option of disabling the /ROMCS signal. This feature is used in systems which, for example, have a shadow RAM. However, prior to disabling the /ROMCS signal, the ROMBR and RAMLBR registers must be re-initialized from their default values.

For more details, please refer to "Programming section".

#### **ROM Emulator Mode**

To ease development, the SAC has a mode to support "ROM emulator" development systems. In this mode, a read data from on-chip registers (except Z181 MPU onchip registers) are available (data bus direction set to output) to make data visible from the outside, so that a ROM Emulator/Logic Analyzer can monitor internal transactions. Otherwise, a read from an internal transaction is not available to the outside (data bus direction set to Hi-Z status). Mode selection is made through the D1 bit in the System Configuration Register (I/O Address: EDh).

#### Programming

The following subsections explain and define the parameters for I/O Address assignments, I/O Control Register Addresses and all pertinent Timing parameters.

#### I/O Address Assignment

The SAC has 78 internal 8-bit registers to control on-chip peripherals and features. Sixty-four registers out of 78 registers are occupied by the Z181 MPU control registers;

two for SCC control registers, four for PIA control registers, four for the Counter/Timer, three for RAM/ROM configuration (memory address boundaries) and one for SAC's system control. The SAC's I/O addresses are listed in Table 1. These registers are assigned in the SAC's I/O addressing space and the I/O addresses are fully decoded from A7-A0 and have no image.

#### **PROGRAMMING** (Continued)

#### Table 1. I/O Control Register Address

| Address    | Register                                                                                           |

|------------|----------------------------------------------------------------------------------------------------|

| 00h        | Z181 MPU Control Registers                                                                         |

| to 3Fh     | (Relocatable to 040h-07Fh, or 080h-0BFh)                                                           |

| E0h        | PIA1 Data Direction Register (P1DDR)                                                               |

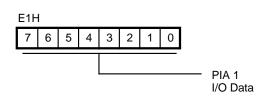

| E1h        | PIA1 Data Port (P1DP)                                                                              |

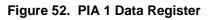

| E2h        | PIA2 Data Direction Register (P2DDR)                                                               |

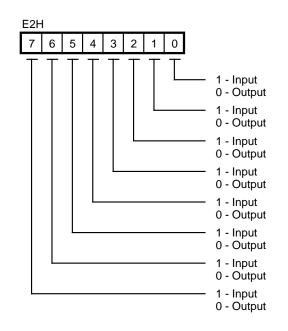

| E3h        | PIA2 Data Register (P2DP)                                                                          |

| E4h        | CTC Channel 0 Control Register (CTC0)                                                              |

| E5h        | CTC Channel 1 Control Register (CTC1)                                                              |

| E6h        | CTC Channel 2 Control Register (CTC2)                                                              |

| E7h        | CTC Channel 3 Control Register (CTC3)                                                              |

| E8h        | SCC Control Register (SCCCR)                                                                       |

| E9h        | SCC Data Register (SCCDR)                                                                          |

| EAh<br>EBh | RAM Upper Boundary Address Register<br>(RAMUBR)<br>RAM Lower Boundary Address Register<br>(RAMLBR) |

| ECh        | ROM Address Boundary Register (ROMBR)                                                              |

| EDh        | System Configuration Register (SCR)                                                                |

| EEh        | Reserved                                                                                           |

| EFh        | Reserved                                                                                           |

#### Z181 MPU Control Registers

The I/O address for these registers can be relocated in 64 byte boundaries by programming of the I/O Control Register (Address xx111111b).

Do not relocate these registers to address from 0C0h since this will cause an overlap of the Z180 registers and the 16 registers of the Z181 (address 0E0h to 0EFh).

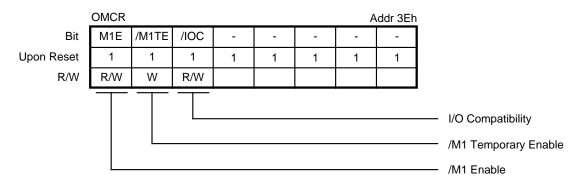

Also, the OMCR register (Address: xx111101b) must be programmed as 0x0xxxxb (x: don't care) as a part of the initialization procedure. The M1E bit (Bit D7) of this register must be programmed as 0 or the interrupt daisy chain is corrupted. The /IOC bit (Bit D5) of this register is programmed as 0 so that the timing of the /RD and /IORQ signals are compatible with Z80 peripherals.

For detailed information, refer to the Z180 Technical Manual.

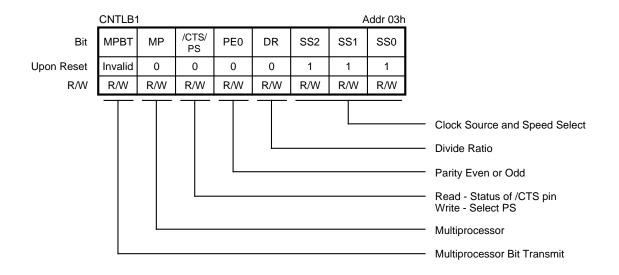

#### ASCI CHANNELS CONTROL REGISTERS

Figure 7. ASCI Control Register A (Ch. 0)

Figure 8. ASCI Control Register A (Ch. 1)

$\ensuremath{^+}$  /CTS - Depending on the condition of /CTS pin. PS - Cleared to 0.

| General<br>Divide Ratio<br>SS, 2, 1, 0 | PS = 0<br>(Divide Ratio = 10)<br>DR = 0 (x16) | DR = 1 (x64)   | PS = 1<br>(Divide Ratio = 30)<br>DR = 0 (x16) | DR = 1 (x64) |

|----------------------------------------|-----------------------------------------------|----------------|-----------------------------------------------|--------------|

| 000                                    | Ø÷ 160                                        | Ø÷640          | Ø ÷ 480                                       | Ø÷ 1920      |

| 001                                    | Ø ÷ 320                                       | Ø÷ 1280        | Ø÷960                                         | Ø÷ 3840      |

| 010                                    | Ø÷640                                         | Ø÷2580         | Ø÷1920                                        | Ø÷7680       |

| 011                                    | Ø÷ 1280                                       | Ø÷5120         | Ø÷3840                                        | Ø÷ 15360     |

| 100                                    | Ø÷2560                                        | Ø÷ 10240       | Ø ÷ 7680                                      | Ø÷ 30720     |

| 101                                    | Ø÷5120                                        | Ø÷20480        | Ø÷15360                                       | Ø÷ 61440     |

| 110                                    | Ø÷ 10240                                      | Ø÷ 40960       | Ø ÷ 30720                                     | Ø÷ 122880    |

| 111                                    | External Clock (Freque                        | ency < Ø ÷ 40) |                                               |              |

| Figure 9. | ASCI Control | <b>Register B</b> | (Ch. 0) |

|-----------|--------------|-------------------|---------|

|-----------|--------------|-------------------|---------|

#### ASCI CHANNELS CONTROL REGISTERS (Continued)

| General<br>Divide Ratio<br>SS, 2, 1, 0 | PS = 0<br>(Divide Ratio = 10)<br>DR = 0 (x16) | DR = 1 (x64)   | PS = 1<br>(Divide Ratio = 30)<br>DR = 0 (x16) | DR = 1 (x64) |

|----------------------------------------|-----------------------------------------------|----------------|-----------------------------------------------|--------------|

| 000                                    | Ø÷160                                         | Ø ÷ 640        | Ø÷ 480                                        | Ø÷ 1920      |

| 001                                    | Ø÷320                                         | Ø÷1280         | Ø÷960                                         | Ø÷ 3840      |

| 010                                    | Ø÷640                                         | Ø ÷ 2580       | Ø÷ 1920                                       | Ø÷7680       |

| 011                                    | Ø÷ 1280                                       | Ø÷5120         | Ø÷3840                                        | Ø÷ 15360     |

| 100                                    | Ø÷2560                                        | Ø÷ 10240       | Ø÷7680                                        | Ø÷ 30720     |

| 101                                    | Ø÷5120                                        | Ø ÷ 20480      | Ø÷ 15360                                      | Ø÷ 61440     |

| 110                                    | Ø÷ 10240                                      | Ø ÷ 40960      | Ø ÷ 30720                                     | Ø÷ 122880    |

| 111                                    | External Clock (Freque                        | ency < Ø ÷ 40) |                                               |              |

| Figure 10. | ASCI | Control | Register | B (Ch. 1) |

|------------|------|---------|----------|-----------|

|------------|------|---------|----------|-----------|

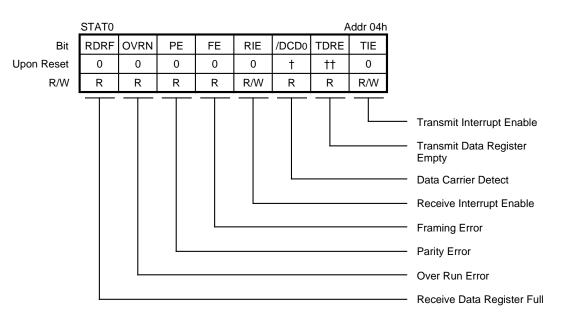

† /DCD0 - Depending on the condition of /DCD0 Pin.

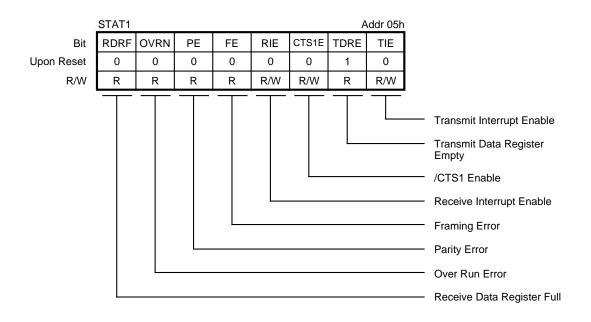

Figure 11. ASCI Status Register

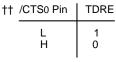

Figure 12. ASCI Status Register (Ch. 1)

#### ASCI CHANNELS CONTROL REGISTERS (Continued)

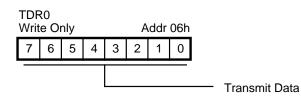

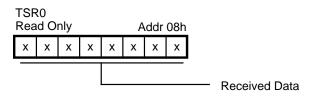

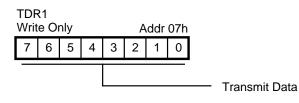

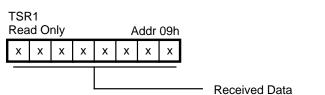

#### Figure 13. ASCI Transmit Data Register (Ch. 0)

Figure 15. ASCI Receive Data Register (Ch. 0)

Figure 14. ASCI Transmit Data Register (Ch. 1) Figure 16. ASCI Receive Data Register (Ch. 1)

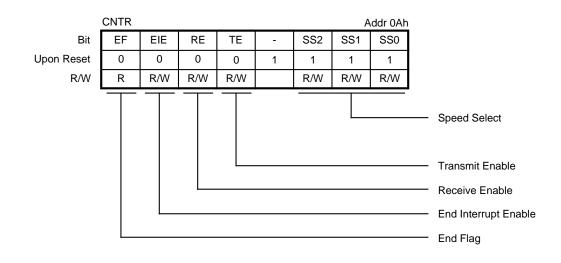

**CSI/O Registers**

| SS2, 1, 0 | Baud Rate | SS2, 1, 0 Baud Rate                |

|-----------|-----------|------------------------------------|

| 000       | Ø ÷ 20    | 100 Ø÷320                          |

| 001       | Ø ÷ 40    | 101 Ø ÷ 640                        |

| 010       | Ø ÷ 80    | 110 Ø÷1280                         |

| 011       | Ø÷ 100    | 111 External Clock                 |

|           |           | (Frequency $< \emptyset \div 20$ ) |

Zilog

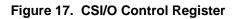

Read - Received Data Write - Transmit Data

#### TIMER REGISTERS

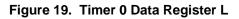

#### **Timer Data Registers**

| TMI<br>Rea | DR0<br>Id/W | _ |   |   | A | ddr | 0Ch |  |

|------------|-------------|---|---|---|---|-----|-----|--|

| 7          | 6           | 5 | 4 | 3 | 2 | 1   | 0   |  |

|   | <br>DR1<br>Id/W | - |   |   | A | ddr | 14h |  |

|---|-----------------|---|---|---|---|-----|-----|--|

| 7 | 6               | 5 | 4 | 3 | 2 | 1   | 0   |  |

| TMI<br>Rea | DR0<br>Id/W | ••• |    |    | А  | ddr | 0Dh | 1 |

|------------|-------------|-----|----|----|----|-----|-----|---|

| 15         | 14          | 13  | 12 | 11 | 10 | 9   | 8   |   |

When Read, read Data Register L before reading Data Register H.

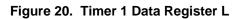

#### Figure 21. Timer 0 Data Register H

| TMI<br>Rea | DR1<br>Id/W | ••• |    |    | A  | ddr | 15h |  |

|------------|-------------|-----|----|----|----|-----|-----|--|

| 15         | 14          | 13  | 12 | 11 | 10 | 9   | 8   |  |

When Read, read Data Register L before reading Data Register H.

#### Figure 22. Timer 1 Data Register H

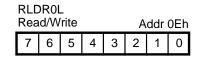

#### **Timer Reload Registers**

Figure 23. Timer 0 Reload Register L

|   |   | 0R1L<br>d/W | - |   |   | A | ddr | 16h |  |

|---|---|-------------|---|---|---|---|-----|-----|--|

| Γ | 7 | 6           | 5 | 4 | 3 | 2 | 1   | 0   |  |

Figure 24. Timer 1 Reload Register L

Addr 17h

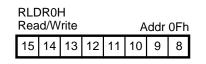

Timer Reload Registers (Continued)

Figure 25. Timer 0 Reload Register H

| Rea | id/W | rite |    |  |

|-----|------|------|----|--|

| 15  | 14   | 13   | 12 |  |

|     |      |      |    |  |

RLDR1H

Figure 26. Timer 1 Reload Register H

11 10 9 8

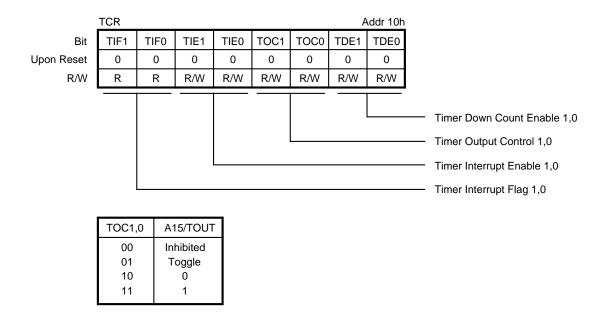

#### **Timer Control Register**

Figure 27. Timer Control Register

#### **Free Running Counter**

| FR0<br>Rea | - | nly |   |   | A | ddr | 18h | _ |

|------------|---|-----|---|---|---|-----|-----|---|

| 7          | 6 | 5   | 4 | 3 | 2 | 1   | 0   |   |

#### **DMA Registers**

| 0.47 |     |

|------|-----|

| SA7  | SA0 |

|      |     |

| SAF<br>Rea | ROH<br>Id/W | /rite |     | Addr 21h |  |  |  |  |

|------------|-------------|-------|-----|----------|--|--|--|--|

| SA1        |             |       | SA8 | 3        |  |  |  |  |

|            |             |       |     |          |  |  |  |  |

SAR0B Read/Write

х

х

Х

х

|   | d/W | rite |   |     | А | ddr | 22h  |   |

|---|-----|------|---|-----|---|-----|------|---|

|   |     |      |   | SA1 | 9 | S   | SA16 | 5 |

| - | -   | -    | - |     |   |     |      |   |

Bits 0-2 (3) are used for SAR0B

0 0

1

1

A19, A18, A17,

х

х

Х

х

| DAF | ROL |      |  |          |     |  |  |  |  |

|-----|-----|------|--|----------|-----|--|--|--|--|

| Rea | d/W | rite |  | Addr 23h |     |  |  |  |  |

| DA7 |     |      |  |          | DA0 |  |  |  |  |

|     |     |      |  |          |     |  |  |  |  |

|     |     |      |  |          |     |  |  |  |  |

|    | R0H<br>ad/W |  | А   | ddr | 24h |  |  |

|----|-------------|--|-----|-----|-----|--|--|

| DA | 15          |  | DA8 |     |     |  |  |

|    |             |  |     |     |     |  |  |

|   |   | R0B<br>Id/W | rite |   |     | A | ٩ddr | 25h |

|---|---|-------------|------|---|-----|---|------|-----|

|   |   |             |      |   | DA1 | 9 | D    | A16 |

| I | - | -           | -    | - |     |   |      |     |

Bits 0-2 (3) are used for DAR0B

| A19, A18 | , A17, A1 | 6 DMA Transfer Request |

|----------|-----------|------------------------|

| X X      | 0 0       | /DREQ0 (external)      |

| X X      | 0 1       | RDR0 (ASCI0)           |

| X X      | 1 0       | TDR0 (ASCI1)           |

| X X      | 1 1       | Not Used               |

### Figure 29. DMA 0 Source Address Registers

**DMA Transfer Request**

/DREQ0 (external) RDR0 (ASCI0) TDR0 (ASCI1)

Not Used

A16

0

1 0

1

#### Figure 30. DMA 0 Destination Address Registers

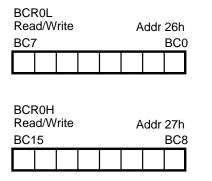

#### DMA REGISTERS (Continued)

#### Figure 31. DMA 0 Byte Counter Registers

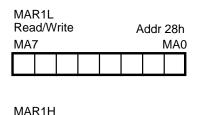

| Rea | id/W | rite | Addr 29 |  |  |     |  |  |

|-----|------|------|---------|--|--|-----|--|--|

| MA  | 15   |      |         |  |  | MA8 |  |  |

|     |      |      |         |  |  |     |  |  |

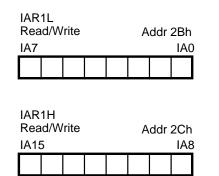

|   | R1B<br>ad/W | rite |   | Addr 2Ah |      |   |  |  |  |  |

|---|-------------|------|---|----------|------|---|--|--|--|--|

|   |             |      |   | MA1      | 1A16 | ; |  |  |  |  |

| - | -           | -    | - |          |      |   |  |  |  |  |

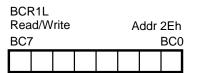

#### Figure 33. DMA 1 I/O Address Registers

| BCF<br>Rea | R1H<br>id/W | rite | A | ddr | 2Fh |     |   |

|------------|-------------|------|---|-----|-----|-----|---|

| BC1        | 5           |      |   |     |     | BC8 | 3 |

|            |             |      |   |     |     |     |   |

#### Figure 34. DMA 1 Byte Count Registers

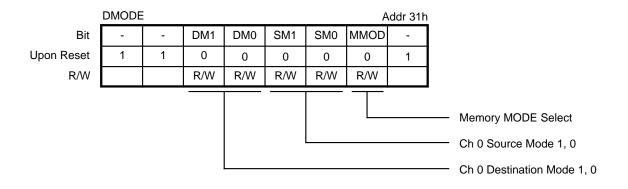

| DM1, 0               | Destination        | Address                                      | SM1, 0               | Source        | Address                                      |

|----------------------|--------------------|----------------------------------------------|----------------------|---------------|----------------------------------------------|

| 00<br>01<br>10<br>11 | M<br>M<br>M<br>I/O | DAR0+1<br>DAR0-1<br>DAR0 Fixed<br>DAR0 Fixed | 00<br>01<br>10<br>11 | M<br>M<br>I/O | SAR0+1<br>SAR0-1<br>SAR0 Fixed<br>SAR0 Fixed |

| MMOD | Mode             |

|------|------------------|

| 0    | Cycle Steal Mode |

| 1    | Burst Mode       |

Figure 36. DMA Mode Registers

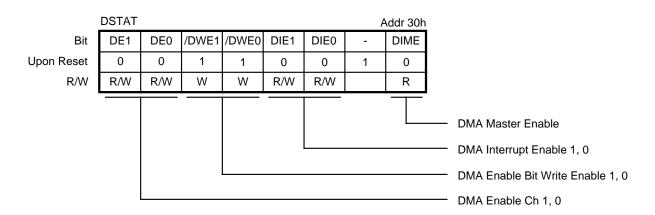

#### DMA REGISTERS (Continued)

|            | DCNTL |      |      |      |      |      | A    | ddr 32h |   |                                    |

|------------|-------|------|------|------|------|------|------|---------|---|------------------------------------|

| Bit        | MWI1  | MWI0 | IWI1 | IWI0 | DMS1 | DMS0 | DIM1 | DIM0    |   |                                    |

| Upon Reset | 1     | 1    | 1    | 1    | 0    | 0    | 0    | 0       |   |                                    |

| R/W        | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W     |   |                                    |

|            |       |      |      |      |      |      |      |         | - |                                    |

|            |       |      |      |      |      |      |      |         |   | DMA Ch 1 I/O Memory<br>Mode Select |

|            |       |      |      |      |      |      |      |         |   | /DREQi Select, i = 1, 0            |

|            |       |      |      |      |      |      |      |         |   | I/0 Wait Insertion                 |

|            |       |      |      |      |      |      |      |         |   | Memory Wait Insertion              |

| MWI1, 0 | No. of Wait States | IWI1, 0 | No. of Wait States |

|---------|--------------------|---------|--------------------|

| 00      | 0                  | 00      | 0                  |

| 01      | 1                  | 01      | 2                  |

| 10      | 2                  | 10      | 3                  |

| 11      | 3                  | 11      | 4                  |

| DMSi | Sense       |

|------|-------------|

| 1    | Edge Sense  |

| 0    | Level Sense |

| DM1, 0 | Transfer Mode | Address Increr | ment/Decrement |

|--------|---------------|----------------|----------------|

| 00     | M - I/O       | MAR1+1         | IAR1 Fixed     |

| 01     | M - I/O       | MAR1-1         | IAR1 Fixed     |

| 10     | I/O - M       | IAR1 Fixed     | MAR1+1         |

| 11     | I/O - M       | IAR1 Fixed     | MAR1-1         |

Figure 37. DMA/WAIT Control Register

#### **MMU Registers**

|            | CBR |     |     |     |     |     | A   | ddr 38h |  |

|------------|-----|-----|-----|-----|-----|-----|-----|---------|--|

| Bit        | CB7 | CB6 | CB5 | CB4 | CB3 | CB2 | CB1 | CB0     |  |

| Upon Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0       |  |

| R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W     |  |

|            |     |     |     |     |     |     |     |         |  |

|            |     |     |     | 1   |     |     |     |         |  |

MMU Common Base Register

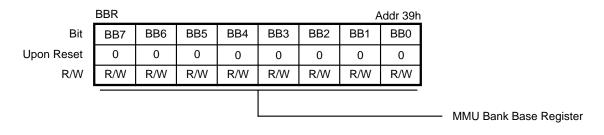

Figure 39. MMU Bank Base Register

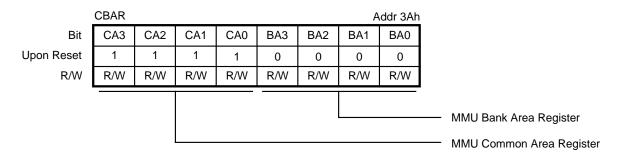

Figure 40. MMU Common/Bank Area Register

#### **System Control Registers**

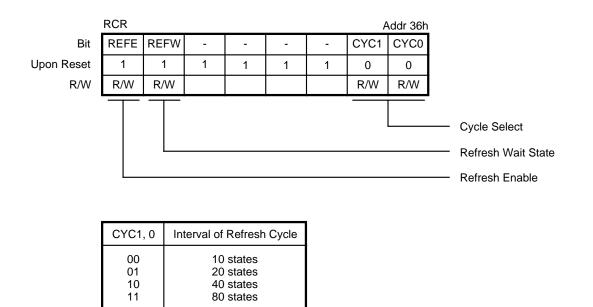

Figure 43. Refresh Control Register

Note: This register has to be programmed as 0x0xxxxxb(x:don't care) as a part of Initialization.

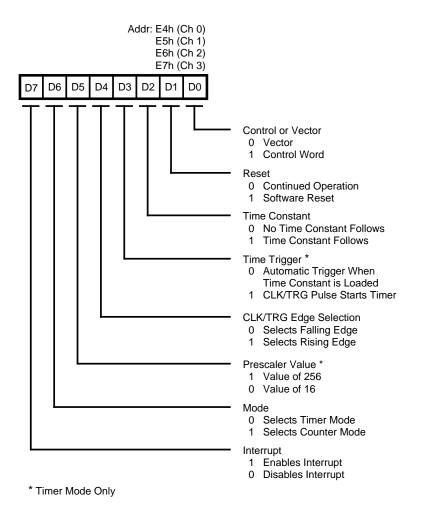

#### **CTC Control Registers**

#### **Channel Control Word**

This word sets the operating modes and parameters as described below. Bit D0 must be a "1" to indicate that this is a Control Word (Figure 46).

For more detailed information, refer to the CTC Technical Manual.

Figure 46. CTC Channel Control Word

This register has the following fields:

**Bit D7.** *Interrupt Enable.* This bit enables the interrupt logic so that an internal INT is generated at zero count. Interrupts are programmed in either mode and may be enabled or disabled at any time.

**Bit D6.** *Mode Bit.* This bit selects either Timer Mode or Counter Mode.

**Bit D5.** *Prescaler Factor.* This bit selects the prescaler factor for use in the timer mode. Either divide-by-16 or divide-by-256 is available.

**Bit D4.** *Clock/Trigger Edge Selector.* This bit selects the active edge of the CLK/TRG input pulses.

**Bit D3.** *Timer Trigger.* This bit selects the trigger mode for timer operation. Either automatic or external trigger may be selected.

**Bit D2.** *Time Constant.* This bit indicates that the next word programmed is time constant data for the downcounter.

**Bit D1.** *Software Reset.* Writing a "1" to this bit indicates a software reset operation, which stops counting activities until another time constant word is written.

#### Time Constant Word

Before a channel can start counting, it must receive a time constant word. The time constant value may be anywhere between 1 and 256, with "0" being accepted as a count of 256 (Figure 47).

Figure 47. CTC Time Constant Word

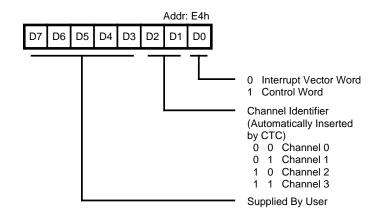

#### Interrupt Vector Word

If one or more of the CTC channels have interrupt enabled, then the Interrupt Vector Word is programmed. Only the five most significant bits of this word are programmed, and bit D0 must be "0". Bits D2-D1 are automatically modified by the CTC channels after responding with an interrupt vector (Figure 48).

Figure 48. CTC Interrupt Vector Word

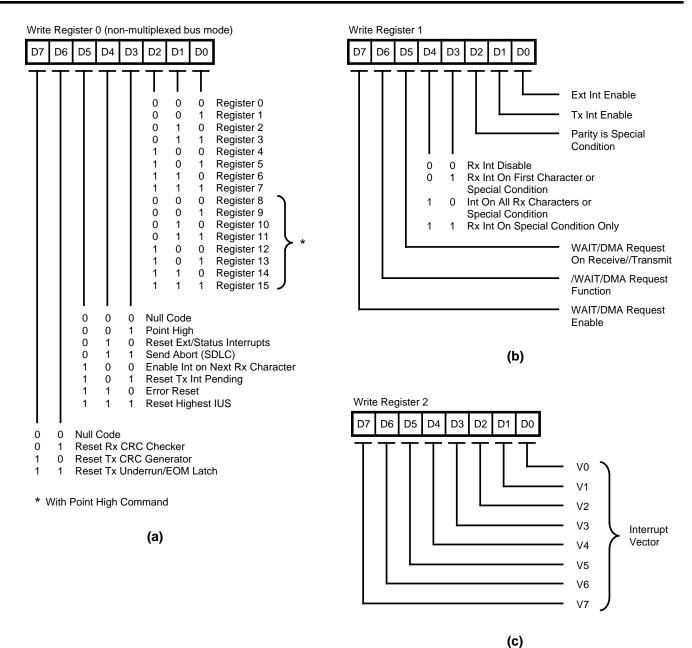

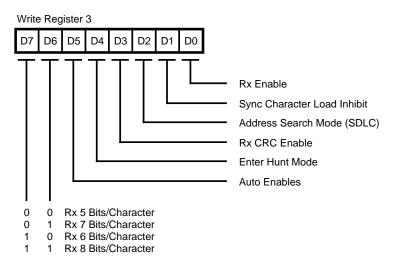

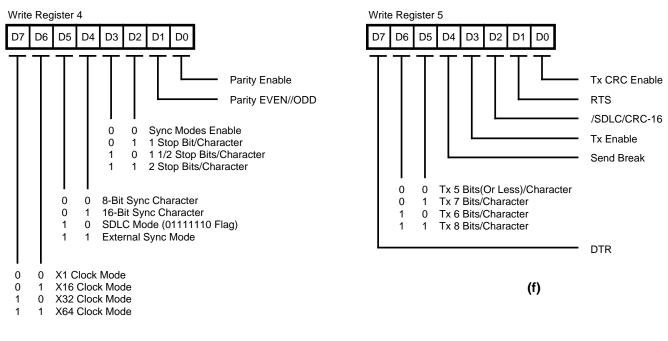

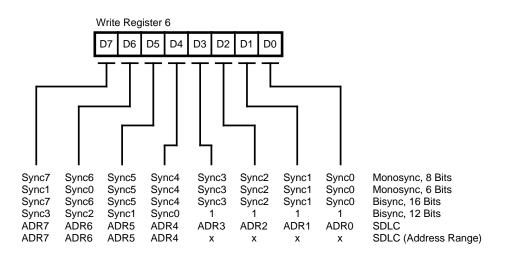

#### SCC REGISTERS

For more detailed information, please refer to the Z8030/ Z8530 SCC Technical Manual.

#### Note:

The Address for the Control/Status Register is E8h. The Address for the Data Register is E9h.

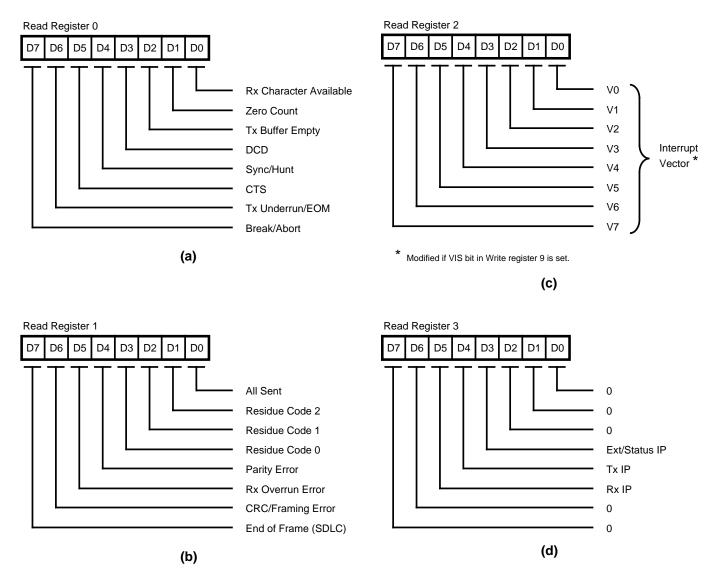

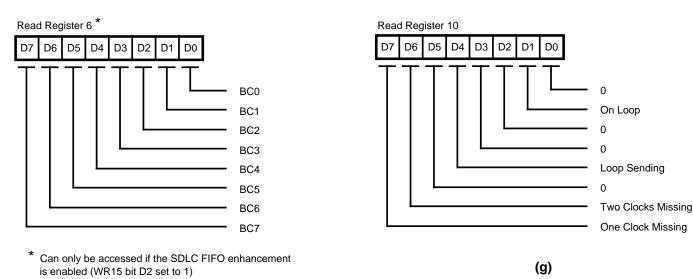

#### **Read Registers**

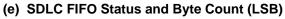

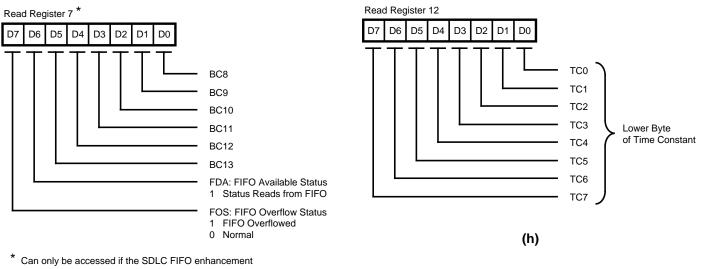

The SCC contains eight read registers. To read the contents of a register (rather than RR0), the program must first initialize a pointer to WR0 in exactly the same manner as a write operation. The next I/O read cycle will place the contents of the selected read registers onto the data bus (Figure 49).

| Bit | Description                                             | Bit  | Description                                          |

|-----|---------------------------------------------------------|------|------------------------------------------------------|

| RR0 | Transmit and Receive buffer status and external status. | RR7  | SDLC FIFO byte count and status (only when enabled). |

| RR1 | Special Receive Condition status.                       | RR8  | Receive buffer.                                      |

| RR2 | Interrupt vector (modified if VIS Bit in WR9 is set).   | RR10 | Miscellaneous status bits.                           |

| RR3 | Interrupt pending bits.                                 | RR12 | Lower byte of baud rate.                             |

| RR6 | SDLC FIFO byte counter lower byte                       | RR13 | Upper byte of baud rate generator time constant.     |

|     | (only when enabled).                                    | RR15 | External Status interrupt information.               |

#### Table 2. SCC Read Registers

### SCC REGISTERS (Continued)

Figure 49. SCC Read Register Bit Functions

2-34

is enabled (WR15 bit D2 set to 1)

#### (f) SDLC FIFO Status and Byte Count (MSB)

#### SCC REGISTERS (Continued)

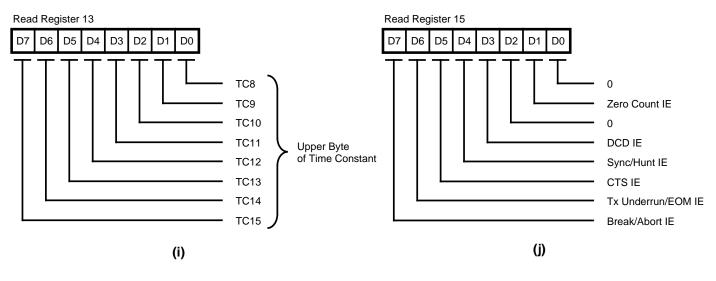

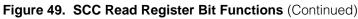

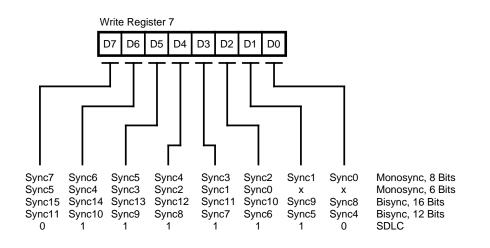

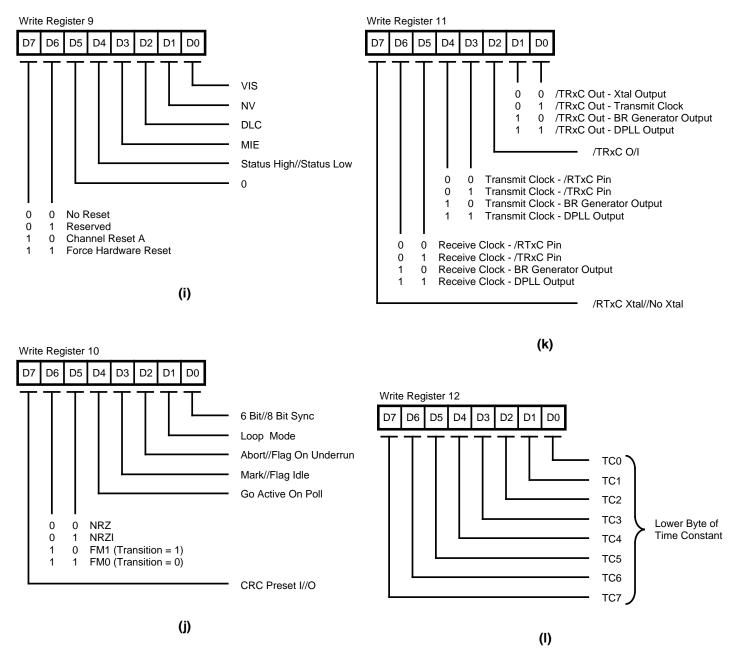

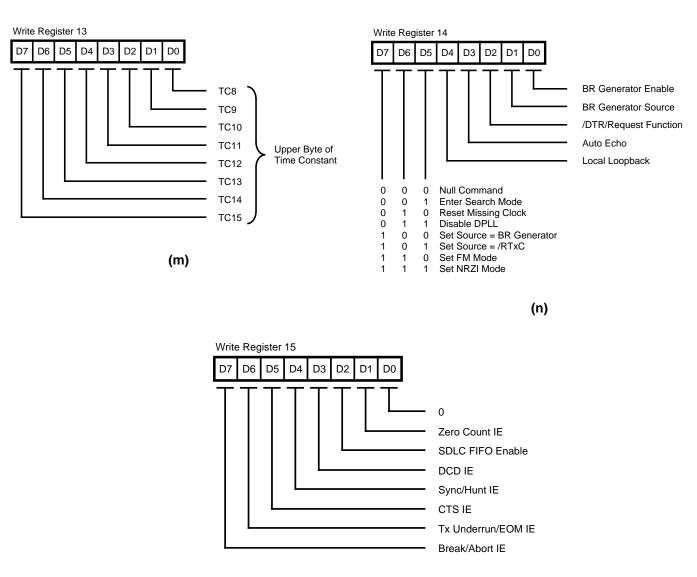

#### Write Registers

The SCC contains fifteen write registers that are programmed to configure the operating modes of the channel. With the exception of WR0, programming the write registers is a two step operation. The first operation is a pointer written to WR0 that points to the selected register. The second operation is the actual control word that is written into the register to configure the SCC channel (Figure 50).

#### Table 3. SCC Write Registers

| Bit | Description                               | Bit  | Description                                     |

|-----|-------------------------------------------|------|-------------------------------------------------|

| WR0 | Register Pointers, various initialization | WR8  | Transmit buffer                                 |

|     | commands                                  | WR9  | Master Interrupt control and reset commands     |

| WR1 | Transmit and Receive interrupt enables,   | WR10 | Miscellaneous transmit and receive control bits |

|     | WAIT/DMA commands                         | WR11 | Clock mode controls for receive and transmit    |

| WR2 | Interrupt Vector                          | WR12 | Lower byte of baud rate generator               |

| WR3 | Receive parameters and control modes      | WR13 | , ,                                             |

| WR4 | Transmit and Receive modes and parameters | WR14 | Miscellaneous control bits                      |

| WR5 | Transmit parameters and control modes     | WR15 | External status interrupt enable control        |

| WR6 | Sync Character or SDLC address            |      | •                                               |

| WR7 | Sync Character or SDLC flag               |      |                                                 |

Figure 50. Write Register Bit Functions

# SCC REGISTERS (Continued)

Figure 50. Write Register Bit Functions (Continued)

Zilog

(g)

(h)

Figure 50. Write Register Bit Functions (Continued)

# SCC REGISTERS (Continued)

Figure 50. Write Register Bit Functions (Continued)

**(**0**)**

Figure 50. Write Register Bit Functions (Continued)

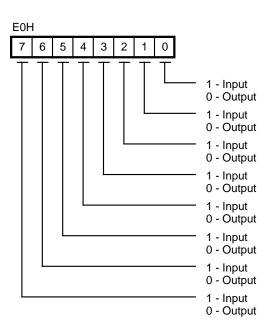

# **PIA Control Registers**

PIA1 Data Direction Register (P1DDR, I/O Address E0h), PIA1 Data Port (P1DP, I/O address E1h), PIA2 Data Direction Register (P2DDR, I/O Address E2h) and PIA2 Data Register (P2DP, I/O Address E3h). These four registers are

Figure 51. PIA 1 Data Direction Register

The Data Port is the register to/from the 8-bit parallel port. At power on Reset, they are initialized to 1.

The Data Direction Register has eight control bits. Individual bits specify each bit's direction. When the bit is set to shown in Figures 51-54. Note that if the CTC/PIA bit in the System Configuration Register is set to one, the CTC I/O functions override the PIA1 function, and programming of P1DDR is ignored.

Figure 53. PIA 2 Data Direction Register

Figure 54. PIA 2 Data Register

a "1", the bit becomes an input, otherwise it is an output. On reset, these registers are initialized to 1, resulting in all lines being inputs.

# **REGISTERS FOR SYSTEM CONFIGURATION**

There are four registers to determine system configuration with the Z181. These registers are: RAM upper boundary address register (RAMUBR, I/O address EAh), RAM lower boundary address register (RAMLBR, I/O address EBh), ROM address boundary register (ROMBR, I/O address ECh) and System Configuration Register (SCR, I/O address EDh).

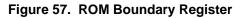

# ROM Address Boundary Register (ROMBR, I/O Address ECh)

This register specifies the address range for the /ROMCS signal. When accessed memory addresses are less than or equal to the value programmed in this register, the /ROMCS signal is asserted (Figure 55).

The A18 signal from the CPU is obtained before it is multiplexed with "TOUT". This signal can be forced to "1" (inactive state) by setting Bit D5 of the System Configuration Register, to allow the user to overlay the RAM area over the ROM area. At power-up reset, this register contains all 1's so that /ROMCS is asserted for all addresses.

#### RAM Lower Boundary Address Register (RAMLBR, I/O Address EBh) and RAM Upper Boundary Address Register (RAMUBR, I/O Address EAh)

These two registers specify the address range for the /RAMCS signal. When accessed memory addresses are less than or equal to the value programmed in the RAMUBR and greater than or equal to the value programmed in the

Chip Select signals are going active for the address range:

/ROMCS: (ROMBR)  $\geq$  A19-A12  $\geq$  0 /RAMCS: (RAMUBR)  $\geq$  A19-A12 > (RAMLBR)

These registers are set to "FFh" at power-on Reset, and the boundary addresses of ROM and RAM are the following:

ROM lower boundary address (fixed) = 00000h

ROM upper boundary address (ROMBR register) = 0FFFFh

RAM lower boundary address (RAMLBR register) = 0FFFFFh

RAM upper boundary address (RAMUBR register) = 0FFFFFh

Since /ROMCS takes priority over /RAMCS, the latter will never be asserted until the value in the ROMBR and RAMLBR registers are re-initialized to lower values.

Figure 55. RAM Upper Boundary Register

Figure 56. RAM Lower Boundary Register

### **REGISTERS FOR SYSTEM CONFIGURATION** (Continued)

Figure 58. System Configuration Register

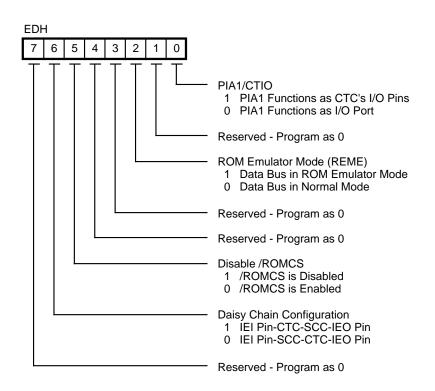

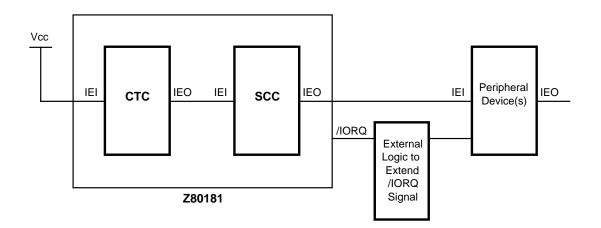

**System Configuration Register (I/O address EDh)** This register is to determine the functionality of PIA1 and the Interrupt Daisy-Chain Configuration (Figure 13). This register has the following control bits:

Bit D7. Reserved and should be programmed as "0".

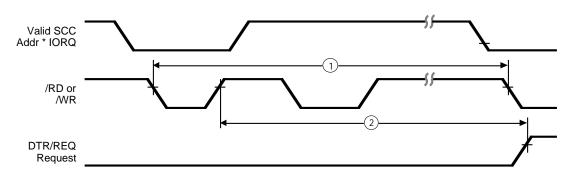

**Bit D6.** *Daisy-Chain Configuration.* Determines the arrangement of the interrupt priority daisy chain.

When this bit is set to "1", priority is as follows:

IEI pin - CTC - SCC - IEO pin

When this bit is "0", priority is as follows:

IEI pin - SCC - CTC - IEO pin

This bit's default (after Reset) is 0.

**Bit D5.** *Disable /ROMCS.* When this bit is set to "1". /ROMCS is forced to a "1" regardless of the status of the address decode logic. This bit's default (after Reset) is 0 and /ROMCS function is enabled.

Bit D4-D3. Reserved and should be programmed as "00".

**Bit D2.** *ROM Emulator Mode Enable.* When this bit is set to a 1, the Z181 is in "ROM emulator mode". In this mode, bus direction for certain transaction periods are set to the opposite direction to export internal bus transactions outside the Z80181. This allows the use of ROM emulators/ logic analyzers for applications development. This bit's default (after Reset) is 0.

Bit D1. Reserved and shall be programmed as "0".

**Bit D0.** *CTC/PIA1.* When this bit is set to "1", PIA1 functions as the CTC's I/O pins. This bit's default (after Reset) is 0.

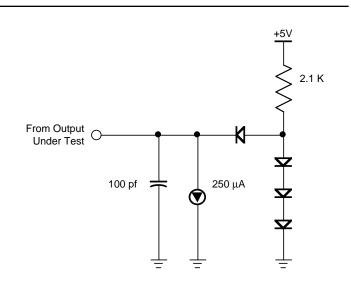

### **Data Bus Direction**

Table 4 shows the state of the SAC's data bus when in SAC bus master condition.

#### Table 4. Data Bus Direction (Z181 Is Bus Master)

#### I/O And Memory Transactions

|                                   | I/O<br>Write To<br>On-Chip<br>Peripherals<br>(SCC/CTC/<br>PIA1/PIA2) | I/O<br>Read From<br>On-Chip<br>Peripherals<br>(SCC/CTC/<br>PIA1/PIA2) | I/O<br>Write To<br>Off-Chip<br>Peripheral | I/O<br>Read From<br>Off-Chip<br>Peripheral | Write<br>To<br>Memory | Read<br>From<br>Memory | Refresh<br>/ | Z80181<br>Idle<br>Mode |

|-----------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------|--------------------------------------------|-----------------------|------------------------|--------------|------------------------|

| Z80181 Data Bus<br>(REME Bit = 0) | Out                                                                  | Ζ                                                                     | Out                                       | In                                         | Out                   | In                     | Z            | Z                      |

| Z80181 Data Bus<br>(REME Bit = 1) | Out                                                                  | Out                                                                   | Out                                       | In                                         | Out                   | In                     | Z            | Z                      |

#### Interrupt Acknowledge Transaction

|                                   | Intack For<br>On-Chip<br>Peripheral<br>(SCC/CTC) | Intack For<br>Off-Chip<br>Peripheral |

|-----------------------------------|--------------------------------------------------|--------------------------------------|

| Z80181 Data Bus<br>(REME Bit = 0) | Z                                                | In                                   |

| Z80181 Data Bus<br>(REME Bit = 1) | Out                                              | In                                   |

Table 5 shows the state of the SAC's data bus when the Z80181 is NOT in bus master condition.

#### Table 5. Data Bus Direction for External Bus Master (Z80181 Is Not Bus Master)

#### I/O And Memory Transactions

|                                   | I/O<br>Write To<br>On-Chip<br>Peripherals<br>(SCC/CTC/<br>PIA1/PIA2) | I/O<br>Read From<br>On-Chip<br>Peripherals<br>(SCC/CTC/<br>PIA1/PIA2) | I/O<br>Write To<br>Off-Chip<br>Peripheral | I/O<br>Read From<br>Off-Chip<br>Peripheral | Write<br>To<br>Memory | Read<br>From<br>Memory | Refresh<br>y | Z80181<br>Idle<br>Mode |