## **High-Performance 8-Bit Microcontrollers**

## Z8 Encore! XP® F3224 Series

**Product Specification**

PS038107-0521

PRELIMINARY

**/**

Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2021 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. Zilog, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. Zilog ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, and ZMOTION are registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

A **Littelfuse** Company

## **Revision History**

Each instance in the following revision history table reflects a change to this document from its previous version. For more details, refer to the corresponding pages or appropriate links provided in the table.

| Date        | Revision<br>Level | Description                                                                                                        | Page No.                          |

|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| May<br>2021 | 07                | Added MCT availability for 32-pin package.                                                                         | <u>1</u> , <u>423</u> -<br>426    |

|             |                   | Removed 20-pin package pending manufacturing support.                                                              | 2, 10, 46,<br>48, 400,<br>422-426 |

|             |                   | Added recommendation to alter the CONTCONV and SCAN bits only while the ADC is idle.                               | 312                               |

|             |                   | Clarified ADC offset compensation and updated ADC gain compensation formula.                                       | <u>315</u>                        |

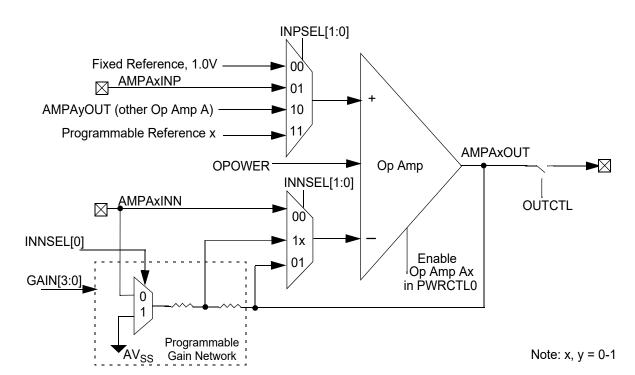

|             |                   | Clarified programmable gain connections in OpAmpA block diagram.                                                   | <u>331</u>                        |

|             |                   | Updated absolute maximum ratings for injection current and pin voltage.                                            | 400                               |

|             |                   | Updated typical current consumption specifications.                                                                | 402                               |

|             |                   | Updated bandgap voltage.                                                                                           | 407                               |

|             |                   | Updated comparator input offset specification.                                                                     | 411                               |

|             |                   | Fixed typos.                                                                                                       | Various                           |

| Oct<br>2020 | 06                | Corrected minor typos.  Removed direct DCO control using the DCOCTLL/DCOCTLH registers and                         | Various <u>78, 79,</u>            |

| 2020        |                   | the SEEDSEL control bit.                                                                                           | 86, 87                            |

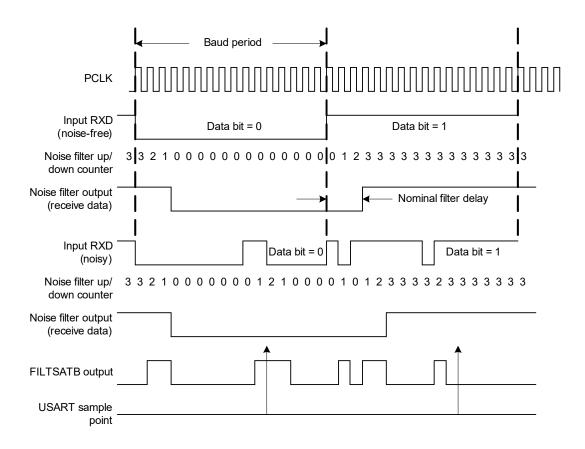

|             |                   | Enhanced UART noise filter description. Corrected Noise Filter Operation figure.                                   | <u>205</u>                        |

|             |                   | Removed ADC ANA12/ANA13 differential pair.                                                                         | <u>308, 320</u>                   |

|             |                   | Clarified ADC wake-up control.                                                                                     | 312                               |

|             |                   | Updated Flash Byte Programming Time.                                                                               | 406                               |

|             |                   | Updated DCO step size and deleted DCOCTLCH/L step size.                                                            | <u>416</u>                        |

|             |                   | Updated 20-SSOP package information.                                                                               | <u>422</u>                        |

|             |                   | Added to Ordering Information Z8F32240100ZCOG and ZMOTIONL400ZCOG.                                                 | <u>423, 425</u>                   |

| Apr         | 05                | Clarified that PortD0/RESET is not a Stop Mode Recovery source.                                                    | <u>48, 64</u>                     |

| 2020        |                   | Added setting SCKFEN=1 to the System Clock Failure description.                                                    | <u>76</u>                         |

|             |                   | Updated FBP register name to FPROT.                                                                                | <u>357</u>                        |

|             |                   | Updated electrical characteristics for: Flash Byte Program Time, $\rm I_{VBIAS},$ and                              |                                   |

|             |                   | I <sub>PROG</sub> . Merged I <sub>DD</sub> FLL into I <sub>DD</sub> DCO. Dropped DCO tempco and voltco parameters. | <u>416</u>                        |

|             |                   | Fixed typos and formatting in Chapters 18, 19, 27, and 29. Updated SSOP                                            | <u>304, 319,</u>                  |

|             |                   | 20-pin Environmental Flow.                                                                                         | <u>400, 423</u>                   |

İ۷

| Sep  | 04 | Updated AV <sub>DD</sub> , AV <sub>SS</sub> pin descriptions.                               | <u>16</u>             |

|------|----|---------------------------------------------------------------------------------------------|-----------------------|

| 2019 |    | Updated Table 7 (Flash Information Area Map).                                               | <u>20</u>             |

|      |    | Removed System Clock failure souce limitation.                                              | <u>76, 83</u>         |

|      |    | Updated CLKCTL3 Register reset value.                                                       | <u>84</u>             |

|      |    | Updated UART DMX Mode interrupt description.                                                | Various               |

|      |    | Updated ADC starting and stopping conversions.                                              | <u>325</u>            |

|      |    | Updated ADC window detection regarding data formatting.                                     | Various               |

|      |    | Added Comparator hysteresis definition.                                                     | 411                   |

|      |    | Update DCO current consumption.                                                             | 416                   |

|      |    | Corrected minor typos.                                                                      | Various               |

| Aug  | 03 | Removed 44-pin LQFP packaging option.                                                       | Various               |

| 2017 |    | Added QFN EP pin.                                                                           | CH <u>2</u>           |

|      |    | Updated System Clock Failure description of clock source detection.                         | <u>76</u>             |

|      |    | Clarified that the WTO is not affected by SCKDIV.                                           | <u>76, 83</u>         |

|      |    | Updated FLLNDIVH reset value.                                                               | 80                    |

|      |    | Changed ADC REFSEL=10 selection to be reserved.                                             | CH <u>19</u> ,        |

|      |    |                                                                                             | <u>409</u>            |

|      |    | Updated ADC fixed reference sampling time (T <sub>S_VDD/2</sub> ), wake-up time, and        | <u>409</u>            |

|      |    | ADC input resistance (R <sub>IN</sub> ). Added VBG ADC sampling time (T <sub>S_VBG</sub> ). | 405                   |

|      |    | Updated symbols in Tables 233 and 234. Updated Stop-Mode Recovery                           | <u>405</u>            |

|      |    | Latency value.                                                                              |                       |

| Jun  | 02 | Corrected minor typos/inconsistencies.                                                      | Various               |

| 2017 |    | Added internal resistor to DBG pin.                                                         | <u>15, 375</u>        |

|      |    | Updated pin configurations for 20-pin SSOP, 32-pin QFN, and 44-pin QFN and LQFP packages.   | <u>11</u> , <u>12</u> |

|      |    | Updated functionality of PWRCTL1[3:2] affecting ADC and DAC VREF.                           | <u>45, 313,</u>       |

|      |    |                                                                                             | 314                   |

|      |    | Removed FLLRDY bit. Updated FLLDONE and SEEDSEL bit functionality.                          | CH <u>8</u>           |

|      |    | Removed ADC translation buffer. Removed 2-pass behavior for 14-bit                          | CH <u>19</u> ,        |

|      |    | resolution conversions in favor of user initiated averaging. Eliminated power               | CH <u>26</u>          |

|      |    | settings. Removed SST field and functionality.                                              |                       |

|      |    | Updated ADC C <sub>IN</sub> .                                                               | <u>314, 410</u>       |

|      |    | Updated comparator window mode connectivity.                                                | <u>337</u>            |

|      |    | Updated T <sub>VBO</sub> value.                                                             | <u>405</u>            |

|      |    | Removed T <sub>LVD</sub> parameter.                                                         |                       |

|      |    | Updated LFXO active current. Added feedback resistor parameter.                             | <u>415</u>            |

|      |    | Updated DCO resolution, DCO control word resolution, T <sub>FLADONE</sub> .                 | <u>416</u>            |

|      |    | Updated POR V <sub>TH.</sub> .                                                              | <u>404</u>            |

|      |    | Corrected Comparator hysteresis setting inconsistency.                                      | <u>411</u>            |

| Oct  | 01 | Original issue.                                                                             | n/a                   |

| 2016 |    |                                                                                             |                       |

|      |    |                                                                                             |                       |

### A Littelfuse Company

## **Table of Contents**

| Overview                                                    |

|-------------------------------------------------------------|

| Features                                                    |

| Part Selection Guide                                        |

| Block Diagram                                               |

| eZ8 CPU and Peripheral Overview                             |

| General-Purpose Input/Output                                |

| Flash Controller                                            |

| Clock System                                                |

| Reference System                                            |

| 12-Bit Analog-to-Digital Converter                          |

| Low-Power Operational Amplifiers                            |

| Analog Comparators                                          |

| Low-Voltage Detector                                        |

| Enhanced SPI                                                |

| UART with LIN, DALI, and DMX  Master/Slave I <sup>2</sup> C |

| Timers                                                      |

| Multi-Channel Timer                                         |

| Interrupt Controller                                        |

| Reset Controller                                            |

| On-Chip Debugger                                            |

| Event System                                                |

| Acronyms and Expansions                                     |

| Pin Description                                             |

| •                                                           |

| Available Packages                                          |

| Pin Configurations                                          |

| Pin Characteristics                                         |

| Address Space                                               |

| Register File                                               |

| Program Memory                                              |

| Data Memory                                                 |

| Flash Information Area                                      |

| Register Map                                                |

| Reset. Stop-Mode Recovery and Low-Voltage Detection         |

| Keset, Stop-Wode Recovery and Low-Voltage Detection         |

| Reset Types                                                    | 0  |

|----------------------------------------------------------------|----|

| System Reset                                                   | 0  |

| Power-On Reset                                                 | 2  |

| Voltage Brown-Out Reset                                        | 3  |

| Watchdog Timer Reset                                           | 4  |

| External Reset Input                                           | 4  |

| External Reset Indicator                                       |    |

| On-Chip Debugger Initiated Reset                               | 5  |

| Stop-Mode Recovery                                             | 5  |

| Stop-Mode Recovery Using Watchdog Timer Time-Out               | 7  |

| Stop-Mode Recovery Using Timer, Comparator, or LVD Interrupt 3 |    |

| Stop-Mode Recovery Using GPIO Port Pin Transition              |    |

| Stop-Mode Recovery Using External RESET Pin                    |    |

| Low-Voltage Detection                                          | 8  |

| Reset Register Definitions                                     | 9  |

| Low-Power Modes                                                | 1  |

| Stop Mode                                                      | 1  |

| Halt Mode                                                      | 2  |

| Peripheral-Level Power Control                                 | 2  |

| Power Control Register Definitions                             | .3 |

| Power Control Register 0                                       |    |

| Power Control Register 1                                       | .5 |

| General-Purpose Input/Output                                   | 6  |

| GPIO Port Availability by Device                               |    |

| Architecture                                                   |    |

| GPIO Alternate Functions                                       |    |

| Shared Reset Pin                                               |    |

| Low Frequency Crystal Oscillator (LFXO) Override               |    |

| External Clock Setup                                           |    |

| Port Alternate Function Mapping                                |    |

| GPIO Control Register Definitions                              |    |

| Port A–E Address Registers                                     |    |

| Port A–E Control Registers                                     |    |

| Port A–E Data Direction Subregisters 6                         |    |

| Port A–E Alternate Function Subregisters 6                     |    |

| Port A–E Output Control Subregisters 6                         |    |

| Port A–E High Drive Enable Subregisters 6                      |    |

| Port A–E Stop-Mode Recovery Source Enable Subregisters 6       |    |

| Port A-E Pull-up Enable Subregisters            |      |

|-------------------------------------------------|------|

| Port A–E Alternate Function Set 1 Subregisters  |      |

| Port C Alternate Function Set 2 Subregister     |      |

| Port A–E Input Data Registers                   |      |

| Port A–E Output Data Register                   | . 69 |

| Clock System                                    | . 70 |

| Architecture                                    | . 71 |

| Clock Selection                                 | . 72 |

| System Clock Selection                          | . 72 |

| Peripheral Clock (Pclk) Selection               | . 73 |

| Clock System Control Register Unlocking/Locking | . 75 |

| Clock Failure Detection and Recovery            | . 76 |

| System Clock Failure                            | . 76 |

| Low Frequency Crystal Oscillator (LFXO)         | . 76 |

| LFXO Operation                                  | . 76 |

| Internal Precision Oscillator (IPO)             | . 77 |

| Operation                                       |      |

| Watchdog Timer Oscillator (WTO)                 | . 78 |

| Digitally Controlled Oscillator (DCO)           |      |

| Operating Modes                                 |      |

| DCO Operation                                   |      |

| Frequency Locked Loop (FLL)                     | . 79 |

| Operating Modes                                 |      |

| FLL Operation                                   | . 79 |

| Clock System Register Definitions               | . 81 |

| Clock Control 0 Register                        | . 81 |

| Clock Control 1 Register                        | . 83 |

| Clock Control 2 Register                        | . 84 |

| Clock Control 3 Register                        | . 84 |

| Clock Control 4 Register                        | . 85 |

| Clock Control 5 Register                        | . 86 |

| Clock Control 6 Register                        | . 87 |

| Clock Control 7 Register                        | . 87 |

| Clock Control 8 Register                        |      |

| Clock Control 9 Register                        | . 88 |

| Interrupt Controller                            | . 89 |

| Interrupt Vector Listing                        | . 89 |

| Architecture                                    | . 92 |

y vii

| Operation           |                                | 92  |

|---------------------|--------------------------------|-----|

| •                   | pt Enable                      |     |

| Interrupt Vector    | ors and Priority               | 93  |

| Interrupt Asser     | rtion                          | 93  |

| Software Inter      | rupt Assertion                 | 94  |

| Interrupt Control F | Register Definitions           | 94  |

| _                   | uest 0 Register                |     |

| Interrupt Requ      | lest 1 Register                | 96  |

| Interrupt Requ      | lest 2 Register                | 97  |

| Interrupt Requ      | nest 3 Register                | 98  |

| IRQ0 Enable I       | High and Low Bit Registers     | 98  |

| IRQ1 Enable I       | High and Low Bit Registers     | 101 |

| •                   | High and Low Bit Registers     |     |

| •                   | High and Low Bit Registers     |     |

| 1 0                 | Select Register                |     |

|                     | pt Select Register 0           |     |

| Interrupt Contr     | rol Register                   | 108 |

| Timers              |                                | 109 |

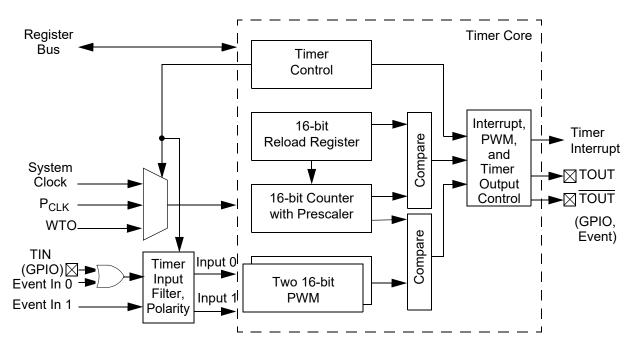

| Timer Architecture  | e                              | 110 |

| Timer Operation .   |                                | 110 |

| 1                   | Source                         |     |

|                     | lodes                          |     |

|                     | ng Modes                       |     |

| Reading the Ti      | imer Count Values              | 131 |

| Timer Interrup      | ots                            | 131 |

| Timer Output        | Signal Operation               | 131 |

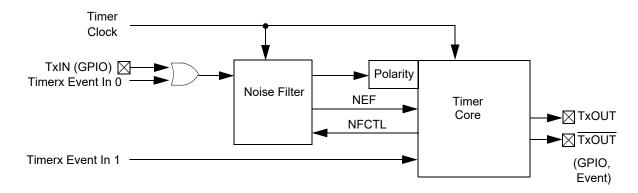

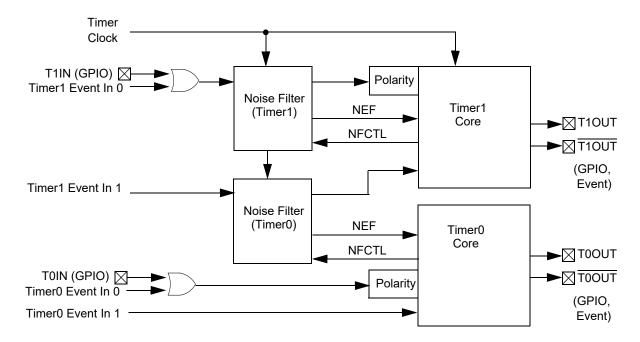

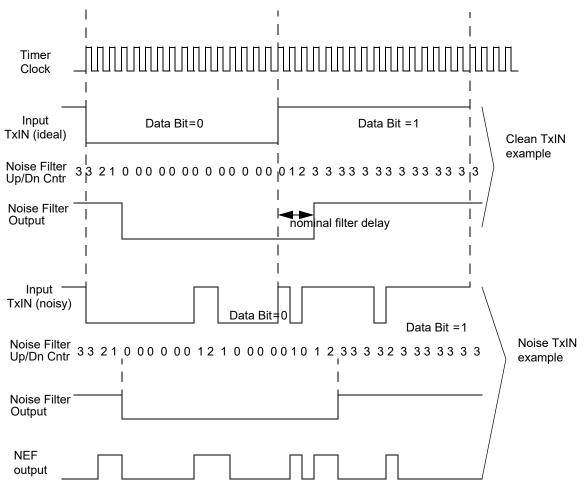

| Timer Input Pa      | ath and Noise Filter           | 131 |

| Timer Register De   | efinitions                     | 134 |

| Timer 0–2 Hig       | gh and Low Byte Registers      | 135 |

| Timer Reload        | High and Low Byte Registers    | 136 |

| Timer 0–2 PW        | M0 High and Low Byte Registers | 137 |

| Timer 0–2 PW        | M1 High and Low Byte Registers | 138 |

| Timer 0–2 Cor       | ntrol Registers                | 139 |

| Timer 0–2 Star      | tus Registers                  | 145 |

| Timer 0–2 No        | ise Filter Control Registers   | 146 |

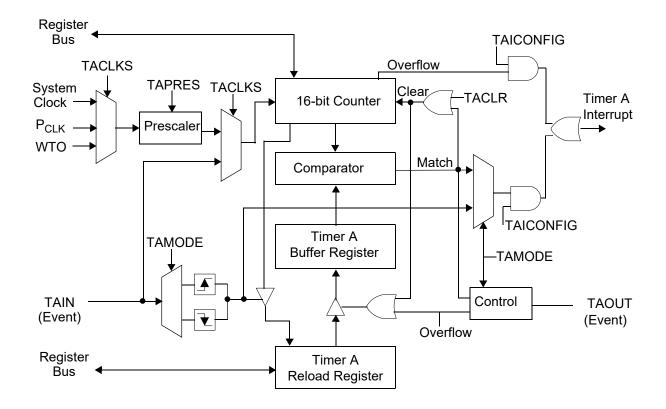

| Timer A             |                                | 148 |

|                     | ture                           |     |

|                     | n                              |     |

|                     | Source and Prescaler           |     |

|                     |                                |     |

## Z8 Encore! XP® F3224 Series Product Specification

viii

| Clearing and Enabling Timer A                    | 150 |

|--------------------------------------------------|-----|

| Low-Power Modes                                  | 150 |

| Timer A Operating Modes                          | 151 |

| Timer A Register Definitions                     | 152 |

| Timer A High and Low Byte Registers              | 152 |

| Timer A Reload High and Low Byte Registers       | 153 |

| Timer A Control Register                         | 154 |

| Timer A Prescale Register                        | 155 |

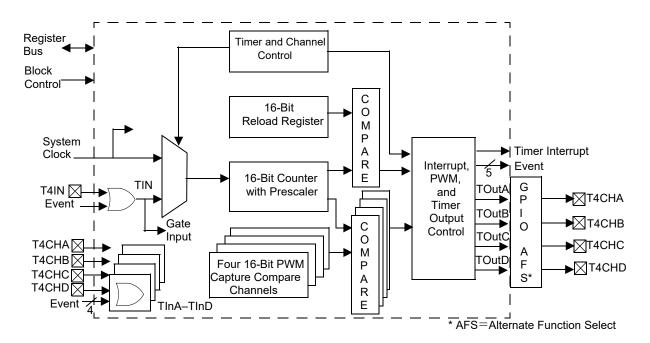

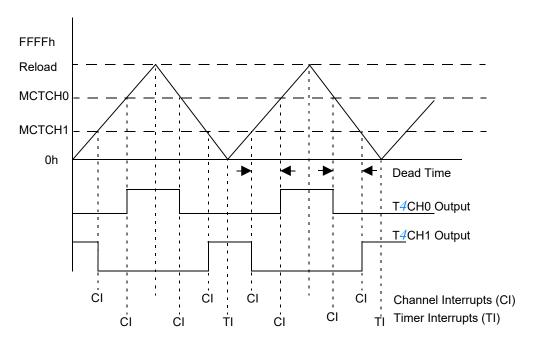

| Multi-Channel Timer                              | 157 |

| Architecture                                     | 157 |

| Timer Operation                                  | 158 |

| Multi-Channel Timer Counter                      | 158 |

| Inputs and Outputs                               | 158 |

| Clock Source                                     | 159 |

| Multi-Channel Timer Clock Prescaler              |     |

| Multi-Channel Timer Start                        |     |

| Multi-Channel Timer Mode Control                 |     |

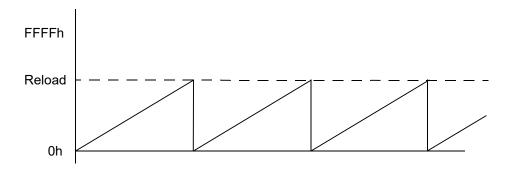

| Count Modulo Mode                                |     |

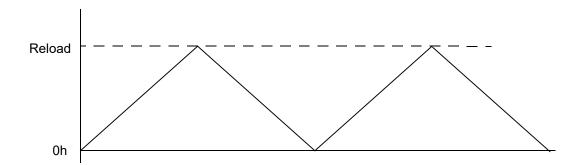

| Count Up/Down Mode                               | 160 |

| Capture/Compare Channel Operation                |     |

| One-Shot Compare Operation                       |     |

| Continuous Compare Operation                     |     |

| PWM Output Operation                             |     |

| Capture Operation                                | 162 |

| Multi-Channel Timer Interrupts                   |     |

| Timer Interrupt                                  |     |

| Channel Interrupts                               |     |

| Low-Power Modes                                  |     |

| Operation in Halt Mode                           |     |

| Operation in Stop Mode                           |     |

| Power Reduction During Operation                 | 163 |

| Multi-Channel Timer Application Examples         |     |

| PWM Programmable Deadband Generation             |     |

| Multiple Timer Intervals Generation              | 164 |

| Multi-Channel Timer Control Register Definitions |     |

| Multi-Channel Timer Address Map                  |     |

| Multi-Channel Timer High and Low Byte Registers  |     |

| MCT Reload High and Low Byte Registers           |     |

| MCT Subaddress Register                          | 168 |

### Z8 Encore! XP® F3224 Series **Product Specification**

ix

| MCT Subregister x (0, 1, or 2)                              | . 169 |

|-------------------------------------------------------------|-------|

| Multi-Channel Timer Control 0 and Control 1 Registers       | . 169 |

| Multi-Channel Timer Channel Status 0 and Status 1 Registers | . 172 |

| Multi-Channel Timer Channel-y Control Registers             | . 173 |

| Multi-Channel Timer Channel-y High and Low Byte Registers   | . 175 |

| Watchdog Timer                                              | . 176 |

| Operation                                                   | . 176 |

| Watchdog Timer Retrigger                                    | . 177 |

| Watchdog Timer Time-Out Response                            | . 177 |

| Watchdog Timer Reload Unlock Sequence                       | . 178 |

| Watchdog Timer Register Definitions                         | . 178 |

| Watchdog Timer Reload High and Low Byte Registers           | . 178 |

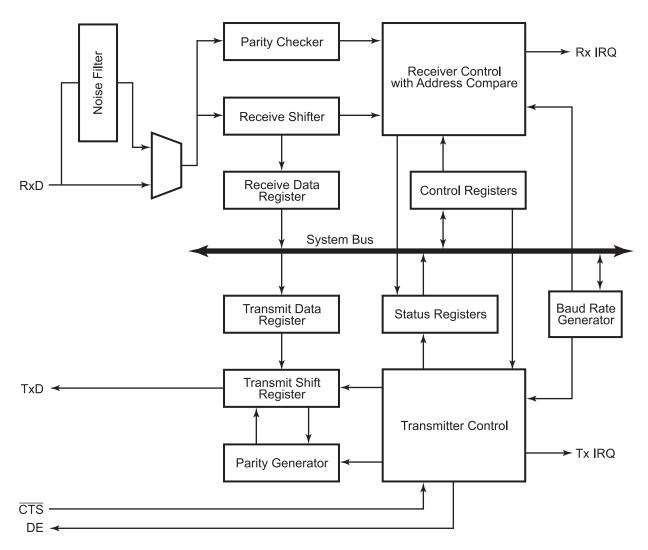

| UART-LDD                                                    | . 180 |

| UART-LDD Architecture                                       | . 181 |

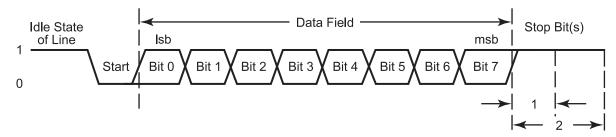

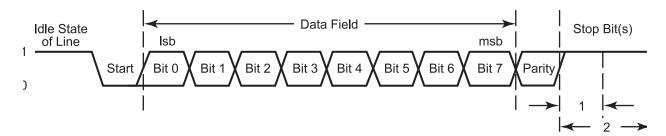

| Data Format for Standard UART Modes                         | . 182 |

| Transmitting Data using the Polled Method                   | . 182 |

| Transmitting Data Using Interrupt-Driven Method             |       |

| Receiving Data Using Polled Method                          | . 184 |

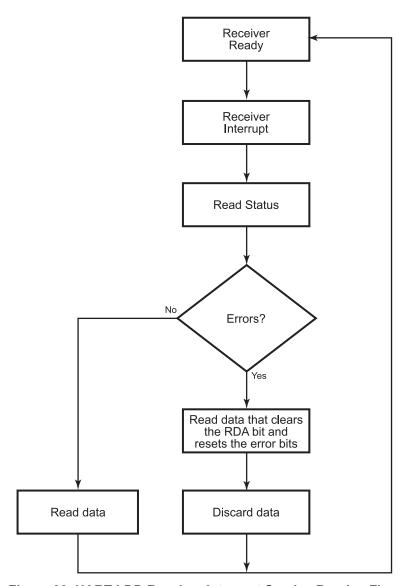

| Receiving Data Using the Interrupt-Driven Method            | . 185 |

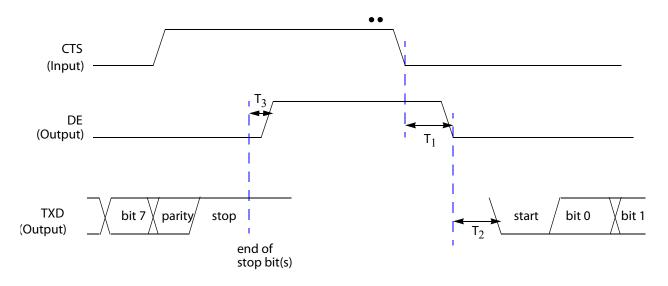

| Clear To Send Operation                                     | . 186 |

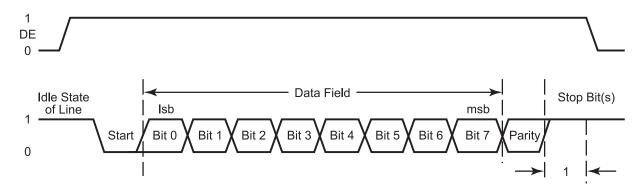

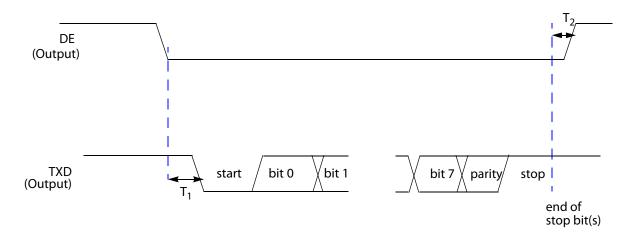

| External Driver Enable                                      | . 186 |

| UART-LDD Special Modes                                      | . 187 |

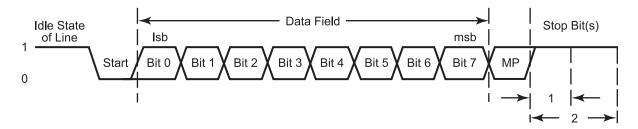

| Multiprocessor Mode                                         | . 187 |

| LIN Protocol Mode                                           | . 189 |

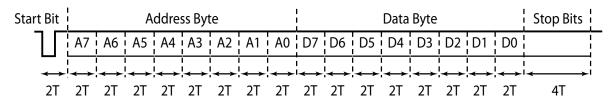

| DALI Protocol Mode                                          | . 193 |

| DMX Protocol Mode                                           | . 197 |

| UART-LDD Interrupts                                         | . 201 |

| UART-LDD Baud Rate Generator                                | . 205 |

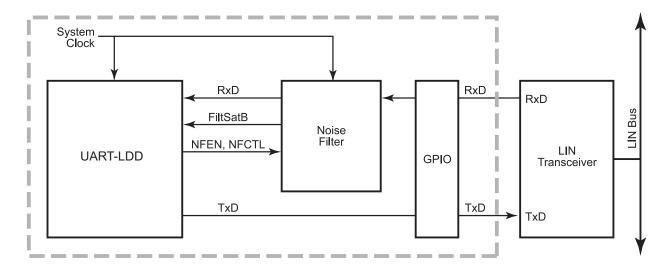

| Noise Filter                                                | . 205 |

| Architecture                                                | . 206 |

| Operation                                                   | . 206 |

| UART-LDD Control Register Definitions                       | . 208 |

| UART-LDD Transmit Data Register                             |       |

| UART-LDD Receive Data Register                              |       |

| UART-LDD Status 0 Register                                  |       |

| UART-LDD Mode Select and Status Register                    |       |

| UART-LDD Control 0 Register                                 |       |

| UART-LDD Control 1 Registers                                |       |

| Noise Filter Control Registers                              | 221   |

Z8 Encore! XP® F3224 Series

# ZILO G A Littelfuse Company

| . 222 |

|-------|

| . 223 |

| . 224 |

| . 225 |

| . 226 |

| . 231 |

| . 231 |

| . 233 |

| . 233 |

| . 233 |

| . 233 |

| . 233 |

| . 234 |

| . 234 |

| . 235 |

| . 237 |

| . 239 |

| . 242 |

| . 243 |

| . 244 |

| . 245 |

| . 245 |

| . 246 |

| . 246 |

| . 248 |

| . 251 |

| . 252 |

| . 253 |

| . 256 |

| . 256 |

| . 257 |

| . 258 |

| . 258 |

| . 259 |

| . 261 |

| . 261 |

| . 261 |

| . 269 |

| . 276 |

|       |

| I <sup>2</sup> C Data Register                         | 276 |

|--------------------------------------------------------|-----|

| I <sup>2</sup> C Interrupt Status Register             |     |

| I <sup>2</sup> C Control Register                      |     |

| I <sup>2</sup> C Baud Rate High and Low Byte Registers | 279 |

| I <sup>2</sup> C State Register                        |     |

| I <sup>2</sup> C Mode Register                         | 284 |

| I <sup>2</sup> C Slave Address Register                | 286 |

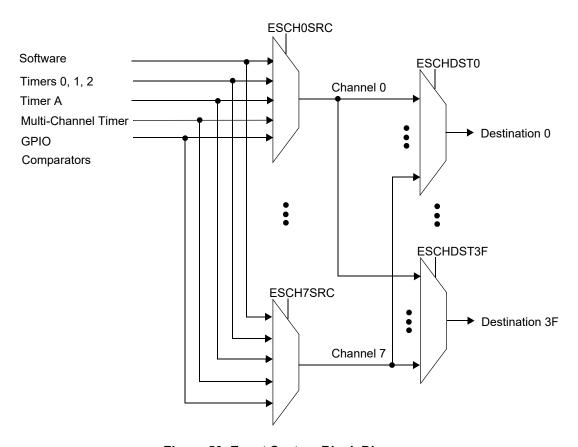

| Event System                                           | 287 |

| Architecture                                           | 287 |

| Source Selection                                       | 288 |

| Destination Selection                                  | 289 |

| Timing Considerations                                  | 291 |

| Event System Usage Examples                            | 291 |

| Event System Register Definitions                      | 292 |

| Event System Source Subaddress Register                | 294 |

| Event System Source Subdata Register                   | 295 |

| Event System Channel 0–7 Source Subregisters           | 296 |

| Event System Destination Subaddress Register           | 297 |

| Event System Destination Subdata Register              | 298 |

| Event System Destination 0–3F Channel Subregisters     | 299 |

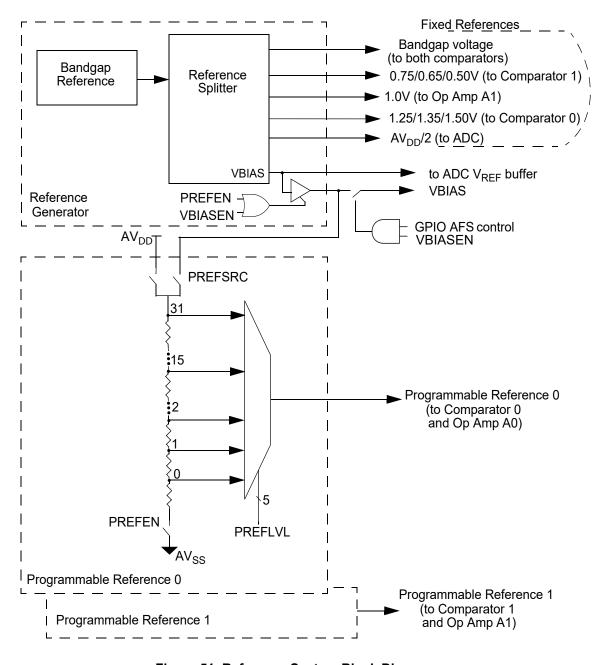

| Reference System                                       | 300 |

| Architecture                                           | 301 |

| Reference System Operation                             | 302 |

| Reference System Register Definitions                  | 303 |

| Fixed Reference Control Register                       | 304 |

| Programmable Reference 0 Control Register              | 305 |

| Programmable Reference 1 Control Register              | 305 |

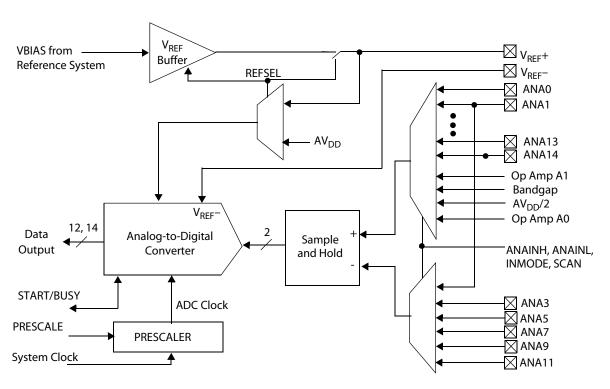

| Analog-to-Digital Converter                            | 307 |

| Architecture                                           | 307 |

| Operation                                              | 308 |

| Input Modes                                            |     |

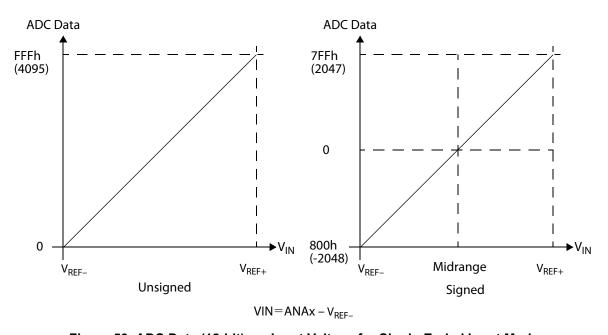

| ADC Data Format                                        | 309 |

| Conversion Options                                     | 311 |

| Starting and Stopping Conversions                      |     |

| Voltage References                                     |     |

| ADC Timing                                             |     |

| Window Detection                                       | 315 |

| ADC Interrupts                                         | 315 |

## Z8 Encore! XP® F3224 Series **Product Specification**

A **Littelfuse** Company

χij

| Calibration and Compensation                                 | . 315 |

|--------------------------------------------------------------|-------|

| ADC Control Register Definitions                             | . 316 |

| ADC Control 0 Register                                       | . 316 |

| ADC Control 1 Register                                       | . 318 |

| ADC Control 2 Register                                       | . 318 |

| ADC Input Select High Register                               |       |

| ADC Input Select Low Register                                |       |

| ADC Offset Calibration Register                              |       |

| ADC Data High Register                                       |       |

| ADC Data Low Register                                        |       |

| Sample Time Register                                         |       |

| ADC Window Upper Threshold High Register                     |       |

| ADC Window Upper Threshold Low Register                      |       |

| ADC Window Lower Threshold High Register                     |       |

| ADC Window Lower Threshold Low Register                      |       |

| Operational Amplifiers                                       |       |

| Architecture                                                 | . 330 |

| Operation                                                    | . 331 |

| Op Amp Register Definitions                                  | . 333 |

| Op Amp A0-1 Control 0 Register                               | . 333 |

| Op Amp A0-1 Control 1 Register                               | . 335 |

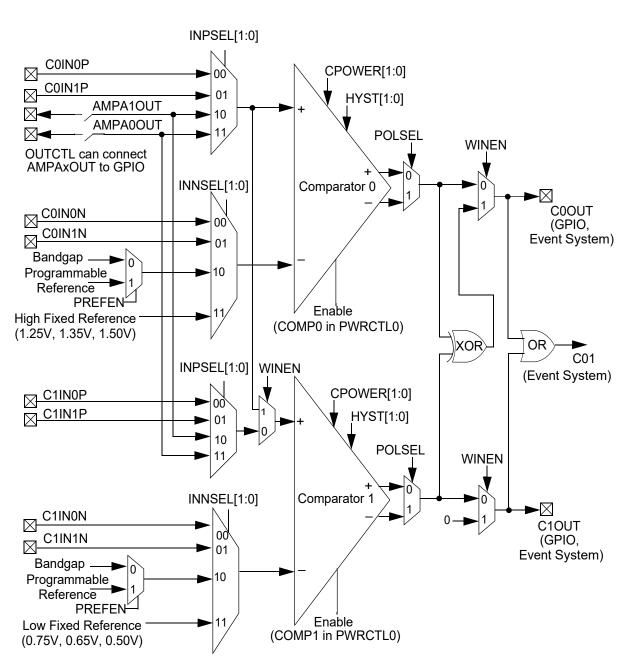

| Comparators                                                  | . 336 |

| Architecture                                                 |       |

| Comparator Operation                                         |       |

| Comparator Register Definitions                              |       |

| Comparator Control Register                                  |       |

| Comparator 0 Control 0 Register                              |       |

| Comparator 0 Control 1 Register                              |       |

| Comparator 1 Control 0 Register                              |       |

| Comparator 1 Control 1 Register                              |       |

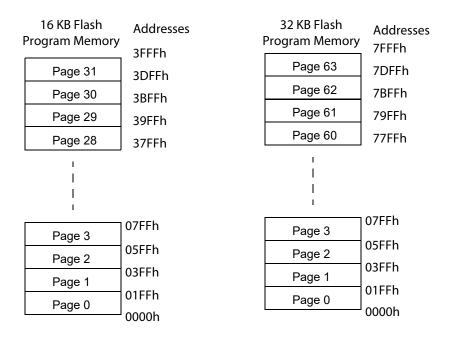

| Flash Memory                                                 | 346   |

| Flash Information Area                                       |       |

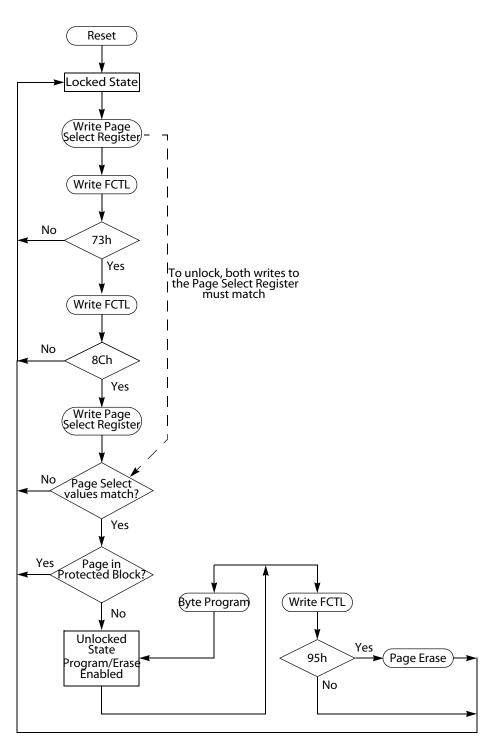

| Operation                                                    |       |

| Flash Operation Timing                                       |       |

| Flash Code Protection Against External Access                |       |

| Flash Code Protection Against Accidental Program and Erasure |       |

| Programming                                                  |       |

| Page Erase                                                   |       |

| Mass Erase                                                   |       |

xiii

| Flash Controller Behavior in Debug Mode                 | 353 |

|---------------------------------------------------------|-----|

| Flash Control Register Definitions                      | 354 |

| Flash Control Register                                  | 354 |

| Flash Status Register                                   |     |

| Flash Page Select Register                              |     |

| Flash Block Protect Register                            | 357 |

| Flash Option Bits                                       | 358 |

| Operation                                               |     |

| Option Bit Configuration by Reset                       | 358 |

| Option Bit Types                                        | 358 |

| Flash Option Bit Control Register Definitions           |     |

| Trim Bit Address Register                               |     |

| Trim Bit Data Register                                  | 362 |

| User Option Bit Address Space                           | 362 |

| Trim Bit Address Space                                  | 364 |

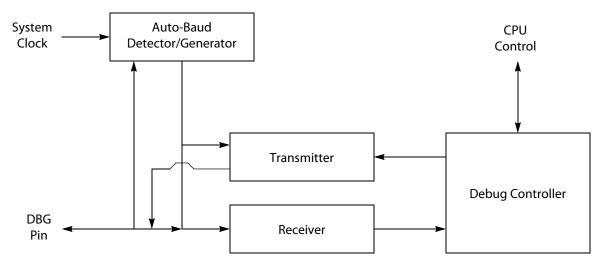

| On-Chip Debugger                                        | 372 |

| Architecture                                            | 372 |

| Operation                                               | 373 |

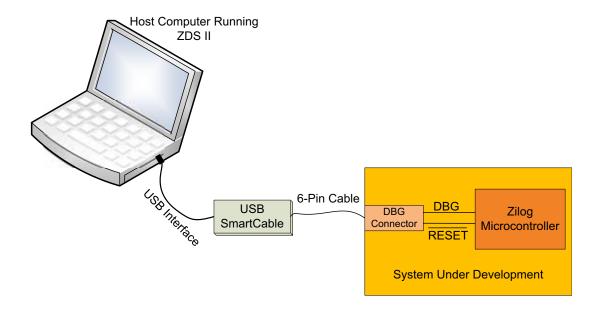

| Development System Overview                             | 373 |

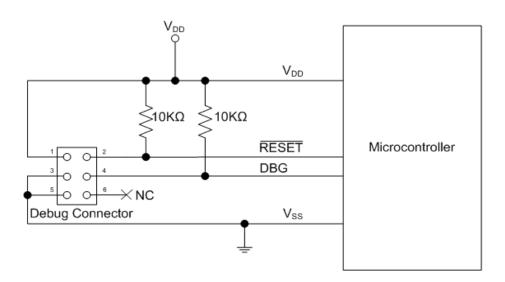

| On-Chip Debugger Interface                              | 374 |

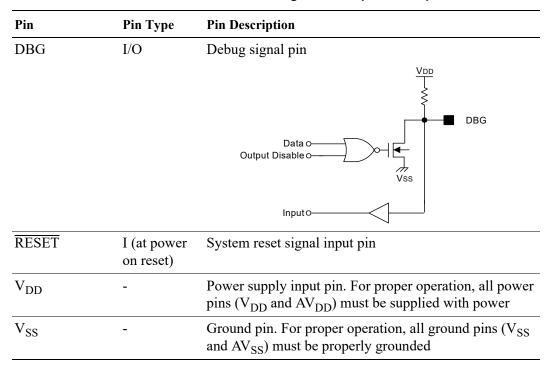

| Pin Description                                         | 375 |

| Debug Mode                                              | 375 |

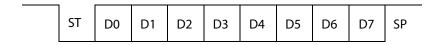

| OCD Data Format                                         |     |

| OCD Auto-Baud Detector/Generator                        |     |

| Breakpoints                                             | 378 |

| eZ8 CPU Instruction Set                                 | 379 |

| Assembly Language Programming Introduction              | 379 |

| Assembly Language Syntax                                | 380 |

| eZ8 CPU Instruction Notation                            | 381 |

| eZ8 CPU Instruction Classes                             | 382 |

| eZ8 CPU Instruction Summary                             | 387 |

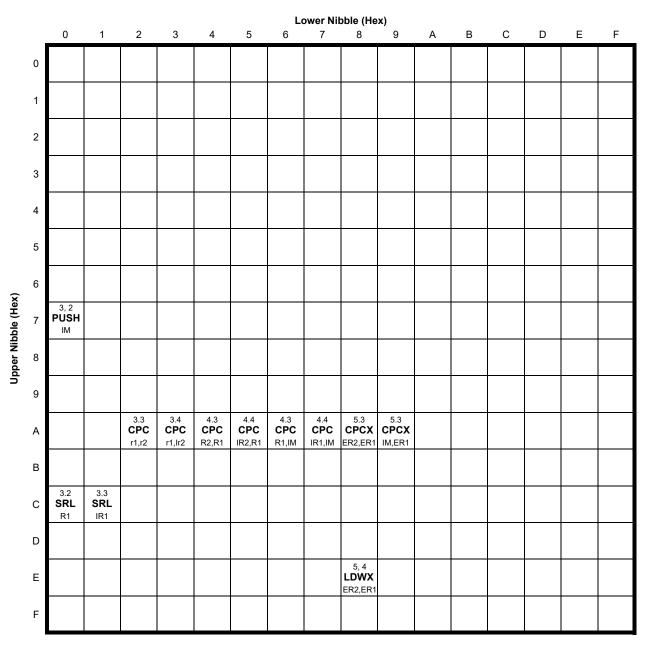

| Op Code Maps                                            | 396 |

| Electrical Characteristics                              | 400 |

| Absolute Maximum Ratings                                | 400 |

| DC Characteristics                                      |     |

| AC Characteristics                                      |     |

| On-Chip Peripheral AC and DC Electrical Characteristics |     |

|                                                         |     |

xiv

| Power-On Reset                                            |

|-----------------------------------------------------------|

| Voltage Brown-Out                                         |

| Stop-Mode Recovery                                        |

| Flash Memory                                              |

| Watchdog Timer                                            |

| Reference System                                          |

| Analog-to-Digital Converter                               |

| Comparator                                                |

| Operational Amplifier, Op Amp A                           |

| Low Voltage Detect                                        |

| Internal Precision Oscillator                             |

| Low Frequency Crystal Oscillator                          |

| Digitally Controlled Oscillator and Frequency-Locked Loop |

| General-Purpose I/O Port Input Data Sample Timing         |

| General-Purpose I/O Port Output Timing                    |

| On-Chip Debugger Timing                                   |

| UART Timing                                               |

| Packaging                                                 |

| Ordering Information                                      |

| Part Number Listing                                       |

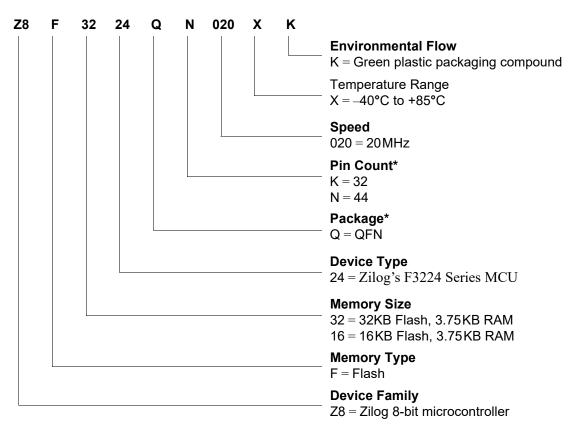

| Part Number Suffix Designations                           |

| Precharacterization Product                               |

|                                                           |

### ΧV

## **List of Figures**

| Figure 1. F3224 Series Block Diagram                                               |

|------------------------------------------------------------------------------------|

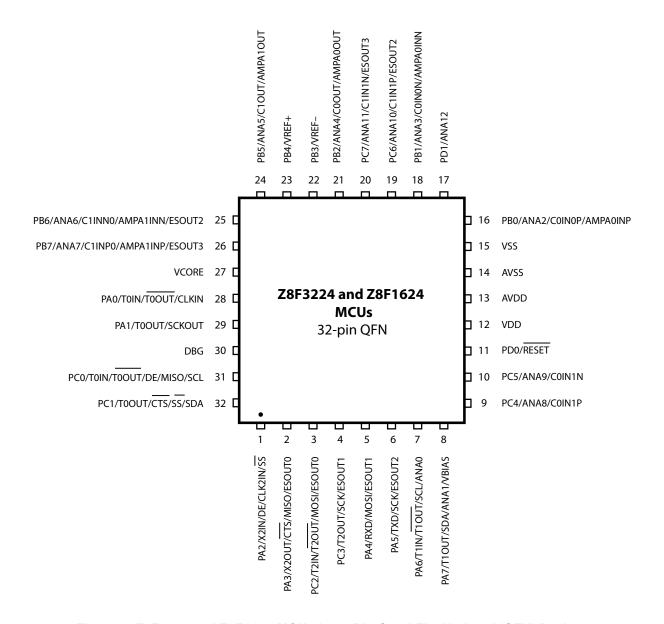

| Figure 2. Z8F3224 and Z8F1624 MCUs in 32-Pin Quad Flat No Lead (QFN) Package 11    |

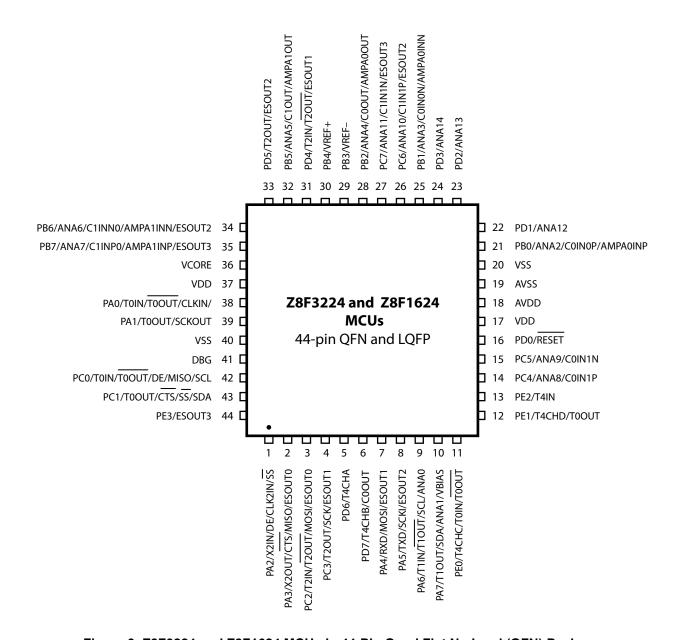

| Figure 3. Z8F3224 and Z8F1624 MCUs in 44-Pin Quad Flat No Lead (QFN) Package 12    |

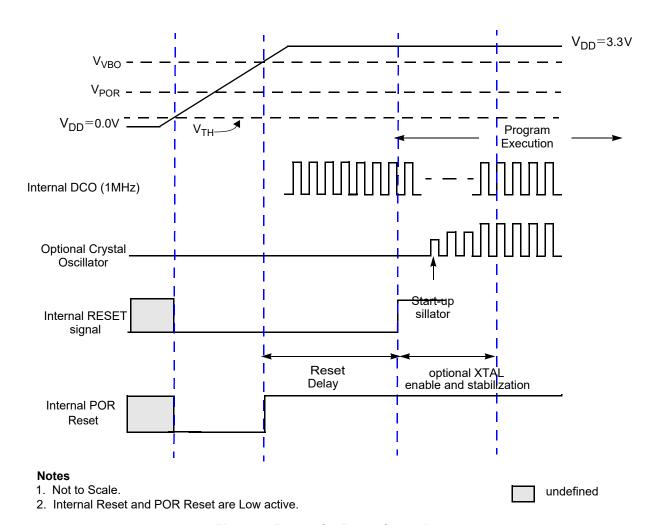

| Figure 4. Power-On Reset Operations                                                |

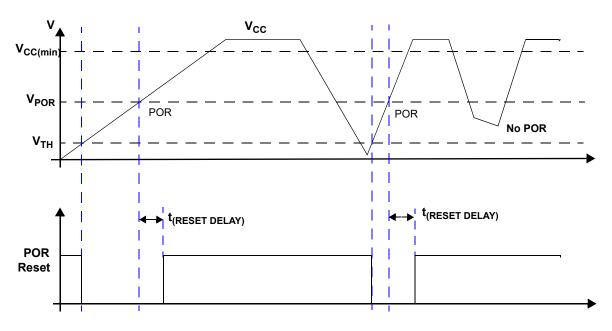

| Figure 5. Power-On Reset Behavior                                                  |

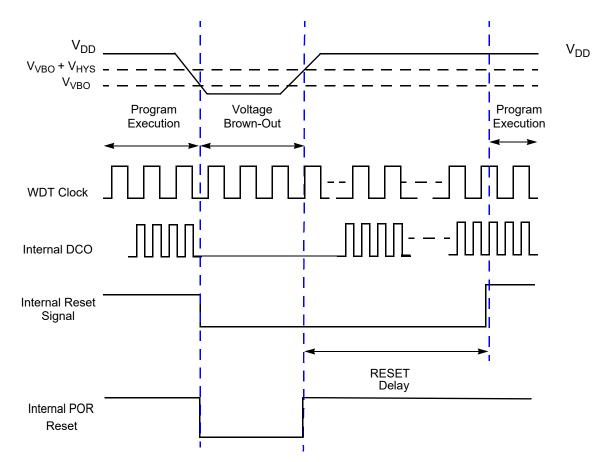

| Figure 6. Voltage Brown-Out Reset Operation                                        |

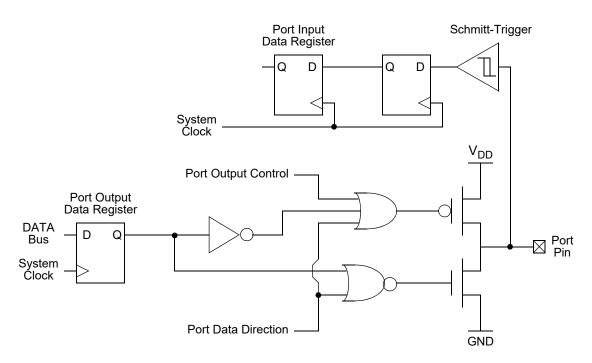

| Figure 7. GPIO Port Pin Block Diagram                                              |

| Figure 8. Clock System Block Diagram                                               |

| Figure 9. Recommended 32.768kHz Crystal Oscillator Configuration                   |

| Figure 10. FLL Block Diagram                                                       |

| Figure 11. Interrupt Controller Block Diagram                                      |

| Figure 12. Timer Block Diagram                                                     |

| Figure 13. Input Path and Noise Filter System Block Diagram                        |

| Figure 14. Example with the Timer0 Noise Filter Reassigned to Timer1               |

| Figure 15. Noise Filter Operation                                                  |

| Figure 16. Timer A Block Diagram                                                   |

| Figure 17. Multi-Channel Timer Block Diagram                                       |

| Figure 18. Count Modulo Mode                                                       |

| Figure 19. Count Up/Down Mode                                                      |

| Figure 20. Count Up/Down Mode with PWM Channel Outputs and Deadband 164            |

| Figure 21. Count Max Mode with Channel Compare                                     |

| Figure 22. UART-LDD Block Diagram                                                  |

| Figure 23. UART-LDD Asynchronous Data Format without Parity                        |

| Figure 24. UART-LDD Asynchronous Data Format with Parity                           |

| Figure 25. UART-LDD Driver Enable Signal Timing with One Stop Bit and Parity . 187 |

| Figure 26. UART-LDD Asynchronous Multiprocessor Mode Data Format 188               |

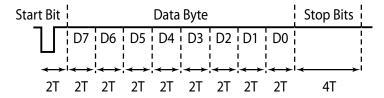

| Figure 27. UART-LDD DALI Standard Frames and Biphase Bit Encoding 194              |

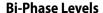

| Figure 28. UART-LDD DMX Frame and Data Slot                                        |

xvi

| Figure 29. UART-LDD Receiver Interrupt Service Routine Flow                             | 204 |

|-----------------------------------------------------------------------------------------|-----|

| Figure 30. Noise Filter System Block Diagram                                            | 206 |

| Figure 31. Noise Filter Operation                                                       | 207 |

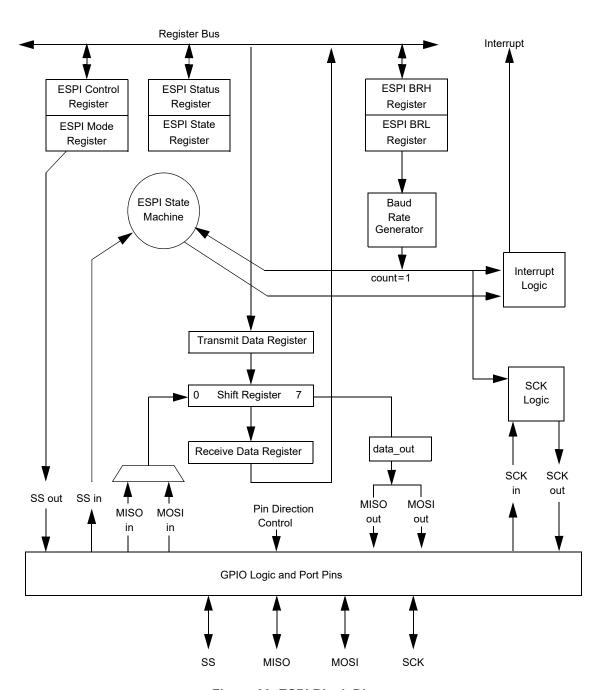

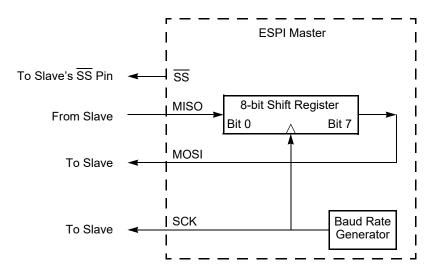

| Figure 32. ESPI Block Diagram                                                           | 232 |

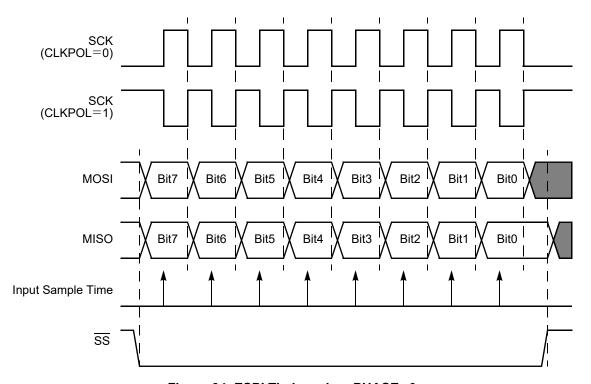

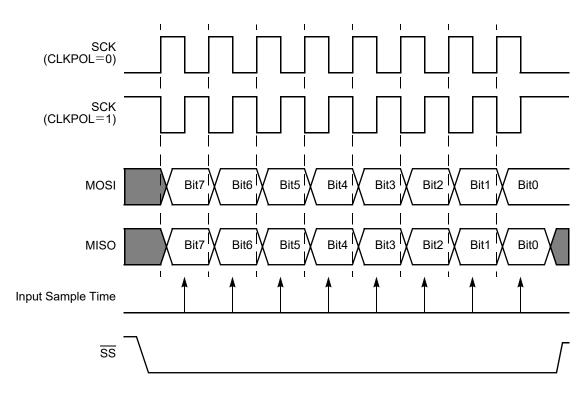

| Figure 33. ESPI Timing when PHASE=0                                                     | 236 |

| Figure 34. ESPI Timing when PHASE=1                                                     | 237 |

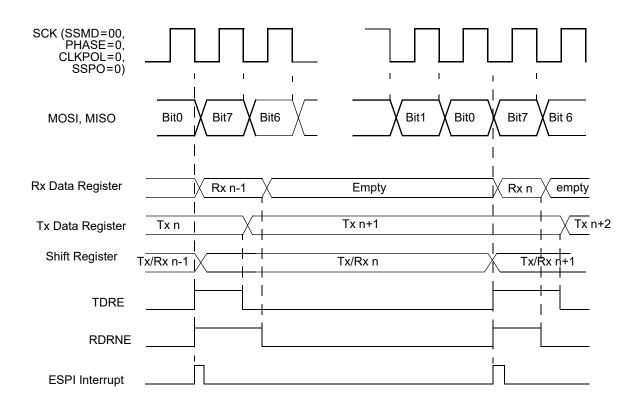

| Figure 35. SPI Mode (SSMD=000)                                                          | 238 |

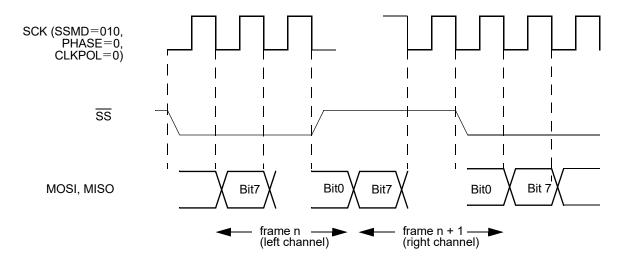

| Figure 36. I <sup>2</sup> S Mode (SSMD=010), Multiple Frames                            | 239 |

| Figure 37. ESPI Configured as an SPI Master in a Single Master, Single Slave System 240 | n   |

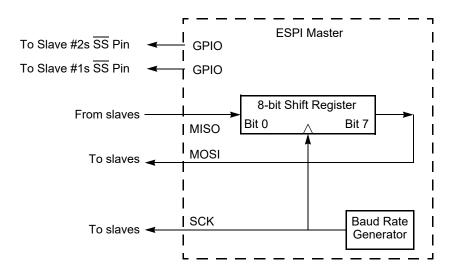

| Figure 38. ESPI Configured as an SPI Master in a Single Master, Multiple Slave Syst 241 | em  |

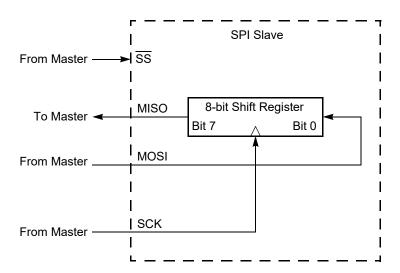

| Figure 39. ESPI Configured as an SPI Slave                                              | 242 |

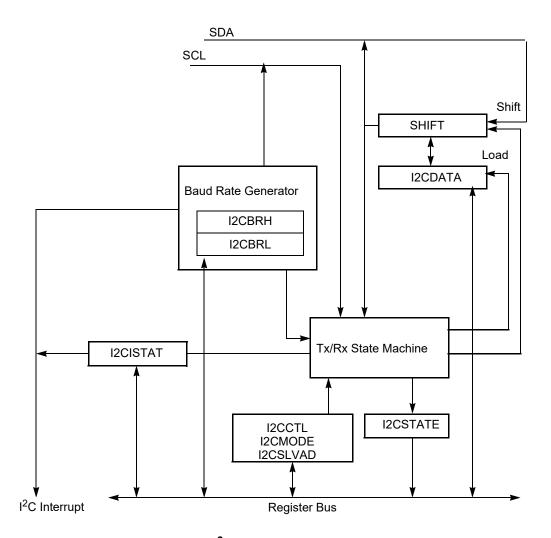

| Figure 40. I <sup>2</sup> C Controller Block Diagram                                    | 257 |

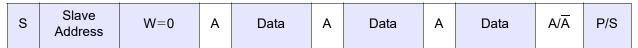

| Figure 41. Data Transfer Format, Master Write Transaction with a 7-Bit Address          | 263 |

| Figure 42. Data Transfer Format, Master Write Transaction with a 10-Bit Address         | 264 |

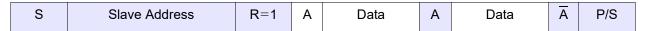

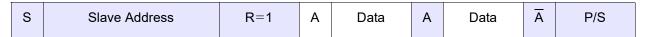

| Figure 43. Data Transfer Format, Master Read Transaction with a 7-Bit Address           | 266 |

| Figure 44. Data Transfer Format, Master Read Transaction with a 10-Bit Address          | 267 |

| Figure 45. Data Transfer Format, Slave Receive Transaction with 7-Bit Address           | 271 |

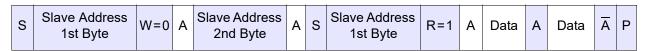

| Figure 46. Data Transfer Format, Slave Receive Transaction with 10-Bit Address          | 272 |

| Figure 47. Data Transfer Format, Slave Transmit Transaction with 7-bit Address          | 273 |

| Figure 48. Data Transfer Format, Slave Transmit Transaction with 10-Bit Address         | 274 |

| Figure 49. Event System Block Diagram                                                   | 288 |

| Figure 50. Reference System Block Diagram                                               | 301 |

| Figure 51. Analog-to-Digital Converter Block Diagram                                    | 308 |

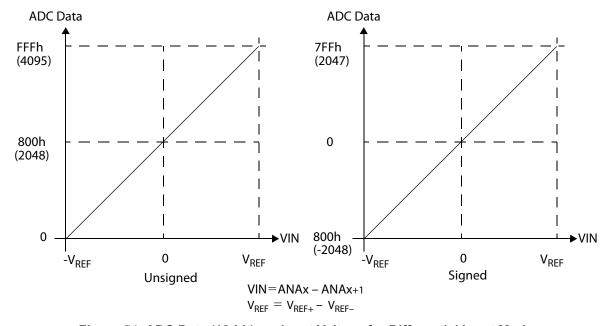

| Figure 52. ADC Data (12-bit) vs. Input Voltage for Single-Ended Input Mode              | 310 |

| Figure 53. ADC Data (12-bit) vs. Input Voltage for Differential Input Mode              | 310 |

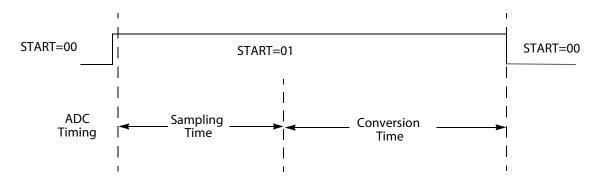

| Figure 54. ADC Conversion Timing Diagram                                                | 314 |

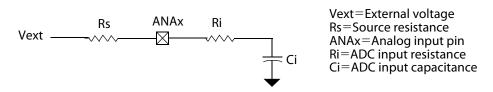

| Figure 55. ADC Input Equivalent Circuit                                                 | 315 |

| Figure 56. Op Amp A Block Diagram                                                       | 331 |

| Figure 57. Comparators Block Diagram                                                    | 337 |

## Z8 Encore! XP® F3224 Series Product Specification

xvii

| Figure 58. Flash Memory Arrangement                           |

|---------------------------------------------------------------|

| Figure 59. Flash Controller Operation Flowchart               |

| Figure 60. On-Chip Debugger Block Diagram                     |

| Figure 61. Development System                                 |

| Figure 62. Target OCD Connector Interface                     |

| Figure 63. OCD Data Format                                    |

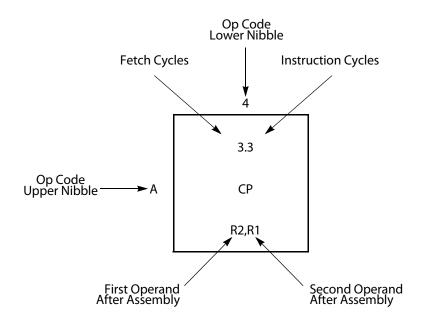

| Figure 64. Op Code Map Cell Description                       |

| Figure 65. First Op Code Map                                  |

| Figure 66. Second Op Code Map after 1Fh                       |

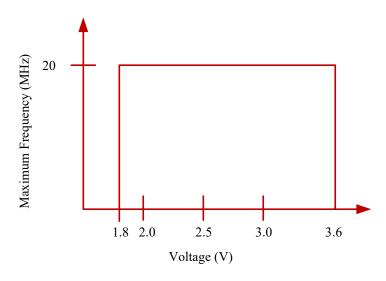

| Figure 67. Maximum System Clock Frequency vs. V <sub>DD</sub> |

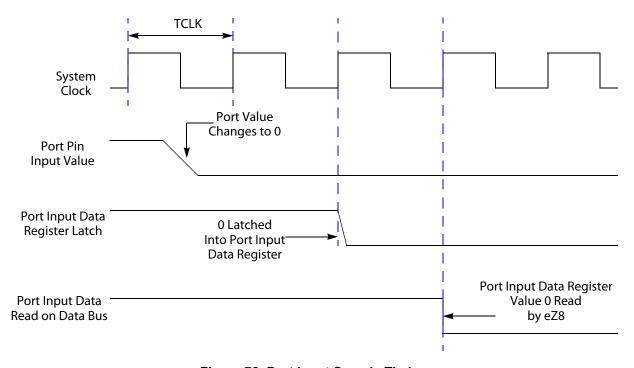

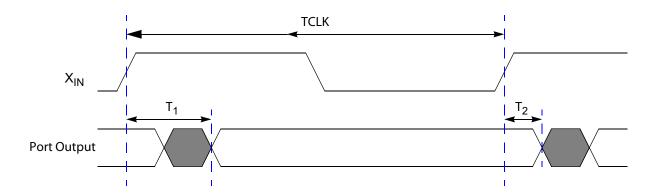

| Figure 68. Port Input Sample Timing                           |

| Figure 69. GPIO Port Output Timing                            |

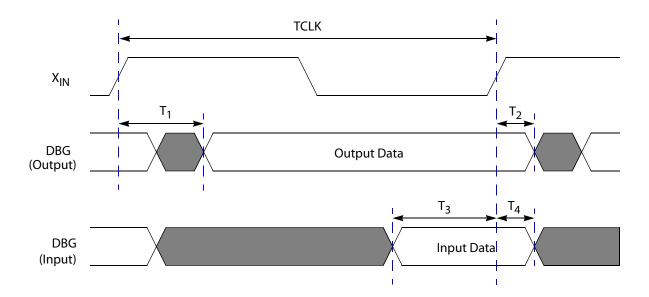

| Figure 70. On-Chip Debugger Timing                            |

| Figure 71. UART Timing With CTS                               |

| Figure 72. UART Timing Without CTS                            |

xviii

## **List of Tables**

| Table 1. F3224 Series Family Part Selection Guide.                           |

|------------------------------------------------------------------------------|

| Table 2. Acronyms and Expansions                                             |

| Table 3. F3224 Series Package Options                                        |

| Table 4. Signal Descriptions                                                 |

| Table 5. Pin Characteristics                                                 |

| Table 6. F3224 Series Program Memory Maps                                    |

| Table 7. F3224 Series Flash Memory Information Area Map                      |

| Table 8. Register File Address Map                                           |

| Table 9. Reset, Stop-Mode Recovery Characteristics and Latency               |

| Table 10. System Reset Sources and Resulting Reset Type                      |

| Table 11. Stop-Mode Recovery Sources and Resulting Action                    |

| Table 12. Reset Status Register (RSTSTAT)                                    |

| Table 13. Reset Status Per Event                                             |

| Table 14. Power Control Register 0 (PWRCTL0)                                 |

| Table 15. Power Control Register 1 (PWRCTL1)                                 |

| Table 16. Port Availability by Device and Package Type                       |

| Table 17. Port Alternate Function Mapping, 20-Pin Parts                      |

| Table 18. Port Alternate Function Mapping, 32-Pin Parts                      |

| Table 19. Port Alternate Function Mapping (44-Pin Parts)                     |

| Table 20. GPIO Port Registers and Subregisters                               |

| Table 21. Port A–E GPIO Address Registers (PxADDR)                           |

| Table 22. Port A–E Control Registers (PxCTL)                                 |

| Table 23. Port A–E Data Direction Subregisters (PxDD) 60                     |

| Table 24. Port A–E Alternate Function Subregisters (P <b>x</b> AF) 61        |

| Table 25. Port A–E Output Control Subregisters (PxOC)                        |

| Table 26. Port A–E High Drive Enable Subregisters (PxHDE)                    |

| Table 27. Port A–E Stop-Mode Recovery Source Enable Subregisters (PxSMRE) 64 |

| Table 28. Port A–E Pull-Up Enable Subregisters (PxPUE)                       |

xix

| Table 29. Port A–E Alternate Function Set 1 Subregisters (PxAFS1) 60 |

|----------------------------------------------------------------------|

| Table 30. Port C Alternate Function Set 2 Subregisters (PxAFS2) 6    |

| Table 31. Port A–E Input Data Registers (PxIN)                       |

| Table 32. Port A–E Output Data Register (PxOUT)                      |

| Table 33. System Clock Configuration and Selection                   |

| Table 34. Peripheral Clock Sources and Usage                         |

| Table 35. Clock Control 0 Register (CLKCTL0)                         |

| Table 36. Clock Control 1 Register (CLKCTL1)                         |

| Table 37. Clock Control 2 Register (CLKCTL2)                         |

| Table 38. Clock Control 3 Register (CLKCTL3)                         |

| Table 39. Clock Control 4 Register (CLKCTL4)                         |

| Table 40. Clock Control 5 Register (CLKCTL5)                         |

| Table 41. Clock Control 6 Register (CLKCTL6)                         |

| Table 42. Clock Control 7 Register (CLKCTL7)                         |

| Table 43. Clock Control 8 Register (CLKCTL8)                         |

| Table 44. Clock Control 9 Register (CLKCTL9)                         |

| Table 45. Trap and Interrupt Vectors in Order of Priority            |

| Table 46. Interrupt Request 0 Register (IRQ0)                        |

| Table 47. Interrupt Request 1 Register (IRQ1)                        |

| Table 48. Interrupt Request 2 Register (IRQ2)                        |

| Table 49. Interrupt Request 3 Register (IRQ3)                        |

| Table 50. IRQ0 Enable and Priority Encoding                          |

| Table 51. IRQ0 Enable High Bit Register (IRQ0ENH)                    |

| Table 52. IRQ0 Enable Low Bit Register (IRQ0ENL)                     |

| Table 53. IRQ1 Enable and Priority Encoding                          |

| Table 54. IRQ1 Enable High Bit Register (IRQ1ENH)                    |

| Table 55. IRQ1 Enable Low Bit Register (IRQ1ENL)                     |

| Table 56. IRQ2 Enable and Priority Encoding                          |

| Table 57. IRQ2 Enable High Bit Register (IRQ2ENH)                    |

| Table 58. IRQ2 Enable Low Bit Register (IRQ2ENL)                     |

XX

| Table 59. IRQ3 Enable and Priority Encoding                    |

|----------------------------------------------------------------|

| Table 60. IRQ3 Enable High Bit Register (IRQ3ENH)              |

| Table 61. IRQ3 Enable Low Bit Register (IRQ3ENL)               |

| Table 62. Interrupt Edge Select Register (IRQES)               |

| Table 63. Shared Interrupt Select Register 0 (IRQSS0)          |

| Table 64. Interrupt Control Register (IRQCTL)                  |

| Table 65. Timer Operating Modes                                |

| Table 66. Triggered One-Shot Mode Initialization Example       |

| Table 67. Demodulation Mode Initialization Example             |

| Table 68. Timer 0–2 High Byte Registers (T <b>x</b> H)         |

| Table 69. Timer 0–2 Low Byte Registers (T <b>x</b> L)          |

| Table 70. Timer 0–2 Reload High Byte Registers (T <b>x</b> RH) |

| Table 71. Timer 0–2 Reload Low Byte Registers (TxRL)           |

| Table 72. Timer 0–2 PWM0 High Byte Registers (TxPWM0H)         |

| Table 73. Timer 0–2 PWM0 Low Byte Registers (TxPWM0L)          |

| Table 74. Timer 0–2 PWM1 High Byte Registers (TxPWM1H)         |

| Table 75. Timer 0–2 PWM1 Low Byte Registers (TxPWM1L)          |

| Table 76. Timer 0–2 Control 0 Registers (T <b>x</b> CTL0)      |

| Table 77. Timer 0–2 Control 1 Registers (T <b>x</b> CTL1)      |

| Table 78. Timer 0–2 Control 2 Registers (TxCTL2)               |

| Table 79. Timer 0–2 Status Register (T <b>x</b> STAT)          |

| Table 80. Timer 0–2 Noise Filter Control Registers (TxNFC)     |

| Table 81. Timer A Operating Modes                              |

| Table 82. Timer A High Byte Register (TAH)                     |

| Table 83. Timer A Low Byte Register (TAL)                      |

| Table 84. Timer A Reload Low Byte Register (TARL)              |

| Table 85. Timer A Control Register (TACTL)                     |

| Table 86. Timer A Reload High Byte Register (TARH)             |

| Table 87. Timer A Prescale Register (T <b>A</b> PS)            |

| Table 88. Timer Count Modes                                    |

xxi

| Table 89. Multi-Channel Timer Address Map                                  | 5 |

|----------------------------------------------------------------------------|---|

| Table 90. MCT High Byte Register (MCTH)                                    | 7 |

| Table 91. MCT Low Byte Register (MCTL)                                     | 7 |

| Table 92. MCT Reload High Byte Register (MCTRH)                            | 3 |

| Table 93. MCT Reload Low Byte Register (MCTRL)                             | 3 |

| Table 94. MCT Subaddress Register (MCTSA)                                  | 3 |

| Table 95. MCT Subregister <b>x</b> (MCTSR <b>x</b> )                       | ) |

| Table 96. Multi-Channel Timer Control 0 Register (MCTCTL0)                 | ) |

| Table 97. Multi-Channel Timer Control 1 Register (MCTCTL1)                 | 1 |

| Table 98. Multi-Channel Timer Channel Status 0 Register (MCTCHS0)          | 2 |

| Table 99. Multi-Channel Timer Channel Status 1 Register (MCTCHS1)          | 2 |

| Table 100. Multi-Channel Timer Channel Control Register (MCTCHyCTL) 173    | 3 |

| Table 101. Multi-Channel Timer Channel-y High Byte Registers (MCTCHyH) 175 | 5 |

| Table 102. Multi-Channel Timer Channel-y Low Byte Registers (MCTCHyL) 175  | 5 |

| Table 103. Watchdog Timer Approximate Time-Out Delays                      | 5 |

| Table 104. Watchdog Timer Reload Low Byte Register (WDTL=FF3h) 179         | ) |

| Table 105. Watchdog Timer Reload High Byte Register (WDTH=FF2h) 179        | ) |

| Table 106. Example Control Register Settings for DALI Mode                 | 7 |

| Table 107. UART-LDD Transmit Data Registers (UTXD)                         | 3 |

| Table 108. UART-LDD Receive Data Registers (UxRXD)                         | 3 |

| Table 109. UART-LDD Status 0 Register, Standard UART Mode (USTAT0) 209     | ) |

| Table 110. UART-LDD Status 0 Register, LIN Mode (USTAT0)                   | ) |

| Table 111. UART-LDD Status 0 Register, DALI Mode (USTAT0)                  | 2 |

| Table 112. UART-LDD Status 0 Register, DMX Mode (USTAT0)                   | 3 |

| Table 113. UART-LDD Mode Select and Status Register (UMDSTAT) 214          | 1 |

| Table 114. Mode Status Fields                                              | 5 |

| Table 115. UART-LDD Control 0 Register (UCTL0)                             | 7 |

| Table 116. Multiprocessor Control Register (UCTL1 with MSEL=000b) 219      | ) |

| Table 117. Noise Filter Control Register (UCTL1 with MSEL=001b)            | 1 |

| Table 118. LIN Control Register (UCTL1 with MSEL=010b)                     | 2 |

## Z8 Encore! XP® F3224 Series Product Specification

xxii

| Table 119. DALI Control Register (UCTL1 with MSEL=100b)                        | . 223 |

|--------------------------------------------------------------------------------|-------|

| Table 120. DMX Control Register (UCTL1 with MSEL=101b)                         | . 224 |

| Table 121. UART-LDD Address Compare Register (UADDR)                           | . 226 |

| Table 122. UART-LDD Baud Rate High Byte Register (UBRH)                        | . 226 |

| Table 123. UART-LDD Baud Rate Low Byte Register (UBRL)                         | . 227 |

| Table 124. UART-LDD Baud Rates, 20.0MHz System Clock                           | . 228 |

| Table 125. UART-LDD Baud Rates, 19.99848MHz System Clock                       | . 229 |

| Table 126. UART-LDD Baud Rates, 10.0 MHz System Clock                          | . 229 |

| Table 127. UART-LDD Baud Rates, <b>7.3728MHz</b> System Clock                  | . 229 |

| Table 128. UART-LDD Baud Rates, <b>2.4576MHz</b> System Clock                  | . 230 |

| Table 129. ESPI Clock Phase (PHASE) and Clock Polarity (CLKPOL) Operation      | . 235 |

| Table 130. ESPI Data Register (ESPIDATA)                                       | . 245 |

| Table 131. ESPI Transmit Data Command Register (ESPITDCR)                      | . 246 |

| Table 132. ESPI Control Register (ESPICTL)                                     | . 246 |

| Table 133. ESPI Mode Register (ESPIMODE)                                       | . 248 |

| Table 134. ESPI Status Register (ESPISTAT)                                     | . 251 |

| Table 135. ESPI State Register (ESPISTATE)                                     | . 252 |

| Table 136. ESPISTATE Values                                                    | . 253 |

| Table 137. ESPI Baud Rate High Byte Register (ESPIBRH)                         | . 254 |

| Table 138. ESPI Baud Rate Low Byte Register (ESPIBRL)                          | . 255 |

| Table 139. I <sup>2</sup> C Master/Slave Controller Registers                  | . 257 |

| Table 140. I <sup>2</sup> C Data Register (I2CDATA=F50h)                       | . 276 |

| Table 141. I <sup>2</sup> C Interrupt Status Register (I2CISTAT=F51h)          | . 277 |

| Table 142. I <sup>2</sup> C Control Register (I2CCTL)                          | . 278 |

| Table 143. I <sup>2</sup> C Baud Rate High Byte Register (I2CBRH=53h)          | . 280 |

| Table 144. I <sup>2</sup> C Baud Rate Low Byte Register (I2CBRL=F54h)          | . 280 |

| Table 145. I <sup>2</sup> C State Register (I2CSTATE), Description when DIAG=1 | . 281 |

| Table 146. I <sup>2</sup> C State Register (I2CSTATE), Description when DIAG=0 | . 282 |

| Table 147. I2CSTATE_H                                                          | . 283 |

| Table 148. I2CSTATE_L                                                          | . 283 |

## Z8 Encore! XP® F3224 Series Product Specification

xxiii

| Table 149. I <sup>2</sup> C Mode Register (I <sup>2</sup> C Mode=F56h)     | 284 |

|----------------------------------------------------------------------------|-----|

| Table 150. I <sup>2</sup> C Slave Address Register (I2CSLVAD=57h)          | 286 |

| Table 151. Event System Signal Sources                                     | 289 |

| Table 152. Event System Destinations                                       | 290 |

| Table 153. Event System Registers and Subregisters                         | 293 |

| Table 154. Event System Source Subaddress Register (ESSSA)                 | 294 |

| Table 155. Event System Source Subdata Register (ESSSD)                    | 295 |

| Table 156. Event System Channel 0–7 Source Subregisters (ESCHxSRC)         | 296 |

| Table 157. Event System Destination Subaddress Register (ESDSA)            | 297 |

| Table 158. Event System Destination Subdata Register (ESDSD)               | 298 |

| Table 159. Event System Destination 0–3F Channel Subregisters (ESDSTxCH) 2 | 299 |

| Table 160. Fixed Reference Control Register (FREFCTL)                      | 04  |

| Table 161. Programmable Reference 0 Control (PREF0CTL)                     | 05  |

| Table 162. Programmable Reference 1 Control (PREF1CTL)                     | 05  |

| Table 163. Compensating ADC results for ADC offset                         | 16  |

| Table 164. ADC Control 0 Register (ADCCTL0)                                | 17  |

| Table 165. ADC Control 1 Register (ADCCTL1)                                | 18  |

| Table 166. ADC Control 2 Register (ADCCTL2)                                | 19  |

| Table 167. ADC Input Select High Register (ADCINSH)                        | 20  |

| Table 168. ADC Input Select Low Register (ADCINSL)                         | 20  |

| Table 169. ADC Offset Calibration Register (ADCOFF)                        | 23  |

| Table 170. ADC Data High Register (ADCD_H)                                 | 24  |

| Table 171. ADC Data Low Register (ADCD_L)                                  | 25  |

| Table 172. Sample Time (ADCST)                                             | 26  |

| Table 173. ADC Window Upper Threshold High Register (ADCUWINH)             | 26  |

| Table 174. ADC Window Upper Threshold Low Register (ADCUWINL)              | 27  |

| Table 175. ADC Window Lower Threshold High Register (ADCLWINH)             | 28  |

| Table 176. ADC Window Lower Threshold Low Register (ADCLWINL)              | 29  |

| Table 177. Op Amp Register Summary                                         | 33  |

| Table 178. Op Amp A0-1 Control 0 Register (AMPAxCTL0)                      | 34  |

xxiv

| Table 179. Op Amp A0-1 Control 1 Register (AMPAxCTL1)        | 335   |

|--------------------------------------------------------------|-------|

| Table 180. Effect of WINEN and POLSEL on Comparator Outputs  | 339   |

| Table 181. Comparator Control Register (CMPCTL)              | 341   |

| Table 182. Comparator 0 Control 0 Register (CMP0CTL0)        | . 342 |

| Table 183. Comparator 0 Control 1 Register (CMP0CTL1)        | . 343 |

| Table 184. Comparator 1 Control 0 Register (CMP1CTL0)        | . 344 |

| Table 185. Comparator 1 Control 1 Register (CMP1CTL1)        | 345   |

| Table 186. F3224 Series Flash Memory Configurations          | 346   |

| Table 187. Flash Code Protection Using the Flash Option Bit  | 350   |

| Table 188. Flash Control Register (FCTL)                     | . 354 |

| Table 189. Flash Status Register (FSTAT)                     | 355   |

| Table 190. Flash Page Select Register (FPS)                  | 356   |

| Table 191. Flash Block Protect Register (FPROT)              | 357   |

| Table 192. Trim Bit Address Register (TRMADR)                | 361   |

| Table 193. Trim Bit Address Map                              | 361   |

| Table 194. Trim Bit Data Register (TRMDR)                    | 362   |

| Table 195. Flash Option Bits at Program Memory Address 0000h | 362   |

| Table 196. Flash Option Bits at Program Memory Address 0001h | 363   |

| Table 197. Trim Bit Address Description                      | 364   |

| Table 198. Trim Option Bits at Address 0000h (TBA0)          | 364   |

| Table 199. Trim Option Bits at Address 0001h                 | 365   |

| Table 200. Trim Option Bits at Address 0002h (TVBG)          | 365   |

| Table 201. Trim Option Bits at Address 0003h (TIPO)          | 366   |

| Table 202. Trim Option Bits at Address 0004h (TLVD_VBO)      | 366   |

| Table 203. LVD_Trim Values                                   | 367   |

| Table 204. Trim Option Bits at Address 0005h (TVREF)         | 368   |

| Table 205. Trim Option Bits at Address 0006h (TVREG)         | 368   |

| Table 206. Trim Option Bits at Address 0007h                 | 369   |

| Table 207. Trim Option Bits at Address 0008h                 | 370   |

| Table 208. Trim Option Bits at Address 0009h                 | 370   |

XXV

| Table 209. Trim Option Bits at Address 000Ah                         | 70 |

|----------------------------------------------------------------------|----|

| Table 210. Trim Option Bits at Address 000Bh                         | 71 |

| Table 211. Trim Option Bits at Address 000Ch (VBIAS)                 | 71 |

| Table 212. Debug Interface pin Description                           | 75 |

| Table 213. OCD Baud-Rate Limits                                      | 77 |

| Table 214                                                            | 78 |

| Table 215. Assembly Language Source Program Example                  | 79 |

| Table 216. Assembly Language Syntax Example 1                        | 80 |

| Table 217. Assembly Language Syntax Example 2                        | 80 |

| Table 218. Notational Shorthand                                      | 81 |

| Table 219. Additional Symbols                                        | 82 |

| Table 220. Arithmetic Instructions                                   | 83 |

| Table 221. Bit Manipulation Instructions                             | 84 |

| Table 222. Block Transfer Instructions                               | 84 |

| Table 223. CPU Control Instructions                                  | 84 |

| Table 224. Logical Instructions                                      | 85 |

| Table 225. Load Instructions                                         | 85 |

| Table 226. Program Control Instructions                              | 86 |

| Table 227. Rotate and Shift Instructions                             | 86 |

| Table 228. eZ8 CPU Instruction Summary                               | 87 |

| Table 229. Op Code Map Abbreviations                                 | 97 |

| Table 230. Absolute Maximum Ratings                                  | 00 |

| Table 231. DC Characteristics                                        | 01 |

| Table 232. Supply Current Characteristics                            | 02 |

| Table 233. AC Characteristics                                        | 03 |

| Table 234. Power-On Reset Electrical Characteristics and Timing      | 04 |

| Table 235. Voltage Brown-Out Electrical Characteristics and Timing 4 | 05 |

| Table 236. Stop-Mode Recovery (SMR) Timing                           | 05 |

| Table 237. Flash Memory Electrical Characteristics and Timing        | 06 |

| Table 238. Watchdog Timer Electrical Characteristics and Timing 4    | 06 |

xxvi

| Table 239. Reference System Electrical Characteristics                       | . 407 |

|------------------------------------------------------------------------------|-------|

| Table 240. Analog-to-Digital Converter Electrical Characteristics and Timing | . 409 |

| Table 241. Comparator Electrical Characteristics                             | . 411 |

| Table 242. Operational Amplifier Electrical Characteristics                  | . 412 |

| Table 243. Low Voltage Detect Electrical Characteristics                     | . 414 |

| Table 244. IPO Electrical Characteristics                                    | . 415 |

| Table 245. Low Frequency Oscillator (LFXO) Characteristics                   | . 415 |

| Table 246. DCO and FLL Electrical Characteristics                            | . 416 |

| Table 247. GPIO Port Input Timing                                            | . 417 |

| Table 248. GPIO Port Output Timing                                           | . 418 |

| Table 249. On-Chip Debugger Timing                                           | . 419 |

| Table 250. UART Timing with CTS                                              | . 420 |

| Table 251. UART Timing Without CTS                                           | . 421 |

| Table 252. F3224 Series Ordering Information                                 | . 423 |

| Table 253. F3224 ZMOTION Series Ordering Information                         | . 425 |

| Table 254. Package and Pin Count Description                                 | . 426 |

## **Chapter 1. Overview**

Zilog's F3224 Series MCUs, members of the Z8 Encore! XP<sup>®</sup> family, are based on Zilog's advanced 8-bit eZ8 CPU core. This microcontroller is optimized for low-power and wireless applications, and supports 1.8 V to 3.6 V low-voltage operation with extremely low Active, Halt and Stop Mode currents, plus it offers an assortment of speed and low-power options. In addition, the feature-rich analog and digital peripherals of the F3224 Series makes it suitable for a variety of applications including safety and security, utility metering, digital power supervisory, hand-held electronic devices, sensing, motion detection and general motor control.

### 1.1. Features

Key features of the F3224 Series MCU include:

- 20MHz eZ8 CPU core

- 16KB or 32KB Flash memory with in-circuit programming capability

- 3.75KB internal RAM

- Up to 15-Channel, 12-bit Analog-to-Digital Converter (ADC) that can be configured for internal or external voltage reference and single-ended or differential inputs

- Two on-chip analog comparators

- Two on-chip, low-power operational amplifiers

- 8 Channel Event System provides communication between peripherals for autonomous triggering

- Full-duplex 9-bit UART port with the support of Local Interconnect Network (LIN) and Digital Addressable Lighting Interface (DALI) protocols. RS-485 Multidrop Mode up to 250kbit/sec (DMX Support) integrated with UARTs

- Enhanced Serial Peripheral Interface (SPI) controller

- I<sup>2</sup>C controller which supports Master/Slave modes

- One 16-bit timer with 3 functional modes

- Three enhanced 16-bit timers with Capture, Compare, and PWM capability

- One additional basic 16-bit timer with interrupt (shared as UART Baud Rate Generator)

- 16-bit Multi-Channel Timer which supports four Capture/Compare/PWM modules

- Watchdog Timer (WDT)

- 26 to 36 General-Purpose Input/Output (GPIO) pins, depending upon package

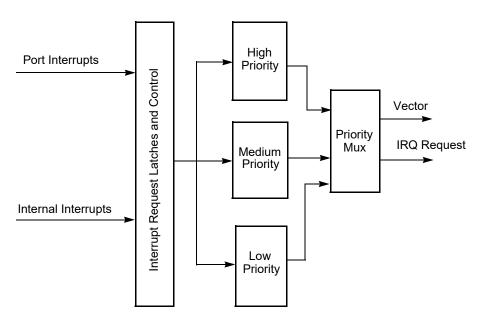

- Up to 30 interrupt sources with up to 23 interrupt vectors

- On-Chip Debugger (OCD)

- Power-On Reset (POR) and Voltage Brown-Out (VBO) protection

- Built-in Low-Voltage Detection (LVD) with programmable voltage threshold

- Low Frequency Crystal Oscillator (LFXO) operating at 32.768kHz with low power consumption

- Internal clock sources and clock multiplication including: Internal Precision Oscillator (IPO), Digitally Controlled Oscillator (DCO), Watchdog Timer Oscillator (WTO) and Frequency Locked Loop (FLL)

- Wide operation voltage range: 1.8V–3.6V

- 32-, and 44-pin packages

- -40°C to +85°C (extended) operating temperature range

### 1.2. Part Selection Guide

Table 1 shows basic features and package styles available for each device within the F3224 Series product line.

**Table 1. F3224 Series Family Part Selection Guide**

| Part<br>Number | Flash<br>(KB) |      | I/O   | ADC<br>Inputs | SPI | I <sup>2</sup> C | UART | Packages        |

|----------------|---------------|------|-------|---------------|-----|------------------|------|-----------------|

| Z8F3224        | 32            | 3840 | 26–36 | 13-19         | 1   | 1                | 1    | 32-, and 44-pin |

| Z8F1624        | 16            | 3840 | 26–36 | 13-19         | 1   | 1                | 1    | 32-, and 44-pin |

3

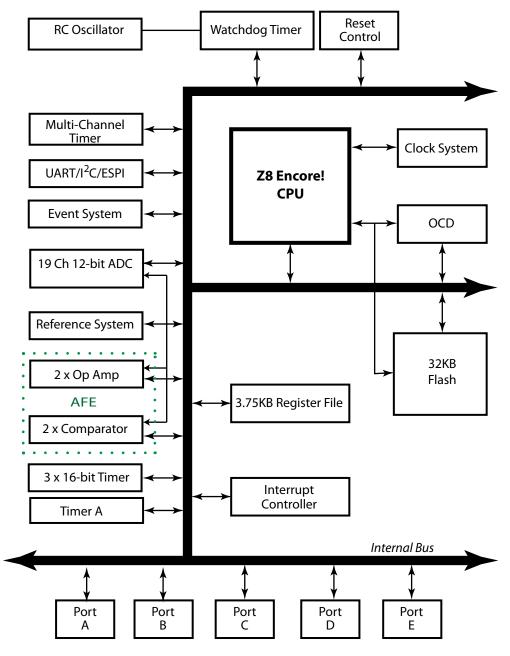

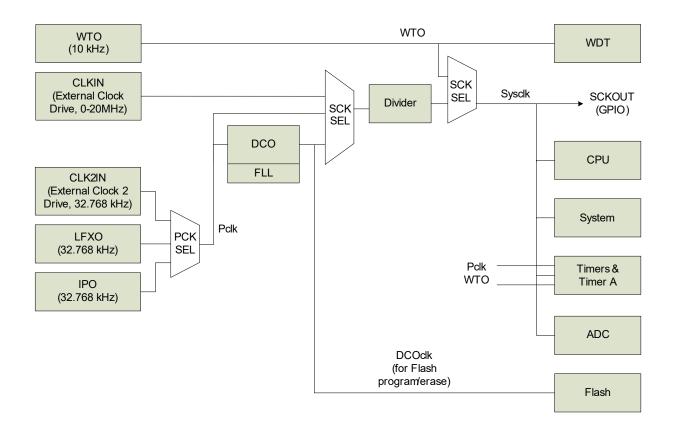

## 1.3. Block Diagram

Figure 1 shows a block diagram of the F3224 Series architecture.

Figure 1. F3224 Series Block Diagram

## 1.4. eZ8 CPU and Peripheral Overview

Zilog's 8-bit eZ8 CPU meets the continuing demand for faster and more code-efficient microcontrollers. It executes a superset of the original Z8 instruction set. The key features of the eZ8 CPU are:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required Program Memory

- Software stack allows greater depth in subroutine calls and interrupts more than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access up to 4KB

- New instructions improve execution efficiency for code developed using higher-level programming languages including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the register file

- Up to 10MIPS operation

- C Compiler-friendly

- 2 to 9 clock cycles per instruction

To learn more about the eZ8 CPU, refer to the eZ8 CPU Core User Manual (UM0128), which is available free for download from the Zilog website.

### 1.4.1. General-Purpose Input/Output

The F3224 Series features 14 to 36 port pins (Ports A–E) for general purpose input/output (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable.

#### 1.4.2. Flash Controller

The Flash Controller is used to program and erase Flash memory, and supports protection against accidental program and erasure.

## 1.4.3. Clock System

The clock system generates a System Clock, a low-frequency Peripheral Clock, and the Watchdog Timer Oscillator. It is comprised of:

- Watchdog Timer Oscillator (WTO).

- 32.768 kHz Internal Precision Oscillator (IPO).

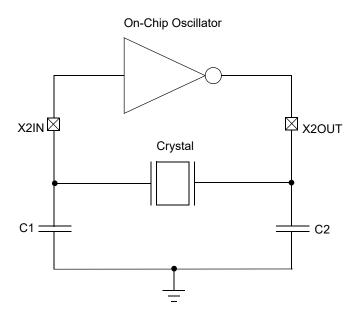

- Low Frequency Crystal Oscillator (LFXO) which is a low-power oscillator optimized for use with a 32.768kHz watch crystal. The IPO and LFXO can be used as clock sources for the Timers in any mode, and as the reference clock for the Frequency Locked Loop (FLL).

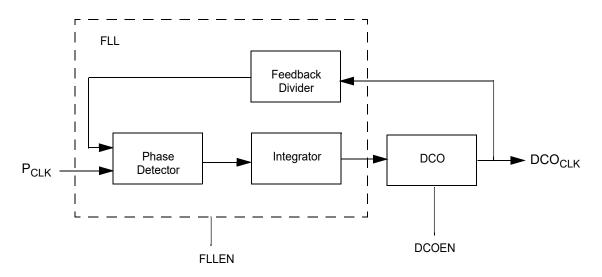

- Digitally Controlled Oscillator (DCO).

- Frequency Locked Loop (FLL). The reference clock for the FLL can be either an Internal Precision Oscillator (IPO) or a Low Frequency Crystal Oscillator. The FLL, in conjunction with the DCO can be configured to generate system clock frequencies from 1 to 20MHz.

#### 1.4.4. Reference System

The Reference System provides programmable and fixed references to the analog peripherals.

#### 1.4.5. 12-Bit Analog-to-Digital Converter

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 12-bit binary number. The ADC supports up to fifteen analog input sources multiplexed with GPIO ports. It is configurable for internal or external voltage reference and single-ended or differential inputs.

#### 1.4.6. **Low-Power Operational Amplifiers**

Two low-power operational amplifiers (Op Amps) are provided: Op Amp A0 and Op Amp A1. Op Amp Ax (x = 0-1) are low-power, general-purpose operational amplifiers with optional internal programmable gain settings. Each Op Amp output can be internally routed to an op amp input, the ADC, a comparator, or an output pin. These op amps can function in all operating modes, including Stop Mode.

#### 1.4.7. **Analog Comparators**

The analog comparators compare the signal at an input pin or at other internal signal sources with either an internal programmable voltage reference, an internal fixed reference, or a second input pin. The comparator outputs are used to either drive an output pin, the Event System, or to generate an interrupt. The comparators can function in all operating modes including Stop Mode.

#### 1.4.8. Low-Voltage Detector

The low-voltage detector generates an interrupt when the supply voltage drops below a user-programmable level.

6

### 1.4.9. Enhanced SPI

The enhanced SPI is a full-duplex, buffered, synchronous character-oriented channel which supports a four-wire interface.

### 1.4.10. UART with LIN, DALI, and DMX

A full-duplex 9-bit UART provides serial, asynchronous communication, and supports the Local Interconnect Network (LIN) and Digital Addressable Lighting Interface (DALI) serial communications protocols as well as Asynchronous Serial Digital Data Transmission Standard for Controlling Lighting Equipment and Accessories (DMX). The UART supports 8-bit and 9-bit data modes, selectable parity, and an efficient bus transceiver Driver Enable signal for controlling a multi-transceiver bus, such as a RS-485. The LIN bus is a cost-efficient, single-master, multiple-slave organization which supports speed up to 20 kilobits. Manchester encoding is supported for the DALI protocol.

### 1.4.11. Master/Slave I<sup>2</sup>C